Professional Documents

Culture Documents

IC Lab Manual by Suresh Babu

Uploaded by

nandakishore.nallaCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

IC Lab Manual by Suresh Babu

Uploaded by

nandakishore.nallaCopyright:

Available Formats

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Department Of ELECTRONICS AND COMMUNICATION ENGINEERING

IC Applications Lab Manual

B.Tech (ECE) III Year I Semester Prepared By Mr. SURESH BABU M

Asst. Prof, ECE Dept., AITH

ANNAMACHARYA INSTITUTE OF TECHNOLOGY AND SCIENCES

Piglipur, Batasingaram, R R DISTRICT 501 512 (A. P.)

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

ANNAMACHARYA INSTITUTE OF TECHNOLOGY AND SCIENCES (Approved by A.I.C.T.E, New Delhi, Affiliated to JNTU, Hyderabad) Campus: Piglipur, Bata Singaram, R. R. District, Hyderabad-501512 (A.P.) Ph.08415-201688

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

CERTIFICATE

This is to certify that Mr./Ms/Mrs _______________________________________ Roll No___________________ Year___________ Semester _________ Department of

_____________ has successfully completed the experiments in the ______________________ lab Prescribed by JNTUH during the academic year _____________.

Internal Examiner

External Examiner

Head of the Department

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

LAB CODE

1. Students should report to the concerned labs as per the time table schedule. 2. Students who turn up late to the labs will in no case be permitted to perform the experiment scheduled for the day. 3. Students should bring a note book of about 100 pages and should enter the readings/observations into the note book while performing the experiment. 4. After completion of the experiment, certification of the concerned staff in-charge in the observation book is necessary. 5. The record of observations along with the detailed experimental procedure of the experiment performed in the immediate last session should be submitted and certified by the staff member in-charge 6. Not more than three students in a group are permitted to perform the experiment on a setup. 7. The group-wise division made in the beginning should be adhered to, and no mix up of student among different groups will be permitted later. 8. The components required pertaining to the experiment should be collected from stores incharge after duly filling in the requisition form. 9. When the experiment is completed, students should disconnect the setup made by them, and should return all the components/instruments taken for the purpose .Any damage of the equipment or burn-out of components will be viewed seriously either by putting penalty or by dismissing the total group of students from the lab for the semester/year. 10. Students should be present in the labs for the total scheduled duration. 11. Students are required to prepare thoroughly to perform the experiment coming to Laboratory. Procedure sheets/data sheets provided to the students groups should be maintained neatly and to be returned after the experiment.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

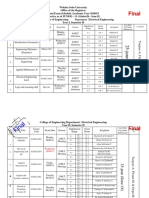

IC APPLICATIONS LAB III Year B.Tech ECE I sem.

LIST OF EXPERIMENTS:

PART 1:TO VERITY THE FOLLOWING FUNCTIONS. 1. Adder, Sustractor, Comparator using IC 741 Op-Amp. 2. Integrator and Differentiator Using IC 741 Op-Amp . 3. IC 555 timer in Monostable Operation. 4. Schmitt trigger circuits using IC 741 &IC 555. 5. IC 565-PLL Application 6. Voltage regulator IC 723, three terminal voltage regulators-7805, 7809, 7912. 7. Active Low pass & High pass Butterworth (Second order) 8. RC Phase Shift and Wien Bridge Oscillators using IC-741 Op-Amp 9. Sample and Hold LF 398 IC. PART 2: TO VERIFY THE FUNCTIONALITY OF THE FOLLOWING

74 SERIES TTL ICs.

1. D Flip-Flop (74LS74) and JK Master-Slave Flip-Flop. 2. Decade Counter (74LS90) and Up-Down Counter (74LS192). 3. Universal Shift Registers-74LS194/195. 4. 3-8 Decoder-74LS138. 5. 4 bit Comparator 74LS85. 6. 81 Multiplexer-74151 and 24demultiplexer-74155. 7. RAM (164)-74189(Read and Write Operations). 8. Stack and queue Implementation using RAM 74189.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

INDEX

Title Page Certificate Lab Code Study of OP AMPs - IC 741, IC 555-functioning, parameters and specifications i ii iii 2

PART 1:

1. Adder, Subtractor, Comparator using IC 741 Op-Amp 2. Active Low pass & High pass Butterworth (Second order) 8 13 18 26 32 36 40,44

3. Integrator and Differentiator Using IC 741 Op-Amp 4. RC Phase Shift and Wien Bridge Oscillators using IC-741 Op-Amp 5. IC 555 timer in Monostable Operation 6. Schmitt trigger circuits using IC 741 &IC 555 7. Voltage regulator IC 723, Three terminal voltage regulators-7805, 7809, 7912

PART 2:

74 SERIES TTL ICs. 1. D Flip-Flop (74LS74) and JK Master-Slave Flip-Flop 2. Decade Counter (74LS90) and Up-Down Counter (74LS192) 3. Universal Shift Registers-74LS194/195 4. 3-8 Decoder-74LS138 5. 4 bit Comparator 74LS85 6. 81 Multiplexer-74151 and 24demultiplexer-74155 7. RAM (164)-74189(Read and Write Operations) 56 58 61 65 67 69 73

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

PART 1 LICA LAB

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Study of OP AMPs - IC 741, IC 555-functioning, parameters and specifications

IC 741 :

General Description:

The IC 741 is a high performance monolithic operational amplifier constructed using the planer epitaxial process. High common mode voltage range and absence of latch-up tendencies make the IC 741 ideal for use as voltage follower. The high gain and wide range of operating voltage provide superior performance in integrator, summing amplifier and general feedback applications.

Block Diagram of Op-Amp:

Pin Configuration:

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Features:

1. No frequency compensation required. 2. Short circuit protection 3. Offset voltage null capability 4. Large common mode and differential voltage ranges 5. Low power consumption 6. No latch-up

Specifications:

1. Voltage gain A = typically 2,00,000 2. I/P resistance RL = , practically 2M 3. O/P resistance R =0, practically 75 4. Bandwidth = Hz. It can be operated at any frequency 5. Common mode rejection ratio = (Ability of op amp to reject noise voltage) 6. Slew rate + V/sec (Rate of change of O/P voltage) 7. When V1 = V2, VD=0 8. Input offset voltage (Rs 10K) max 6 mv 9. Input offset current = max 200nA 10. Input bias current : 500nA 11. Input capacitance : typical value 1.4pF 12. Offset voltage adjustment range : 15mV 13. Input voltage range : 13V 14. Supply voltage rejection ratio : 150 V/V 15. Output voltage swing: + 13V and 13V for RL > 2K 16. Output short-circuit current: 25mA 17. supply current: 28mA 18. Power consumption: 85mW 19. Transient response: rise time= 0.3 s Overshoot= 5% Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Applications:

1. AC and DC amplifiers 2. Active filters 3. Oscillators 4. Comparators 5. Regulators

IC 555:

Description:

The operation of SE/NE 555 timer directly depends on its internal function. The three equal resistors R1, R2, R3 serve as internal voltage divider for the source voltage. Thus one-third of the source voltage VCC appears across each resistor. Comparator is basically an Op amp which changes state when one of its inputs exceeds the reference voltage. The reference voltage for the lower comparator is +1/3 VCC. If a trigger pulse applied at the negative input of this comparator drops below +1/3 VCC, it causes a change in state. The upper comparator is referenced at voltage +2/3 VCC. The output of each comparator is fed to the input terminals of a flip flop. The flip-flop used in the SE/NE 555 timer IC is a bistable multivibrator. This flip flop changes states according to the voltage value of its input. Thus if the voltage at the threshold terminal rises above +2/3 VCC, it causes upper comparator to cause flip-flop to change its states. On the other hand, if the trigger voltage falls below +1/3 VCC, it causes lower comparator to change its states. Thus the output of the flip flop is controlled by the voltages of the two comparators. A change in state occurs when the threshold voltage rises above +2/3 VCC or when the trigger voltage drops below +1/3 Vcc. The output of the flip-flop is used to drive the discharge transistor and the output stage. A high or positive flip-flop output turns on both the discharge transistor and the output stage. The discharge transistor becomes conductive and behaves as a low resistance short circuit to ground. The output stage behaves similarly. When the flip-flop output assumes the low or zero states reverse action takes place i.e., the discharge transistor behaves as an open circuit or positive VCC state. Thus the operational state of

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

the discharge transistor and the output stage depends on the voltage applied to the threshold and the trigger input terminals.

Block Diagram of IC 555:

Pin Configuration:

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Function of Various Pins of 555 IC:

Pin (1) of 555 is the ground terminal; all the voltages are measured with respect to this pin. Pin (2) of 555 is the trigger terminal, If the voltage at this terminal is held greater than one-third of

VCC, the output remains low. A negative going pulse from Vcc to less than Vec/3 triggers the output to go High. The amplitude of the pulse should be able to make the comparator (inside the IC) change its state. However the width of the negative going pulse must not be greater than the width of the expected output pulse. Pin (3) is the output terminal of IC 555. There are 2 possible output states. In the low output state, the output resistance appearing at pin (3) is very low (approximately 10 ). As a result the output current will goes to zero , if the load is connected from Pin (3) to ground , sink a current I Sink (depending upon load) if the load is connected from Pin (3) to ground, and sinks zero current if the load is connected between +VCC and Pin (3). Pin (4) is the Reset terminal. When unused it is connected to +Vcc. Whenever the potential of Pin (4) is drives below 0.4V, the output is immediately forced to low state. The reset terminal enables the timer over-ride command signals at Pin (2) of the IC. Pin (5) is the Control Voltage terminal. This can be used to alter the reference levels at which the time comparators change state. A resistor connected from Pin (5) to ground can do the job. Normally 0.01F capacitor is connected from Pin (5) to ground. This capacitor bypasses supply noise and does not allow it affect the threshold voltages. Pin (6) is the threshold terminal. In both astable as well as monostable modes, a capacitor is connected from Pin (6) to ground. Pin (6) monitors the voltage across the capacitor when it charges from the supply and forces the already high O/p to Low when the capacitor reaches +2/3 VCC. Pin (7) is the discharge terminal. It presents an almost open circuit when the output is high and allows the capacitor charge from the supply through an external resistor and presents an almost short circuit when the output is low. Pin (8) is the +Vcc terminal. 555 can operate at any supply voltage from +3 to +18V.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Features of 555 IC

1. The load can be connected to o/p in two ways i.e. between pin 3 & ground 1 or between pin 3 & VCC (supply) 2. 555 can be reset by applying negative pulse, otherwise reset can be connected to +V cc to avoid false triggering. 3. An external voltage effects threshold and trigger voltages. 4. Timing from micro seconds through hours. 5. Monostable and bistable operation 6. Adjustable duty cycle 7. Output compatible with CMOS, DTL, TTL 8. High current output sink or source 200mA 9. High temperature stability 10. Trigger and reset inputs are logic compatible.

Specifications:

1. Operating temperature 2. Supply voltage 3. Timing 4. Sink current 5. Temperature stability : : : : : SE 555-- -55oC to 125oC ,NE555---0 o to 70 o C +5V to +18V Sec to Hours 200mA 50 PPM/oC change in temp or 0-005% /oC.

Applications:

Monostable and Astable Multivibrators 1. dc-ac converters 2. Digital logic probes 3. Waveform generators 4. Analog frequency meters 5. Tachometers 6. Temperature measurement and control 7. Infrared transmitters 8. Regulator & Taxi gas alarms etc.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

1. OP AMP APPLICATIONS - ADDER, SUBTRACTOR, COMPARATOR CIRCUITS

AIM: To study the applications of IC 741 as adder, sub tractor, comparator. APPARATUS: 1. IC 741 2. Resistors (1K)4 3. Function generator 4. Regulated power supply 5. IC bread board trainer 6. CRO 7. Patch cards and CRO probes CIRCUIT DIAGRAM: Adder:

Subtractor:

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY Comparator:

IC Applications LAB

THEORY: ADDER: Op-Amp may be used to design a circuit whose output is the sum of several input signals such as circuit is called a summing amplifier or summer. We can obtain either inverting or non inverting summer. The circuit diagrams shows a two input inverting summing amplifier. It has two input voltages V1and V2, two input resistors R1, R2 and a feedback resistor Rf. Assuming that op-amp is in ideal conditions and input bias current is assumed to be zero, there is no voltage drop across the resistor Rcomp and hence the non inverting input terminal is at ground potential. By taking nodal equations. V1/R1 +V2/R2 +V0/Rf =0 V0 = - [(Rf/R1) V1 +(Rf/R2) V2] And here R1 = R2 = Rf = 1K V0 = -(V1 +V2) Thus output is inverted and sum of input. SUBTRACTOR: A basic differential amplifier can be used as a sub tractor. It has two input signals V1 and V2 and two input resistances R1 and R2 and a feedback resistor Rf. The input signals scaled to the desired values by selecting appropriate values for the external resistors. From the figure, the output voltage of the differential amplifier with a gain of 1 is V0 = -R/Rf(V2-V1) V0 = V1-V2. Also R1 =R2 = Rf =1K. Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Thus, the output voltage V0 is equal to the voltage V1 applied to the non inverting terminal minus voltage V2 applied to inverting terminal. Hence the circuit is sub tractor. COMPARATOR: A comparator is a circuit which compares a signal voltage applied at one input of an op-amp with a known reference voltage at the other input. It is basically an open loop op-amp with output Vsat as in the ideal transfer characteristics. It is clear that the change in the output state takes place with an increment in input Vi of only 2mv. This is the uncertainty region where output cannot be directly defined There are basically 2 types of comparators. 1. Non inverting comparator and. 2. Inverting comparator. The applications of comparator are zero crossing detectors, window detector, and time marker generator and phase meter.

OBSERVATIONS: ADDER: V1(V) 2.5 3.8 V2(V) 2.5 4.0 Vo(V) -5.06 -8.04 V1(V) 2.5 4.1 COMPARATOR: MODEL GRAPH: V2(V) 3.3 5.7 Vo(V) 0.8 1.67 SUBTRACTOR:

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY PROCEDURE: ADDER: 1. Connections are made as per the circuit diagram. 2. Apply input voltage 1) V1= 5v,V2=2v 2) V1= 5v,V2=5v 3) V1= 5v, V2=7v. 3. Using Millimeter measure the dc output voltage at the output terminal. 4. For different values of V1 and V2 measure the output voltage. SUBTRACTOR: 1. Connections are made as per the circuit diagram. 2. Apply input voltage 1) V1= 5v,V2=2v 2) V1= 5v,V2=5v 3) V1= 5v,V2=7v. 3. Using multi meter measure the dc output voltage at the output terminal. 4. For different values of V1 and V2 measure the output voltage. COMPARATOR: 1. Connections are made as per the circuit diagram. 2. Select the sine wave of 10V peak to peak, 1K Hz frequency.

IC Applications LAB

3. Apply the reference voltage 2V and trace the input and output wave forms. 4. Superimpose input and output waveforms and measure sine wave amplitude with reference to Vref. 5. Repeat steps 3 and 4 with reference voltages as 2V, 4V, -2V, -4V and observe the waveforms. 6. Replace sine wave input with 5V dc voltage and Vref= 0V. 7. Observe dc voltage at output using CRO. 8. Slowly increase Vref voltage and observe the change in saturation voltage. PRECAUTIONS: 1. Make null adjustment before applying the input signal. 2. Maintain proper Vcc levels. RESULT: The operation of IC 741 Op-Amp as adder, sub tractor and comparator is studied and values are noted.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

VIVA QUESTIONS: 1. What is an op-amp? 2. What are ideal characteristics of op amp? 3. What is the function of adder? 4. What is meant by comparator?

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

2. ACTIVE FILTER APPLICATIONS - LPF, HPF [ FIRST ORDER ]

AIM: To study Op-Amp as first order LPF and first order HPF and to obtain frequency response. APPARATUS: 1. IC 741. 2. Resistors (10K--2, 560, 330 3. Capacitors(0.1) 4. Bread board trainer 5. CRO 6. Function generator 7. connecting wires 8. Patch cards. CIRCUIT DIAGRAM: (a) LPF (b) HPF

THEORY: LOWPASS FILTER: A LPF allows frequencies from 0 to higher cut of frequency, fH. At fH the gain is 0.707 Amax, and after fH gain decreases at a constant rate with an increase in frequency. The gain decreases 20dB each time the frequency is increased by 10. Hence the rate at which the gain rolls off after f H is 20dB/decade or 6 dB/ octave, where octave signifies a two fold increase in frequency. Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH, The frequency f=fH is called the cut off frequency because the gain of the filter at this frequency is down Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

by 3 dB from 0 Hz. Other equivalent terms for cut-off frequency are -3dB frequency, break frequency, or corner frequency. HIGH PASS FILTER: The frequency at which the magnitude of the gain is 0.707 times the maximum value of gain is called low cut off frequency. Obviously, all frequencies higher than f L are pass band frequencies with the highest frequency determined by the closed loop band width all of the op-amp.

Design:

First Order LPF: To design a Low Pass Filter for higher cut off frequency f H = 4 KHz and pass band gain of 2 fH = 1/( 2RC ) Assuming C=0.01 F, the value of R is found from R= 1/(2fHC) =3.97K The pass band gain of LPF is given by RF=( AF-1) R1=10K First Order HPF: To design a High Pass Filter for lower cut off frequency fL = 4 KHz and pass band gain of 2 fL = 1/( 2RC ) Assuming C=0.01 F,the value of R is found from R= 1/(2fLC) =3.97K The pass band gain of HPF is given by RF=( AF-1) R1=10K AF = 1+ (RF/R1)= 2 Assuming R1=10 K, the value of RF is found from AF = 1+ (RF/R1)= 2 Assuming R1=10 K, the value of RF is found from

Procedure: First Order LPF 1. 2. Connections are made as per the circuit diagram shown in Fig 1. Apply sinusoidal wave of constant amplitude as the input such that op-amp does not go into saturation. 3. 4. Vary the input frequency and note down the output amplitude at each step as shown in Table (a). Plot the frequency response as shown in Fig 3.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY First Order HPF 1. 2. Connections are made as per the circuit diagrams shown in Fig 2.

IC Applications LAB

Apply sinusoidal wave of constant amplitude as the input such that op-amp does not go into saturation.

3. 4.

Vary the input frequency and note down the output amplitude at each step as shown in Table (b). Plot the frequency response as shown in Fig 4.

OBSERVATIONS: Tabular Form and Sampled Values: a)LPF Input voltage Vin = 0.5V

Frequency

O/P Voltage(V)

Voltage Gain Vo/Vi

Gain indB

100Hz 200Hz 300Hz 500Hz 750Hz 900Hz 1KHz 2KHz 3KHz 4KHz 5KHz 6KHz 7KHz 8KHz 9KHz 10KHz

0.9 0.9 0.9 0.9 0.9 0.9 0.9 0.8 0.75 0.7 0.65 0.55 0.5 0.45 0.4 0.35

1.8 1.8 1.8 1.8 1.8 1.8 1.8 1.6 1.5 1.4 1.3 1.1 1.0 0.9 0.8 0.7

5.105 5.105 5.105 5.105 5.105 5.105 5.105 4.08 3.52 2.92 2.27 0.82 0 -0.91 -1.94 -3.09

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY b) HPF Frequency O/P Voltage(V) Voltage Gain Vo/Vi 500Hz 700Hz 800Hz 1KHz 2KHz 3KHz 4KHz 5KHz 6KHz 7KHz 8KHz 9KHz 10KHz 0.12 0.16 0.2 0.24 0.4 0.55 0.7 0.75 0.8 0.85 0.85 0.85 0.85 0.24 0.32 0.4 0.48 0.8 1.1 1.4 1.5 1.6 1.7 1.7 1.7 1.7 -12.39 -9.89 -7.95 -6.38 -1.938 0.83 2.92 3.52 4.08 4.60 4.60 4.60 4.60 Gain indB

IC Applications LAB

MODEL GRAPH: High Pass Filter Low Pass Filter

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY PRECAUTIONS: 1. Make null adjustment before applying the input signal. 2. Maintain proper Vcc levels.

IC Applications LAB

RESULT: The frequency response of LPF and HPF is plotted using IC741 Op-Amp.

VIVA QUESTIONS: 1. What is the function of the filter? 2. What are the different types of filters? 3. Define pass band and stop band of filters? 4. Define cut off frequency? 5. What is the difference between HPF&LPF?

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

3. Integrator and Differentiator Circuits using IC 741

Aim: To design and verify the operation of an integrator and differentiator for a given input.

Apparatus required: S.No 1 2 3 4 5 6 Equipment/Component name 741 IC Capacitors Resistors Regulated Power supply Function generator Cathode Ray Oscilloscope Specifications/Value Refer page no 2 0.1f, 0.01f 159, 1.5k (0 30)V,1A (1Hz 1MHz) (0 20MHz) Quantity 1 Each one Each one 1 1 1

Theory Integrator: In an integrator circuit, the output voltage is integral of the input signal. The output voltage of an integrator is given by Vo = -1/R1Cf

Vidt

o

At low frequencies the gain becomes infinite, so the capacitor is fully charged and behaves like an open circuit. The gain of an integrator at low frequency can be limited by connecting a resistor in shunt with capacitor.

Differentiator: In the differentiator circuit the output voltage is the differentiation of the input voltage. The output voltage of a differentiator is given by Vo = -RfC1

dVi .The input impedance of dt

this circuit decreases with increase in frequency, thereby making the circuit sensitive to high frequency noise. At high frequencies circuit may become unstable.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY Circuit Diagrams:

IC Applications LAB

Fig 1: Integrator

Fig 2: Differentiator

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY Design equations: Integrator: Choose T = 2RfCf Where T= Time period of the input signal Assume Cf and find Rf Select Rf = 10R1

IC Applications LAB

Vo (p-p) =

1 R1C f

T /2

V

o

i ( p p)

dt

Differentiator Select given frequency fa = 1/(2RfC1), Assume C1 and find Rf Select fb = 10 fa = 1/2R1C1 and From R1C1 = RfCf, find Cf Procedures: Integrator find R1

1. Connect the circuit as per the diagram shown in Fig 2. Apply a square wave/sine input of 4V(p-p) at 1KHz 3. Observe the output at pin 6. 4. Draw input and output waveforms as shown in Fig

Differentiator 1. Connect the circuit as per the diagram shown in Fig 2. Apply a square wave/sine input of 4V(p-p) at 1KHz 3. Observe the output at pin 6 4. Draw the input and output waveforms as shown in Fig Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY Wave Forms: Integrator

IC Applications LAB

Fig 3: Input and output waves forms of integrator

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY Differentiator

IC Applications LAB

Fig 4 :Input and output waveforms of Differentiator Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY Sample readings: Integrator Input Square wave Amplitude(VP-P) (V) 8 Time period (ms) 1

IC Applications LAB

Output - Triangular Amplitude (VP-P) (V) 10 Time period (ms) 1

Input sine wave Amplitude(VP-P) (V) 8 Time period (ms) 1 6

Output - cosine Amplitude (VP-P) (V) Time period (ms) 1

Differentiator

Input square wave Amplitude (VP-P) (V) 8 Time period (ms) 1

Output - Spikes Amplitude (VP-P) (V) 28 Time period (ms) 1

Input sine wave Amplitude (VP-P) (V) 8 Time period (ms) 1

Output - cosine Amplitude (VP-P) (V) 1.8 Time period (ms) 1

Model Calculations: Integrator: For T= 1 msec fa= 1/T = 1 KHz Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY fa = 1 KHz = 1/(2RfCf) Assuming Cf= 0.1f, Rf is found from Rf=1/(2faCf) Rf=1.59 K Rf = 10 R1 R1= 159 Differentiator For T = 1 msec f= 1/T = 1 KHz fa = 1 KHz = 1/(2RfC1) Assuming C1= 0.1f, Rf is found from R f=1/(2faC1) Rf=1.59 K fb = 10 fa = 1/2R1C1 for C1= 0.1f; R1 =159 Precautions: Check the connections before giving the power supply. Readings should be taken carefully.

IC Applications LAB

Result: For a given square wave and sine wave, output waveforms for integrator and differentiator are observed. Inferences: Spikes and triangular waveforms can be obtained from a given square waveform by using differentiator and integrator respectively.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY Questions & Answers:

IC Applications LAB

1. What are the problems of ideal differentiator? Ans: At high frequencies the differentiator becomes unstable and breaks into oscillation. The differentiator is sensitive to high frequency noise. 2. What are the problems of ideal integrator? Ans: The gain of the integrator is infinite at low frequencies. 3. What are the applications of differentiator and integrator? Ans: The differentiator used in waveshaping circuits to detect high frequency components in an input signal and also as a rate-of change detector in FM demodulators. The integrator is used in analog computers and analog to digital converters and signal-wave shaping circuits. 4. What is the need for Rf in the circuit of integrator? Ans: The gain of an integrator at low frequencies can be limited to avoid the saturation problem if the feedback capacitor is shunted by a resistance R f 5. What is the effect of C1 on the output of a differentiator? Ans: It is used to eliminate the high frequency noise problem.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

4. IC 741 Oscillator Circuits Phase Shift and Wien Bridge Oscillators

Aim:

To design (i) phase shift and (ii) Wien Bridge oscillators for the given frequency of oscillation

and verify it practically.

Apparatus required:

S.No 1 2 Equipment/Component name IC 741 Resistors Specifications/Value Refer page no 2 1.3 K,3.18 K 13K, ,31.8 K Variable Resistor 3 Capacitors 500 K pot 0.1 F 0.01 F 4 5 Regulated Power supply Cathode Ray Oscilloscope (0 30V),1A (0 -20MHz) Quantity 1 Each Three Each one 1 3 2 1 1

Theory:

The A741 is a high performance monolithic operational amplifier constructed using the planar epitaxial process. High common mode voltage range and absence of latch-up tendencies make the A741 ideal for use as voltage follower. The high gain and wide range of operating voltage provides superior performance in integrator, summing amplifier and general feedback applications. In the phase shift oscillator, out of 360o phase shift, 180o phase shift is provided by the op-amp and another 180o is by 3 RC networks. In the Weinbridge oscillator, the balancing condition of the bridge provides the total 360o phase shift.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Circuit Diagrams:

Fig 1 : RC Phase shift oscillator

Fig 2: Wien Bridge oscillator

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Design: 2. Phase shift oscillator

To design a phase shift oscillator with f o =500 Hz fo = 1/(2RC 6 ) and gain= RF/R1= 29 Assuming C = 0.1 F,the value of R is found from R = 1/ (2 foC 6 ) = 1.3 K

Take R1 = 10R =13 K RF = 29R1 (use 500K pot)

2. Wien bridge Oscillator

To design a Wien bridge oscillator with fo =5 KHz fo = 1/2RC and RF = 2R1 Assuming C = 0.01 F,the value of R is found from R= 1/2fc= 3.18 K Take R1 = 10 R=31.8 K RF = 2R1 (use 100K pot)

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Procedure: 1. Phase shift oscillator

1. Connect the circuit as per the circuit diagram shown in Fig 1 2. Observe the output waveform on the CRO. 3. Vary the potentiometer to get the undistorted waveform as shown Fig a. 4. Measure the time period and amplitude of the output waveform.

5.

Plot the waveforms on a graph sheet.

2. Wien bridge Oscillator

1. Connect the circuit as per the circuit diagram shown in Fig 2

2. Observe the output waveform on the CRO. 3. Vary the potentiometer to get the undistorted waveform as shown in Fig b 4. Measure the time period and amplitude of the output waveform. 5. Plot the waveforms on a graph sheet

Waveforms:

Fig (a): RC Phase Shift Oscillator Fig (b): Wien Bridge Oscillator Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Tabular form: 1. Phase shift oscillator:

S.No Amplitude(VP-P) Time period (ms) 1 20V 2.2 Practical frequency (Hz) 454 Theoretical frequency (Hz) 500

2. Wien bridge Oscillator:

S.No Amplitude(VP-P) Time period (ms) 1 20V 0.22ms Practical frequency (Hz) 4.545KHz Theoretical frequency (Hz) 5KHz

Precautions:

Check the connections before giving the power supply. Readings should be taken carefully.

Result:

RC phase shift and Wien bridge oscillators are designed and output shown in Fig (a) and (b). waveforms are observed as

Inferences:

Sinusoidal waveforms can be designed by using RC phase shift and Wien-Bridge oscillators.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Questions & Answers:

1 What is an oscillator? Ans: Oscillator is a circuit that generates a repetitive waveform of fixed amplitude and frequency without any external input signal. 2 How do you change the frequency of oscillation in RC phase shift and Wien bridge oscillators? Ans: By varying either resistor R or capacitor C values 3 What are the applications of oscillators? Ans: Oscillators are used in radio, television, computers, and communications 4 What is the advantage of using opamp in the oscillator circuit? Ans: Opamp is used to generate a variety of output wave forms. 5 How do you achieve fine variations in fo ? Ans: Fine variations in fo can be achieved by changing C value. 6 How do you achieve coarse variations in fo ? Ans: Coarse variations in fo can be achieved by changing R value

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

5. IC 555 Timer-Monostable Operation Circuit

Aim: To generate a pulse using Monostable Multivibrator by using IC555 Apparatus required:

S.No Equipment/Component name 1 2 3 4 5 6 555 IC Capacitors Resistor Regulated Power supply Function Generator Cathode ray oscilloscope Refer page no 6 0.1f,0.01f 10k (0 30V),1A (1HZ 1MHz) (0 20MHz) 1 Each one 1 1 1 1 Specifications/Value Quantity

Theory:

A Monostable Multivibrator, often called a one-shot Multivibrator, is a pulse-generating

circuit in which the duration of the pulse is determined by the RC network connected externally to the 555 timer. In a stable or stand by mode the output of the circuit is approximately Zero or at logic-low level. When an external trigger pulse is obtained, the output is forced to go high ( VCC). The time for which the output remains high is determined by the external RC network connected to the timer. At the end of the timing interval, the output automatically reverts back to its logic-low stable state. The output stays low until the trigger pulse is again applied. Then the cycle repeats. The Monostable circuit has only one stable state (output low), hence the name monostable. Multivibrator is low. Normally the output of the Monostable

Design:

Consider VCC = 5V, for given tp Output pulse width tp = 1.1 RA C Assume C in the order of microfarads & Find R A

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Circuit Diagram:

Fig1: Monostable Circuit using IC555

Typical values:

If C=0.1 F , RA = 10k then tp = 1.1 mSec Trigger Voltage =4 V

Procedure:

1. Connect the circuit as shown in the circuit diagram. 2. Apply Negative triggering pulses at pin 2 of frequency 1 KHz. 3. Observe the output waveform and measure the pulse duration. 4. Theoretically calculate the pulse duration as T high=1.1. RAC 5. Compare it with experimental values.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Waveforms:

Fig 2 (a): Trigger signal

(b): Output Voltage

(c): Capacitor Voltage

Sample Readings:

Trigger 0 to 5V range 1)1V,0.09msec Output wave 0 to 5V range 4.6V, 0.5msec Capacitor output 0 to 3.33 V range 3V, 0.88 msec

Precautions:

Check the connections before giving the power supply. Readings should be taken carefully.

Result: The input and output waveforms of 555 timer monostable Multivibrator are observed as shown

in Fig 2(a), (b), (c).

Inferences:

Output pulse width depends only on external components RA and C connected to IC555.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Questions & Answers:

1. Is the triggering given is edge type or level type? If it is edge type, trailing or raising edge? Ans: Edge type and it is trailing edge 2. What is the effect of amplitude and frequency of trigger on the output? Ans: Output varies proportionally. 3. How to achieve variation of output pulse width over fine and course ranges? Ans: One can achieve variation of output pulse width over fine and course ranges varying capacitor and resistor values respectively 4. What is the effect of Vcc on output? Ans: The amplitude of the output signal is directly proportional to Vcc 5. What are the ideal charging and discharging time constants (in terms of R and C) of capacitor voltage? Ans: Charging time constant T=1.1RC Sec Discharging time constant=0 Sec 6. What is the other name of monostable Multivibrator? Why? Ans: i) Gating circuit .It generates rectangular waveform at a definite time and thus could be used in gate parts of the system. ii) One shot circuit. The circuit will remain in the stable state until a trigger pulse is received. The circuit then changes states for a specified period, but then it returns to the original state. 7. What are the applications of monostable Multivibrator? Ans: Missing Pulse Detector, Frequency Divider, PWM, Linear Ramp Generator by

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

6. Schmitt Trigger Circuits- using IC 741 & IC 555

Aim: To design the Schmitt trigger circuit using IC 741 and IC 555 Apparatus required:

S.No 1 2 3 4 5 Equipment/Component name IC 741 555IC Cathode Ray Oscilloscope Multimeter Resistors 100 56 K 6 7 Capacitors Regulated power supply 0.1 f, 0.01 f (0 -30V),1A Specifications/Value Quantity Refer page no 2 Refer page no 6 (0 20MHz) 1 1 1 1 2 1 Each one 1

Theory:

The circuit shows an inverting comparator with positive feed back. This circuit converts orbitrary wave forms to a square wave or pulse. The circuit is known as the Schmitt trigger (or) squaring circuit. The input voltage Vin changes the state of the output Vo every time it exceeds certain voltage levels called the upper threshold voltage Vut and lower threshold voltage Vlt. When Vo= - Vsat, the voltage across R1 is referred to as lower threshold voltage, Vlt. When Vo=+Vsat, the voltage across R1 is referred to as upper threshold voltage Vut. The comparator with positive feed back is said to exhibit hysterisis, a dead band condition.

Circuit Diagrams:

Fig 1: Schmitt trigger circuit using IC 741

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Fig 2: Schmitt trigger circuit using IC 555

Design:

Vutp = [R1/(R1+R2 )](+Vsat) Vltp = [R1/(R1+R2 )](-Vsat) Vhy = Vutp Vltp =[R1/(R1+R2)] [+Vsat (-Vsat)]

Procedure: 1. 2. 3. 4.

Connect the circuit as shown in Fig 1 and Fig2. Apply an orbitrary waveform (sine/triangular) of peak voltage greater than UTP to the input of a Schmitt trigger. Observe the output at pin6 of the IC 741 and at pin3 of IC 555 Schmitt trigger circuit by varying the input and note down the readings as shown in Table 1 and Table 2 Find the upper and lower threshold voltages (Vutp, VLtp) from the output wave form. Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH, Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Wave forms:

Fig 3: (a) Schmitt trigger input wave form (b) Schmitt trigger output wave form

Sample readings: Table 1:

Parameter 741 Voltage( Vp-p) Time period(ms) 3.6 0.72 Input 555 4 1 741 24.8 0.72 Output 555 4.4 1

Table 2:

Parameter Vutp Vltp 741 0.2V -0.05 555 0.4V -0.4V

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Precautions:

Check the connections before giving the power supply. Readings should be taken carefully.

Results:

UTP and LTP of the Schmitt trigger are obtained by using IC 741 and IC 555 as shown in Table 2.

Inferences:

Schmitt trigger produces square waveform from a given signal.

Questions & Answers:

1. What is the other name for Schmitt trigger circuit? Ans: Regenerative comparator 2. In Schmitt trigger which type of feed back is used? Ans: Positive feedback. 3. What is meant by hysteresis? Ans: The comparator with positive feedback is said to be exhibit hysteresis, a deadband When the input of the comparator is exceeds Vutp, its back to its original state,+ condition.

output switches from + Vsat to - Vsat and reverts

Vsat ,when the input goes below Vltp

4. What are effects of input signal amplitude and frequency on output? Ans: The input voltage triggers the output every time it exceeds certain voltage levels (UTP and LTP). Output signal frequency is same as input signal frequency.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

7. Voltage Regulator using IC723

Aim: To design a low voltage variable regulator of 2 to 7V using IC 723. Apparatus required:

S.No 1 Equipment/Component name IC 723 Specifications/Value Refer appendix A 3.3K,4.7K,100 1K, 5.6K 0 -30 V,1A 3 digit display Quantity 1

2 3 4 5

Resistors Variable Resistors Regulated Power supply Multimeter

Each one Each one 1 1

Theory:

A voltage regulator is a circuit that supplies a constant voltage regardless of changes in load current and input voltage variations. Using IC 723, we can design both low voltage and high voltage regulators with adjustable voltages. For a low voltage regulator, the output VO can be varied in the range of voltages Vo < Vref, where as for high voltage regulator, it is VO > Vref. The voltage Vref is generally about 7.5V. Although voltage regulators can be designed using Op-amps, it is quicker and easier to use IC voltage Regulators.IC 723 is a general purpose regulator and is a 14-pin IC with internal short circuit current limiting, thermal shutdown, current/voltage boosting etc. Furthermore it is an djustable voltage regulator which can be varied over both positive and negative voltage ranges. By simply varying the connections made

externally, we can operate the IC in the required mode of operation. Typical performance parameters are line and load regulations which determine the precise characteristics of a regulator. The pin configuration and specifications are shown in the Appendix-A.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Circuit Diagram:

Fig1: Voltage Regulator

Design of Low voltage Regulator :Assume Io= 1mA,VR=7.5V RB = 3.3 K For given Vo R1 = ( VR VO ) / Io R2 = VO / Io

Procedure:

a) Line Regulation: 1. Connect the circuit as shown in Fig 1. 2. Obtain R1 and R2 for Vo=5V

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH, Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

3. By varying Vn from 2 to 10V, measure the output voltage Vo. 4. Draw the graph between Vn and Vo as shown in model graph (a) 5. Repeat the above steps for Vo=3V b) Load Regulation: For Vo=5V 1. Set Vi such that VO= 5 V 2. By varying RL, measure IL and Vo 3. Plot the graph between IL and Vo as shown in model graph (b) 4. Repeat above steps 1 to 3 for VO=3V.

Sample Readings:

a) Line Regulation: Vo set to 5V Vo set to 3V

Vi(V) 0 1 2 3 4 5 6 7 8 9

Vo(V) 0 0.65 0.66 1.23 2.68 3.40 4.13 4.90 5.33 5.33 5.33

Vi(V) 0 1 2 3 4 5 6 7 8 9 10

Vo(V) 0 0.65 0.69 1.05 1.42 1.80 2.19 2.57 2.81 2.81 2.81

10

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

a) Load Regulation:

Vo set to 5V

IL (mA) Vo(V) 2.81 2.81 2.81 2.81 2.81 2.81 2.81 2.81 2.81 2.81 2.81 2.81

Vo set to 3V

Vo(V)

24

IL (mA) 46 44 40 35 28 20 18 16 12 8 6 4 2

5.33

22

5.33

20

5.33

18

5.33

16

5.33 5.33 5.33 5.33 5.33 5.33 5.33 5.33 5.33

14 12 10 8 6 4 2

Model graphs: a) Line Regulation: b) Load Regulation:

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Precautions:

Check the connections before giving the power supply. Readings should be taken carefully.

Results:

Low voltage variable Regulator of 2V to 7V using IC 723 is designed. Load and Line Regulation characteristics are plotted.

Inferences:

Variable voltage regulators can be designed by using IC 723.

Questions & Answers:

1. What is the effect of R1 on the output voltage? Ans: R1 decreases for an increase in the output voltage. 2. What are the applications of voltage regulators? Ans: Voltage regulators are used as control circuits in PWM, series type switch mode supplies, regulated power supplies, voltage stabilizers. 3. What is the effect of Vi on output? Ans: Output varies linearly with input voltage up to some value (o/p voltage+ dropout voltage) and remains constant.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

8. Three Terminal Voltage Regulators- 7805, 7809, 7912

Aim:

To obtain the regulation characteristics of three terminal voltage regulators.

Apparatus required:

S.No 1 2 3 4 5 6 7 8 9

Equipment/Component Name Bread board IC7805 IC7809 IC7912 Multimeter Milli ammeter Regulated power supply Connecting wires Resistors pot

Specifications/Values

Quantity 1

Refer appendix A Refer appendix A Refer appendix A 3 digit display 0-150 mA 0-30 V 100 ,1k

1 1 1 1 1 1

Each one

Theory:

A voltage regulator is a circuit that supplies a constant voltage regardless of changes in load current and input voltage. IC voltage regulators are versatile, relatively inexpensive and are available with features such as programmable output, current/voltage boosting, internal short circuit current limiting, thermal shunt down and floating operation for high voltage applications. The 78XX series consists of three-terminal positive voltage regulators with seven voltage options. These ICs are designed as fixed voltage regulators and with adequate heat sinking can deliver output currents in excess of 1A.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

The 79XX series of fixed output voltage regulators are complements to the 78XX series devices. These negative regulators are available in same seven voltage options. Typical performance parameters for voltage regulators are line regulation, load regulation, temperature stability and ripple rejection. The pin configurations and typical parameters at 250C are shown in the Appendix-B.

Circuit Diagrams:

Fig 1: Positive Voltage Regulator

Fig 2: Negative Voltage Regulator

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Procedure: a) Line Regulation:

1. Connect the circuit as shown in Fig 1 by keeping S open for 7805. 2. Vary the dc input voltage from 0 to 10V in suitable stages and note down the output voltage in each case as shown in Table1 and plot the graph between input voltage and output voltage. 3. Repeat the above steps for negative voltage regulator as shown in Fig.2 for 7912 for an input of 0 to -15V. 4. Note down the dropout voltage whose typical value = 2V and line regulation typical value = 4mv for Vin =7V to 25V.

b) Load regulation:

1. Connect the circuit as shown in the Fig 1 by keeping S closed for load regulation. 2. Now vary R1 and measure current IL and note down the output voltage Vo in each case as shown in Table 2 and plot the graph between current IL and Vo. 3. Repeat the above steps as shown in Fig 2 by keeping switch S closed for negative voltage regulator 7912.

c) Output Resistance:

Ro= (VNL VFL) IFL

VNL VFL IFL -

load voltage with no load current load voltage with full load current full load current.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Sample readings: a) Line regulation

1) IC 7805 Input Voltage Vi,(V) 0 5 6 7 10 Output Voltage Vo(V) 0 4.05 4.86 5 5

b) Load Regulation

1) IC 7805 Load Current IL(mA) 44 40 30 20 16 8 Output Voltage Vo(V) 5 5 5 4.98 4.97 4.96

2) IC 7809

2) IC 7809

Load Current Input Voltage Vi,(V) 0 5 10 12 14 Output Voltage Vo(V) 0 48 7.4 33 8.7 25 9 21 9 15 IL(mA) 56

Output Voltage Vo(V) 9 9 9 8.96 8.82 8.60

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

3)7912

3) IC 7912

Load Current Input Voltage Vi,(V) 0 -10 -12 -14 -15 Output Voltage Vo(V) 0 -9.59 -11.59 -12 -12 IL(mA) 56 46 38 28 24 20

Output Voltage Vo(V) -12.09 -12.09 -12.07 -12.06 -11.98 -11.80

Graphs:

IC 7805

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

IC 7809

IC7912

% load regulation = VNL - VFL x 100 VFL

Precautions:

Check the connections before giving the power supply. Readings should be taken carefully.

Result:

Line and load regulation characteristics of 7805, 7809 and 7912 are plotted Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH, Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Inferences:

Line and load regulation characteristics of fixed positive and negative three terminal voltages are obtained. These voltage regulators are used in regulated power supplies.

Questions & Answers:

1. Mention the IC number for a negative fixed three terminal voltage regulator of 12V. Ans: IC 7912 2. Explain the significance of IC regulators in power supply Ans: To get constant dc voltages. 3. What is drop-out voltage? Ans: The difference between input and output voltages is called dropout voltage 4. What is the role of C1 and C2? Ans: C1 is used to cancel the inductive effects. C2 is used to improve the transient response of regulator. 4. What are C1 and C2 called? Ans: Bypass capacitors

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

APPENDIX-A IC723

Pin Configuration

Specifications of 723:

Power dissipation Input Voltage Output Voltage : Output Current : : : 1W 9.5 to 40V

2 to 37V 150mA for Vin-Vo = 3V 10mA for Vin-Vo = 38V

Load regulation : Line regulation :

0.6% Vo 0.5% Vo

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

APPENDIX-B

Pin Configurations: 78XX 79XX

Plastic package

Typical parameters at 25oC:

Parameter Vout,V Imax,A Load Reg,mV Line Reg,mV Ripple Rej,dB Dropout Rout,m ISL,A LM 7805 5 1.5 10 3 80 2 8 2.1 LM 7809 9 1.5 12 6 72 2 16 0.45 LM 7912 -12 1.5 12 4 72 2 18 1.5

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

REFERENCES

1. D.Roy Choudhury and Shail B.Jain, Linear Integrated Circuits, 2 nd edition, New Age International. 2. James M. Fiore, Operational Amplifiers and Linear Integrated Circuits: Theory and Application, WEST. 3. Malvino, Electronic Principles, 6th edition, TMH 4. Ramakant A. Gayakwad, Operational and Linear Integrated Circuits,4 th edition, PHI. 5. Roy Mancini, OPAMPs for Everyone, 2nd edition, Newnes. 6. S. Franco, Design with Operational Amplifiers and Analog Integrated Circuits, 3rd edition, TMH. 7. William D. Stanley, Operational Amplifiers with Linear Integrated Circuits, 4 th edition, Pearson. 8. www.analog.com

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

PART 2 DICA LAB

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

1. D Flip Flop-IC 7474

Aim: To verify the truth table of D Flip Flop-IC 7474 Apparatus :1. D flip-flops Trainer Kit. 2. Set of Patch chords. D-Flip -Flop:

D-flip-flop using Nand gates :

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

TRUTH TABLE:

Procedure: 1. Connect S, R and D terminal to the logic input switches. 2. Connect the clock terminals to bounceless pulser high or low. 3. Connect Q and Q terminals to logic output indicators. 4. Set the S, R and D signals by means of the switches as per TruthTable3. Verify the Q and Q outputs.

Result: Verified the truth tables of D Flip-Flops.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

2. DECADE COUNTER 74LS90

Aim: To construct and verify the working of a single digit decade counter using IC 7490. Apparatus: 1) IC7490 Decade counter kit 2) Connecting patch cards. Circuit Diagram:-

FIGURE 1

Procedure: 1. Wire the circuit diagram shown in figure 1. 2. Connect the 1Hz clock to pin CPO.(14) 3. Connect the reset terminals (MR1 & MR2) to high and set terminals (MS1 & MS2) to zero and observe the output. 4. Now connect set and reset inputs to zero and observe the outputs. 5. Record the counter states for each clock pulse. 6. Design mod 6 counter using IC 7490 as shown in fig 2. 7. Record the counter states for each clock pulse. 8. Now Construct decade counter using J K F/Fs and record the counter states

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

MOD 6 COUNTERS:

Truth Table:-

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Result: - Verified the working of a single digit decade counter using IC 7490.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

3. UNIVERSAL SHIFT REGISTER-74LS194

Aim: - To study the following applications of the Universal shift register using IC 74194. a. Shift Right Logic b. Shift Left Logic c. Parallel Load

Apparatus:1. Universal Shift Register using IC 74194 Trainer boards. 2. 5v fixed DC power supply.

Circuit Diagram:-

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Procedure:STEP: 1. MASTER RESET Set the inputs as below and observe the out puts as per table 1

A logic 0 on MR resets all outputs to logic 0 irrespective of other inputs. STEP: 2 PARALLEL LOAD In this step we load the data parallel. Set the inputs as below and observe the outputs.

Here when S1 & S0 are both logic 1 the input data is transferred parallely to output at the clock positive transition change the input data and observe the change at the output . STEP: 3. SHIFT LEFT LOGIC 0 . Set Q0, Q1, Q2, Q3 to 1 1 1 1 by putting DSL to Logic 1 . While running the above step, change the logic input DSL to logic 0 And S0 to logic 0 in the same sequence .Observe the following outputs after each clock pulse and verify .

In the sequence 4 clock pulses logic o s are shifted left successively with each clock pulse . STEP: 4. SHIFT LEFT LOGIC 1 S Set the Q0 Q1 Q2 Q3 to 0 0 0 0 by setting DSL input to logic 0 .

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH, Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Now switch DSL input to logic 1 and observe the shifting of logic 1 s to left as below . Observe the following outputs after each clock pulse and verify.

STEP: 5 . SHIFT RIGHT LOGIC 0 Set the Q0 Q1 Q2 Q3 to 1 1 1 1 by setting DSR input to logic 1 . Repeat step 4 and parallel load logic 1s in all the 4 outputs. Change the logic inputs of DSR to logic 0 and then of S1 to logic 0 in the same sequence. Observe the following outputs after each clock pulse and verify.

STEP: 6 SHIFT RIGHT LOGIC 1s Now at this condition of all 0 at the outputs switch DSR to logic 1 this will enable all logic as serial data and logic 1 s will be shifted successively with each clock pulse as shown below . Observe the following table and verify the outputs .

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

STEP: 7. In the above steps for shift left or shift right operation ,(step 3 4 5 6 ) if both the S0 &S1 switches are forced to logic 0 , then shifting operation will cease and whatever is the output data it will freeze or hold. Observe this condition and verify.

Result:- Verified the applications of the Universal shift register using IC 74194

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

4. 3 TO 8 DECODER-74LS138

Aim: To verify operation of the 3 to 8 decoder using Ic 74138. Apparatus: 1) 3 to 8 decoder Ic 74138 kit. 2) Patch chords. Theory: A decoder is a combinational circuit that connects the binary information from n input lines to a maximum of 2 n unique output lines .The IC 74138 accepts three binary inputs and when enable provides 8 individual active low outputs. The device has 3 enable inputs .Two active low and one active high. Circuit Diagram

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Logic Diagram:

Procedure :1. Make the connections as per the circuit diagram . 2. Change the values of G1,G2A,G2B,A,B,and C, using switches. 3. Observe status of Y0, to Y7 on LEDs. 4. Verify the truth table.

Result:- Verified the Operation of 3 to 8 Decoder.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY 5. 4 BIT COMPARATOR

IC Applications LAB

Aim:- To study the operation of 4-bit Magnitude Comparator using Ic7485.

Apparatus :- 1 . Power supply. 2. IC7485 4-bit Comparator kit. Theory :Magnitude Comparator is a logical circuit , which compares two signals A and B and generates three logical outputs, whether A > B, A = B, or A < B . IC 7485 is a high speed 4-bit Magnitude comparator, which compares two 4-bit words. The A = B Input must be held high for proper compare operation.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Procedure:1. Connect the circuit as shown in fig. Feed the 4-bit binary words A0, A1 , A2 , A3 and B0 , B1, B2 , B3 .from the logic input switches. 2. Pin 3 of IC 7485 should be at logic 1 to enable compare operation. 3. Observe the output A>B, A=B , and A<B on logic indicators. The outputs must be 1 or 0 respectively. 4. Repeat the steps 1 ,2 and 3 for various inputs A0 ,A1 , A2 , A3 and B0 , B1 , B2 , B3 and observe the outputs at A>B , A=B and A<B .

Result:- Verified the operation of 4-bit magnitude comparator using IC 7485 .

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

6. 8:1 Multiplexer 74151

Aim: To verify the truth table of a given 8 to 1 Multiplexer and 1 to 8 De-Multiplexer using IC 74151 and 74138 . Apparatus: 1. 8 to 1 Multiplexer Trainer kit . 2. Connecting patch chords. Theory: Multiplexer means many to one. A multiplexer is a circuit with many inputs but only one output. By using control signals (select lines ) we can select any input to the output. Multiplexer is also called as data selector because the output bit depends on the input data bit that is selected. The general idea about the multiplexing the circuit has N input signals, M control signals and 1 output signal.8 X 1 Multiplexer has 8 input signals and one output signal, three data control or select lines. These data control lines are nothing but 3-bit binary code on the data control signal inputs which will allow the data on the corresponding data input to pass through to the data output.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Logic Diagram:

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Procedure: 1. Switch on the trainer by connecting power chord to the AC mains 2. By using pulsar switch reset the control signals (Q2 Q1 Q0 ) to 0 0 0 3. Connect the output terminals (pin 5) to the output LEC indicator. 4. Apply logic 1 to I0 input (pin 4) by using the switch. The output LED indicator glows 5. Apply logic 0 to I0 input (pin 4) by using the switch. The output LEC indicator is off. 6. Verify the truth table by changing the control 3 signal states using pulsar switch from 000 to 111

Result: The truth table of 8 to 1 multiplexer has been verified.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

7. RAM (164) - IC 7489

Aim: -To study the operation of the RAM Ic7489. Apparatus: 1. RAM IC 7489 Trainer kits. 2. Connecting wires. Pin Diagram: -

Operation: RAM IC 7489 is 16 words x 4-bit Read/WriteMemory. The Truth Table for the RAM IC 7489 is given below.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

The memory Enable pin is used to select 1- of-n ICs i.e. like a Chip Select signal. For simply city, the memory enable pin is permanently held low. The address lines are given through an up /down counter with preset capability. The set address switch is held high to allow the user choose any location in the RAM, using the address bits. The address and data bits are used to set an address and enter the data. The Read/Write switch is used to write data on to the RAM. Procedure: This experiment has 3 stages Clearing the memory, data entry (Write operation) and data verification (Read operation). Clearing the Memory: -The RAM IC 7489 is a volatile memory. This means that it will lose the data stored in it, on loss of power. However, this dose not means that the content of the memory becomes 0h, but not always. The RAM IC 7489 does not come with a Clear Memory signal. The memory has to be cleared manually. 1. Position the Stack/Queue switch in the Queue position. 2. Position the Set Address switch in the 1 position. 3. Set the address bits to 0h (first byte in the memory) 4. Position the Set Address switch in the 0 position to disable random access and enable the counter. 5. Position the Read/Write switch in the Write position to write data on to the memory. 6. Set the data bits to 0h (clearing the content) 7. Observe that the LEDs (D3 to D0) glow. This is to indicate that the content is 0h. Refer the truth table above and observe that the data outputs of the RAM will be compliments of the data inputs. 8. Position the Increment/Decrement switch in the Increment position. 9. Press the Clock to increment the counter to the next address. As the Read /Write switch is already in the Write position, and the data bits are set to the 0h, the content in the new location is also replaced with 0h.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Write Operation: 1. Assume that the following data has to be written on to the RAM. The address and data are given in the hexadecimal format.

2. Position the Stack/Queue switch in the Queueposition. 3. Position the Read/Write switch in the Write position to enable the entry of data in to the RAM. 4. Position the Set Address switch in the 1 position to allow random access of memory. 5. Set the desired address (any address at random) using the address bit switches. 6. Set the desired data (refer table for the data to be entered in each location) using the data bit switches. 7. Observe that the data is indicated by the LEDs (D3 toD0). This is because the data is written on to the RAM. 8. Also observe that the data is indicated by the data outputs is the compliment of the data input (refer truth table condition ME =L and WE=L) .

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

9. After each data entry, make a note of the location where data is entered. This is to make sure that we are not re entering data in the same location. 10. Repeat steps 4 and 5 until data has been entered in all the addresses listed in the above table 11. Position the Read/Write switch in the Read position, to disable data entry. 12. This completes data entry. Read Operation: 1. Position the Stack/Queue switch in the Queue position. 2. Position the Set Address switch in the 0 position to allow random access of memory. 3. Position Read/Write switches in the Read position, to disable unauthorized entry of data. 4. Set the desired address (any address at random). 5. Observe that the data entered in the location is indicated by the LEDs (D3 toD0). This is because the data was written during the data entry procedure. 6. Also observe that the data indicated by the data out puts is the compliment of the data input (refer truth table condition ME=L and WE=H).

Result: - Operation of the RAM Ic7489 has been verified.

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

8. 4 BIT COMPARATOR 74LS85

Aim:- To study the operation of 4-bit Magnitude Comparator using Ic7485. Apparatus: - 1 . Power supply. 2. IC7485 4-bit Comparator kit. Theory:Magnitude Comparator is a logical circuit, which compares two signals A and B and generates three logical outputs, whether A > B, A = B, or A < B . IC 7485 is a high speed 4-bit Magnitude comparator, which compares two 4-bit words. The A = B Input must be held high for proper compare operation.

CIRCUIT DIAGRAM:

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

ANNAMACHARYA INSTITUTE OF SCIENCE AND TECHNOLOGY

IC Applications LAB

Procedure:1. Connect the circuit as shown in fig. Feed the 4-bit binary words A0, A1 , A2 , A3 and B0 , B1, B2 , B3 from the logic input switches. 2. Pin 3 of IC 7485 should be at logic 1 to enable compare operation. 3. Observe the output A>B, A=B , and A<B on logic indicators. The outputs must be 1 or 0 respectively. 4. Repeat the steps 1 ,2 and 3 for various inputs A0 ,A1 , A2 , A3 and B0 , B1 , B2 , B3 and observe the outputs at A>B , A=B and A<B .

Verification Table

Result:- Verified the operation of 4-bit magnitude comparator using IC 7485 .

Prepared By SURESH BABU M Asst.Prof ,ECE Dept.,AITH,

Cont No.+91-80992 28247

You might also like

- ECD Lab EEC 752Document17 pagesECD Lab EEC 752juhi99360% (5)

- Programmable Logic Devices 2, TutorialDocument10 pagesProgrammable Logic Devices 2, Tutorialindresh.verma100% (1)

- UNIT V Digital Integrated Circuits Introduction Part IIDocument135 pagesUNIT V Digital Integrated Circuits Introduction Part IINayab Rasool SK100% (1)

- LIC Manual NewDocument84 pagesLIC Manual NewVandhana PramodhanNo ratings yet

- Electronics Circuits Lab ManualDocument109 pagesElectronics Circuits Lab ManualIndische Mädchen100% (2)

- Lab ManualDocument66 pagesLab ManualcommunicationridersNo ratings yet

- Digital Electronics Lab ManualDocument93 pagesDigital Electronics Lab ManualAnoop MathewNo ratings yet

- Design A RC Coupled CE Transistor AmplifierDocument7 pagesDesign A RC Coupled CE Transistor AmplifierSudeep Nayak100% (1)

- Lab ManualDocument19 pagesLab ManualSanthi SriNo ratings yet

- Digital Logic Design Lab ManualDocument55 pagesDigital Logic Design Lab ManualEngr Zaryab WarraichNo ratings yet

- Amplifier 1Document37 pagesAmplifier 1Pawan VermaNo ratings yet

- Chapter 11 Laboratory ExperimentDocument102 pagesChapter 11 Laboratory ExperimentMrinal TakNo ratings yet

- Mirror AdderDocument51 pagesMirror AdderjeevanprsdNo ratings yet

- Non-Inverting Operational Amplifier ConfigurationDocument10 pagesNon-Inverting Operational Amplifier ConfigurationMirHaiderAliShaurov100% (1)

- EI2353-Digital System DesignDocument13 pagesEI2353-Digital System DesignSanthosh KumarNo ratings yet

- Unit 2 Transistors Opamp: December 17, 2021 1Document73 pagesUnit 2 Transistors Opamp: December 17, 2021 1Abhishek SataleNo ratings yet

- Ac Lab CompleteDocument50 pagesAc Lab CompletePraveen ChittiNo ratings yet

- 1.circuits and Simulation Integrated Laboratory 2013 RegulationDocument46 pages1.circuits and Simulation Integrated Laboratory 2013 RegulationNandha KumarNo ratings yet

- MicrosequencerDocument38 pagesMicrosequencerJonathan MejiaNo ratings yet

- Dr. N.G.P. Institute of Technology - Coimbatore-48: Analog and Digital Integrated CircuitsDocument48 pagesDr. N.G.P. Institute of Technology - Coimbatore-48: Analog and Digital Integrated CircuitsMrs.S.Divya BMENo ratings yet

- Cmos Analog Ic Design Course Plan NewDocument9 pagesCmos Analog Ic Design Course Plan Newjim2001No ratings yet

- EI2353 DSDQbankDocument24 pagesEI2353 DSDQbankRaja RockNo ratings yet

- Linear Integrated Circuits Lab ManualDocument50 pagesLinear Integrated Circuits Lab Manuals989403590391% (11)

- EC2257-Lab Manual For Circuits and Simulation Integrated LaboratoryDocument38 pagesEC2257-Lab Manual For Circuits and Simulation Integrated Laboratorygokila_dr9897No ratings yet

- Logic Gates & AmplifiersDocument103 pagesLogic Gates & AmplifiersAnusha NatarajanNo ratings yet

- Circuits and Simulation Lab ManualDocument99 pagesCircuits and Simulation Lab Manualkasim_1983No ratings yet

- Lab Manual ElectronicsDocument57 pagesLab Manual ElectronicsNaveen Rockzz Bhavans100% (2)

- Digital Logic Design Lab Manual: Department of Electrical Engineering, Fast-Nu, LahoreDocument115 pagesDigital Logic Design Lab Manual: Department of Electrical Engineering, Fast-Nu, LahoreQasim LodhiNo ratings yet

- Vtu 3RD Sem Cse Logic Design Notes 10CS33Document63 pagesVtu 3RD Sem Cse Logic Design Notes 10CS33EKTHATIGER633590100% (3)

- Lecture 5 - Climper and Clamper CircuitDocument22 pagesLecture 5 - Climper and Clamper CircuitArifah HamidunNo ratings yet

- Electronic Devices and Circuit Theory: Operational AmplifiersDocument26 pagesElectronic Devices and Circuit Theory: Operational AmplifiersLarry CubillasNo ratings yet

- Frequency Response of Two Stage RC Coupled AmplifierDocument38 pagesFrequency Response of Two Stage RC Coupled AmplifierAyesha Gupta100% (2)

- Basic Electronics LabDocument60 pagesBasic Electronics Labrahulsingle67% (3)

- Digital Electronics Lab Manual PDFDocument94 pagesDigital Electronics Lab Manual PDFRamkumar Sivakaminathan50% (2)

- LIC Lab ManualDocument65 pagesLIC Lab ManualBala Subramanian0% (1)

- EE3706 - Chapter 5 - Operational AmplifiersDocument34 pagesEE3706 - Chapter 5 - Operational AmplifiersQuang Huy Doan NgocNo ratings yet

- Study Gates, Flip-Flops LabDocument51 pagesStudy Gates, Flip-Flops Labsudipta2580No ratings yet

- Computer OrganizationDocument396 pagesComputer Organizationkanaka raghu sreeramaNo ratings yet

- Parallel ResonanceDocument14 pagesParallel ResonanceSubhuNo ratings yet

- 16 Micro-Programmed ControlDocument36 pages16 Micro-Programmed ControlJohn Paul Cordova100% (1)

- Analog Electronics Course OverviewDocument36 pagesAnalog Electronics Course OverviewcooljseanNo ratings yet

- Multiplier & Divider Questions and Answers - SanfoundryDocument5 pagesMultiplier & Divider Questions and Answers - SanfoundryHarith Nawfel100% (1)

- LIC FLEXI Lab Manual Second Experiment Student Copy-3Document5 pagesLIC FLEXI Lab Manual Second Experiment Student Copy-3Vignesh RamakrishnanNo ratings yet

- MALVINO & BATES Chapter 08Document29 pagesMALVINO & BATES Chapter 08Reece RevosaNo ratings yet

- Semiconductor Device ModellingDocument39 pagesSemiconductor Device ModellingBiswajit Behera100% (1)

- Practical Signal ProcessingDocument30 pagesPractical Signal ProcessingLokender TiwariNo ratings yet

- STLD Lab Manual ExperimentsDocument42 pagesSTLD Lab Manual ExperimentssaikiranNo ratings yet

- Introduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationFrom EverandIntroduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationNo ratings yet

- Millimicrosecond Pulse Techniques: International Series of Monographs on Electronics and InstrumentationFrom EverandMillimicrosecond Pulse Techniques: International Series of Monographs on Electronics and InstrumentationNo ratings yet

- Ica Lab NewDocument105 pagesIca Lab Newveeru57No ratings yet

- AKNM - 4047 - AKNMGptcDocument70 pagesAKNM - 4047 - AKNMGptcVIKASH YADAVNo ratings yet

- AKNM - 4047--AKNMGptc (1)Document70 pagesAKNM - 4047--AKNMGptc (1)asmitaingale0808No ratings yet

- Control Systems and Simulation LabDocument91 pagesControl Systems and Simulation Labkiran_y2No ratings yet

- Lica Lab ManualDocument95 pagesLica Lab ManualPavan PakkiNo ratings yet

- Analog Circuits Lab Manual: Atria Institute of TechnologyDocument60 pagesAnalog Circuits Lab Manual: Atria Institute of TechnologyTháHäKâduvàyîLzNo ratings yet

- QoS-based Power Allocation for Cellular Networks using MATLABDocument36 pagesQoS-based Power Allocation for Cellular Networks using MATLABnandakishore.nallaNo ratings yet

- Resource Allocation With Frequency Reuse Using MatlabDocument31 pagesResource Allocation With Frequency Reuse Using Matlabnandakishore.nallaNo ratings yet

- MATLAB Communications Major Project ListDocument1 pageMATLAB Communications Major Project Listnandakishore.nallaNo ratings yet

- Factors Affecting Consumer Behaviour in the Telecom IndustryDocument6 pagesFactors Affecting Consumer Behaviour in the Telecom Industrynandakishore.nallaNo ratings yet

- MOSEK Licensing Guide: Release 9.3.20Document31 pagesMOSEK Licensing Guide: Release 9.3.20nandakishore.nallaNo ratings yet

- Electrical Final Scedule FinalDocument6 pagesElectrical Final Scedule Finalnandakishore.nallaNo ratings yet

- ABCD RULE Maliganat and MelonomaDocument3 pagesABCD RULE Maliganat and Melonomanandakishore.nallaNo ratings yet

- Joint Routing and Resource Allocation For Millimeter Wave Picocellular BackhaulDocument13 pagesJoint Routing and Resource Allocation For Millimeter Wave Picocellular Backhaulnandakishore.nallaNo ratings yet

- Chapter-2 Laplace Transform: Definition of The Laplace TransformationDocument15 pagesChapter-2 Laplace Transform: Definition of The Laplace Transformationnandakishore.nallaNo ratings yet

- Optimal Cooperative Data Transmission Over SC-FDMA Channel Estimation On LTE-A Based NetworksDocument3 pagesOptimal Cooperative Data Transmission Over SC-FDMA Channel Estimation On LTE-A Based Networksnandakishore.nallaNo ratings yet

- G. Sayanna EthiopiaDocument3 pagesG. Sayanna Ethiopianandakishore.nallaNo ratings yet

- Binder MulticarreirDocument5 pagesBinder MulticarreirjobinvcmNo ratings yet

- Chapter - 3: Elements of Realiazability Theory: Requirements Is Called Network SynthesisDocument4 pagesChapter - 3: Elements of Realiazability Theory: Requirements Is Called Network Synthesisnandakishore.nallaNo ratings yet