Professional Documents

Culture Documents

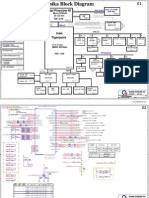

Mini2440 Schematic

Uploaded by

ajeezaecCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Mini2440 Schematic

Uploaded by

ajeezaecCopyright:

Available Formats

1

D CPU1 01-CPU1.Sch

CPU2 02-CPU2.Sch

CPU3 03-CPU3.Sch

SDRAM 04-MEM.sch

C UART_USB_ETC 05-UART_USB_POWER.sch

mini2440

Audio 06-Audio.sch

DM9000 07-DM9000.sch

Interface 08-INTERFACE.sch

A Title Size B Date: File: 1 2 3 4 5 11-Oct-2008 C:\mini2440\mini2440 .ddb Sheet of Drawn By: 6

Number Revision

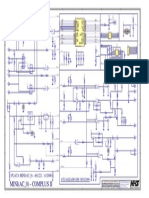

D R64 4.7K BUS BUS

OM0

D VDD33V

NORBOOT

S2 1 2 3 4 5 CON5

nXDACK0 nLED_3 nXDREQ0 nLED_4

K2 nLED_1 L5 nLED_2 F6 nGCS0 B2 nGCS1 C3 nGCS2 C4 nGCS3 D3 nLAN_CS C2 nGCS5 C5 LnOE E4 nWAIT E6 LnWE T15 R13

1 2 3

J1 CON3

OM0

NOR FLASH, BIOS NAND FLASH,

C5 15p

NANDBOOT

R35

4.7K U1A

L3 K7 K6 K5

XTIpll

X2 12M

C6 15p

XTOpll

nXDACK0/GPB9 nXDACK1/GPB7 nXDREQ0/GPB10 nXDREQ1/GPB8

nXBACK/GPB5 nXBREQ/GPB6 nGCS0 nGCS1/GPA12 nGCS2/GPA13 nGCS3/GPA14 nGCS4/GPA15 nGCS5/GPA16 nOE nWAIT nWE OM0 OM1

ADC

Clock EXYCLK CLKOUT0/GPH9 CLKOUT1/GPH10 MPLLCAP UPLLCAP OM2 OM3 XTIpll XTOpll XTIrtc XTOrtc

TOUT0/GPB0 TOUT1/GPB1 TOUT2/GPB2 TOUT3/GPB3 TCLK0/GPB4 TCLK1/EINT19/GPG11

LADDR0 LADDR1 LADDR2 LADDR3 LADDR4 LADDR5 LADDR6 LADDR7 LADDR8 LADDR9 LADDR10 LADDR11 LADDR12 LADDR13 LADDR14 LADDR15 LADDR16 LADDR17 LADDR18 LADDR19 LADDR20 LADDR21 LADDR22 LADDR23 LADDR24 LADDR25

AIN0 AIN1 AIN2 AIN3 AIN4/TSYM AIN5/TSYP AIN6/TSXM AIN7/TSXP Aref

F7 E7 B7 F8 C7 D8 E8 D7 G8 B8 A8 C8 B9 H8 E9 C9 D9 G9 F9 H9 D10 C10 H10 E10 C11 G10 D11

ADDR/GPA0 ADDR1 ADDR2 ADDR3 ADDR4 ADDR5 ADDR6 ADDR7 ADDR8 ADDR9 ADDR10 ADDR11 ADDR12 Address ADDR13 ADDR14 ADDR15 ADDR16 ADDR17 ADDR18 ADDR19 ADDR20 ADDR21 ADDR22 ADDR23 ADDR24 ADDR25 ADDR26

DMA

Chip Select

S3C2440 Data

Timer

DATA0 DATA1 DATA2 DATA3 DATA4 DATA5 DATA6 DATA7 DATA8 DATA9 DATA10 DATA11 DATA12 DATA13 DATA14 DATA15 DATA16 DATA17 DATA18 DATA19 DATA20 DATA21 DATA22 DATA23 DATA24 DATA25 DATA26 DATA27 DATA28 DATA29 DATA30 DATA31

D12 C12 E11 A13 F10 F11 C13 A14 D13 B15 A17 C14 D15 C15 D14 B17 C16 E15 E14 E13 E12 E16 F15 G13 E17 G12 F14 F12 G11 G16 H13 F13

LDATA0 LDATA1 LDATA2 LDATA3 LDATA4 LDATA5 LDATA6 LDATA7 LDATA8 LDATA9 LDATA10 LDATA11 LDATA12 LDATA13 LDATA14 LDATA15 LDATA16 LDATA17 LDATA18 LDATA19 LDATA20 LDATA21 LDATA22 LDATA23 LDATA24 LDATA25 LDATA26 LDATA27 LDATA28 LDATA29 LDATA30 LDATA31

22p

XTIrtc

C1

X1 32.768kHz

XTOrtc

C2 22p

S3C2440X H12 R9 P10 N14 P17 P13 T13 G14 G15 M14 L12

CLKOUT0 CLKOUT1 MPLLCAP UPLLCAP

R14 U17 R15 P15 T16 T17 R16 P16 U16

VDD33V VDD33V R68 4.7K

MPLLCAP UPLLCAP

GPB0 GPB1 L3MODE L3DATA L3CLOCK EINT19

AIN0 AIN1 AIN2 AIN3 TSYM TSYP TSXM TSXP

XTIpll XTOpll XTIrtc XTOrtc

J6 J5 J7 K3 K4 U12

C40 2n7

C41 680p

A Title Size B Date: File: 1 2 3 4 5 11-Oct-2008 C:\mini2440\mini2440 .ddb Sheet of Drawn By: 6

Number Revision

VDD33V

NR1 10K

NCON GPG13 GPG14 GPG15

NR2 10K

NR3 10K

NR4 10K

D GPIO_IO GPIO_IO GPIO_IO GPIO_IO GPIO_IO GPIO_IO GPIO_IO GPIO_IO GPIO_IO GPIO_IO

1K NR5

1K NR8

I2SLRCK I2SSCLK CDCLK I2SSDI I2SSDO

SPIMISO EINT13 SPIMOSI EINT14 SPICLK EINT15 nSS_SPI EINT11

I2CSCL I2CSDA

P12 N11 N12 U14

P7 R7 T7 L8 U6

M10 T11 L11 U13

U8 M9

K9 K10 P9 R11 L9 L10 J10 R10

LSCLK1 LnSRAS LnSCAS LSCKE

1 2 3 4

22

8 7 6 5

LLSCLK1 LLnSRAS LLnSCAS LLSCKE

DN0 DP0 PDN0 PDP0

RA7

EINT20 GPG13 GPG14 GPG15

VDD33V U1B

R17 10K R22 10K

SPIMISO0/GPE11 SPIMISO1/EINT13/GPG5 SPIMOSI0/GPE12 SPIMOSI1/EINT14/GPG6 SPICLK0/GPE13 SPICLK1/EINT15/GPG7 nSS0/EINT10/GPG2 nSS1/EINT11/GPG3

LLSCLK0 LLnSCS0

R55 22 R63 22

LSCLK0 LnSCS0 LnWBE0 LnWBE1 LnWBE2 LnWBE3 LLnSCS0 LLnSCAS LLnSRAS LLSCKE LLSCLK0 LLSCLK1 ALE CLE RnB NCON nFCE nFRE nFWE SDCLK SDCMD SDDATA0 SDDATA1 SDDATA2 SDDATA3

D4 B5 D5 E5 D2 E3 D6 C6 A2 B4 B3 D1 F5 G6 R12 F4 E1 F3 N8 K8 R8 M8 P8 J9

nBE0:nWBE0:DQM0 nBE1:nWBE1:DQM1 nBE2:nWBE2:DQM2 nBE3:nWBE3:DQM3 nGCS6:nSCS0 IIC nGCS7:nSCS1 nSCAS nSRAS SDRAM SCKE SCLK0 SCLK1

I2SLRCK/GPE0 I2SSCLK/GPE1 CDCLK/GPE2 I2SSDI/nSS0/GPE3 I2SSDO/I2SSDI/GPE4

EINT20/GPG12 EINT21/GPG13 EINT22/GPG14 EINT23/GPG15

IICSCL/GPE14 IICSDA/GPE15

DN0 DP0 DN1/PDN0 DP1/PDP0

USS

IIS

SPI

ALE/GPA18 CLE/GPA17 FRnB NAND CTRL NCON nFCEGPA22 nFRE/GPA20 nFWE/GPA19 SDCLK/GPE5 SDCMD/GPE6 SDIO SDDATA0/GPE7 SDDATA1/GPE8 SDDATA2/GPE9 SDDATA3/GPE10

LCD DATA LCD CTRL UART LEND/GPC0 VCLK/GPC1 VLINE:HSYNC/GPC2 VFRAME:VSYNC/GPC3 VM:VDEN/GPC4 LCD_LPCOE/GPC5 LCD_LPCREV/GPC6 LCD_LPCREVB/GPC7 LCD_PWREN/EINT12/GPG4

VD0/GPC8 VD1/GPC9 VD2/GPC10 VD3/GPC11 VD4/GPC12 VD5/GPC13 VD6/GPC14 VD7/GPC15 VD8/GPD0 VD9/GPD1 TSP VD10/GPD2 VD11/GPD3 VD12/GPD4 VD13/GPD5/USBTXDN1 VD14/GPD6/USBTXDP1 VD15/GPD7/USBOEN1 VD16/GPD8/SPIMISO1 VD17/GPD9/SPIMOSI1 VD18/GPD10/LPICLK1 VD19/GPD11/USBRXDP1 VD20/GPD12/USBRXDN1 VD21/GPD13/USBRXD1 VD22/nSS1/GPD14 VD23/nSS0/GPD15

N2 L6 N4 R1 N3 P2 M6 P3 R2 M5 N5 R3 P4 R4 P5 N6 M7 T4 R5 T5 P6 R6 N7 U5

VD0 VD1 VD2 VD3 VD4 VD5 VD6 VD7 VD8 VD9 VD10 VD11 VD12 VD13 VD14 VD15 VD16 VD17 VD18 VD19 VD20 VD21 VD22 VD23

EINT19 EINT15 EINT14 EINT13 EINT11 EINT8

2

K4 K5

K1

K2

K3

2

K6

CON12 8 7 6 5 4 3 2 1 CON8 B

GND VDD33V EINT19 EINT15 EINT14 EINT13 EINT11 EINT8

GPG11 GPG7 GPG6 GPG5 GPG3 GPG0

nCTS0/GPH0 nRTS0/GPH1 TXD0/GPH2 RXD0/GPH3 TXD1/GPH4 RXD1/GPH5 nRTS1/TXD2/GPH6 nCTS1/RXD2/GPH7 UCLK/GPH8

JTAG nTRST TCK TDI TDO TMS

S3C2440X K11 L17 K13 K14 K16 K17 J11 J15 K15 H15 J13 H17 J16 J14 L1 L4 M1 L7 M4 M3 M2 P1 P11 VDD33V

nLED_1

LEND VCLK VLINE VFRAME VM USB_EN LCDVF1 LCDVF2 LCD_PWR

LED1 GREEN LED2 GREEN LED3 GREEN LED4 GREEN

R40 1K R41 1K R42 1K R43 1K

nCTS0 nRTS0 TXD0 RXD0 TXD1 RXD1 TXD2 RXD2 WP_SD

nTRST TCK TDI TDO TMS

nLED_2

nLED_3

nLED_4

A Title Size B Date: File: 1 2 3 4 5 11-Oct-2008 C:\mini2440\mini2440 .ddb Sheet of Drawn By: 6

Number Revision

VDD33V

D7 1N4148 R12

D8

TP1 CON1 1

VDDRTC

10K

BAT1 BATTERY 1N4148

VDD33V VDD33V

R10 15K

VDDRTC

PWREN

VDD1.25V N16 M13 F1 F16 A16 B11 A10 A6 A1

VDD1.25V U11 T8 T6 U2 U1 L2 J2

H14 J12 N15 P14 J17 G4

U1C nBATT_FLT PWREN VDD_RTC(3.3V) VDD_adc(3.3V) VDDalive(1.2V) VDDalive(1.2V) VDDA_MPLL(1.2V) VDDA_UPLL(1.2V) VDDiarm(1.2V) VDDiarm(1.2V) VDDiarm(1.2V) VDDiarm(1.2V) VDDiarm(1.2V) VDDiarm(1.2V) VDDiarm(1.2V) VDDi(1.2V) VDDi(1.2V) VDDi(1.2V) VDDi(1.2V) VDDi(1.2V) VDDi(1.2V) VDDi(1.2V)

nRESET

H16 N13 N17 M16 L13 M15 M17 L14 L15 L16 N9 T9 T10 M11 N10 G5 G7 G2 J3 J4 H6 G3 H5 H4 H3 H7 J8 H2

nRESET nRSTOUT/GPA21 EINT0/GPF0 EINT1/GPF1 EINT2/GPF2 EINT3/GPF3 EINT4/GPF4 EINT5/GPF5 EXT INT EINT6/GPF6 EINT7/GPF7 EINT8/GPG0 EINT9/GPG1 EINT16/GPG8 EINT17/GPG9/nRST1 EINT18/GPG10/nCTS1

EINT0 EINT1 EINT2 EINT3 EINT4 EINT5 EINT6 IRQ_LAN EINT8 EINT9 nCD_SD EINT17 EINT18

VDDMOP(SCLK,100MHz:3.3V) VDDMOP(SCLK,100MHz:3.3V) VDDMOP(SCLK,100MHz:3.3V) VDDMOP(SCLK,100MHz:3.3V) VDDMOP(SCLK,100MHz:3.3V) VDDMOP(SCLK,100MHz:3.3V) VDDMOP(SCLK,100MHz:3.3V) VDDOP()3.3V) VDDOP()3.3V) VDDOP()3.3V) VDDOP()3.3V) VSSA_ADC VSSi VSSi VSSi VSSi VSSi VSSi VSSi VSSA_mPLL VSSA_UPLL

VDD33V B6 A9 B12 B14 B16 F17 C1 K12 T12 T3 J1 T14 F2 A3 A4 B10 A12 C17 G17

VSSMOP VSSMOP VSSMOP VSSMOP VSSMOP VSSMOP VSSMOP VSSMOP VSSMOP VSSMOP VSSMOP VSSMOP VSSMOP VSSMOP VSSMOP

CAM_PCLK CAM_VSYNC CAM_HREF CAMCLK CAMRST CAMDATA0 CAMDATA1 CAMDATA2 CAMDATA3 CAMDATA4 CAMDATA5 CAMDATA6 CAMDATA7

VSSiarm vssiarm VSSiarm VSSiarm VSSiarm VSSiarm VSSiarm

CAMPCLK/GPJ8 CAMVSYNC/GPJ9 CAMHREF/GPJ10 CAMCLKOUT/GPJ11 CAMRESET/GPJ12 CAMERA IF CAMDATA0/GPJ0 CAMDATA1/GPJ1 CAMDATA2/GPJ2 CAMDATA3/GPJ3 CAMDATA4/GPJ4 CAMDATA5/GPJ5 CAMDATA6/GPJ6 CAMDATA7/GPJ7

B R17 M12

S3C2440X B1 E2 D17 D16 A15 B13 A11 A7 A5 N1 U3 U9 U15 G1 H11 CA1 CA2 CA3 CA4 CA5 CA6 CA7 CA8 CA9 CA10 CA11 CA12 CA13 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF A VDD1.25V C20 C21 C22 C23 C24 C25 100nF 100nF 100nF 100nF 100nF 100nF CA14 CA15 CA16 CA17 CA18 100nF 100nF 100nF 100nF 100nF CA20 CA21 CA22 CA23 100nF 100nF 100nF 100nF Title Size B Date: File: 1 2 3 4 5 11-Oct-2008 C:\mini2440\mini2440 .ddb Sheet of Drawn By: 6 H1 K1 T1 T2 U4 U7 U10 VDD33V C14 C15 C16 C17 C18 C19 100nF 100nF 100nF 100nF 100nF 100nF A

Number Revision

LADDR2 LADDR3 LADDR4 LADDR5 LADDR6 LADDR7 LADDR8 LADDR9 LADDR10 LADDR11 LADDR12 LADDR13 LADDR14 LADDR24 LADDR25 LnWBE0 LnWBE1 LSCKE LSCLK0

23 24 25 26 29 30 31 32 33 34 22 35 36 20 21 15 39 37 38 28 41 54 6 12 46 52

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 BA0 BA1 LDQM UDQM SCKE SCLK VSS0 VSS1 VSS2 VSSQ0 VSSQ1 VSSQ2 VSSQ3

U6

DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15 nSCS nSRAS nSCAS nWE VDD0 VDD1 VDD2 VDDQ0 VDDQ1 VDDQ2 VDDQ3

2 4 5 7 8 10 11 13 42 44 45 47 48 50 51 53

LDATA0 LDATA1 LDATA2 LDATA3 LDATA4 LDATA5 LDATA6 LDATA7 LDATA8 LDATA9 LDATA10 LDATA11 LDATA12 LDATA13 LDATA14 LDATA15

LADDR2 LADDR3 LADDR4 LADDR5 LADDR6 LADDR7 LADDR8 LADDR9 LADDR10 LADDR11 LADDR12 LADDR13 LADDR14 LADDR24 LADDR25 LnWBE2 LnWBE3 LSCKE LSCLK1

23 24 25 26 29 30 31 32 33 34 22 35 36 20 21 15 39 37 38 28 41 54 6 12 46 52

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 BA0 BA1 LDQM UDQM SCKE SCLK VSS0 VSS1 VSS2 VSSQ0 VSSQ1 VSSQ2 VSSQ3

U7

DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15 nSCS nSRAS nSCAS nWE VDD0 VDD1 VDD2 VDDQ0 VDDQ1 VDDQ2 VDDQ3

2 4 5 7 8 10 11 13 42 44 45 47 48 50 51 53 19 18 17 16 1 14 27 3 9 43 49

LDATA16 LDATA17 LDATA18 LDATA19 LDATA20 LDATA21 LDATA22 LDATA23 LDATA24 LDATA25 LDATA26 LDATA27 LDATA28 LDATA29 LDATA30 LDATA31 LnSCS0 LnSRAS LnSCAS LnWE VDD33V

nCD_SD WP_SD SDDATA1 SDDATA0 SDCLK

VDD33V

VDD33V

4 3 2 1

RA8

4 3 2 1 RA9 5 6 7 8

19 LnSCS0 18 LnSRAS 17 LnSCAS 16 LnWE VDD33V 1 14 27 3 9 43 49

5 6 7 8

VDD33V

CON7

SD/MMC CARD

11 10 8 7 6 5 4 3 2 1 9

nCD WP DAT1 DAT0 GND CLK VDD GND CMD CD/DAT3 DAT2 PAD4 PAD3 PAD2 PAD1 15 14 13 12 C

HY57V561620(32MB)

VDD33V HY57V561620 (32MB) C27 C28 C29 100nF 100nF 100nF

SDCMD SDDATA3 SDDATA2

VDD33V C30 C31 C32 C33 100nF 100nF 100nF 100nF

LADDR1 LADDR2 LADDR3 LADDR4 LADDR5 LADDR6 LADDR7 LADDR8 LADDR9 LADDR10 LADDR11 LADDR12 LADDR13 LADDR14 LADDR15 LADDR16 LADDR17 LADDR18 LADDR19 LADDR20 LADDR21 LADDR22

NOR FLASH

U10 25 24 23 22 21 20 19 18 8 7 6 5 4 3 2 1 48 17 16 9 10 13 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 A17 A18 A19 A20/NC A21/NC D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 29 31 33 35 38 40 42 44 30 32 34 36 39 41 43 45

LDATA0 LDATA1 LDATA2 LDATA3 LDATA4 LDATA5 LDATA6 LDATA7 LDATA8 LDATA9 LDATA10 LDATA11 LDATA12 LDATA13 LDATA14 LDATA15

NAND FLASH

VDD33V B

R6 10K

RnB nFCE CLE ALE nFWE nFRE

U2

K9Fxx08

7 9 16 17 18 8 6 13 36

R/B CE CLE ALE WE RE SE VSS VSS

I/O7 I/O6 I/O5 I/O4 I/O3 I/O2 I/O1 I/O0 WP VCC VCC

44 43 42 41 32 31 30 29 19 12 37

LDATA7 LDATA6 LDATA5 LDATA4 LDATA3 LDATA2 LDATA1 LDATA0

VDD33V

VDD33V VDD OE WE CE 37 28 11 26 12 14

LnOE LnWE nGCS0

C10 0.1uF

VDD33V

R7 10K R69 10K

VDD33V

15 47 27 46

NC NC VSS VSS /RST/NC /WP

nRESET

A AM29LV160DB/SST39VF1601

A Title Size B Date: File: 11-Oct-2008 C:\mini2440\mini2440 .ddb Sheet of Drawn By: 6

Number Revision

NETLINK2

R5

D

NETLINK

D

NETLINK3

0 R8 0 R13

VDD33V

R82 4.7K

75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51

NETLINK1

NETACT

VDD33V U18 VDD33V 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 RD1 50 RD5 50 TXTX+ RXRX+

NC NC DVDD DVDD GPIO3 GPIO2 GPIO1 GPIO0 EECS EECK EEDO EEDI DGND LINK_ACT# DUP# SPEED# CLK20MO DGND MDC MDIO DVDD TX_EN TXD3 TXD2 TXD1

R16 1K R39 1K LAN 1 2 3 4 5 6 7 8 9 10 11 12 A B C D TD+ TDGND GND RD+ RDGLEDA GLEDk YLEDA YLEDK A B C D HR911103A C

VDD33V C

nRESET

C81 10uF

C79 10uF

C74 0.1uF

C36 0.1uF

GND

VDD33V

LDATA15 LDATA14 LDATA13 LDATA12 LDATA11 LDATA10 LDATA9 LDATA8

LADDR2

VDD33V

IRQ_LAN

76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100

IOR# IOW# AEN IOWAIT DVDD SD0 SD1 SD2 SD3 SD4 SD5 SD6 SD7 RST DGND TEST1 TEST2 TEST3 TEST4 DVDD X2_25M X1_25M DGND SD AGND

DGND NC LINK_O WACKUP PW_RST# DGND SD15 SD14 SD13 SD12 SD11 SD10 SD9 SD8 DVDD IO16 CMD SA4 SA5 SA6 SA7 SA8 SA9 DGND INT

DM9000

TXD0 TX_CLK TEST5 RX_CLK RX_ER RX_DV COL CRS DGND RXD3 RXD2 RXD1 RXD0 LINK_I DVDD AVDD TXOTXO+ AGND AGND RXIRXI+ AVDD AVDD BGRES

NETACT

VDD33V TXTX+ RXRX+ RD6 50 RD3 50 CD1 0.1u

C8 0.1uF

1 C35

NETLINK

GND B VDD33V

R83 6.8K %1

0.1uF

LDATA0 LDATA1 LDATA2 LDATA3 LDATA4 LDATA5 LDATA6 LDATA7

nWAIT

LnOE LnWE

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 X6 25M C77 22p

nLAN_CS

C78 22p

VDD33V 1

R76 4.7K

Title Size A3 Date: File: 1 2 3 4 5 6

Number Revision

11-Oct-2008 C:\mini2440\mini2440.ddb 7 Sheet of Drawn By: 8

VDD5V VDD33V 16 D

TXD0 RXD0 nRTS0 nCTS0

C54 1 R23 0.1uF 22 1 1 R24 22 1 1 6 2 7 3 8 4 9 5

(male)

R27

DN0 2 DP0 2

RSTXD0 RSRXD0 RSRTS0 RSCTS0

15K 2

USB_DUSB_D+

USB-HOST 1 2 3 4 VBUS DD+ GND USB Port A type

USB(HOST)SOCKET

T1IN ROUT1 T2IN ROUT2 C1+ C1-

VDD

11 12 10 9 1

U17 14 T1OUT 13 RIN1 T2OUT RIN2 C2+ C27 8 4 5

COM0 BOXCONN_DB9

R28

15K 2

C55 104 3

C58 104

RSTXD0 RSCTS0 RSRXD0 RSRTS0

USB,GPC5

USB_5V

USB_EN1

R291.5K

2 1 R30470K USB-DEVICE 2 1 2 3 4 VBUS DD+ GND USB Port A type C

2 C56 104

VSS

V+

VMAX3232SOP

6 C59 104

PDN0 PDP0

C CON1

TXD0 RXD0 VDD5V GND

15

1 1

R2522 R2622

2 2

CON2

TXD1 RXD1 VDD5V GND

CON3

TXD2 RXD2 VDD5V GND

1 2 3 4 CON4

1 2 3 4 CON4

1 2 3 4 CON4

USB

1.8V()

S1 CON5 1 2 3 4 5 VDD5V 1 C37 104

VDD5V VDDIN

1.25V()

VDD33V 2 C11 10uF/10V C38 104 /FAULT 8 VDD33V /SHDN GND CC SET 5 C34 104 4 3 U9 4 3 1 2 1 2 R2 470

nRESET

U14 GND Vin Vout NC 3 4 C65 10uF

VDD18V

U5 MAX8860EUA18 IN OUT OUT 1 4 C13 10uF/10V R31 10

VDD1.25V C43 104

C64 10uF

1 2 3 DC_JACK

VDDIN GND GND VDD5V

CN1

LM1117-1.8V

5V

VDD5V CON8 1 2 3 4 CON4 C3 100nF C9 10uF

3.3V()

U4 1 GND Vin Vout NC 3 4 C12 10uF C39 C7 100nF VDD33V

7 6

MAX811 R32 0 R33 100K RST SW-PB 3

LM1117-33 2

33nF/6.3V

H1 1 CON1 H2 1 CON1 H3 A 1 CON1 H4 1 CON1

H5 1 CON1 H6 1 CON1 A Title VDD33V R1 330

RED Power

Size B Date: File: 1 2 3 4 5

Number 11-Oct-2008 C:\mini2440\mini2440 .ddb Sheet of Drawn By: 6 Revision

J2 3 2 1 CON3 D

VDDLCD VD0 VD2 VD4 VD6 GND VD9 VD11 VD13 VD15 VD16 VD18 VD20 VD22 GND GPB1 VM VLINE TSXM TSYM GND

VDD5V VDD33V

general int resist pulled up

LCD 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 LCD41P 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40

VDDLCD VD1 VD3 VD5 VD7 VD8 VD10 VD12 VD14 GND VD17 VD19 VD21 VD23 LCD_PWR nRESET VFRAME VCLK TSXP TSYP VDD5V EINT17 EINT3 nGCS1 nGCS3 LnOE nWAIT nXDACK0 LADDR0 LADDR2 LADDR4 LADDR6 LDATA0 LDATA2 LDATA4 LDATA6 LDATA8 LDATA10 LDATA12 LDATA14

CON5 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40

GND EINT18 EINT9 nGCS2 nGCS5 LnWE nRESET nXDREQ0 LADDR1 LADDR3 LADDR5 LADDR24 LDATA1 LDATA3 LDATA5 LDATA7 LDATA9 LDATA11 LDATA13 LDATA15

CEMERA

I2CSDA I2CSCL EINT20 CAMRST CAMCLK CAM_HREF CAM_VSYNC CAM_PCLK CAMDATA7 CAMDATA6 CAMDATA5 CAMDATA4 CAMDATA3 CAMDATA2 CAMDATA1 CAMDATA0 VDD33V VDD_CAM VDD18V GND

D RA1 CON4

VDD5V GND AIN0 AIN2 EINT0 EINT2 EINT4 EINT6 EINT9 EINT13 EINT15 EINT18 SPIMISO SPICLK I2CSCL GPB0 CLKOUT0

10K

VDD33V D1

1N4148

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 CON20

1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33

2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34

VDD33V nRESET AIN1 AIN3 EINT1 EINT3 EINT5 EINT8 EINT11 EINT14 EINT17 EINT19 SPIMOSI nSS_SPI I2CSDA GPB1 CLKOUT1

EINT0 EINT1 EINT2 EINT4

1 2 3 4

VDD33V EINT5 8 EINT6 7 CLKOUT0 6 CLKOUT1 5

RA2 1 2 3 4

10K

VDD33V 8 7 6 5

KBD resist pulled up

spi resist pulled up

RA3

EINT11 EINT13 EINT14 EINT15

10K

1 2 3 4 RA5

10K

VDD33V SPICLK 8 SPIMISO 7 SPIMOSI 6 nSS_SPI 5 VDD33V EINT3 8 EINT9 7 EINT17 6 EINT18 5

RA4 1 2 3 4 RA6 1 2 3 4

10K

VDD33V 8 7 6 5 VDD33V 8 7 6 5

10K

I2CSCL I2CSDA

1 2 3 4

HEADER 18X2

i2c resist pulled up system busl int resist pulled up

HEADER 20X2

LCD

JTAG

B

R58

nTRST TDI TMS TCK

CMOS

GPIO

VDD5V VDD33V SPEAKER C

I2C:AT24C08

AD

VDD33V B 2

JTAG 1 3 5 7 9 2 4 6 8 10

nRESET TDO

SPEAKER

R57 1K

GPB0

U8 1 2 3 4 A0 VDD A1 WP A2 SCL GND SDA 24C08 8 7 6 5

I2CSCL I2CSDA

AIN0

R34 1.5K

Q1 9014

TAP A 1

HEADER 4X2

A Title Size B Date: File: 1 2 3 4 5 11-Oct-2008 C:\mini2440\mini2440 .ddb Sheet of Drawn By: 6

R59

R60

R61

VDD33V

W1 10K

10K

10K

10K

10K

Number Revision

C45 VDD33V 1 VDD33V 10 AU_AVDD33V 3 7 25

VINL

10uF/16V

U12

UDA1341TS

LINEOUT_L

CON14 EARJACK ROUT1 ROUT2 LOUT1 LOUT2

5 4

3 2

10uF/16V 2

6 8 22

VINL2 Vref(ADC&DAC) VINR2 QMUTE AGCSTAT OVERFL SYSCLK BCK WS DATAO DATAI L3MODE L3CLOCK L3DATA TEST2 TEST1 AVSS(ADC) Vnref(ADC) DVSS AVSS(DAC)

28 23 9 21 20 1 5 11 27 C47 R77 R78 R79 R80 10K 10K 10K 10K

R4 10K

R9 10K

LINEOUT_L LINEOUT_R OUTR OUTL

MIC2 C26

MIC2_IN

CDCLK I2SSCLK I2SLRCK I2SSDI I2SSDO

12 16 17 18 19

CON10 MIC_IN

MIC_IN GND MIC_IN

MICROPHONE1

10uF/16V R14 4.7K

L3MODE 13 L3CLOCK 14 L3DATA 15

10uF/16V R3 4.7K VDD33V

1 2 3 CON3

VDD33V

R15 100 C42 10uF/16V C4 C44 10uF/16V 0.1uF C48

R11 100

L4 10mH

C71 +

AVDD(ADC) Vpref(ADC) AVDD(DAC)

VINL1 VINR1

2 4

C46

10uF/16V

VINR

GND

DVDD

VOUTL VOUTR

26 24

LINEOUT_R

10uF/16V

A Title Size B Date: File: 1 2 3 4 5 11-Oct-2008 C:\mini2440\mini2440 .ddb Sheet of Drawn By: 6

Number Revision

You might also like

- Abus Hängetaster HTDocument31 pagesAbus Hängetaster HTJoachim LückingNo ratings yet

- DOSProg HBDocument800 pagesDOSProg HBswflyNo ratings yet

- GNU DebianDocument963 pagesGNU DebianMoh TahirNo ratings yet

- TomescuDocument111 pagesTomescuFlory2die4No ratings yet

- d001 Siebensegmentanzeige v02Document9 pagesd001 Siebensegmentanzeige v02mail87523No ratings yet

- Lipp - VPN Virtuelle Private NetzwerkeDocument421 pagesLipp - VPN Virtuelle Private NetzwerkeJohn BarrowsNo ratings yet

- g18029 Tuf Gaming Z590-Plus Um v2 WebDocument70 pagesg18029 Tuf Gaming Z590-Plus Um v2 WebnvbNo ratings yet

- WAGODocument234 pagesWAGOZljacNo ratings yet

- Usersguide Arduinosimulator1.4 EnglischDocument19 pagesUsersguide Arduinosimulator1.4 EnglischJonathas100% (1)

- Beamicon2 CncPod2 - InstallationDocument6 pagesBeamicon2 CncPod2 - InstallationfarowarezNo ratings yet

- Controlador EasyPort FluidSim USBDocument2 pagesControlador EasyPort FluidSim USBKevin ArceNo ratings yet

- Einstieg in LinuxDocument65 pagesEinstieg in Linuxhancu georgeNo ratings yet

- Paragon Backup and Recovery 17 PRODocument44 pagesParagon Backup and Recovery 17 PROTom0% (1)

- Ezs BuchDocument260 pagesEzs Buchapi-3823762No ratings yet

- KST UserTech 30 deDocument75 pagesKST UserTech 30 deFlow89No ratings yet

- Spez KR C1 06 enDocument22 pagesSpez KR C1 06 enafonsomoutinhoNo ratings yet

- Kss 82 83 Cread Cwrite deDocument69 pagesKss 82 83 Cread Cwrite deNicolas Romero100% (1)

- SP 01 en CCD Farbkamera M Zoom HochaufloesendDocument8 pagesSP 01 en CCD Farbkamera M Zoom HochaufloesendMatthew KuttikadNo ratings yet

- HP Mini 210 - Quanta Annika 1.1 - Rev 1.ADocument32 pagesHP Mini 210 - Quanta Annika 1.1 - Rev 1.Astruja460% (1)

- Ob5269 - Ob3362 mp3389Document1 pageOb5269 - Ob3362 mp3389Andres AlegriaNo ratings yet

- HP Mini 210 - Quanta Annika - Rev 1aDocument32 pagesHP Mini 210 - Quanta Annika - Rev 1aMarco VasquezNo ratings yet

- Ardui PiDocument1 pageArdui PiAllan MoreiraNo ratings yet

- Samsung SGH-C170 SchematicsDocument5 pagesSamsung SGH-C170 SchematicsGeorge GeorgescuNo ratings yet

- Mini (AC 0) .19.02.09Document1 pageMini (AC 0) .19.02.09Fernando Carvalho Sperotto100% (1)

- Schematic - Samsung Bn44-00289b (Et)Document2 pagesSchematic - Samsung Bn44-00289b (Et)gmzombie100% (1)

- BOMDocument10 pagesBOMskyddNo ratings yet

- Schema IBM Z60Document73 pagesSchema IBM Z60Eva Beti PetreNo ratings yet

- VWDocument6 pagesVWSima PurkovNo ratings yet

- KRC 2 Ed 2005 E-PlanDocument49 pagesKRC 2 Ed 2005 E-PlandataromaNo ratings yet

- BN44 00428BDocument7 pagesBN44 00428BDanielito Espi RiveNo ratings yet

- BN44 00260aDocument2 pagesBN44 00260aJuan VilasNo ratings yet

- VWDocument6 pagesVWAleksander Alexander100% (1)

- BN AsdDocument7 pagesBN AsdvasileisipNo ratings yet

- PartsDocument2 pagesPartsestenioNo ratings yet

- Blaupunkt Opel Car 2003 300 300ntDocument29 pagesBlaupunkt Opel Car 2003 300 300ntsandocan75No ratings yet

- Blaupunkt Opel Car 2003 300 300nt PDFDocument29 pagesBlaupunkt Opel Car 2003 300 300nt PDFsandocan75-1No ratings yet

- Blaupunkt - Opel Car 300Document29 pagesBlaupunkt - Opel Car 30016marius50% (2)

- UntitledDocument9 pagesUntitledCarsten WollnyNo ratings yet

- Log Z Ow91 Wauzzzgb9lr037151 13014kmDocument8 pagesLog Z Ow91 Wauzzzgb9lr037151 13014kmЛеонид ПротасовNo ratings yet

- Getriebeturbofan und konventioneller Turbofan: Ein Vergleich auf der Basis stationärer LeistungsrechnungenFrom EverandGetriebeturbofan und konventioneller Turbofan: Ein Vergleich auf der Basis stationärer LeistungsrechnungenNo ratings yet

- Steuergeräte-Entwicklung mit AUTOSAR: Evaluierung der Entwicklungsumgebung Arctic Studio: Entwicklung AUTOSAR-basierter SystemeFrom EverandSteuergeräte-Entwicklung mit AUTOSAR: Evaluierung der Entwicklungsumgebung Arctic Studio: Entwicklung AUTOSAR-basierter SystemeNo ratings yet

- Cryopyrin-assoziierte periodische Syndrome (CAPS)From EverandCryopyrin-assoziierte periodische Syndrome (CAPS)No ratings yet

- Die Zukunft des intelligenten Automobils: Wirtschaftliche Markteinführungsszenarien am Beispiel AudiFrom EverandDie Zukunft des intelligenten Automobils: Wirtschaftliche Markteinführungsszenarien am Beispiel AudiNo ratings yet

- VW Multivan / VW Transporter T5 115-235 PS, Diesel 84-174 PS 5/03-6/15: So wird´s gemacht - Band 134From EverandVW Multivan / VW Transporter T5 115-235 PS, Diesel 84-174 PS 5/03-6/15: So wird´s gemacht - Band 134Rating: 5 out of 5 stars5/5 (2)

- Skoda Octavia II von 6/04 bis 1/13: So wird's gemacht - Band 142From EverandSkoda Octavia II von 6/04 bis 1/13: So wird's gemacht - Band 142No ratings yet

- Der Weg zum eigenen Roboter: Tipps, Tricks und kleine ProjekteFrom EverandDer Weg zum eigenen Roboter: Tipps, Tricks und kleine ProjekteNo ratings yet

- Einführung in die C-Programmierung mit dem ATmega32: Aufbau und ProgrammierungFrom EverandEinführung in die C-Programmierung mit dem ATmega32: Aufbau und ProgrammierungNo ratings yet

- Chaos Computer Club & Schäuble S Fingerprint, "Vol.2"Document14 pagesChaos Computer Club & Schäuble S Fingerprint, "Vol.2"oliver becker100% (1)

- Igel 2110 UserguideDocument108 pagesIgel 2110 Userguidebat-kf100% (2)

- Edgar Zilsel - WikipediaDocument2 pagesEdgar Zilsel - WikipediaHannes WeilerNo ratings yet

- A2.2 Bausteintest2 Warenwelt AngabeDocument3 pagesA2.2 Bausteintest2 Warenwelt AngabeGiana AraujoNo ratings yet