Professional Documents

Culture Documents

Chapter #8: Finite State Machine Design 8.5 Finite State Machine Word Problems

Uploaded by

Shivani Mittal0 ratings0% found this document useful (0 votes)

19 views22 pagesFinite String Pattern Recognizer A finite string recognizer has one input (X) and one output (Z) the output is asserted whenever the input sequence.010. Has been observed, as long as the sequence 100 has never been seen.

Original Description:

Original Title

lec16

Copyright

© © All Rights Reserved

Available Formats

PPT, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentFinite String Pattern Recognizer A finite string recognizer has one input (X) and one output (Z) the output is asserted whenever the input sequence.010. Has been observed, as long as the sequence 100 has never been seen.

Copyright:

© All Rights Reserved

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

19 views22 pagesChapter #8: Finite State Machine Design 8.5 Finite State Machine Word Problems

Uploaded by

Shivani MittalFinite String Pattern Recognizer A finite string recognizer has one input (X) and one output (Z) the output is asserted whenever the input sequence.010. Has been observed, as long as the sequence 100 has never been seen.

Copyright:

© All Rights Reserved

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

You are on page 1of 22

Contemporary Logic Design

Finite State Machine Design

R.H. Katz Transparency No. 16-1

Chapter #8: Finite State Machine Design

8.5 Finite State Machine Word Problems

Contemporary Logic Design

Finite State Machine Design

R.H. Katz Transparency No. 16-2

Finite State Machine Word Problems

Mapping English Language Description to Formal Specifications

Four Case Studies:

Finite String Pattern Recognizer

Complex Counter with Decision Making

Traffic Light Controller

Digital Combination Lock

We will use state diagrams and ASM Charts

Contemporary Logic Design

Finite State Machine Design

R.H. Katz Transparency No. 16-3

Finite State Machine Word Problems

1. Finite String Pattern Recognizer

A finite string recognizer has one input (X) and one output (Z).

The output is asserted whenever the input sequence 010

has been observed, as long as the sequence 100 has never been

seen.

Step 1. Understanding the problem statement

Sample input/output behavior:

X: 00101010010

Z: 00010101000

X: 11011010010

Z: 00000001000

The outputs have been written to lag behind the inputs.

Contemporary Logic Design

Finite State Machine Design

R.H. Katz Transparency No. 16-4

Finite State Machine Word Problems

Finite String Recognizer

Step 2. Draw State Diagrams/ASM Charts for the strings that must be

recognized. I.e., 010 and 100.

Moore State Diagram

Reset signal places

FSM in S0

Outputs 1

Loops in State

S0

[0]

S1

[0]

S2

[0]

S3

[1]

S4

[0]

S5

[0]

S6

[0]

Reset

0 1

1

0

0

0

0,1

Contemporary Logic Design

Finite State Machine Design

R.H. Katz Transparency No. 16-5

Finite State Machine Word Problems

Finite String Recognizer

Exit conditions from state S3: have recognized 010

if next input is 0 then have 0100!

if next input is 1 then have 0101 = 01 (state S2)

S0

[0]

S1

[0]

S2

[0]

S3

[1]

S4

[0]

S5

[0]

S6

[0]

Reset

0 1

1

0

0

0

0,1

0

1

01

010

100

Contemporary Logic Design

Finite State Machine Design

R.H. Katz Transparency No. 16-6

Finite State Machine Word Problems

Finite String Recognizer

Exit conditions from S1: recognizes strings of form 0 (no 1 seen)

loop back to S1 if input is 0

Exit conditions from S4: recognizes strings of form 1 (no 0 seen)

loop back to S4 if input is 1

S0

[0]

S1

[0]

S2

[0]

S3

[1]

S4

[0]

S5

[0]

S6

[0]

Reset

0

1

1

0

1 0

0

1

0

0,1 0

010

01

0

100

Contemporary Logic Design

Finite State Machine Design

R.H. Katz Transparency No. 16-7

Finite State Machine Word Problems

Finite String Recognizer

S2, S5 with incomplete transitions

S2 = 01; If next input is 1, then string could be prefix of (01)1(00)

S4 handles just this case!

S5 = 10; If next input is 1, then string could be prefix of (10)1(0)

S2 handles just this case!

Final State Diagram

S0

[0]

S1

[0]

S2

[0]

S3

[1]

S4

[0]

S5

[0]

S6

[0]

Reset

0 1

0 1

1

1

1

0

1

0

0,1

0

0

0

01

010

100

10

1

Contemporary Logic Design

Finite State Machine Design

R.H. Katz Transparency No. 16-8

Finite State Machine Word Problems

Finite String Recognizer

Verify I/O behavior of your state diagram to insure it functions

like the specification

X: 00101010010

Z: 00010101000

X: 11011010010

Z: 00000001000

Sample input/output behavior:

Contemporary Logic Design

Finite State Machine Design

R.H. Katz Transparency No. 16-9

Finite State Machine Word Problems

2. Complex Counter

A sync. 3 bit counter has a mode control M. When M = 0, the counter

counts up in the binary sequence. When M = 1, the counter advances

through the Gray code sequence.

Binary: 000, 001, 010, 011, 100, 101, 110, 111

Gray: 000, 001, 011, 010, 110, 111, 101, 100

Example Valid I/O behavior:

Mode Input M

0

0

1

1

1

0

0

Current State

000

001

010

110

111

101

110

Next State (Z2 Z1 Z0)

001

010

110

111

101

110

111

Output = Next State

Contemporary Logic Design

Finite State Machine Design

R.H. Katz Transparency No. 16-10

Finite State Machine Word Problems

Complex Counter

Derive the State Diagram using Moore FSM

Contemporary Logic Design

Finite State Machine Design

R.H. Katz Transparency No. 16-11

Finite State Machine Word Problems

3. Traffic Light Controller

A busy highway is intersected by a little used farmroad. Detectors

C sense the presence of cars waiting on the farmroad.

With no car on farmroad, light remain green in highway direction. If

vehicle on farmroad, highway lights go from Green to Yellow to Red,

allowing the farmroad lights to become green. These stay green only

as long as a farmroad car is detected but never longer than a set

interval. When these are met, farm lights transition from Green to

Yellow to Red, allowing highway to return to green. Even if farmroad

vehicles are waiting, highway gets at least a set interval as green.

Assume you have an interval timer that generates a short time pulse

(TS) and a long time pulse (TL) in response to a set (ST) signal. TS

is to be used for timing yellow lights and TL for green lights.

Contemporary Logic Design

Finite State Machine Design

R.H. Katz Transparency No. 16-12

Finite State Machine Word Problems

Traffic Light Controller

Picture of Highway/Farmroad Intersection:

Highway

Highway

Farmroad

Farmroad

HL

HL

FL

FL

C

C

Contemporary Logic Design

Finite State Machine Design

R.H. Katz Transparency No. 16-13

Finite State Machine Word Problems

Traffic Light Controller

Tabulation of Inputs and Outputs:

Input Signal

reset

C

TS

TL

Output Signal

HG, HY, HR

FG, FY, FR

ST

Description

place FSM in initial state

detect vehicle on farmroad

short time interval expired

long time interval expired

Description

assert green/yellow/red highway lights

assert green/yellow/red farmroad lights

start timing a short or long interval

Tabulation of Unique States: Some light configuration imply others

State

S0

S1

S2

S3

Description

Highway green (farmroad red)

Highway yellow (farmroad red)

Farmroad green (highway red)

Farmroad yellow (highway red)

Contemporary Logic Design

Finite State Machine Design

R.H. Katz Transparency No. 16-14

Finite State Machine Word Problems

Traffic Light Controller

Refinement of ASM Chart:

Start with basic sequencing and outputs:

S

0

S

3

S

1

S

2

H. HG

H. FR

H. HR

H. FY

H. HR

H. FG

H. HY

H. FR

Contemporary Logic Design

Finite State Machine Design

R.H. Katz Transparency No. 16-15

Finite State Machine Word Problems

Traffic Light Controller

Determine Exit Conditions for S0:

Car waiting and Long Time Interval Expired- C TL

Equivalent ASM Chart Fragments

S

0

S

0

H.HG

H.FR

H.HG

H.FR

TL

TL C

H.ST

C

H.ST

S

1

H.HY

H.FR

S

1

H.HY

H.FR

0

0

1

1

0

1

OR

Contemporary Logic Design

Finite State Machine Design

R.H. Katz Transparency No. 16-16

Finite State Machine Word Problems

Traffic Light Controller

S1 to S2 Transition:

Set ST on exit from S0

Stay in S1 until TS asserted

Similar situation for S3 to S4 transition

S

1

H. HY

H. FR

TS

H. ST

S

2

H. HR

H. FG

0 1

Contemporary Logic Design

Finite State Machine Design

R.H. Katz Transparency No. 16-17

Finite State Machine Word Problems

Traffic Light Controller

S2 Exit Condition: no car waiting OR long time interval expired

Complete ASM Chart for Traffic Light Controller

S

0

S

3

H. HG

H. FR

H. ST

H. HR

H. FY

TS TL C

H. ST

H. ST

S

1

S

2

H. HY

H. FR

H. ST

H. HR

H. FG

TS

TL + C

0 0 1

1

1 0

1

0

Contemporary Logic Design

Finite State Machine Design

R.H. Katz Transparency No. 16-18

Finite State Machine Word Problems

Traffic Light Controller

Compare with state diagram:

Advantages of State Charts:

Concentrates on paths and conditions for exiting a state

Exit conditions built up incrementally, later combined into

single Boolean condition for exit

Easier to understand the design as an algorithm

S0: HG

S1: HY

S2: FG

S3: FY

Reset

TL + C

S0

TLC/ST

TS

S1 S3

S2

TS/ST

TS/ST

TL + C/ST

TS

TL C

MEALY

Contemporary Logic Design

Finite State Machine Design

R.H. Katz Transparency No. 16-19

Finite State Machine Word Problems

4. Digital Combination Lock

"3 bit serial lock controls entry to locked room. Inputs are RESET,

ENTER, 2 position switch for bit of key data. Locks generates an

UNLOCK signal when key matches internal combination. ERROR

light illuminated if key does not match combination. Sequence is:

(1) Press RESET, (2) enter key bit, (3) Press ENTER, (4) repeat (2) &

(3) two more times."

Problem specification is incomplete:

how do you set the internal combination?

exactly when is the ERROR light asserted?

Make reasonable assumptions:

combination hardwired into next state logic vs. stored in internal

register

assert as soon as error is detected vs. wait until full combination

has been entered

==>Our design: registered combination plus error after full combination

Contemporary Logic Design

Finite State Machine Design

R.H. Katz Transparency No. 16-20

Finite State Machine Word Problems

Digital Combination Lock

Understanding the problem: draw a block diagram

Internal

Combination

Operator Data

Inputs:

Reset

Enter

Key-In

L0, L1, L2

Outputs:

Unlock

Error

UNLOCK

ERROR

RESET

ENTER

KEY -IN

L

0

L

1

L

2

Combination

Lock FSM

Contemporary Logic Design

Finite State Machine Design

R.H. Katz Transparency No. 16-21

Finite State Machine Word Problems

Digital Combination Lock

Derive the ASM or the State Diagram Implementation

Contemporary Logic Design

Finite State Machine Design

R.H. Katz Transparency No. 16-22

HW #16 -- Section 8.5

You might also like

- Word ProblemsDocument64 pagesWord ProblemsmjunaidnNo ratings yet

- Finite State Machine DesignDocument32 pagesFinite State Machine DesignluffydmonNo ratings yet

- Motivation: Word ProblemsDocument31 pagesMotivation: Word ProblemsluffydmonNo ratings yet

- Chapter #8: Finite State Machine DesignDocument57 pagesChapter #8: Finite State Machine DesignAli AhmadNo ratings yet

- Finite State Machine DesignDocument64 pagesFinite State Machine Designivanf15No ratings yet

- Finite State Machine Design: Prith Banerjee Ece C03 Advanced Digital Design Spring 1998Document47 pagesFinite State Machine Design: Prith Banerjee Ece C03 Advanced Digital Design Spring 1998VIKRAMNo ratings yet

- Chapter #8: Finite State Machine DesignDocument57 pagesChapter #8: Finite State Machine DesignniluNo ratings yet

- Finite State MachineDocument57 pagesFinite State MachinedoomachaleyNo ratings yet

- Chapter #10: Finite State Machine ImplementationDocument32 pagesChapter #10: Finite State Machine Implementationphani_abkNo ratings yet

- ResearchDocument9 pagesResearchhatemalshandoli1No ratings yet

- Advanced Digital Systems DesignDocument12 pagesAdvanced Digital Systems DesignlawrencerajasekaranNo ratings yet

- Vending MAchineDocument22 pagesVending MAchineavireddy1100% (2)

- ECE 545-Digital System Design With VHDL: Sequential Logic Review and Algorithmic State Machines 9/9/08Document29 pagesECE 545-Digital System Design With VHDL: Sequential Logic Review and Algorithmic State Machines 9/9/08Rahul TulsianiNo ratings yet

- Capstone ResearchProject Moore Mealy MachineDocument9 pagesCapstone ResearchProject Moore Mealy MachineAnish ChatterjeeNo ratings yet

- Intro. To Comp. Eng. Chapter Viii-1 Finite State MachinesDocument33 pagesIntro. To Comp. Eng. Chapter Viii-1 Finite State MachinesUday Soundar RajNo ratings yet

- Combinational and Sequential Circuits DesignDocument25 pagesCombinational and Sequential Circuits DesignJadesh ChandaNo ratings yet

- Examples of Finite State Machines (FSMS) : Counters and Pattern GeneratorsDocument71 pagesExamples of Finite State Machines (FSMS) : Counters and Pattern GeneratorsflowarNo ratings yet

- Examples of Finite State Machines (FSMS) : Counters and Pattern GeneratorsDocument71 pagesExamples of Finite State Machines (FSMS) : Counters and Pattern GeneratorsArif Sumardiono100% (1)

- Finite State Machine Implementation: Prith Banerjee Ece C03 Advanced Digital Design Spring 1998Document31 pagesFinite State Machine Implementation: Prith Banerjee Ece C03 Advanced Digital Design Spring 1998Sai PrashanthNo ratings yet

- Lec Verilog TrafficLight SynthesisDocument32 pagesLec Verilog TrafficLight SynthesisKartikey ManchandaNo ratings yet

- Chapter #9: Finite State Machine Optimization: Contemporary Logic DesignDocument34 pagesChapter #9: Finite State Machine Optimization: Contemporary Logic DesignAshish PuraniNo ratings yet

- Fundamentals of Computer Systems: Finite State MachinesDocument32 pagesFundamentals of Computer Systems: Finite State Machinesjp_20_20No ratings yet

- State Encoding: One-Hot Encoding Output EncodingDocument24 pagesState Encoding: One-Hot Encoding Output EncodingRajesh BathijaNo ratings yet

- Finite State MachinesDocument8 pagesFinite State MachinesHnd FinalNo ratings yet

- Mah Adsd RPTDocument5 pagesMah Adsd RPTSurendra MalluNo ratings yet

- Chapter 3: Sequential Logic Some Definitions: Dr. Tim Mcguire Sam Houston State UniversityDocument6 pagesChapter 3: Sequential Logic Some Definitions: Dr. Tim Mcguire Sam Houston State Universitydemos2011No ratings yet

- Basic Sequential Design Steps: Flip-Flop Inputs Primary OutputsDocument10 pagesBasic Sequential Design Steps: Flip-Flop Inputs Primary OutputsAnkur SinghNo ratings yet

- ECN 252 Lab 6 - Design of D Flip-Flop and CountersDocument2 pagesECN 252 Lab 6 - Design of D Flip-Flop and CountersRUSHIL MOTWANINo ratings yet

- Hardware Slides 08Document30 pagesHardware Slides 08Taqi ShahNo ratings yet

- ECE 331 - Digital System Design: Derivation of State Graphs and State TablesDocument39 pagesECE 331 - Digital System Design: Derivation of State Graphs and State TablesRizulNo ratings yet

- Delay in VLSIDocument27 pagesDelay in VLSIlevan100% (1)

- CS 501 TOC Lab ManualDocument28 pagesCS 501 TOC Lab ManualAnupriya JainNo ratings yet

- Count and Registers GuideDocument31 pagesCount and Registers GuideBharadwaja PisupatiNo ratings yet

- CP1 Programmable Logic Controller Models GuideDocument45 pagesCP1 Programmable Logic Controller Models GuideSuzaini SupingatNo ratings yet

- Traffic light controller FSM designDocument7 pagesTraffic light controller FSM designVIKRAMNo ratings yet

- 07 FSMDocument46 pages07 FSMSP SpurtinathNo ratings yet

- Sequential Circuits II DocumentDocument21 pagesSequential Circuits II DocumentBlueNo ratings yet

- Lec17 FSM PDFDocument27 pagesLec17 FSM PDFNithin KumarNo ratings yet

- Summary of PCM SystemsDocument35 pagesSummary of PCM Systemsrafey111No ratings yet

- Lec19 FSMDocument14 pagesLec19 FSMGAURAV KUMARNo ratings yet

- Project AssignmentDocument2 pagesProject AssignmentbatoolNo ratings yet

- At CommandDocument29 pagesAt Commanddjango68No ratings yet

- Digital Design Using VHDL: Using Xilinx'S Tool For Synthesis and Modelsim For Verification Part (Iv)Document17 pagesDigital Design Using VHDL: Using Xilinx'S Tool For Synthesis and Modelsim For Verification Part (Iv)Rakesh Kumar DNo ratings yet

- Electronics Hardware Questions : Answers & Follow UpsDocument12 pagesElectronics Hardware Questions : Answers & Follow UpsJayachandra MakannavarNo ratings yet

- Finite State Machine Representation of Sequential CircuitsDocument38 pagesFinite State Machine Representation of Sequential CircuitsTaqi ShahNo ratings yet

- Electrical Logic Lab Manual 04Document11 pagesElectrical Logic Lab Manual 04Carson R. DickNo ratings yet

- Chapter #7: Sequential Logic Case StudiesDocument48 pagesChapter #7: Sequential Logic Case StudiesShivani AggarwalNo ratings yet

- HCTL 2017Document12 pagesHCTL 2017ivancho1070No ratings yet

- Master SetDocument624 pagesMaster SetEr Lokesh MahorNo ratings yet

- Rotary EncoderDocument6 pagesRotary EncoderalesysNo ratings yet

- Lect5 FSMDocument23 pagesLect5 FSMSangeetha BajanthriNo ratings yet

- VLSI & ASIC Digital Design Interview QuestionsDocument6 pagesVLSI & ASIC Digital Design Interview QuestionsRupesh Kumar DuttaNo ratings yet

- Cool Muscle Frequently Asked QuestionDocument5 pagesCool Muscle Frequently Asked QuestionsaileikNo ratings yet

- Unit 3 CSADocument25 pagesUnit 3 CSAyugdevNo ratings yet

- Digital Design With SystemVerilogDocument58 pagesDigital Design With SystemVerilogStephen A. EdwardsNo ratings yet

- Dvp-Es2 Ss2 Sa2 Sx2-Program o en 20110302Document609 pagesDvp-Es2 Ss2 Sa2 Sx2-Program o en 20110302puskyboyNo ratings yet

- Mock DataDocument56 pagesMock DataAnonymous O2bvbOuNo ratings yet

- Airframe Exam Review QuestionsDocument23 pagesAirframe Exam Review QuestionsbirukNo ratings yet

- Display TFT SPI ST7735Document6 pagesDisplay TFT SPI ST7735Adlene DenniNo ratings yet

- Sea Cities British English Teacher Ver2Document6 pagesSea Cities British English Teacher Ver2Kati T.No ratings yet

- Understanding Power Dynamics and Developing Political ExpertiseDocument29 pagesUnderstanding Power Dynamics and Developing Political Expertisealessiacon100% (1)

- IPA Assignment Analyzes New Public AdministrationDocument8 pagesIPA Assignment Analyzes New Public AdministrationKumaran ViswanathanNo ratings yet

- ERC12864-12 DemoCode 4wire SPI 2Document18 pagesERC12864-12 DemoCode 4wire SPI 2DVTNo ratings yet

- Hyd Schematic 2658487205 - 005Document3 pagesHyd Schematic 2658487205 - 005Angelo Solorzano100% (2)

- Alstom TOPGASDocument8 pagesAlstom TOPGASKatarina WilliamsNo ratings yet

- Documentation For UStarDocument26 pagesDocumentation For UStarthunder77No ratings yet

- Ethanol: Safety Data SheetDocument19 pagesEthanol: Safety Data SheetNitika SinhaNo ratings yet

- Senior Design Projects 201-2020 - For Website - MEDocument5 pagesSenior Design Projects 201-2020 - For Website - MEYujbvhujgNo ratings yet

- Syllabus Agri 2015Document248 pagesSyllabus Agri 2015parvathivignesh279No ratings yet

- CD1 ISO/IEC 17000 Conformity Assessment - Vocabulary and General PrinciplesDocument26 pagesCD1 ISO/IEC 17000 Conformity Assessment - Vocabulary and General PrinciplesMAC CONSULTORESNo ratings yet

- Republic of The Philippines Iba, Zambales: President Ramon Magsaysay State UniversityDocument3 pagesRepublic of The Philippines Iba, Zambales: President Ramon Magsaysay State UniversityErika Joy EscobarNo ratings yet

- University Reserch Worksheet PDFDocument7 pagesUniversity Reserch Worksheet PDFapi-410567922No ratings yet

- AWS D1.5 PQR TitleDocument1 pageAWS D1.5 PQR TitleNavanitheeshwaran SivasubramaniyamNo ratings yet

- wt-and-fds-practical-slipsDocument32 pageswt-and-fds-practical-slipsRohidas SapkalNo ratings yet

- E Requisition SystemDocument8 pagesE Requisition SystemWaNi AbidNo ratings yet

- Small Healthcare Organization: National Accreditation Board For Hospitals & Healthcare Providers (Nabh)Document20 pagesSmall Healthcare Organization: National Accreditation Board For Hospitals & Healthcare Providers (Nabh)Dipti PatilNo ratings yet

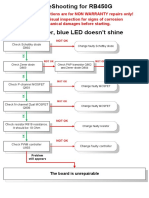

- RB450G Trouble ShootingDocument9 pagesRB450G Trouble Shootingjocimar1000No ratings yet

- Lesson Element Baron-Cohen Et Al. (1997) : Instructions and Answers For TeachersDocument10 pagesLesson Element Baron-Cohen Et Al. (1997) : Instructions and Answers For TeachersSyed SumaiyahNo ratings yet

- Travel Agency ManagementDocument47 pagesTravel Agency ManagementKatherine BarretoNo ratings yet

- The Godfather Term One Sample Basic Six Annual Scheme of Learning Termly Scheme of Learning WEEK 1 - 12Document313 pagesThe Godfather Term One Sample Basic Six Annual Scheme of Learning Termly Scheme of Learning WEEK 1 - 12justice hayfordNo ratings yet

- Rúbrica de composición escritaDocument2 pagesRúbrica de composición escritafrancisco alonsoNo ratings yet

- Schwarzschild Metric and Black Hole HorizonsDocument39 pagesSchwarzschild Metric and Black Hole Horizonsসায়ন চক্রবর্তীNo ratings yet

- Proposed - TIA - 1392 - NFPA - 221Document2 pagesProposed - TIA - 1392 - NFPA - 221Junior TorrejónNo ratings yet

- Xiaomi Mi Drone 4K User Manual GuideDocument47 pagesXiaomi Mi Drone 4K User Manual GuideΜιχάλης ΛαχανάςNo ratings yet

- Radiograph Evaluation ChecklistDocument2 pagesRadiograph Evaluation ChecklistZulfadli Haron100% (1)

- Packing, Transportation and Marketing of Ornamental FishesDocument16 pagesPacking, Transportation and Marketing of Ornamental Fishesraj kiranNo ratings yet