Professional Documents

Culture Documents

DELL VOSTRO-3500 Winery15 PDF

Uploaded by

ronaldovieiraOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DELL VOSTRO-3500 Winery15 PDF

Uploaded by

ronaldovieiraCopyright:

Available Formats

5

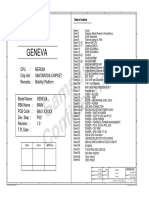

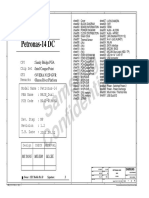

Winery CALPELLA N11M-GE Schematics

Mobile Arrandale

Intel Ibex Peak-M

C

2010-01-18

REV : X-build

B

DY : Nopop Component

UMA : Pop when schematic is UMA

DIS : Pop when schematic is DIS

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

Document Number

Custom

Cover Page

Rev

X01

Vostro Calpella

Date: Monday, January 18, 2010

5

Sheet

1

of

91

CPU DC/DC

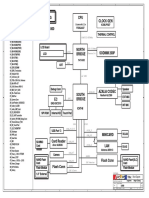

Winery CALPELLA Block Diagram

PCB LAYER

L1:

L2:

L3:

L4:

L5:

L6:

Top

VCC

Signal

Signal

GND

Bottom

Clock Generator

SLG8SP585

Project code

Part Number

PCB P/N

Revision

VRAM

91.4ES01.001

48.4ES11.0SB

09297

SA

Nvidia

N11M-GE(40nm)

DDRIII

1066

100MHz/

2.5Gbps

800/1066MHz

DDR III 1066 Channel B

PCIe x 16

800/1066MHz

Arrandale

LVDS

57

HDMI

RGB CRT

55

LCD

LVDS

54

TPS2231R

Slot 1

New Card

35

RTL8111DL

Switchable74

RGB CRT

Switchable74

LVDS

DMIx4

2.5 GT/s

USB 2.0 x 1

USB 2.0

480Mbps

Free fall sensor

SM Bus

INPUTS

OUTPUTS

+DC_IN

+PBATT

+PWR_SRC

40

CAMERA

USB 2.0 x 1

49

TPS51218

63

INPUTS

400KHz

OUTPUTS

+PWR_SRC

VTT_CORE

73

PCI/PCI BRIDGE

TPM

(only for 15") 76

LPC Bus

33MHz

Digital Mic Array

USB 2.0 x 1

Bluetooth

73

Biometric

78

LDO

(On daughter board)

USB 2.0 x 1

24MHz

51

APL5930

20,21,22,23,24,25,26,27,28

INPUTS

OUTPUTS

+3.3V_ALW

+1.8V_RUN

KBC

SPI

30

SM Bus

NUVOTON

NPCE781BA0DX

SPI

SATA

3Gbps

SATA,USB

OP AMP

LDO

37

Flash ROM

256kB 62

USB,ESATA

Multi-Port x1

2CH SPEAKER

60

63

ODD

HDD59

Touch

PAD

68

Int.

KB

Thermal

& Fan

68

EMC2102

Flash ROM

4MB

INPUTS

OUTPUTS

+3.3V_ALW

+1.8V_RUN_GPU

A

<Core Design>

Wistron Corporation

39,58

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

62

Capacity Board

(On daughter board)

4

87

RT9025

BQ24745

SYSTEM DC/DC

Right Side:

USB x 1

USB 2.0 x 1

ACPI 1.1

Azalia

CODEC

+VCC_GFX_CORE

76

LPC I/F

IDT

92HD81

Left Side:

USB x 2

USB 2.0 x 2

PCIE ports (8)

AZALIA

OUTPUTS

+PWR_SRC

64

Touch Panel

(only for 15")76

USB 2.0 x 1

USB 2.0

SATA ports (6)

(On daughter board)

INPUTS

CHARGER

High Definition Audio

480Mbps

(On daughter board)

Mini-Card

PCIE x 1

86

TPS51218

ETHERNET (10/100/1000Mb)

Realtek

RTS5138

65

WWAN/ WiMAX

14 USB 2.0/1.1 ports

HP OUT

Mini-Card

PCIE x 1

100MHz

2.5Gbps

Intel

PCH

+CPU_GFXCORE

61

802.11a/b/g/n

PCIE

OUTPUTS

+PWR_SRC

SYSTEM DC/DC

USB 2.0 x 1

FDI(UMA)

2.7 GT/s

53

ADP3211

(On daughter board)

CardReader

MIC IN

SYSTEM DC/DC

INPUTS

LVDS

(8 in 1)SD/MMC

MS/MS Pro/xD

+1.5V_SUS

+0.75V_DDR_VTT

+V_DDR_MCH_REF

+PWR_SRC

RJ45

CONN

50

OUTPUTS

19

10/100/1000LOM

PCIE x 1

RGB CRT

+15V_ALW

+3.3V_RTC_LDO

+5V_ALW

+3.3V_ALW

INPUTS

RGB CRT

8,9,10,11,12,13,14

OUTPUTS

TPS51116

Power SW

(On daughter board)

75

CRT

INPUTS

SYSTEM DC/DC

PCIE x 1 & USB 2.0 x 1

HDMI

46

TPS51125

18

80,81,82,83

HDMI

+VCC_CORE

SYSTEM DC/DC

Slot 0

DDRIII

1066

Bandwidth

:8GB

OUTPUTS

+PWR_SRC

Intel CPU

47,48

INPUTS

+PWR_SRC

DDRIII 1066 Channel A

VRAM(gDDR3)

64Mbx16x4 (512MB)484,85

:

:

:

:

ISL62883

Size

Document Number

Custom

Block Diagram

Rev

X01

Vostro Calpella

Date: Monday, January 18, 2010

Sheet

1

of

91

+PWR_SRC

Adapter

TPS51116PWPRG4

50

ISL62883

ADP3211

TPS51218

4748

AO4407A

45

TPS51218DSCR

53

86

49

+V_DDR_MCH_REF

+1.5V_SUS

+0.75V_DDR_VTT

Charger

BQ24745

+PBATT

Battery

+VCC_CORE

+CPU_GFXCORE

+VCC_GFX_CORE

For Intel GPU

For NVIDIA GPU

+1.05V_VTT

FDS8880

87

45

Arrandale

: 1.05V

FDS8880

+1.5V_RUN_GPU

87

TPS51125

46

+1.05V_GFX_PCIE

P2703

52

+5V_ALW

+5V_ALW2

AO4468

+3.3V_RTC_LDO

42

+5V_ALW

+1.5V_CPU

+3.3V_ALW

+15V_ALW

+1.5V_RUN

TPS2062AD

Daughter BD

+5V_USB0

For USB Port1

AO4468

TPS2062AD

42

+5V_RUN

TPS2062AD

63

+5V_USB1

For USB Port2,3

AO3403

63

+5V_USB2

TPS2231R

35

AO4468

Daughter BD

+3.3V_LAN

+3.3V_CARDAUX

APL5930

42

+3.3V_RUN

RT9025

51

+1.8V_RUN

FDS8880

87

TPS2231R

87

Daughter BD

+1.8V_RUN_GPU

+3.3V_RUN_GPU

+1.5V_CARD

For ESATA

RTL8111DL

G5285T11U

54

DVDD12

+LCDVDD

TPS2231R

Daughter BD

+3.3V_CARD

Power Shape

Regulator

LDO

Switch

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Power Block Diagram

Size

Document Number

Custom

Rev

Vostro Calpella

Date: Monday, January 18, 2010

5

Sheet

1

X01

3

of

91

+3.3V_RUN

+3.3V_RUN+3.3V_RUN

PCH

+3.3V_RUN

SRN2K2J-1-GP

SRN2K2J-1-GP

PCH

D

SMBCLK

SMB_CLK

SMBDATA

SMB_DATA

SRN2K2J-1-GP

SRN2K2J-1-GP

+3.3V_RUN

DIMM 1

PCH_SMBDATA

PCH_SMBCLK

+3.3V_RUN

D

SCL

18

SDA

SMBus Address:A0

22

2N7002SPT

PCH_SMBCLK

PCH_SMBDATA

L_DDC_CLK

LDDC_CLK

L_DDC_CLK

B1

L_DDC_DATA

DIMM 2

VCC

B0

GND

NC7SB3157P6X-1GP

SCL

SDA

SRN2K2J-1-GP

19

LDDC_CLK_CON

SMBus Address:A2

Clock

Generator

PCH_SMBCLK

SMBCLK

PCH_SMBDATA SMBDATA

SMB_CLK

PCH_SMBCLK

PCH_SMBDATA

SMB_DATA

PCH_SMBCLK

PCH_SMBDATA

C

PCH_SMBCLK

PCH_SMBDATA

LCD Conn.

54

07

SMB_CLK

SMB_DATA

64

L_DDC_DATA

LDDC_DATA

SMB_CLK

SMB_DATA

B1

VCC

B0

GND

NC7SB3157P6X-1GP

CRT_DDC_CLK

CRT_DDC_DATA

Minicard

WWAN

76

+3.3V_RUN

Minicard

WLAN

SMB_CLK

SMB_DATA

LDDC_DATA_CON

SMBus address:D2

Express

Card

Switchable Graphic SMBus Block Diagram

PCH SMBus Block Diagram

+3.3V_ALW

+3.3V_RUN

+3.3V_RUN

+3.3V_RUN

65

SRN2K2J-1-GP

SRN2K2J-1-GP

Free fall

sensor

SCL/SPC

SDA/SDI/SDO

+3.3V_RUN

DY

+5V_CRT_RUN

C

GMCH_DDCCLK

CRT_CLK_DDC

40

B1

VCC

B0

GND

DDC_CLK_CON2

+3.3V_RUN_GPU

SRN2K2J-1-GP

NC7SB3157P6X-1GP

SDVO_CTRLCLK

SDVO_CTRLDATA

DDC_CLK_CON

CRT CONN

55

KBC SMBus Block Diagram

N11M-GE

+5V_RUN

2N7002DW-1-GP

+3.3V_RUN

I2CC_SCL

I2CC_SDA

GMCH_DDCDATA

CRT_DAT_DDC

B1

VCC

B0

GND

DDC_DATA_CON2

DDC_DATA_CON

NC7SB3157P6X-1GP

TouchPad Conn.

SRN10KJ-5-GP

PSDAT1

B

PSCLK1

TPDATA

TPCLK

TPDATA

TPCLK

+3.3V_RUN

TPDATA

68

TPCLK

I2CA_SCL

I2CA_SDA

+3.3V_RTC_LDO

+3.3V_RUN

+3.3V_RUN

SRN2K2J-1-GP

SRN2K2J-1-GP

SRN2K2J-1-GP

+3.3V_RUN

DY

+5V_RUN

BQ24745

SCL

SDA

SDVO_CLK

HDMI_SCLK_DDC

45

SMBus address:12

SRN4K7J-8-GP

B1

B0

GND

VCC

A

HDMI_SCLK_CON_L

+3.3V_RUN

SRN2K2J-1-GP

NC7SB3157P6X-1GP

Battery Conn.

SCL1

BAT_SCL

SDA1

BAT_SDA

PBAT_SMBCLK1

PBAT_SMBDAT1

CLK_SMB

HDMI_SCLK_CON

44

DAT_SMB

SMBus address:16

SRN100J-3-GP

HDMI

55

2N7002DW-1-GP

KBC

+3.3V_RUN

NPCE781

+3.3V_RTC_LDO

SDVO_DAT

SRN4K7J-8-GP

+3.3V_RUN

SRN4K7J-8-GP

KBC_SCL1

GPIO74/SDA2

KBC_SDA1

HDMI_SDATA_DDC

IFPC_AUX_I2CW_SDA#

Thermal

B1

VCC

B0

GND

HDMI_SDATA_CON_L

NC7SB3157P6X-1GP

GPIO73/SCL2

HDMI_SDATA_CON

IFPC_AUX_I2CW_SCL

+3.3V_RUN

THERM_SCL

SMCLK

THERM_SDA

SMDATA

39

SMBus address:7A

<Core Design>

2N7002DW-1-GP

Capacity

Board

THERM_SCL

THERM_SDA

SCL

SDA

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

(On daughter board)

Title

SMBus address:0A

Size

C

Date:

5

SMBUS Block Diagram

Document Number

Rev

X01

Vostro Calpella

Monday, January 18, 2010

Sheet

1

of

91

Thermal Block Diagram

Audio Block Diagram

0R3-0-U-GP

DP1

SPKR_PORT_D_L+

AUD_SPK_L1

AUD_SPK_L1_R

SPKR_PORT_D_L-

AUD_SPK_L2

AUD_SPK_L2_R

SPKR_PORT_D_R-

AUD_SPK_R2

AUD_SPK_R2_R

SPKR_PORT_D_R+

AUD_SPK_R1

EMC2102_DN1

SPEAKER

AUD_SPK_R1_R

0R3-0-U-V-GP

44

MMBT3904-3-GP

SC470P50V3JN-2GP

2

DN1

EMC2102_DP1

WWAN

Thermal

EMC2102

DP2

VGA_THERMDA

DPLUS

VGA_THERMDC

AUD_HP1_JACK_L

HP1_PORT_B_R

AUD_HP1_JACK_R

HP

OUT

Codec

92HD81

50

GPU

SC470P50V3JN-2GP

DN2

HP1_PORT_B_L

DMINUS

54

HP0_PORT_A_L

AUD_EXT_MIC_L

HP0_PORT_A_R

AUD_EXT_MIC_R

VREFOUT_A_OR_F

AUD_VREFOUT_B

MIC

IN

MMBT3904-3-GP

SC470P50V3JN-2GP

50

3

HW T8 sensor

DP3

CPU_THERMDA

33R2J-2-GP

DMIC_CLK/GPIO1

AUD_DMIC_CLK_G_R

AUD_DMIC_CLK

MMBT3904-3-GP

DMIC0/GPIO2

SC470P50V3JN-2GP

DN3

AUD_DMIC_IN0

CPU_THERMDC

33R2J-2-GP

AUD_DMIC_IN0_R

HW T8 sensor

( CPU )

28

Digital

MIC

Array

47

22

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Thermal/Audio Block Diagram

Size

Document Number

Custom

Rev

X01

Vostro Calpella

Date: Monday, January 18, 2010

A

Sheet

E

of

91

E

Calpella Schematic Checklist Rev.0_7

Calpella Schematic Checklist Rev.0_7

Schematics Notes

Pin Name

Strap Description

Configuration (Default value for each bit is

1 unless specified otherwise)

Default

Value

1: Disabled - No Physical Display Port attached to

Embedded DisplayPort.

0: Enabled - An external Display Port device is

connected to the Embedded Display Port.

1: Normal Operation.

0: Lane Numbers Reversed 15 -> 0, 14 -> 1, ...

SPKR

Reboot option at power-up

Default Mode: Internal weak Pull-down.

No Reboot Mode with TCO Disabled: Connect to Vcc3_3 with 8.2-k

- 10-k weak pull-up resistor.

CFG[4]

Embedded

DisplayPort

Presence

INIT3_3V#

Weak internal pull-down. Do not pull high.

CFG[3]

GNT3#/

GPIO55

Default Mode: Internal pull-up.

Low (0) = Top Block Swap ModeNote: Connect to ground with 4.7-k?

weak pull-down resistor. CRB uses a 1 k

do not stuff resistor.

PCI-Express Static

Lane Reversal

CFG[0]

High (1) = Integrated VRM is enabled

Low (0) = Integrated VRM is disabled

Default (SPI): Left both GNT0# and GNT1# floating. No pull up

required.

Boot from PCI: Connect GNT1# to ground with 1-k pull-down

resistor. Leave GNT0# Floating.

Boot from LPC: Connect both GNT0# and GNT1# to ground with 1-k

pull-down resistor.

Default - Internal pull-up.

Low (0)= Configures DMI for ESI compatible operation (for servers

only. Not for mobile/desktops).

PCI-Express

Configuration

Select

1: Single PCI-Express Graphics

0: Bifurcation enabled

INTVRMEN

CFG[7]

Reserved Temporarily used

for early

Clarksfield

samples.

Clarksfield (only for early samples pre-ES1) Connect to GND with 3.01K Ohm/5% resistor

Note: Only temporary for early CFD samples

(rPGA/BGA) [For details please refer to the WW33

MoW and sighting report].

For a common motherboard design (for AUB and CFD),

the pull-down resistor should be used. Does not

impact AUB functionality.

GNT0#,

GNT1#/GPIO51

GNT2#/

GPIO53

Processor Strapping

PCH Strapping

Name

GPIO33

Default: Do not pull low.

Disable ME in Manufacturing Mode: Connect to ground with 1-k

pull-down resistor.

SPI_MOSI

Enable iTPM: Connect to Vcc3_3 with 8.2-k weak pull-up resistor.

Disable iTPM: Left floating, no pull-down required.

Enable Danbury: Connect to Vcc3_3 with 8.2-k weak pull-up

resistor.

Disable Danbury: Connect to ground with 4.7-k weak pull-down

resistor.

NV_ALE

NC_CLE

Weak internal pull-up. Do not pull low.

HAD_DOCK_EN#

/GPIO[33]

HDA_SDO

Low (0): Flash Descriptor Security will be overridden.

High (1) : Flash Descriptor Security will be in effect.

Weak internal pull-down. Do not pull high.

HDA_SYNC

Weak internal pull-down. Do not pull high.

GPIO15

Weak internal pull-down. Do not pull high.

GPIO8

Weak internal pull-up. Do not pull low.

GPIO27

Default = Do not connect (floating)

High(1) = Enables the internal VccVRM to have a clean supply for

analog rails. No need to use on-board filter circuit.

Low (0) = Disables the VccVRM. Need to use on-board filter

circuits for analog rails.

4

1

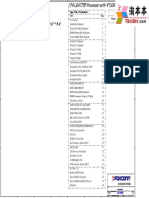

PCIE Routing

LANE1

Card reader

LANE2

MiniCard WLAN

LANE3

LAN

LANE4

MiniCard WWAN

LANE5

New Card

1

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

Document Number

Custom

Table of Content

Rev

X01

Vostro Calpella

Date: Monday, January 18, 2010

Sheet

of

91

DW

DW

12/08 Item 5

12/08 Item 5

+1.05V_RUN_SL585_IO

1

2

CPU_0#

CPU_0

XTAL_IN

XTAL_OUT

28

27

TP_CPU_1#

TP_CPU_1

19

20

CPU_1#

CPU_1

SDA

SCL

31

32

CK_PWRGD

EC701

SC4D7P50V2CN-1GP

Q701

2N7002A-7-GP

VSS_SATA

PCH_SMBDATA [18,19,23,40,64,65]

PCH_SMBCLK [18,19,23,40,64,65]

CLK_XTAL_IN

X701

X-14D31818M-37GP

C714

SC12P50V2JN-3GP

1st Silego 71.08585.003

2nd ICS

71.93197.003

CLK_XTAL_OUT

2

1

VSS_27

8

VSS_DOT

2

VSS_SRC

12

VSS_REF

GND

VSS_CPU

21

26

DY

CLK_XTAL_IN

CLK_XTAL_OUT

R705

10KR2J-3-GP

CLK_PCH_14M [23]

22

23

CLK_VGA_27M [81]

CLK_CPU_BCLK#

CLK_CPU_BCLK

1 33R2J-2-GP

1 33R2J-2-GP

1 33R2J-2-GP

[23] CLK_CPU_BCLK#

[23] CLK_CPU_BCLK

VR_CLKEN# [47]

R703 2

DY

DY

18

15

VDD_SRC_IO

VDD_CPU_IO

+3.3V_RUN

1 2K2R2J-2-GP

SRC_1/SATA#

SRC_1/SATA

33

+3.3V_RUN_SL585

R701 2

11

10

SLG8SP585VTR-GP

Mount

Mount DY

CPU_STOP#

CK_PWRGD

FSC

CLK_PCIE_SATA#

CLK_PCIE_SATA

DY

NON-SS

16

25

30

[23] CLK_PCIE_SATA#

[23] CLK_PCIE_SATA

1

1

SS

R706 2

R710 2

SRC_2#

SRC_2

CPU_STOP#

CKPWRGD/PD#

REF_0/CPU_SEL

R710

CLK_27M

CLK_27M_SS

14

13

27MHZ

27MHZ_SS

R706

6

7

CLKIN_DMI#

CLKIN_DMI

TP701

TP702

C712

SCD1U10V2KX-4GP

DOT_96#

DOT_96

TPAD14-GP

TPAD14-GP

C711

SCD1U10V2KX-4GP

VGA 27M

4

3

[23] CLKIN_DMI#

[23] CLKIN_DMI

C710

DY SC10U6D3V3MX-GP

C709

DYSC1U10V2KX-1GP

+1.05V_RUN_SL585_IO

VDD_27

29

VDD_REF

VDD_DOT

VDD_CPU

U701

DREFCLK#

DREFCLK

1

+3.3V_RUN_SL585

VDD_SRC

C705

SCD1U10V2KX-4GP

DREFCLK#

DREFCLK

C707

SCD1U10V2KX-4GP

17

C703

SCD1U10V2KX-4GP

1

2

C704

SCD1U10V2KX-4GP

C708

SCD1U10V2KX-4GP

24

C702

SC10U10V5ZY-1GP

1

2

C701

SC1U10V2KX-1GP

DY

DY

[23]

[23]

+1.05V_VTT

R709

0R0603-PAD-1-GP

+3.3V_RUN_SL585

R708

0R0603-PAD-1-GP

+3.3V_RUN

C715

SC15P50V2JN-2-GP

+1.05V_VTT

FSC

DY

2 1

R704

4K7R2J-2-GP

FSC

SPEED

133MHz

(Default)

100MHz

R707

10KR2J-3-GP

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

Clock Generator SLG8SP585

Document Number

Rev

Vostro Calpella

Date: Monday, January 18, 2010

5

Sheet

1

X01

of

91

D

1 OF 9

A24

C23

B22

A21

DMI_RX#0

DMI_RX#1

DMI_RX#2

DMI_RX#3

[22]

[22]

[22]

[22]

DMI_PTX_CRXP0

DMI_PTX_CRXP1

DMI_PTX_CRXP2

DMI_PTX_CRXP3

B24

D23

B23

A22

DMI_RX0

DMI_RX1

DMI_RX2

DMI_RX3

[22]

[22]

[22]

[22]

DMI_CTX_PRXN0

DMI_CTX_PRXN1

DMI_CTX_PRXN2

DMI_CTX_PRXN3

D24

G24

F23

H23

DMI_TX#0

DMI_TX#1

DMI_TX#2

DMI_TX#3

[22]

[22]

[22]

[22]

DMI_CTX_PRXP0

DMI_CTX_PRXP1

DMI_CTX_PRXP2

DMI_CTX_PRXP3

D25

F24

E23

G23

DMI_TX0

DMI_TX1

DMI_TX2

DMI_TX3

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

E22

D21

D19

D18

G21

E19

F21

G18

FDI_TX#0

FDI_TX#1

FDI_TX#2

FDI_TX#3

FDI_TX#4

FDI_TX#5

FDI_TX#6

FDI_TX#7

[22]

[22]

[22]

[22]

[22]

[22]

[22]

[22]

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

D22

C21

D20

C18

G22

E20

F20

G19

FDI_TX0

FDI_TX1

FDI_TX2

FDI_TX3

FDI_TX4

FDI_TX5

FDI_TX6

FDI_TX7

[22]

[22]

FDI_FSYNC0

FDI_FSYNC1

F17

E17

FDI_FSYNC0

FDI_FSYNC1

[22]

FDI_INT

C17

FDI_INT

[22]

[22]

FDI_LSYNC0

FDI_LSYNC1

F18

D17

FDI_LSYNC0

FDI_LSYNC1

Calpella Platform Design Guide

Revision 1.6

Page 89

CLARKUNF

2.4 Arrandale Graphics Disable Guideline

It applies to Arrandale and Clarksfield discrete graphic designs.

FDI_TX[7:0] and FDI_TX#[7:0] can be left floating on the Arrandale. The GFX_IMON,

FDI_FSYNC[0], FDI_FSYNC[1], FDI_LSYNC[0], FDI_LSYNC[1], and FDI_INT signals on

the Arrandale side should be tied to GND (through 1-k 5% resistors).

B26

A26

B27

A25

PEG_IRCOMP_R

PEG_RX#0

PEG_RX#1

PEG_RX#2

PEG_RX#3

PEG_RX#4

PEG_RX#5

PEG_RX#6

PEG_RX#7

PEG_RX#8

PEG_RX#9

PEG_RX#10

PEG_RX#11

PEG_RX#12

PEG_RX#13

PEG_RX#14

PEG_RX#15

K35

J34

J33

G35

G32

F34

F31

D35

E33

C33

D32

B32

C31

B28

B30

A31

PCIE_MRX_GTX_N15

PCIE_MRX_GTX_N14

PCIE_MRX_GTX_N13

PCIE_MRX_GTX_N12

PCIE_MRX_GTX_N11

PCIE_MRX_GTX_N10

PCIE_MRX_GTX_N9

PCIE_MRX_GTX_N8

PCIE_MRX_GTX_N7

PCIE_MRX_GTX_N6

PCIE_MRX_GTX_N5

PCIE_MRX_GTX_N4

PCIE_MRX_GTX_N3

PCIE_MRX_GTX_N2

PCIE_MRX_GTX_N1

PCIE_MRX_GTX_N0

PEG_RX0

PEG_RX1

PEG_RX2

PEG_RX3

PEG_RX4

PEG_RX5

PEG_RX6

PEG_RX7

PEG_RX8

PEG_RX9

PEG_RX10

PEG_RX11

PEG_RX12

PEG_RX13

PEG_RX14

PEG_RX15

J35

H34

H33

F35

G33

E34

F32

D34

F33

B33

D31

A32

C30

A28

B29

A30

PCIE_MRX_GTX_P15

PCIE_MRX_GTX_P14

PCIE_MRX_GTX_P13

PCIE_MRX_GTX_P12

PCIE_MRX_GTX_P11

PCIE_MRX_GTX_P10

PCIE_MRX_GTX_P9

PCIE_MRX_GTX_P8

PCIE_MRX_GTX_P7

PCIE_MRX_GTX_P6

PCIE_MRX_GTX_P5

PCIE_MRX_GTX_P4

PCIE_MRX_GTX_P3

PCIE_MRX_GTX_P2

PCIE_MRX_GTX_P1

PCIE_MRX_GTX_P0

PEG_TX#0

PEG_TX#1

PEG_TX#2

PEG_TX#3

PEG_TX#4

PEG_TX#5

PEG_TX#6

PEG_TX#7

PEG_TX#8

PEG_TX#9

PEG_TX#10

PEG_TX#11

PEG_TX#12

PEG_TX#13

PEG_TX#14

PEG_TX#15

L33

M35

M33

M30

L31

K32

M29

J31

K29

H30

H29

F29

E28

D29

D27

C26

PCIE_MTX_GRX_C_N15

PCIE_MTX_GRX_C_N14

PCIE_MTX_GRX_C_N13

PCIE_MTX_GRX_C_N12

PCIE_MTX_GRX_C_N11

PCIE_MTX_GRX_C_N10

PCIE_MTX_GRX_C_N9

PCIE_MTX_GRX_C_N8

PCIE_MTX_GRX_C_N7

PCIE_MTX_GRX_C_N6

PCIE_MTX_GRX_C_N5

PCIE_MTX_GRX_C_N4

PCIE_MTX_GRX_C_N3

PCIE_MTX_GRX_C_N2

PCIE_MTX_GRX_C_N1

PCIE_MTX_GRX_C_N0

C829

C827

C832

C812

C803

C811

C828

C810

C823

C804

C831

C825

C821

C813

C806

C816

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

DIS2

DIS2

DIS2

DIS2

DIS2

DIS2

DIS2

DIS2

DIS2

DIS2

DIS2

DIS2

DIS2

DIS2

DIS2

DIS2

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

PCIE_MTX_GRX_N15

PCIE_MTX_GRX_N14

PCIE_MTX_GRX_N13

PCIE_MTX_GRX_N12

PCIE_MTX_GRX_N11

PCIE_MTX_GRX_N10

PCIE_MTX_GRX_N9

PCIE_MTX_GRX_N8

PCIE_MTX_GRX_N7

PCIE_MTX_GRX_N6

PCIE_MTX_GRX_N5

PCIE_MTX_GRX_N4

PCIE_MTX_GRX_N3

PCIE_MTX_GRX_N2

PCIE_MTX_GRX_N1

PCIE_MTX_GRX_N0

PEG_TX0

PEG_TX1

PEG_TX2

PEG_TX3

PEG_TX4

PEG_TX5

PEG_TX6

PEG_TX7

PEG_TX8

PEG_TX9

PEG_TX10

PEG_TX11

PEG_TX12

PEG_TX13

PEG_TX14

PEG_TX15

L34

M34

M32

L30

M31

K31

M28

H31

K28

G30

G29

F28

E27

D28

C27

C25

PCIE_MTX_GRX_C_P15

PCIE_MTX_GRX_C_P14

PCIE_MTX_GRX_C_P13

PCIE_MTX_GRX_C_P12

PCIE_MTX_GRX_C_P11

PCIE_MTX_GRX_C_P10

PCIE_MTX_GRX_C_P9

PCIE_MTX_GRX_C_P8

PCIE_MTX_GRX_C_P7

PCIE_MTX_GRX_C_P6

PCIE_MTX_GRX_C_P5

PCIE_MTX_GRX_C_P4

PCIE_MTX_GRX_C_P3

PCIE_MTX_GRX_C_P2

PCIE_MTX_GRX_C_P1

PCIE_MTX_GRX_C_P0

C826

C822

C818

C815

C808

C802

C820

C805

C817

C801

C814

C824

C830

C809

C807

C819

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

DIS2

DIS2

DIS2

DIS2

DIS2

DIS2

DIS2

DIS2

DIS2

DIS2

DIS2

DIS2

DIS2

DIS2

DIS2

DIS2

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

PCIE_MTX_GRX_P15

PCIE_MTX_GRX_P14

PCIE_MTX_GRX_P13

PCIE_MTX_GRX_P12

PCIE_MTX_GRX_P11

PCIE_MTX_GRX_P10

PCIE_MTX_GRX_P9

PCIE_MTX_GRX_P8

PCIE_MTX_GRX_P7

PCIE_MTX_GRX_P6

PCIE_MTX_GRX_P5

PCIE_MTX_GRX_P4

PCIE_MTX_GRX_P3

PCIE_MTX_GRX_P2

PCIE_MTX_GRX_P1

PCIE_MTX_GRX_P0

Intel(R) FDI

[22]

[22]

[22]

[22]

[22]

[22]

[22]

[22]

PCI EXPRESS -- GRAPHICS

DMI_PTX_CRXN0

DMI_PTX_CRXN1

DMI_PTX_CRXN2

DMI_PTX_CRXN3

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

DMI

[22]

[22]

[22]

[22]

CLARKSFIELD

CPU1A

R801 1

R802 1

2 49D9R2F-GP

2 750R2F-GP

EXP_RBIAS

PCIE_MRX_GTX_N[0..15]

PCIE_MRX_GTX_P[0..15]

PCIE_MRX_GTX_N[0..15] [80]

PCIE_MRX_GTX_P[0..15] [80]

PCIE_MTX_GRX_N[0..15]

PCIE_MTX_GRX_N[0..15] [80]

B

PCIE_MTX_GRX_P[0..15]

PCIE_MTX_GRX_P[0..15] [80]

Reversal

1.PCI-Express Static Lane Reversal

(15 -> 0, 14 -> 1, ...)

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

CPU (PCIE/DMI/FDI)

Document Number

Rev

Vostro Calpella

Date: Monday, January 18, 2010

Sheet

X01

of

91

2

DPLL_REF_SSCLK#_R1

DPLL_REF_SSCLK_R 2

Processor Compensation Signals

R905

R906

R904 1

DY 2

68R2-GP

COMP2

H_COMP1

G16

COMP1

H_COMP0

AT26

COMP0

20R2F-GP

49D9R2F-GP

49D9R2F-GP

H_CPURST#

TPAD14-GP

TP901

SKTOCC#_R

AH24

H_CATERR#

R936

0R2J-2-GP

1

DY

[47] H_PROCHOT#

H_PROCHOT_R#

H_CPURST#

R908

0R0402-PAD

1

2

PECI

AK15

AP26

[22] H_PM_SYNC

AT15

VCCPWRGOOD

PROCHOT#

THERMTRIP#

RESET_OBS#

AL15

PM_SYNC

AN14

VCCPWRGOOD_1

AN27

VCCPWRGOOD_0

[22] PM_DRAM_PWRGD

PM_DRAM_PWRGD AK13

SM_DRAMPWROK

[49] H_VTTPWRGD

AM15

VTTPWRGOOD

H_PWRGD_XDPAM26

TAPPWRGOOD

[25,42] H_PWRGOOD

PLT_RST#

PLT_RST#_R

AL14

AR30

AT30

PEG_CLK

PEG_CLK#

E16

D16

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

A18

A17

BCLK_CPU_P [25]

BCLK_CPU_N [25]

BCLK_ITP_CPU_P R939 1

BCLK_ITP_CPU_N R940 1

R915

750R2F-GP

+1.5V_RUN

0R2J-2-GP

2

0R2J-2-GP

2

S3 circuit

Normal

+1.5V_SUS

R934

1KR2J-1-GP

S

SM_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

+1.05V_VTT

SM_DRAMRST#

F6

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

4

3

AN15

AP15

PRDY#

PREQ#

AT28

AP27

XDP_PRDY#

XDP_PREQ#

TCK

TMS

TRST#

AN28

AP28

AT27

XDP_TCLK

XDP_TMS

XDP_TRST#

TDI

TDO

TDI_M

TDO_M

AT29

AR27

AR29

AP29

XDP_TDI_R

XDP_TDO_R

XDP_TDI_M

XDP_TDO_M

DBR#

AN25

H_DBR#_R

1

2

DY

1

2

R935

0R2J-2-GP

PM_EXTTS#0 [18]

PM_EXTTS#1 [19]

R907 1

2 100R2F-L1-GP-U

R910 1

2 24D9R2F-L-GP

SM_RCOMP_2

R911 1

2 130R2F-1-GP

DW

10/26 Item 31

XDP_OBS0

XDP_OBS1

XDP_OBS2

XDP_OBS3

XDP_OBS4

XDP_OBS5

XDP_OBS6

XDP_OBS7

RSTIN#

[25,37,49,50]

R988

100KR2J-1-GP

SM_RCOMP_1

VTT_PWRGD

+3.3V_ALW

R2114 1

2 10KR2J-3-GP

U927_B 1

+1.05V_VTT

XDP_TMS

R914

VCC

VTT_PWRGD_R3 2

R977

1K6R2F-GP

1

XDP_TDI_R

R916

PM_DRAM_PWRGD

XDP_PREQ#

R917

GND

XDP_TCLK

74LVC1G08GW-1-GP

1.1k

0.75k

No Stuff

1.27k

3k

Calpella Platform S3 Power Reduction Platform

S3 Power Reduction CRB Implementation

Design Details

Revision 0.1

XDP_DBRESET# [22,25]

U927

CLARKUNF

DDR3 Compensation Signals

R909

AJ22

AK22

AK24

AJ24

AJ25

AH22

AK23

AH23

SM_DRAMRST#

0611

SM_RCOMP_0

0R2J-2-GP

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

DDR3_DRAMRST# [18,19]

Q901

BSS138-7-F-GP

SRN10KJ-5-GP

PM_EXT_TS#0

PM_EXT_TS#1

Vgs(th)<=1.5V

RN905

AL1

AM1

AN1

R918

1

1

1

1

DY 2

DY 2

DY 2

DY 2

51R2J-2-GP

51R2J-2-GP

51R2J-2-GP

51R2J-2-GP

R919

1K1R2F-GP

R920

BCLK_ITP_P

BCLK_ITP_N

DPLL_REF_SSCLK_R

DPLL_REF_SSCLK#_R

R919

DY

DY

DY

C915

SCD047U16V2ZY-1GP

CLK_EXP_P [23]

CLK_EXP_N [23]

[21,37,64,65,70,76,77,80]

R913

1K6R2F-GP

1

2

A16

B16

BCLK_ITP

BCLK_ITP#

PWR MANAGEMENT

DY

CATERR#

AN26

[25,37,42] H_THRMTRIP#

R931

1KR2J-1-GP

XDP_RST#_R

1

AK14

THERMAL

[25] H_PECI

SKTOCC#

DDR_RST_GATE [25]

SRN1KJ-7-GP

BCLK

BCLK#

R903

AT24

H_PROCHOT_R#

H_COMP2

2 68R2-GP

COMP3

4

3

R933 1

AT23

CLOCKS

H_CATERR#

H_COMP3

20R2F-GP

DDR3

MISC

2 49D9R2F-GP

JTAG & BPM

R902 1

MISC

R901

2 OF 9

CPU1B

Processor Pullups

CLARKSFIELD

+1.05V_VTT

RN907

PM_DRAM_PWRGD

H_PWRGOOD

1

R927 1

R929

H_PWRGD_XDP

1

R930

[22] PM_PWRBTN#_R

C902

[23] SML0_DATA

SCD1U16V2KX-3GP

[23] SML0_CLK

DY

DY

DY

DY

DY

DY

DY

XDP_TDI_M

TCK(PIN AN28)

XDP_TDO_R

DY 2

1

R926

GMCH Only

C901

SCD1U16V2KX-3GP

DY

BCLK_ITP_P

BCLK_ITP_N

XDP_TDI

XDP_TRST#

0R2J-2-GP

XDP_TDO

R923

51R2J-2-GP

0R2J-2-GP

2

1

R925

Scan Chain

(Default)

CPU Only

+1.05V_VTT

DY

R924

0R2J-2-GP

XDP Connector

TCK(PIN 57)

0R2J-2-GP

0R2J-2-GP

Stuff --> R921, R924, R926

No Stuff --> R922, R925

Stuff --> R921, R922

No Stuff --> R924, R926, R925

Stuff --> R926, R925

No Stuff --> R921, R922, R924

JTAG MAPPING

3

5

7

9

11

13

XDP_OBS2

15

XDP_OBS3

17

19

21

23

25

XDP_OBS4

27

XDP_OBS5

29

31

XDP_OBS6

33

XDP_OBS7

35

37

H_CPUPWRGD_XDP

2

39

2 1KR2J-1-GP PM_PWRBTN#_XDP

41

0R2J-2-GP

43

H_PWRGD_XDP_R

2

45

0R2J-2-GP

47

49

R937 1

0R2J-2-GP

SML0_DATA_XDP 51

2

SML0_CLK_XDP 53

R938 1

0R2J-2-GP

2

55

XDP_TCLK

57

59

XDP_OBS0

XDP_OBS1

1

R922

R928

51R2J-2-GP

<Core Design>

XDP_RST#_R

XDP_PREQ#

XDP_PRDY#

CPU

1

R921

XDP_TDO_M

NP1

61

2

62

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

63

64

NP2

XDP_TDI_R

XDP1

+1.05V_VTT

+1.05V_VCCP use Decoupling Capacitor close

ITP connector 100 mil ( max )

XDP Connector

R920

750R2F-GP

XDP_DBRESET# [22,25]

Wistron Corporation

XDP_TDO

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

XDP_TRST#

XDP_TDI

XDP_TMS

Title

XDP_RST#_R

1

R932

2

DY0R2J-2-GP

Size

PLT_RST# [21,37,64,65,70,76,77,80]

CPU (THERMAL/CLOCK/PM )

Document Number

Date: Monday, January 18, 2010

Rev

Vostro Calpella

STC-CONN60A-GP-U1

Sheet

of

X01

91

4 OF 9

CPU1D

3 OF 9

[18]

[18]

[18]

[18]

[18]

[18]

M_A_BS0

M_A_BS1

M_A_BS2

AC3

AB2

U7

M_A_CAS#

M_A_RAS#

M_A_WE#

AE1

AB3

AE9

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

SA_CK1

SA_CK#1

SA_CKE1

M_CLK_DDR1 [18]

M_CLK_DDR#1 [18]

M_CKE1 [18]

SA_CS#0

SA_CS#1

AE2

AE8

M_CS0# [18]

M_CS1# [18]

SA_ODT0

SA_ODT1

AD8

AF9

M_ODT0 [18]

M_ODT1 [18]

B9

D7

H7

M7

AG6

AM7

AN10

AN13

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_CLK_DDR0 [18]

M_CLK_DDR#0 [18]

M_CKE0 [18]

Y6

Y5

P6

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

M_B_DQ[63..0]

[19] M_B_DQ[63..0]

AA6

AA7

P7

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DM[7..0] [18]

M_A_DQS#[7..0] [18]

M_A_DQS[7..0] [18]

SA_BS0

SA_BS1

SA_BS2

SA_CAS#

SA_RAS#

SA_WE#

SA_DQS#0

SA_DQS#1

SA_DQS#2

SA_DQS#3

SA_DQS#4

SA_DQS#5

SA_DQS#6

SA_DQS#7

C9

F8

J9

N9

AH7

AK9

AP11

AT13

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

C8

F9

H9

M9

AH8

AK10

AN11

AR13

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_A[15..0] [18]

B5

A5

C3

B3

E4

A6

A4

C4

D1

D2

F2

F1

C2

F5

F3

G4

H6

G2

J6

J3

G1

G5

J2

J1

J5

K2

L3

M1

K5

K4

M4

N5

AF3

AG1

AJ3

AK1

AG4

AG3

AJ4

AH4

AK3

AK4

AM6

AN2

AK5

AK2

AM4

AM3

AP3

AN5

AT4

AN6

AN4

AN3

AT5

AT6

AN7

AP6

AP8

AT9

AT7

AP9

AR10

AT10

CLARKSFIELD

A10

C10

C7

A7

B10

D10

E10

A8

D8

F10

E6

F7

E9

B7

E7

C6

H10

G8

K7

J8

G7

G10

J7

J10

L7

M6

M8

L9

L6

K8

N8

P9

AH5

AF5

AK6

AK7

AF6

AG5

AJ7

AJ6

AJ10

AJ9

AL10

AK12

AK8

AL7

AK11

AL8

AN8

AM10

AR11

AL11

AM9

AN9

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AL13

AR14

AP14

CLARKSFIELD

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

DDR SYSTEM MEMORY A

M_A_DQ[63..0]

[18] M_A_DQ[63..0]

D

SA_CK0

SA_CK#0

SA_CKE0

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

[19]

[19]

[19]

M_B_BS0

M_B_BS1

M_B_BS2

AB1

W5

R7

SB_BS0

SB_BS1

SB_BS2

[19]

[19]

[19]

M_B_CAS#

M_B_RAS#

M_B_WE#

AC5

Y7

AC6

SB_CAS#

SB_RAS#

SB_WE#

SB_CK0

SB_CK#0

SB_CKE0

W8

W9

M3

M_CLK_DDR2 [19]

M_CLK_DDR#2 [19]

M_CKE2 [19]

SB_CK1

SB_CK#1

SB_CKE1

V7

V6

M2

M_CLK_DDR3 [19]

M_CLK_DDR#3 [19]

M_CKE3 [19]

SB_CS#0

SB_CS#1

AB8

AD6

M_CS2# [19]

M_CS3# [19]

SB_ODT0

SB_ODT1

AC7

AD1

M_ODT2 [19]

M_ODT3 [19]

SB_DM0

SB_DM1

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SB_DM6

SB_DM7

D4

E1

H3

K1

AH1

AL2

AR4

AT8

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

SB_DQS#0

SB_DQS#1

SB_DQS#2

SB_DQS#3

SB_DQS#4

SB_DQS#5

SB_DQS#6

SB_DQS#7

D5

F4

J4

L4

AH2

AL4

AR5

AR8

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

C5

E3

H4

M5

AG2

AL5

AP5

AR7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

U5

V2

T5

V3

R1

T8

R2

R6

R4

R5

AB5

P3

R3

AF7

P5

N1

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DM[7..0] [19]

M_B_DQS#[7..0] [19]

M_B_DQS[7..0] [19]

DDR SYSTEM MEMORY - B

CPU1C

M_B_A[15..0] [19]

CLARKUNF

CLARKUNF

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

Document Number

CPU (DDR)

Rev

Vostro Calpella

Date: Monday, January 18, 2010

5

Sheet

1

10

X01

of

91

5 OF 9

CPU1E

CFG0

1

1

SA_DIMM_VREF#

SB_DIMM_VREF#

1:Single PEG

0:Bifurcation enabled

DY

TP1116

TP1117

PCI-Express Configuration Select

R1101

3KR2F-GP

CFG0

DIS

5%

CFG3

CFG4

CFG3

CFG3 - PCI-Express Static Lane Reversal

CFG7

R1102

3KR2F-GP

CFG3

2

1 :Normal Operation

0 :Lane Numbers Reversed

15 -> 0, 14 -> 1, ...

RSVD#AP25

RSVD#AL25

RSVD#AL24

RSVD#AL22

RSVD#AJ33

RSVD#AG9

RSVD#M27

RSVD#L28

SA_DIMM_VREF

SB_DIMM_VREF

RSVD#G25

RSVD#G17

RSVD#E31

RSVD#E30

AM30

AM28

AP31

AL32

AL30

AM31

AN29

AM32

AK32

AK31

AK28

AJ28

AN30

AN32

AJ32

AJ29

AJ30

AK30

H16

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

RSVD_TP_86

CFG4

CFG4 - Display Port Presence

CFG4

DY

R1103

3KR2F-GP

1:Disabled; No Physical Display Port

attached to Embedded Display Port

0:Enabled; An external Display Port

device is connected to the Embedded

Display Port

B19

A19

RSVD#B19

RSVD#A19

A20

B20

RSVD#A20

RSVD#B20

U9

T9

RSVD#U9

RSVD#T9

AC9

AB9

RSVD#AC9

RSVD#AB9

Calpella Platform Design Guide

Revision 1.6

4.8.3.1

LVDS Switching

J29

J28

Switchable GFX, just like integrated GFX only, to enable LVDS it is required that the

OEM set the LDVS (L_DDC_DATA) strap to present (pulled up) and the eDP strap

(CFG[4]) to disabled (not pulled down).

4.8.3.2

RSVD#J29

RSVD#J28

eDP Switching

eDP for Switchable GFX can only be driven out of Port D of PCH. To configure Port D for

embedded DP it is required to set the DDPD_CTRLDATA strap high to 3.3V Core rail

through 2.2 k 5% resistor, LVDS (L_DDC_DATA) strap as no connect and the eDP

strap CFG[4] as no connect.

Page 482,486

RESERVED

CFG0

AP25

AL25

AL24

AL22

AJ33

AG9

M27

L28

J17

H17

G25

G17

E31

E30

CLARKSFIELD

RSVD#AJ13

RSVD#AJ12

AJ13

AJ12

RSVD#AH25

RSVD#AK26

AH25

AK26

RSVD#AL26

RSVD_NCTF_37

AL26

AR2

RSVD#AJ26

RSVD#AJ27

AJ26

AJ27

RSVD#AL28

RSVD#AL29

RSVD#AP30

RSVD#AP32

RSVD#AL27

RSVD#AT31

RSVD#AT32

RSVD#AP33

RSVD#AR33

AL28

AL29

AP30

AP32

AL27

AT31

AT32

AP33

AR33

RSVD#AR32

AR32

RSVD_TP#E15

RSVD_TP#F15

KEY

RSVD#D15

RSVD#C15

RSVD#AJ15

RSVD#AH15

E15

F15

A2

D15

C15

AJ15

AH15

SA_CK2

SA_CK#2

SA_CKE2

SA_CS#2

SA_ODT2

SA_CK3

SA_CK#3

SA_CKE3

SA_CS#3

SA_ODT3

AA5

AA4

R8

AD3

AD2

AA2

AA1

R9

AG7

AE3

SB_CK2

SB_CK#2

SB_CKE2

SB_CS#2

SB_ODT2

SB_CK3

SB_CK#3

SB_CKE3

SB_CS#3

SB_ODT3

V4

V5

N2

AD5

AD7

W3

W2

N3

AE5

AD9

VSS

VSS (AP34) can be left NC is

CRB implementation; EDS/DG

recommendation to GND.

AP34

CLARKUNF

CFG7

CFG7(Reserved) - Temporarily used for early

Clarksfield samples.

TP1118

TPAD14-GP

CFG7

Clarksfield (only for early samples pre-ES1) Connect to GND with 3.01K Ohm/5% resistor.

Note: Only temporary for early CFD sample

(rPGA/BGA) [For details please refer to the

WW33 MoW and sighting report].

For a common M/B design (for AUB and CFD),

the pull-down resistor shouble be used. Does

not impact AUB functionality.

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

CPU (RESERVED)

Document Number

Rev

X01

Vostro Calpella

Date: Monday, January 18, 2010

5

Sheet

1

11

of

91

CLARKSFIELD

1

2

1

2

1

2

C1221

1

2

1

2

1.1V RAIL POWER

TP_H_VTTVID1

The decoupling capacitors, filter

recommendations and sense resistors on the

CPU/PCH Rails are specific to the CRB

Implementation. Customers need to follow the

recommendations in the Calpella Platform

Design Guide.

C1222

CPU VIDS

VTT_SELECT

2

PSI#

C1233

DY

C1234

+1.05V_VTT

[47]

CPU_VID[6..0]

[47]

PM_DPRSLPVR [47]

B

TP1203

TPAD14-GP

+VCC_CORE

VCC_SENSE

VSS_SENSE

AJ34

AJ35

R1201

100R2F-L1-GP-U

IMVP_IMON [47]

AN35

VCC_SENSE

VSS_SENSE

VCC_SENSE [47]

VSS_SENSE [47]

ISENSE

VTT_SENSE

VSS_SENSE_VTT

B15

A15

TP_VSS_SENSE_VTT 1

R1204

100R2F-L1-GP-U

VTT_SENSE [49]

TP1202

TPAD14-GP

POWER

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

G15

C1211

SC10U6D3V5KX-1GP

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

CPU_VID5

CPU_VID6

DY

SC10U6D3V5KX-1GP

AK35

AK33

AK34

AL35

AL33

AM33

AM35

AM34

C1205

DY

SC10U6D3V5KX-1GP

AN33

VID

VID

VID

VID

VID

VID

VID

PROC_DPRSLPVR

C1204

SC22U6D3V5MX-2GP

SC10U6D3V5MX-3GP

PSI#

C1203

DY

SC10U6D3V5KX-1GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC10U6D3V5KX-1GP

SC22U6D3V5MX-2GP

C1243

DY

AF10

AE10

AC10

AB10

Y10

W10

U10

T10

J12

J11

J16

J15

C1218

DY

+1.05V_VTT

SC10U6D3V5KX-1GP

C1242

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

CPU CORE SUPPLY

C1241

C1232

SC10U6D3V5KX-1GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C1240

C1231

C1217

SC10U6D3V5KX-1GP

C1230

C1201

SC10U6D3V5KX-1GP

C1224

C1216

SC10U6D3V5KX-1GP

DY

SC22U6D3V5MX-2GP

C1239

DY

C1210

SC10U6D3V5KX-1GP

C1229

SC22U6D3V5MX-2GP

C1238

C1223

SC22U6D3V5MX-2GP

C1228

C1220

SC22U6D3V5MX-2GP

C1215

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C1237

DY

SC22U6D3V5MX-2GP

C1227

C1209

SC10U6D3V5KX-1GP

C1214

SC22U6D3V5MX-2GP

C1236

C1208

SC22U6D3V5MX-2GP

C1235

DY

C1226

SC10U6D3V5KX-1GP

SC22U6D3V5MX-2GP

C1213

SC22U6D3V5MX-2GP

SC10U6D3V5KX-1GP

C1225

SC22U6D3V5MX-2GP

SC10U6D3V5KX-1GP

C1212

DY

C1207

AH14

AH12

AH11

AH10

J14

J13

H14

H12

G14

G13

G12

G11

F14

F13

F12

F11

E14

E12

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

SC22U6D3V5MX-2GP

C1206

+1.05V_VTT

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

SC10U6D3V5KX-1GP

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

SC10U6D3V5KX-1GP

48A

+VCC_CORE

AG35

AG34

AG33

AG32

AG31

AG30

AG29

AG28

AG27

AG26

AF35

AF34

AF33

AF32

AF31

AF30

AF29

AF28

AF27

AF26

AD35

AD34

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AD26

AC35

AC34

AC33

AC32

AC31

AC30

AC29

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

Y35

Y34

Y33

Y32

Y31

Y30

Y29

Y28

Y27

Y26

V35

V34

V33

V32

V31

V30

V29

V28

V27

V26

U35

U34

U33

U32

U31

U30

U29

U28

U27

U26

R35

R34

R33

R32

R31

R30

R29

R28

R27

R26

P35

P34

P33

P32

P31

P30

P29

P28

P27

P26

SENSE LINES

+VCC_CORE

6 OF 9

CPU1F

PROCESSOR CORE POWER

<Core Design>

CLARKUNF

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

CPU (VCC_CORE)

Document Number

Rev

X01

Vostro Calpella

Date: Monday, January 18, 2010

5

Sheet

1

12

of

91

1

2

2

AR25

AT25

AM24

+1.5V_SUS

SCD1U10V2KX-4GP

+1.5V_SUS

425302_425302_Calpella_S3PowerReduction_WhitePape

C1307

C1306

TC1301

SE330U2VDM-L-GP

C1305

C1304

C1303

C1302

C1301

VCCPLL

VCCPLL

VCCPLL

L26

L27

M26

+1.5V_RUN

3A

2

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

J22

J20

J18

H21

H20

H19

GFX_IMON [53]

C1310

SC10U6D3V5MX-3GP

+1.05V_VTT

C1311

SC10U6D3V5KX-1GP

DY

2

VTT0

VTT0

VTT0

VTT0

P10

N10

L10

K10

GFX_VR_EN [53]

TP1303TPAD14-GP

TP_GFX_DPRSLPVR1

SC10U6D3V5KX-1GP

AJ1

AF1

AE7

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

[53]

[53]

[53]

[53]

[53]

[53]

[53]

SC22U6D3V5MX-2GP

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GFX_VID0

GFX_VID1

GFX_VID2

GFX_VID3

GFX_VID4

GFX_VID5

GFX_VID6

SC1U6D3V2KX-GP

- 1.5V RAILS

Revision 0.7

DDR3

SENSE

LINES

GFX_VR_EN

GFX_DPRSLPVR

GFX_IMON

DYC1379

SCD1U10V2KX-4GP

VCC_AXG_SENSE [53]

VSS_AXG_SENSE [53]

SC1U6D3V2KX-GP

GFX_VID

GFX_VID

GFX_VID

GFX_VID

GFX_VID

GFX_VID

GFX_VID

AM22

AP22

AN22

AP23

AM23

AP24

AN24

+1.5V_RUN

DYC1378

SCD1U10V2KX-4GP

+1.5V_SUS

SC1U6D3V2KX-GP

VTT1

VTT1

VTT1

FDI

C1309

SC10U6D3V5KX-1GP

J24

J23

H25

AR22

AT22

SC1U6D3V2KX-GP

+1.05V_VTT

VAXG_SENSE

VSSAXG_SENSE

DYC1377

C1376

SC56P25V2JN-GP

+1.5V_SUS

SC1U6D3V2KX-GP

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

GRAPHICS

Please note that the VTT Rail

Values are

Arrandale VTT=1.05V;

Clarksfield VTT=1.1V

AT21

AT19

AT18

AT16

AR21

AR19

AR18

AR16

AP21

AP19

AP18

AP16

AN21

AN19

AN18

AN16

AM21

AM19

AM18

AM16

AL21

AL19

AL18

AL16

AK21

AK19

AK18

AK16

AJ21

AJ19

AJ18

AJ16

AH21

AH19

AH18

AH16

GRAPHICS VIDs

1

2

1

2

1

2

C1328

SC10U6D3V5MX-3GP

C1326

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SE330U2VDM-L-GP

DY

C1327

CLARKSFIELD

22A

TC1303

7 OF 9

CPU1G

POWER

+CPU_GFXCORE

+1.5V_RUN

+1.5V_RUN

+1.5V_RUN

1

2

DY

B

+1.8V_RUN

C1321

SC2D2U10V3KX-1GP

C1322

SC10U6D3V5MX-3GP

C1320

SC4D7U6D3V5KX-3GP

SC1U25V5KX-1GP

C1319

C1318

DY DY

1.35A

SC1U25V5KX-1GP

CLARKUNF

C1316

SC10U6D3V5MX-3GP

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

1.8V

1

2

C1315

SC22U6D3V5MX-2GP

C1314

SC10U6D3V5KX-1GP

C1312

SC10U6D3V5KX-1GP

K26

J27

J26

J25

H27

G28

G27

G26

F26

E26

E25

PEG & DMI

18A

1.1V

+1.05V_VTT

+1.05V_VTT

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

CPU (VCC_GFXCORE)

Document Number

Rev

Vostro Calpella

Date: Monday, January 18, 2010

5

Sheet

1

13

X01

of

91

VSS

K27

K9

K6

K3

J32

J30

J21

J19

H35

H32

H28

H26

H24

H22

H18

H15

H13

H11

H8

H5

H2

G34

G31

G20

G9

G6

G3

F30

F27

F25

F22

F19

F16

E35

E32

E29

E24

E21

E18

E13

E11

E8

E5

E2

D33

D30

D26

D9

D6

D3

C34

C32

C29

C28

C24

C22

C20

C19

C16

B31

B25

B21

B18

B17

B13

B11

B8

B6

B4

A29

A27

A23

A9

CLARKUNF

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

CLARKSFIELD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

9 OF 9

CPU1I

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE6

AD10

AC8

AC4

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

AB6

AA10

Y8

Y4

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

W6

V10

U8

U4

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

T6

R10

P8

P4

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

N6

M10

L35

L32

L29

L8

L5

L2

K34

K33

K30

VSS

NCTF

CLARKSFIELD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

8 OF 9

CPU1H

AT20

AT17

AR31

AR28

AR26

AR24

AR23

AR20

AR17

AR15

AR12

AR9

AR6

AR3

AP20

AP17

AP13

AP10

AP7

AP4

AP2

AN34

AN31

AN23

AN20

AN17

AM29

AM27

AM25

AM20

AM17

AM14

AM11

AM8

AM5

AM2

AL34

AL31

AL23

AL20

AL17

AL12

AL9

AL6

AL3

AK29

AK27

AK25

AK20

AK17

AJ31

AJ23

AJ20

AJ17

AJ14

AJ11

AJ8

AJ5

AJ2

AH35

AH34

AH33

AH32

AH31

AH30

AH29

AH28

AH27

AH26

AH20

AH17

AH13

AH9

AH6

AH3

AG10

AF8

AF4

AF2

AE35

NCYF TEST PIN:

A35,AT1,AT35,B1,A3,A33,A34,

AP1,AP35,AR1,AR35,AT2,AT3,

AT33,AT34,C1,C35,B35

VSS_NCTF

VSS_NCTF

VSS_NCTF

AR34

B34

B2

VSS_NCTF#A35

VSS_NCTF#AT1

VSS_NCTF#AT35

VSS_NCTF#B1

RSVD_NCTF#A3

RSVD_NCTF#A33

RSVD_NCTF#A34

RSVD_NCTF#AP1

RSVD_NCTF#AP35

RSVD_NCTF#AR1

RSVD_NCTF#AR35

RSVD_NCTF#AT2

RSVD_NCTF#AT3

RSVD_NCTF#AT33

RSVD_NCTF#AT34

RSVD_NCTF#C1

RSVD_NCTF#C35

RSVD_NCTF#B35

A35

AT1

AT35

B1

A3

A33

A34

AP1

AP35

AR1

AR35

AT2

AT3

AT33

AT34

C1

C35

B35

TP_MCP_VSS_NCTF2

TP_MCP_VSS_NCTF3

TP_MCP_VSS_NCTF4

TP_MCP_VSS_NCTF1

1

1

1

1

TP1402

TP1406

TP1405

TP1401

CLARKUNF

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

CPU (VSS)

Size

Document Number

Rev

Vostro Calpella

Date: Monday, January 18, 2010

5

Sheet

1

14

of

X01

91

(Blanking)

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

A3

Document Number

Date: Monday, January 18, 2010

5

Reserved

Rev

Vostro Calpella

Sheet

1

15

X01

of

91

(Blanking)

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

A3

Document Number

Date: Monday, January 18, 2010

5

Reserved

Rev

Vostro Calpella

Sheet

1

16

X01

of

91

(Blank)

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

Document Number

Custom

(Reserve)

Rev

X01

Vostro Calpella

Date: Monday, January 18, 2010

5

Sheet

1

17

of

91

DM1

[10] M_A_A[15..0]

M_A_BS0

M_A_BS1

M_A_BS2

[10]

[10]

Layout Note:

Place near DM1

+1.5V_SUS

DY

2

DY

2

[10]

TC1803

ST330U2D5VBM-1-GP

C1803

SC10U6D3V5MX-3GP

C1812

SC10U6D3V5MX-3GP

C1804

SC10U6D3V5MX-3GP

C1811

SC10U6D3V5MX-3GP

C1802

SC10U6D3V5MX-3GP

C1816

SC10U6D3V5MX-3GP

C1814

SC1U10V2KX-1GP

1

2

1

2

1

2

1

2

1

2

C1813

SC1U10V2KX-1GP

C1823

SC10U6D3V5MX-3GP

C1801

SC1U10V2KX-1GP

C1815

SC1U10V2KX-1GP

DY C1873

DY C1874

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

1

C1872

SCD1U10V2KX-4GP

+1.5V_SUS

C1875

SCD1U10V2KX-4GP

425302_425302_Calpella_S3PowerReduction_WhitePape

Revision 0.7

DY

2

C1810

SCD1U16V2KX-3GP

+V_DDR_REF

C1809

SC2D2U10V3KX-1GP

[10]

[10]

M_ODT0

M_ODT1

BA0

BA1

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

5

7

15

17

4

6

16

18

21

23

33

35

22

24

34

36

39

41

51

53

40

42

50

52

57

59

67

69

56

58

68

70

129

131

141

143

130

132

140

142

147

149

157

159

146

148

158

160

163

165

175

177

164

166

174

176

181

183

191

193

180

182

192

194

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

10

27

45

62

135

152

169

186

DQS0#

DQS1#

DQS2#

DQS3#

DQS4#

DQS5#

DQS6#

DQS7#

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

12

29

47

64

137

154

171

188

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

M_ODT0

M_ODT1

116

120

ODT0

ODT1

126

1

VREF_CA

VREF_DQ

+V_DDR_REF

30

203

204

C1805

SC2D2U10V3KX-1GP

110

113

115

CS0#

CS1#

114

121

CKE0

CKE1

73

74

CK1

CK1#

102

104

M_CLK_DDR1

M_CLK_DDR#1

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

11

28

46

63

136

153

170

187

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

SDA

SCL

200

202

PCH_SMBDATA

PCH_SMBCLK

199

SA0

SA1

197

201

NC#1

NC#2

NC#/TEST

77

122

125

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

75

76

81

82

87

88

93

94

99

100

105

106

111

112

117

118

123

124

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

2

3

8

9

13

14

19

20

25

26

31

32

37

38

43

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

205

206