Professional Documents

Culture Documents

Stick Diagrams Layout Planning

Uploaded by

Sangya ShrivastavaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Stick Diagrams Layout Planning

Uploaded by

Sangya ShrivastavaCopyright:

Available Formats

Stick Diagrams

Stick Diagrams

by

Rita Jain Professor and Head

Department of Electronics and Communication Engineering Lakshmi Narain College of Technology, Bhopal

ritajain_bpl@yahoo.com

1 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Layout

The Design Rules describe: Minimum width to avoid breaks in a line Minimum spacing to avoid shorts between lines Minimum overlap to ensure two layers completely overlap Unit Transistor Transistor dimensions are specified by their W/L ratio For 0.6 m process, W = 1.2 m and L = 0.6 m Such a minimum width contacted transistor is called UNIT TRANSISTOR

2 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Inverter Layout

Transistor dimensions specified as Width / Length

Minimum size is 4 / 2, sometimes called 1 unit For 0.6 mm process, W=1.2 m, L=0.6 m

3 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Layout

A conservative but easy to use Design Rules for nwell process is as follows: Metal and diffusion have minimum width spacing of 4 Contacts are 2 X 2 and must be surrounded by 1 on the layers above and below Polysilicon uses a width of 2 Polysilicon overlaps diffusion by 2 where a transistor is desired and has a spacing of 1 away where no transistor is desired Polysilicon and contacts have a spacing of 3 from other polysilicon or contacts N-well surrounds PMOS transistors by 6 and avoids NMOS transistors by 6

4 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Simplified Design Rules

Conservative rules to get you started

5 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Stick Diagrams

Stick diagrams help plan layout quickly

Need not be to scale Draw with color pencils or dry-erase markers

6 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Stick Diagrams

VLSI design aims to translate circuit concepts onto silicon. stick diagrams are a means of capturing topography and layer information using simple diagrams. Stick diagrams convey layer information through colour codes (or monochrome encoding). Acts as an interface between symbolic circuit and the actual layout.

7 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Stick Diagrams

Does show all components/vias. It shows relative placement of components. Goes one step closer to the layout Helps plan the layout and routing

Does not show

Exact placement of components Transistor sizes Wire lengths, wire widths, tub boundaries. Any other low level details such as parasitics.

8 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Wiring Tracks

A wiring track is the space required for a wire

4 width, 4 spacing from neighbor = 8 pitch

Transistors also consume one wiring track

9 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Well Spacing

Wells must surround transistors by 6

Implies 12 between opposite transistor flavors Leaves room for one wire track

10 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Area Estimation

Estimate area by counting wiring tracks

Multiply by 8 to express in

11 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Example: Inverter

12 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Example: NAND3

Horizontal N-diffusion and p-diffusion strips Vertical polysilicon gates Metal1 VDD rail at top Metal1 GND rail at bottom 32 l by 40 l

13 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Stick Diagrams Some rules

Rule 1. When two or more sticks of the same type cross or touch each other that represents electrical contact.

14 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Stick Diagrams Some rules

Rule 2. When two or more sticks of different type cross or touch each other there is no electrical contact. (If electrical contact is needed we have to show the connection

explicitly).

15 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Stick Diagrams Some rules

Rule 3. When a poly crosses diffusion it represents a transistor.

Note: If a contact is shown then it is not a transistor.

Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

16

Stick Diagrams

Stick Diagrams Some rules

Rule 4. In CMOS a demarcation line is drawn to avoid touching of p-diff with n-diff. All pMOS must lie on one side of the line and all nMOS will have to be on the other side.

17 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Stick Diagrams

N+

N+

18 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Stick Diagrams

VDD X X X VDD

Stick Diagram

X Gnd

Gnd

19

Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Stick Diagrams

VDD X X X

VDD

X Gnd

Gnd

20

Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Stick Diagrams Notations

Metal 1 poly ndiff pdiff

Can also draw in shades of gray/line style.

Similarly for contacts, via, tub etc..

21 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

How to draw Stick Diagrams

22 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

NOR Gate

23 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Stacked Layout

Power

Out

C B

Ground

24 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Methods for generating Stick Diagrams

Construct a Logic Graph of the Schematics Identify each transistor by a unique name of its gate signal (A, B, C, D ..) Identify each connection to the transistor by a unique name (1,2,3,4,5,..) Construct an Euler Path for both pull-up and pull-down network Euler Path is defined by a path that traverses each node in the path, such that each edge is visited only once Path is defined by the order of each transistor name Euler Path for the pull-up network must be same as the path of pulldown network Euler paths are not necessarily unique It may be necessary to redefined the function to find a Euler path

25 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Methods for generating Stick Diagrams

Once the Euler path is found it is time to layout the stick diagram Trace two lines horizontally to represent PMOS and NMOS Trace the number of Inputs vertically across each strip. These represent the gate contacts to the devices that are made of poly Surround NMOS and PMOS by P-well and N-well Trace a blue line horizontally above and below the PMOS and NMOS lines to represent the metal of VDD and VSS Label each poly line with the Euler path label, in order from left to right Place the connection label upon NMOS and PMOS devices

26 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Stick Diagrams

Sketch a stick diagram for O3AI and estimate area Y = ((A+B+C).D)

27 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Stick Diagrams

VDD

VDD

A B C Y D B

A Y D D

C Y

B C

VSS

C

VSS

Pull-up Network

Pull-down Network

28 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Stick Diagrams

29 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Area Estimation

30 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

OAI21 Logic Graph

A j B X = !(C (A + B)) C A i i B B X A C X C

B j A C

GND A B C PDN

VDD PUN

31 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Home Work

1. Draw the stick diagram for two input CMOS NAND gate. 2. Draw the stick diagram for two input NAND gate using NMOS Logic. 3. Draw the stick diagram for 2:1 MUX using a) Pass transistors b) Transmission gates. 4. Draw Stick Diagrams for the following equations Y = ( A + B + C ).D : Y = A + ( B + C ).D

5. 6. For a process technology with L = 5 micron meter give the size of the layout for the following : (a) 4-input NOR gate and 4-Input NAND gate Draw Stick Diagram for the circuits given below and estimate its area (circuits given in next few slides) Identify the logic functions (stick diagrams given in next few slides)

7.

Drawing stick diagram is truly Fun !!! Enjoy it !!!

32 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Draw Stick Diagram for the circuit given below and estimate its area

B A C D OUT = !(D + A (B + C)) A D B C

33 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Draw Stick Diagram for the circuits given below and estimate its area

34 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

Draw Stick Diagram for the circuits given below and estimate its area

A B

C D X = !((A+B)(C+D)) A B C D

C A

D B

35 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

What logic function is this?

Routing channel VDD

signals

GND

What logic function is this?

36 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

What logic function is this?

A VDD

C VDD

GND

GND

37 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

Stick Diagrams

What logic function is this?

A VDD B D C

GND

38 Rita Jain, Faculty, Department of Electronics & Communication Engineering, LNCT, Bhopal

You might also like

- Electrical Overstress (EOS): Devices, Circuits and SystemsFrom EverandElectrical Overstress (EOS): Devices, Circuits and SystemsNo ratings yet

- Introduction To Transfer Function in MATLABDocument10 pagesIntroduction To Transfer Function in MATLABvoltax1No ratings yet

- Modelling & Simulation of BJT Device ModelsDocument29 pagesModelling & Simulation of BJT Device ModelsvanithapremkumarNo ratings yet

- Optical Amplifier1Document8 pagesOptical Amplifier1Sunil FageriaNo ratings yet

- Lecture 3 Single Stage AmplifiersDocument76 pagesLecture 3 Single Stage Amplifierstranhieu_hcmutNo ratings yet

- Cmos LayoutDocument13 pagesCmos LayoutshastryNo ratings yet

- 01 Experiment 1 - Familiarization of Components and InstrumentsDocument5 pages01 Experiment 1 - Familiarization of Components and InstrumentsNikita Mayee sahooNo ratings yet

- Cep Micro2 170857Document13 pagesCep Micro2 170857Ramsha MalikNo ratings yet

- Determine System Stability with Nyquist CriterionDocument25 pagesDetermine System Stability with Nyquist CriterionHosein KerdarNo ratings yet

- Chapter 2 Linear Signal ModelsDocument40 pagesChapter 2 Linear Signal ModelsSisayNo ratings yet

- Eesyll PDFDocument130 pagesEesyll PDFDeepak DeepuNo ratings yet

- Why VLSI? - Moore's Law. - The VLSI Design ProcessDocument28 pagesWhy VLSI? - Moore's Law. - The VLSI Design Processlim hyNo ratings yet

- Experiment No.03: Mathematical Modeling of Physical System: ObjectiveDocument5 pagesExperiment No.03: Mathematical Modeling of Physical System: ObjectiveSao SavathNo ratings yet

- MATRIX CHAIN MultiplicationDocument41 pagesMATRIX CHAIN Multiplicationsam bordgeNo ratings yet

- Sequential Decoding by Stack AlgorithmDocument9 pagesSequential Decoding by Stack AlgorithmRam Chandram100% (1)

- Matrices Solved ProblemsDocument19 pagesMatrices Solved Problemsvivek patel100% (1)

- Creating An Inverter Layout Using L-EditDocument9 pagesCreating An Inverter Layout Using L-EditVinod MannNo ratings yet

- Switch CapacitorDocument90 pagesSwitch CapacitorVaibhav Khurana100% (1)

- BCM Unit - 1 (A)Document79 pagesBCM Unit - 1 (A)Mr. G. SathiyaseelanNo ratings yet

- Frequency Shift KeyingDocument3 pagesFrequency Shift Keyingsobia aslamNo ratings yet

- STLDDocument18 pagesSTLDGagan tej gowdNo ratings yet

- Twin T NetworkDocument2 pagesTwin T NetworkVijayalakshmi Prakash100% (1)

- Stick Diagram & Euler Path: VLSI Design CourseDocument20 pagesStick Diagram & Euler Path: VLSI Design CourseSelvasundar KumarNo ratings yet

- Electric Power Engineering Lecture NotesDocument209 pagesElectric Power Engineering Lecture NotesRaj Boda0% (1)

- DSP Module 4 NotesDocument16 pagesDSP Module 4 NotesChetan Naik massand100% (1)

- Digital Logic FPGA Lab ManualDocument35 pagesDigital Logic FPGA Lab ManualBilal RajaNo ratings yet

- Diode Resistance & Diode Equivalent CircuitsDocument42 pagesDiode Resistance & Diode Equivalent Circuitsgirishkumardarisi254No ratings yet

- Module1 EC NotesDocument25 pagesModule1 EC NotesTriveni M KNo ratings yet

- Engineering Drawing: North South UniversityDocument14 pagesEngineering Drawing: North South UniversityMD. Zobayer Ahmed 1610766642No ratings yet

- D-Band Frequency Tripler For Passive Imaging - Final 13th JulyDocument4 pagesD-Band Frequency Tripler For Passive Imaging - Final 13th JulyTapas SarkarNo ratings yet

- Electronic Circuits Lab Manual Clippers and AmplifiersDocument29 pagesElectronic Circuits Lab Manual Clippers and AmplifiersAshwath NadahalliNo ratings yet

- DLD GTU Question Bank: Chapter-1 Binary SystemDocument5 pagesDLD GTU Question Bank: Chapter-1 Binary Systemnirav34No ratings yet

- Advanced DSPDocument2 pagesAdvanced DSPAshar Wahid Hashmi50% (2)

- Modal Analysis of Step-Index FibersDocument25 pagesModal Analysis of Step-Index Fibersd24testNo ratings yet

- Lecture Signal Flow GraphsDocument56 pagesLecture Signal Flow GraphsFahadKhNo ratings yet

- Dynamic Programming Rod or Pole Cutting ProblemDocument17 pagesDynamic Programming Rod or Pole Cutting ProblemAbhishek karwalNo ratings yet

- JNTUK R16 II-I DLD UNIT I NotesDocument30 pagesJNTUK R16 II-I DLD UNIT I NotesSowmya Koneru100% (1)

- COMPARING SCHMITT TRIGGERSDocument4 pagesCOMPARING SCHMITT TRIGGERSSaurabh ChakravartyNo ratings yet

- 9086 CMOS Analog Design Chapter 6Document24 pages9086 CMOS Analog Design Chapter 6Yogindr SinghNo ratings yet

- Graph Theory PDFDocument20 pagesGraph Theory PDFNihar Kuchroo100% (1)

- Chapter 10 PDFDocument26 pagesChapter 10 PDFPugazhendhi MuthuNo ratings yet

- DLD LAB REPORT 3Document8 pagesDLD LAB REPORT 3HimelNo ratings yet

- Expt 5 - Wein Bridge Oscillator (2020)Document3 pagesExpt 5 - Wein Bridge Oscillator (2020)samarthNo ratings yet

- Linear Circuit Analysis Lab ManualsDocument97 pagesLinear Circuit Analysis Lab ManualsAbdul Saboor KhanNo ratings yet

- T15.Matrix and Vector AlgebraDocument42 pagesT15.Matrix and Vector Algebraambida02No ratings yet

- Unit # 5 Dynamic Cmos and ClockingDocument15 pagesUnit # 5 Dynamic Cmos and ClockingKiran KumariNo ratings yet

- Chapter SixDocument5 pagesChapter Sixyunus memonNo ratings yet

- 9.small Signal Analysis of MosfetsDocument27 pages9.small Signal Analysis of MosfetsNitin Mehta - 18-BEC-030No ratings yet

- A CMOS Bandgap Reference Circuit With Sub-1V OperationDocument5 pagesA CMOS Bandgap Reference Circuit With Sub-1V Operationbooky_mookyNo ratings yet

- Personality Matrix Folding AnalysisDocument23 pagesPersonality Matrix Folding Analysiskrishnaprasad50% (2)

- A 3-Db Quadrature Coupler Suitable For PCB Circuit DesignDocument5 pagesA 3-Db Quadrature Coupler Suitable For PCB Circuit Designagmnm1962No ratings yet

- Kogge-Stone AdderDocument6 pagesKogge-Stone AdderVijay Dhar MauryaNo ratings yet

- Modeling of Passive Elements With ASITICDocument20 pagesModeling of Passive Elements With ASITICKyusang ParkNo ratings yet

- LinearDocument46 pagesLinearSheikh Riasat100% (1)

- 2 33Document2 pages2 33Eric KialNo ratings yet

- Microelectronics Lab: Integrated Circuits Design Session 1Document36 pagesMicroelectronics Lab: Integrated Circuits Design Session 1Rekha YadavNo ratings yet

- Vlsi LabDocument17 pagesVlsi LabbitseceNo ratings yet

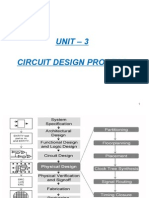

- Unit - 3 Circuit Design ProcessDocument30 pagesUnit - 3 Circuit Design ProcessNagarjun RajputNo ratings yet

- JNTUK BTech 2 1 Electronics Communications R20 Syllabus PDFDocument19 pagesJNTUK BTech 2 1 Electronics Communications R20 Syllabus PDFKethavath Sakrunaik KNo ratings yet

- CMOS Lambda Design Rules SummaryDocument15 pagesCMOS Lambda Design Rules SummarySougata GhoshNo ratings yet

- Amdahls LawDocument18 pagesAmdahls LawSangya ShrivastavaNo ratings yet

- Amdahls LawDocument18 pagesAmdahls LawSangya ShrivastavaNo ratings yet

- Principles of Communication Systems by Taub & SchillingDocument119 pagesPrinciples of Communication Systems by Taub & SchillingInsane Clown Prince40% (5)

- TDMA Versus CDMA SNatarajanDocument10 pagesTDMA Versus CDMA SNatarajanSanjay KumarNo ratings yet

- Cellular NetworksDocument58 pagesCellular NetworksSangya ShrivastavaNo ratings yet

- Principles of Communication Systems by Taub & SchillingDocument119 pagesPrinciples of Communication Systems by Taub & SchillingInsane Clown Prince40% (5)

- Frequency ReuseDocument1 pageFrequency ReuseSangya ShrivastavaNo ratings yet

- 3 Months Look Ahead PlanDocument6 pages3 Months Look Ahead PlananjnaNo ratings yet

- The Rope Memory-A Permanent Storage DeviceDocument14 pagesThe Rope Memory-A Permanent Storage DevicePaul CultreraNo ratings yet

- Section 1.1: Configure The ACME Headquarters Network (AS 12345) As Per The Following RequirementsDocument59 pagesSection 1.1: Configure The ACME Headquarters Network (AS 12345) As Per The Following Requirementsdimkatsar30No ratings yet

- CCFL Inverter ZXDocument26 pagesCCFL Inverter ZXcuzquilloNo ratings yet

- Translated Camera Test Equipment ManualDocument43 pagesTranslated Camera Test Equipment ManualAltaf HussainNo ratings yet

- Assignment 4Document2 pagesAssignment 4Priya RadhakrishnanNo ratings yet

- Amber Krieg ResumeDocument1 pageAmber Krieg Resumeapi-376941376No ratings yet

- ZXCTN 6500 V1.00.10R2 Benchmark Slides - 20141023Document32 pagesZXCTN 6500 V1.00.10R2 Benchmark Slides - 20141023محيي الدين الكميشىNo ratings yet

- Alzheimers Assistant PDFDocument34 pagesAlzheimers Assistant PDFabhirami manikandanNo ratings yet

- Big Data Simplified: Book DescriptionDocument14 pagesBig Data Simplified: Book DescriptionN C NAGESH PRASAD KOTINo ratings yet

- Dir x1560 Datasheet Eu enDocument2 pagesDir x1560 Datasheet Eu enMilosNo ratings yet

- Forward Error Correction (FEC)Document6 pagesForward Error Correction (FEC)gamer08No ratings yet

- TranslatorsDocument3 pagesTranslatorsijas100% (1)

- Pinouts ICRDocument38 pagesPinouts ICRAdal Vera100% (1)

- Optix BWS 1600 GDocument23 pagesOptix BWS 1600 GRohit SharmaNo ratings yet

- NGC 8206 Startup GuideDocument24 pagesNGC 8206 Startup Guidelafuria1234No ratings yet

- Vinculum's Supply Chain PracticeDocument26 pagesVinculum's Supply Chain PracticeVinculumGroup100% (1)

- Exercise: Answer the following questionsDocument11 pagesExercise: Answer the following questionsluqyana fauzia hadi100% (1)

- CD KEY Untuk PerusahaanDocument30 pagesCD KEY Untuk PerusahaanAriagus BjoNo ratings yet

- Scripting Language - WikipediaDocument9 pagesScripting Language - WikipediaGilbertNo ratings yet

- Resume Juan Carlos MoralesDocument1 pageResume Juan Carlos Moralesjuancarlosmorales.1397No ratings yet

- Teach Yourself Logic 2020 - Peter SmithDocument99 pagesTeach Yourself Logic 2020 - Peter SmithPaolo Pagliaro100% (1)

- Curve Weighting: Effects of High - End Non - LinearityDocument3 pagesCurve Weighting: Effects of High - End Non - LinearityhF2hFhiddenFaceNo ratings yet

- Medical Image ProcessingDocument24 pagesMedical Image ProcessingInjeti satish kumarNo ratings yet

- 2010 PAARL Standards For Academic LibrariesDocument6 pages2010 PAARL Standards For Academic LibrariesChristian Robert NalicaNo ratings yet

- Unit 5 Instructor Graded AssignmentDocument3 pagesUnit 5 Instructor Graded Assignmentrosalindcsr_64842985No ratings yet

- Accounting 12 Course OutlineDocument3 pagesAccounting 12 Course OutlineKenrose LaguyoNo ratings yet

- III Year SyllabusDocument68 pagesIII Year SyllabusFaiz KarobariNo ratings yet

- Signal Flow GraphDocument48 pagesSignal Flow GraphsufyanNo ratings yet

- t370hw02 VC AuoDocument27 pagest370hw02 VC AuoNachiket KshirsagarNo ratings yet