Professional Documents

Culture Documents

VLSI IEEE 2012 Titles

Uploaded by

nssaravananeceOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

VLSI IEEE 2012 Titles

Uploaded by

nssaravananeceCopyright:

Available Formats

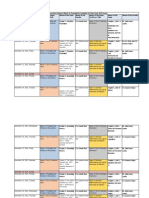

COGNITION TECH LABS

FPGA

Mobile no.: +91-9043451654, +91-9786866345

Implementation of image reconstruction algorithm using compressive sensing in Implementation of algorithm for detection and correction of defective pixels in FPGA

1.

Efficient VLSI implementation of soft-input soft-output fixed-complexity sphere decoder

FPGA implementation of graph cut based image thresholding Efficient FPGA implementation of steerable Gaussian smoothers Background subtraction algorithm for moving object detection in FPGA Design and Implementation of a Pipelined Datapath for High-Speed Face Detection Using FPGA High speed FPGA implementation of hough transform for real-time applications Real time hardware co-simulation of Edge Detection for video processing system An FPGA embedded system architecture for handwritten symbol recognition 2D/3D FPGA array for brain process and numerical computation A moving window architecture for a HW/SW codesign based Canny edge detection for FPGA A low computing power frame rate converter An FPGA-based accelerator for cortical object classification New digital Pulse-Mode Neural Network based image denoising FPGA design of H.264/AVC intra-frame prediction architecture for high resolution video encoding FPGA implementation of chaotic state sequence generator for secure communication An FPGA-Based Hardware Implementation of Configurable Pixel-Level Color Image Fusion FPGA based real time face detection using Adaboost and histogram equalization

COGNITION TECH LABS

FPGA

Mobile no.: +91-9043451654, +91-9786866345

Implementation of image reconstruction algorithm using compressive sensing in Multichannel Pulse-Coupled-Neural-Network-Based Color Image Segmentation for Object Detection VLSI Implementation of a Bio-Inspired Olfactory Spiking Neural Network VLSI Implementation of Advanced Encryption Standard A novel architecture for VLSI implementation of RSA cryptosystem Analysis and VLSI Implementation of EWA Rendering for Real-time HD Video Applications Area-Efficient VLSI Implementation for Parallel Linear-Phase FIR Digital Filters of Odd Length Based on Fast FIR Algorithm Implementation of VLSI-oriented FELICS algorithm using Pseudo Dual-Port RAM VLSI design and implementation of reconfigurable OFDM transceivers for software defined radio An adaptive, linear-line approximation method and its VLSI implementation for maximum power control of photovoltaic system VLSI implementation with double cipher and media processing for ad-hoc network Modified Redundant Representation for Designing Arithmetic Circuits with Small Complexity Design and implementation of high-performance high-valency ling adders Fast two-pick n2n round-robin arbiter circuit A Scalable Architecture for Dual Basis GF(2m) Multiplications Design and implementation of low power FFT/IFFT processor for wireless communication Hardware Efficient Architecture for Generating Sine/Cosine Waves

COGNITION TECH LABS

Presence of Multiple Transient Errors

Mobile no.: +91-9043451654, +91-9786866345

Relaxed Fault-Tolerant Hardware Implementation of Neural Networks in the Nonbinary LDPC Code Decoder Architecture With Efficient Check Node Processing Low-power Logarithmic Number System Addition/Subtraction and their Impact on Digital Filters A novel VLSI architecture for generation of Six Phase pulse compression sequences VLSI signal processing oriented segmentation based serial parallel multiplier VLSI Based Robust Router Architecture A fault tolerant parallel-prefix adder for VLSI and FPGA design Highly secured high throughput VLSI architecture for AES algorithm A Novel Interpolation Chip for Real-Time Multimedia Applications A Nonbinary LDPC Decoder Architecture With Adaptive Message Control Design of Low Power TPG Using LP-LFSR A high throughput sort free VLSI architecture for wireless applications A non linear equation based cryptosystem for image encryption and decryption Semi-Serial On-Chip Link Implementation for Energy Efficiency and High Throughput Efficient Configurable Decoder Architecture for Nonbinary Quasi-Cyclic LDPC Codes Hardware Implementation of Nakagami and Weibull Variate Generators Dual-Layer Adaptive Error Control for Network-on-Chip Links Design and Implementation of an On-Chip Permutation Network for Multiprocessor System-On-Chip CORDIC Designs for Fixed Angle of Rotation

COGNITION TECH LABS

Routing-efficient architecture implementation of an

Mobile no.: +91-9043451654, +91-9786866345

internal-response-based

BIST

Area- and Power-Efficient Architecture for High-Throughput Implementation of Lifting 2-D DWT Hardware Implementation of a Digital Watermarking System for Video Authentication VLSI Architecture for a Reconfigurable Spectrally Efficient FDM Baseband Transmitter Secure Dual-Core Cryptoprocessor for Pairings Over Barreto-Naehrig Curves on FPGA Platform Implementation of random walk algorithm by parallel computing Scalable Packet Classification on FPGA Throughput/Resource-Efficient Applications Parallel Architecture for Hierarchical Optical Flow Estimation Based on FPGA Hardware Implementation of a Digital Watermarking System for Video Authentication Techniques for Compensating Memory Errors in JPEG2000 Derating based hardware optimizations in soft error tolerant designs High-Speed Low-Power Viterbi Decoder Design for TCM Decoders Construction of Optimum Composite Field Architecture for Compact HighThroughput AES S-Boxes A Built-In Repair Analyzer With Optimal Repair Rate for Word-Oriented Memories Design and implementation of an optical OFDM baseband receiver in FPGA An FPGA Chip Identification Generator Using Configurable Ring Oscillators VLSI Architecture of Arithmetic Coder Used in SPIHT Reconfigurable Processor for Multimedia

COGNITION TECH LABS

A Network-on-Chip-based turbo/LDPC decoder architecture

2.

Mobile no.: +91-9043451654, +91-9786866345

Reconfigurable Accelerator for the Word-Matching Stage of BLASTN Real-time multi-view rendering based on FPGA Performance Using FPGA Correlator The design and implementation of fire smoke detection system based on FPGA Real-Time Vehicle Identification Hardware A multifunctional, reconfigurable pulse generator for high-frequency ultrasound imaging Gesture recognition using field programmable gate arrays A hardware acceleration of a real time video processing Lossy Compression of Discrete Sources via the Viterbi Algorithm FPGA implementation of IEEE 802.15.3c receiver

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- HOW To Use Jmeter To Load Test T24Document27 pagesHOW To Use Jmeter To Load Test T24Hiếu KoolNo ratings yet

- A Strategic Management PaperDocument7 pagesA Strategic Management PaperKarll Brendon SalubreNo ratings yet

- Gender and Other Cross Cutting Issues Mental HealthDocument6 pagesGender and Other Cross Cutting Issues Mental HealthJamira Inoc SoboNo ratings yet

- Hireena Essay AnsDocument2 pagesHireena Essay AnsTasniiem ChandraaNo ratings yet

- PaperDocument4 pagesPapermani4489No ratings yet

- Read MeDocument4 pagesRead MenssaravananeceNo ratings yet

- Sea in FpgaDocument5 pagesSea in FpganssaravananeceNo ratings yet

- BlueBoardUserManual v1.4Document27 pagesBlueBoardUserManual v1.4Gautam AdhiNo ratings yet

- A Multi CarrierDocument1 pageA Multi CarriernssaravananeceNo ratings yet

- Restaurant Social Media GuideDocument30 pagesRestaurant Social Media GuideHoàng gia NghiêmNo ratings yet

- 1ST Periodical Test ReviewDocument16 pages1ST Periodical Test Reviewkaren rose maximoNo ratings yet

- 2000 T.R. Higgins Award Paper - A Practical Look at Frame Analysis, Stability and Leaning ColumnsDocument15 pages2000 T.R. Higgins Award Paper - A Practical Look at Frame Analysis, Stability and Leaning ColumnsSamuel PintoNo ratings yet

- The Teacher and The LearnerDocument23 pagesThe Teacher and The LearnerUnique Alegarbes Labra-SajolNo ratings yet

- JNTUA Mechanical Engineering (R09) Syllabus BookDocument147 pagesJNTUA Mechanical Engineering (R09) Syllabus Bookslv_prasaad0% (1)

- Starting an NGO - A Guide to the Key StepsDocument22 pagesStarting an NGO - A Guide to the Key StepsBadam SinduriNo ratings yet

- ICS Technical College Prospectus 2024 Edition 1Document36 pagesICS Technical College Prospectus 2024 Edition 1samuel287kalumeNo ratings yet

- G10 - Math - Q1 - Module 7 Grade 10Document12 pagesG10 - Math - Q1 - Module 7 Grade 10Shua HongNo ratings yet

- Advantages of Computerizing and Networking ComputersDocument5 pagesAdvantages of Computerizing and Networking ComputersIn BioNo ratings yet

- Important instructions on judicial procedure from Narada SmritiDocument6 pagesImportant instructions on judicial procedure from Narada SmritirohitNo ratings yet

- Avance Collection Mixer Grinder SpecsDocument3 pagesAvance Collection Mixer Grinder SpecsfaNo ratings yet

- HDL Coder™ ReferenceDocument487 pagesHDL Coder™ ReferenceVictor Colpo NavarreteNo ratings yet

- Oposa vs. Factoran 224 Scra 792Document28 pagesOposa vs. Factoran 224 Scra 792albemartNo ratings yet

- Fci FC CotsDocument25 pagesFci FC CotsMatthew DuNo ratings yet

- 2017 Grade 9 Math Challenge OralsDocument3 pages2017 Grade 9 Math Challenge OralsGracy Mae PanganibanNo ratings yet

- Iwwusa Final Report IdsDocument216 pagesIwwusa Final Report IdsRituNo ratings yet

- Plate Tectonics LessonDocument3 pagesPlate Tectonics LessonChristy P. Adalim100% (2)

- Working Capital Management (2015)Document62 pagesWorking Capital Management (2015)AJNo ratings yet

- Messier 88Document3 pagesMessier 88Matheus RochaNo ratings yet

- Transactionreceipt Ethereum: Transaction IdentifierDocument1 pageTransactionreceipt Ethereum: Transaction IdentifierVALR INVESTMENTNo ratings yet

- Atlanta Pipes and FittingsDocument2 pagesAtlanta Pipes and Fittingsotadoyreychie31No ratings yet

- Aligning With New Digital Strategy A Dynamic CapabilitiesDocument16 pagesAligning With New Digital Strategy A Dynamic Capabilitiesyasit10No ratings yet

- RCC Lintel and Slab PlanDocument3 pagesRCC Lintel and Slab PlanSaurabh Parmar 28No ratings yet

- Volume 4-6Document757 pagesVolume 4-6AKNo ratings yet

- RRC Igc1Document6 pagesRRC Igc1kabirNo ratings yet

- Chapter 1-The Indian Contract Act, 1872, Unit 1-Nature of ContractsDocument10 pagesChapter 1-The Indian Contract Act, 1872, Unit 1-Nature of ContractsALANKRIT TRIPATHINo ratings yet