Professional Documents

Culture Documents

Examen 2005

Uploaded by

Yassir RochdOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Examen 2005

Uploaded by

Yassir RochdCopyright:

Available Formats

Majeure MNO

examen PHY568 Circuits Electroniques

Majeure Micro-Nano-Optoelectronique Cours :"Circuits lectroniques" PHY568 Sujet Examen

Dure 2h30 Polycopis de cours et damphi autoriss Corrigs de Petite Classe non autoriss

1er Exercice : Dimensionnement dun latch (6 points)

On considre le schma de latch ci-dessous, appel latch conflit :

CK Inv1 Y On suppose que linverseur dentre a pour dimensions Wn = 10 , Wp = 20 , Ln = Lp = 1 . Les dimensions de linterrupteur N sont Wn = 10 , Ln = 1 . Q1) Fournir le chronogramme de fonctionnement de ce latch. Quelles sont les contraintes temporelles que doit respecter le signal D par rapport au signal CK ? Q2) Expliquer quel est le problme pos par lcriture dune nouvelle valeur dans ce latch. Inv2

Q3) On suppose que le latch contient la valeur 1 (X = 0, Y = 1), et quon cherche crire la valeur 0 (D = 0, CK = 1). Donner une condition sur la valeur de rsistance Ron du transistor N de linverseur inv1 Q4) On suppose quon cherche maintenant crire la valeur 1. Donner une condition sur la valeur de rsistance Ron du transistor P de linverseur inv1 Q5) Proposez un dimensionnement pour les deux inverseurs inv1 et inv2 constituant la boucle de mmorisation, en justifiant votre rponse.

Anne 2005 (X2002)

1/4

Majeure MNO

examen PHY568 Circuits Electroniques

2me Exercice : Testeur de rflexes (8 points)

On souhaite raliser un dispositif permettant de tester les rflexes, aprs une soire arrose par exemple. Ce testeur est ralis comme un automate de Moore. Outre le signal dhorloge H, le circuit possde trois entres : go, stop, reset et 5 sorties : On, T(richeur), E(xcellent), B(on), F(aible).

reset On go stop H E

TESTEUR DE REFLEXE

F B T

Le principe consiste mesurer le temps coul entre lactivation successive des signaux go et stop. L unit de mesure est le temps de cycle de lhorloge H. Le comportement de ce testeur peut tre dcrit comme suit : On suppose que le circuit a t initialis grce au signal reset dans un tat o toutes les sorties valent 0. Le signal reset est synchrone, cest dire que sa valeur nest prise en compte quau moment du front de lhorloge H. La sortie On passe 1 lorsquune personne (le passager dune voiture par exemple) active le signal go. La sortie T passe 1 si la personne active le signal stop avant ou en mme temps quelle dactive le signal go. Si le signal stop est effectivement activ aprs le signal go, o E passe 1, si stop est activ un cycle aprs go. o B passe 1, si stop est activ deux cycle aprs go. o F passe 1, si stop est activ plus de deux cycle aprs go..

On notera que F ne passe 1 qu partir du moment o lutilisateur appuie sur le bouton stop. Il faut activer le signal reset pour remettre 0 les signaux de sortie et dmarrer un nouveau test, et le signal reset nest pris en compte que si lun des signaux E,F , B ou T a la valeur 1. Q1) Reprsentez graphiquement lautomate de Moore 8 tats dcrivant le comportement de ce testeur. On attachera chaque transition lexpression Boolenne dpendant des entres qui valide cette transition. Q2) Construire le tableau dfinissant pour chaque tat la valeur des 5 signaux de sortie.

Q3) En supposant un codage de type one-hot (une bascule par tat), en dduire les expressions boolennes des 8 signaux dentre dans les 8 bascules reprsentant le registre dtat. Ces expressions Boolennes dpendent des 3 signaux dentre go, stop, et reset, et des 8 variables stockes dans le registre dtat. Q4) Donner les expressions boolennes des 5 signaux de sortie.

Anne 2005 (X2002)

2/4

Majeure MNO

examen PHY568 Circuits Electroniques

clk rst

stop

go

on

F E B Exemple de scnario

3me Exercice : additionneur CMOS (6 points)

Un additionneur de 2 mots binaires de n bits (An-1Ai A0 & Bn-1Bi B0) peut tre ralis en utilisant n additionneur binaires complets comme dcrit sur la figure suivante.

A0 B0 Ai-1 Bi_1 Ai Bi Ai+1 Bi+1 An-1 Bn-1

C0 ADD0

R0

Ci-1

ADD(i-1)

Ri-1 Ci

Ri ADD(i)

Ci+1

ADD(i+1)

R i+1

C0

Rn-1 ADD(n-1)

Vss

S0

Si-1

Si

Si+1

Sn-1

Le chemin critique au niveau temporel correspond la propagation de la retenue. Nous chercherons donc une structure permettant dacclrer la propagation de la retenue. Ladditionneur binaire complet permet dadditionner 3 bits de poids numrique gaux (a,b,c), et de recoder la valeur sur deux bits (r,s) o s est le bit de somme et r le bit de retenue. Q1) a b c s r Construire la table de vrit de ladditionneur binaire complet. 0 0 0 1 0 0 0 1 0 1 1 0 0 0 1 1 0 1 0 1 1 1 1 1

Anne 2005 (X2002)

3/4

Majeure MNO

examen PHY568 Circuits Electroniques

Q2) Donner lexpression canonique de r et s sous forme de somme de produits, en utilisant les oprateurs OR, AND et NOT. Dans la forme canonique, tous les produits contiennent 3 termes. Q3) Simplifier les expressions Boolennes de r et s pour diminuer le nombre de littraux, en utilisant les 3 mmes oprateurs que dans la question prcdente. Q4) Re-crire le rsultat prcdent en utilisant les lois de Morgan de faon nutiliser que des oprateurs NAND, NOR, ou NOT et en minimisant le nombre de portes logiques sur le chemin de propagation de la retenue. Q5) Proposer un schma complet pour ladditionneur binaire complet, et en dduire le nombre de portes traverses sur le chemin critique dans le cas de deux mots de 16 bits.

Anne 2005 (X2002)

4/4

You might also like

- Exos de Logique SéquentielleDocument5 pagesExos de Logique SéquentielleSabrine Khoualdi100% (1)

- Exercices d'intégrales de lignes, de surfaces et de volumesFrom EverandExercices d'intégrales de lignes, de surfaces et de volumesNo ratings yet

- TD Automatique 1A JMD 2011Document20 pagesTD Automatique 1A JMD 2011Hajri MohamedNo ratings yet

- 3 Ex Travail Puiss Energ 13 ComprDocument7 pages3 Ex Travail Puiss Energ 13 ComprYassir RochdNo ratings yet

- Oscillateur À Résistance Négative Cours Morchid PDFDocument8 pagesOscillateur À Résistance Négative Cours Morchid PDFYassir RochdNo ratings yet

- TD Automatique 1A 2016 JMD 2Document20 pagesTD Automatique 1A 2016 JMD 2Adil ChentoufNo ratings yet

- Cours 10 CG Toutes ClassesDocument46 pagesCours 10 CG Toutes ClassesDiakaridia Coulibaly100% (5)

- TD Automatique 1A 2016 JMDDocument20 pagesTD Automatique 1A 2016 JMDFaïssolath Achirou100% (1)

- TD01 Asservissements 1Document10 pagesTD01 Asservissements 1fekielyes100% (1)

- TD 11 FiltrageDocument4 pagesTD 11 Filtragelina hkl officialNo ratings yet

- Microcontrôleur PIC16F84Document33 pagesMicrocontrôleur PIC16F84infobadrino88% (24)

- Exercice Corrige Bac Blanc Physique Ondes Sonores PDFDocument2 pagesExercice Corrige Bac Blanc Physique Ondes Sonores PDFYassir Rochd0% (1)

- Les Compteurs Et Decompteurs PDFDocument11 pagesLes Compteurs Et Decompteurs PDFbakkari MNo ratings yet

- Fiche Technique 7-ConductimetrieDocument2 pagesFiche Technique 7-ConductimetrieYassir RochdNo ratings yet

- Série D'exercices N°3-3tech-Bascules-Compteurs-2012-2013Document9 pagesSérie D'exercices N°3-3tech-Bascules-Compteurs-2012-2013Hyacinthe Kossi100% (3)

- Fiche InterventionDocument1 pageFiche InterventionReagan Bodele100% (1)

- TD N°4 Représentation Des SLCI FT Schémas Blocs SLCI Asservis 1 PDFDocument4 pagesTD N°4 Représentation Des SLCI FT Schémas Blocs SLCI Asservis 1 PDFseye abdou aziz50% (2)

- Muo003 - 0 PRM CGM Am 4+Document28 pagesMuo003 - 0 PRM CGM Am 4+hardev100% (1)

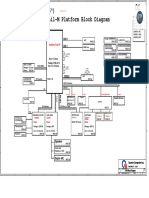

- Acer Aspire E3-111 Quanta ZHJDocument33 pagesAcer Aspire E3-111 Quanta ZHJtusharNo ratings yet

- ExosSupp CircuitsSéquentiels 2011-2012Document9 pagesExosSupp CircuitsSéquentiels 2011-2012Hamza ToumiNo ratings yet

- TD revision automatique 2022Document4 pagesTD revision automatique 2022Oussama ChoukerNo ratings yet

- Corrige Cc2 D Automatisme 2011 2012Document4 pagesCorrige Cc2 D Automatisme 2011 2012MonCf MerrNo ratings yet

- TD5 CircuitSequentiel3Document4 pagesTD5 CircuitSequentiel3Ahmed Yacine abdelmalekNo ratings yet

- Travaux Diriges RégulationDocument7 pagesTravaux Diriges RégulationsonamoffothierryNo ratings yet

- Corrige TD06Document4 pagesCorrige TD06ulrichsiriacNo ratings yet

- TD N 4 - Electrocinétique, Décomposition D Un Signal Périodique en Série de Fourier Et Filtrage Linéaire A. ElectrocinétiqueDocument5 pagesTD N 4 - Electrocinétique, Décomposition D Un Signal Périodique en Série de Fourier Et Filtrage Linéaire A. Electrocinétiqueandreas smethNo ratings yet

- Portes Log I QuesDocument7 pagesPortes Log I QuesGerard MarcelNo ratings yet

- Serie 3Document6 pagesSerie 3Soufiane DaifNo ratings yet

- Les CompteursDocument7 pagesLes CompteursSoufiane AggourNo ratings yet

- Automatique Juin2013Document6 pagesAutomatique Juin2013brahim nfaaNo ratings yet

- Cours de Compteurs Num Riques 2015-2016Document28 pagesCours de Compteurs Num Riques 2015-2016Mamadou Korka KantéNo ratings yet

- Fonction ComptageDocument9 pagesFonction ComptagedukenukembabiesNo ratings yet

- tp1 PDFDocument7 pagestp1 PDFbazine noriNo ratings yet

- Cours TP Synthèses Des Contrôleurs Avancés Mécatronique CI2 HC Février2024Document75 pagesCours TP Synthèses Des Contrôleurs Avancés Mécatronique CI2 HC Février2024fiberx01servicesNo ratings yet

- TD Système Ordre 1 PDFDocument5 pagesTD Système Ordre 1 PDFJribi TalelNo ratings yet

- Magazine 1 Filtrage Des SignauxDocument97 pagesMagazine 1 Filtrage Des SignauxHoussein ElyatimNo ratings yet

- Registres Et CompteursDocument7 pagesRegistres Et CompteursELMEHDI CHOUINENo ratings yet

- Compte UrsDocument28 pagesCompte Urssouheil_souNo ratings yet

- TD Cna CanDocument2 pagesTD Cna CanYOUNESS KARAMINo ratings yet

- Régulation Industrielle ExerciceDocument13 pagesRégulation Industrielle ExerciceRidouan Hije100% (2)

- Td1 Auto Dic2Document3 pagesTd1 Auto Dic2Cheikh Ibrahima Alioune SAMBOUNo ratings yet

- 3 Logique SequentielleDocument4 pages3 Logique SequentiellesanaelarbiNo ratings yet

- Td2 Master SanDocument3 pagesTd2 Master SanMahrez DerdoumNo ratings yet

- Chap 2 Rappel Sur Les Circuits Logique CombinatoireDocument7 pagesChap 2 Rappel Sur Les Circuits Logique CombinatoireKycelle MbouzekoNo ratings yet

- Comp DecompDocument11 pagesComp Decomparnaud.michauxNo ratings yet

- TP2MISEDocument1 pageTP2MISEBenrabah IkhlasNo ratings yet

- ATS Genie-Electrique 2007 ATS PDFDocument11 pagesATS Genie-Electrique 2007 ATS PDFsb aliNo ratings yet

- Chap7 Les CompteursDocument10 pagesChap7 Les CompteursDěmøïšěllë RãnNo ratings yet

- TD CLDocument3 pagesTD CLAyman KenNo ratings yet

- Registres Et CompteursDocument11 pagesRegistres Et CompteursMaher ZaraiNo ratings yet

- Chapitre 5Document12 pagesChapitre 5bachar soumiaNo ratings yet

- Tpn02 DiagDocument7 pagesTpn02 DiagAhmed Mehdi DALI100% (1)

- Exam FIP Avril2012Document2 pagesExam FIP Avril2012Ali MEDJGHOUNo ratings yet

- NOM/Prénom: Num. ÉtudiantDocument3 pagesNOM/Prénom: Num. ÉtudiantsaraNo ratings yet

- P514 P523 Corrige td3 Fste ElhanaouiDocument12 pagesP514 P523 Corrige td3 Fste ElhanaouiZaza RatsiNo ratings yet

- Exercices - Asservissement A ChercherDocument13 pagesExercices - Asservissement A ChercherLaurenne YaoNo ratings yet

- Chap4 IV - Les CompteursDocument27 pagesChap4 IV - Les Compteursycqrb9thmsNo ratings yet

- Fiche Technique 2-Phmetrie PDFDocument1 pageFiche Technique 2-Phmetrie PDFYassir RochdNo ratings yet

- 1AR Echerche Spectre Atomique PDFDocument10 pages1AR Echerche Spectre Atomique PDFDadati SouNo ratings yet

- CoursDocument5 pagesCoursYassir RochdNo ratings yet

- Theorie PenduleDocument8 pagesTheorie PenduleNeneNo ratings yet

- Sujet No 10 PhysiqueDocument7 pagesSujet No 10 PhysiqueYassir RochdNo ratings yet

- Phy 3Document13 pagesPhy 3Yassir Rochd100% (1)

- Série Ec PDFDocument2 pagesSérie Ec PDFYassir RochdNo ratings yet

- (Torrent9.red) Larousse - Orthographe - Les Indispensables PDFDocument122 pages(Torrent9.red) Larousse - Orthographe - Les Indispensables PDFgranmysteNo ratings yet

- Exo Gravitation 3 4 5 6 CorrDocument2 pagesExo Gravitation 3 4 5 6 CorrYassir RochdNo ratings yet

- TD Oscillation Mecanique 2014 Lolb-Wahab DiopDocument5 pagesTD Oscillation Mecanique 2014 Lolb-Wahab DiopYassir Rochd100% (2)

- Travail Et Puissance PDFDocument4 pagesTravail Et Puissance PDFYassir RochdNo ratings yet

- 3 1 Chapitre - 2Document6 pages3 1 Chapitre - 2Yassir RochdNo ratings yet

- ChampmagnDocument21 pagesChampmagnYassir RochdNo ratings yet

- TD Oscillation Mecanique 2014 Lolb-Wahab DiopDocument5 pagesTD Oscillation Mecanique 2014 Lolb-Wahab DiopYassir Rochd100% (2)

- Cinema TiqueDocument32 pagesCinema TiqueAhmed HaniNo ratings yet

- Chimie C Chap11 Application Electrolyse PDFDocument1 pageChimie C Chap11 Application Electrolyse PDFYassir RochdNo ratings yet

- Chimie C Chap11 Application Electrolyse PDFDocument1 pageChimie C Chap11 Application Electrolyse PDFYassir RochdNo ratings yet

- TermS PH Chap11Document17 pagesTermS PH Chap11Yassir RochdNo ratings yet

- Theorie PenduleDocument8 pagesTheorie PenduleNeneNo ratings yet

- Exercices de DYNAMIQUE de RotationDocument13 pagesExercices de DYNAMIQUE de RotationYassir RochdNo ratings yet

- Ex Dipole RLCDocument4 pagesEx Dipole RLClamilouch6498100% (1)

- Ex Dipole RLCDocument4 pagesEx Dipole RLClamilouch6498100% (1)

- Tp03complet PDFDocument12 pagesTp03complet PDFYassir RochdNo ratings yet

- Exercice Bac Blanc Physique Ondes Sonores PDFDocument3 pagesExercice Bac Blanc Physique Ondes Sonores PDFYassir Rochd50% (2)

- Transformations Lentes Et RapidesDocument10 pagesTransformations Lentes Et RapidesJosé Ahanda NguiniNo ratings yet

- Cours 3 Circuits LogiquesDocument92 pagesCours 3 Circuits LogiquesDonMidowNo ratings yet

- Evaluation N04 6emeDocument2 pagesEvaluation N04 6emeCedric LenantaisNo ratings yet

- SPSS 1Document11 pagesSPSS 1AhlemNo ratings yet

- Fusionneuse FSM-60SDocument1 pageFusionneuse FSM-60Syass8888No ratings yet

- SQL LoaderDocument11 pagesSQL Loaderyvelin001No ratings yet

- Installation Du Serveur Exchange 2003Document13 pagesInstallation Du Serveur Exchange 2003neoman552No ratings yet

- Coding 11Document93 pagesCoding 11NasreddineNo ratings yet

- Instructions SQLDocument14 pagesInstructions SQLAime SeriNo ratings yet

- Formation Oracle VM AdministrationDocument156 pagesFormation Oracle VM AdministrationIsshin KurosakiNo ratings yet

- TP2 Mout104Document5 pagesTP2 Mout104Abdallah GrimaNo ratings yet

- Exposé TEC 3Document2 pagesExposé TEC 3Ayoub AfqirNo ratings yet

- SNMPDocument477 pagesSNMPbmabdouNo ratings yet

- CV TarikDocument2 pagesCV TarikdualcorefreeNo ratings yet

- 798315.10 - Matériel Déporté MDXLDocument2 pages798315.10 - Matériel Déporté MDXLefsloug100% (1)

- MB Memory A320m-S2h Raven 20181220 PDFDocument8 pagesMB Memory A320m-S2h Raven 20181220 PDFDaniel Da RochaNo ratings yet

- 3eme SEDUENCESDocument4 pages3eme SEDUENCESLuidovie12 SigneNo ratings yet

- Video Portero DH VTK Vto5000c Vth1200dsDocument2 pagesVideo Portero DH VTK Vto5000c Vth1200dsJuan Marcelo RiveroNo ratings yet

- Initiation Excel 2007Document42 pagesInitiation Excel 2007hjayekoue01No ratings yet