Professional Documents

Culture Documents

Actividad Complementaria U1

Uploaded by

Louis CharlesOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Actividad Complementaria U1

Uploaded by

Louis CharlesCopyright:

Available Formats

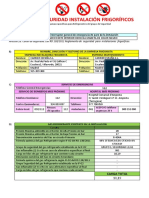

ACTIVIDADES COMPLEMENTARIAS Unidad 1.

Circuitos secuenciales bsicos

Una vez finalizadas las dos actividades complementarias de esta unidad, comprima el archivo en formato zip o rar, dando clic derecho al archivo, Enviar a, Carpeta comprimida. Luego envelas a su facilitador a travs del medio utilizado para tal fin en el curso. Actividad complementaria 1

Llenar las siguientes tablas correspondientes al funcionamiento de cada uno de los siguientes circuitos secuenciales. Tenga en cuenta los simuladores que se encuentran en los contenidos de la unidad 1, all encontrar la manera de realizar la verificacin de circuito combinacional, tabla de verdad y diagrama de tiempos de cada circuito secuencial. Funcionamiento de latch SR con entrada activa en nivel alto Circuito Ubica las entradas R y S y las salidas Q y Q (escribiendo en combinacional las casillas en blanco) en el siguiente diagrama.

Tabla de verdad

Llena la tabla de la verdad de acuerdo al comportamiento de las entradas Entrad as S R 0 0 0 1 1 0 1 1 salidas Q q 0 1 0 Q0 q 1 0 0 Comentario de funcionamiento Estado anterior, permanece igual Reset Set Estado prohibido

Diagrama de tiempos

Raye el cronograma de acuerdo al comportamiento de la tabla de verdad. Ejemplo de cmo llenar la cuadricula del diagrama de tiempos

Funcionamiento de latch SR con entrada activa en nivel Bajo Circuito Ubica las entradas R y S y las salidas Q y Q (escribiendo en combinacional las casillas en blanco) en el siguiente diagrama.

Tabla de verdad

Llena la tabla de la verdad de acuerdo al comportamiento de las entradas Entrad as S R 0 0 0 1 1 0 1 1 salidas Q 1 1 0 q Q 1 0 1 Q Comentario de funcionamiento Estado prohibido Set Reset Estado anterior

Diagrama de tiempos

Raye el cronograma de acuerdo al comportamiento de la tabla de verdad. Ejemplo de cmo llenar la cuadricula del diagrama de tiempos

Funcionamiento de latch SR con entrada activa de validacin Circuito Ubica las entradas E, R y S y las salidas Q y Q (escribiendo combinacional en las casillas en blanco) en el siguiente diagrama.

Tabla de verdad

Llena la tabla de la verdad de acuerdo al comportamiento de las entradas Entradas salidas Comentario de

E 1 1 1 0 Diagrama de tiempos

S 0 0 1 1

R 0 1 0 1

Raye el cronograma de acuerdo al comportamiento de la tabla de verdad. Ejemplo de cmo llenar la cuadricula del diagrama de tiempos

Actividad complementaria 2 Llenar las siguientes tablas correspondientes al funcionamiento de cada uno de los siguientes circuitos secuenciales. Tenga en cuenta los simuladores que se encuentran en los contenidos de la unidad 1, all encontrar la manera de realizar la verificacin de circuito combinacional, tabla de verdad y diagrama de tiempos de cada circuito secuencial.

Circuito combinacional

Funcionamiento de latch D Ubica las entradas E y D y las salidas Q y Q (escribiendo en las casillas en blanco) en el siguiente diagrama.

Tabla de verdad

Llena la tabla de la verdad de acuerdo al comportamiento de las entradas

Entrad as E D 1 0 1 1 0 X Diagrama de tiempos

salida s Q Q 0 1 1 0 0 0

Comentario de funcionamiento Reset Set No importa

Raye el cronograma de acuerdo al comportamiento de la tabla de verdad. Ejemplo de cmo llenar la cuadricula del diagrama de tiempos

Circuito combinacional

Funcionamiento de Flip-Flop SR Ubica las entradas CLK, S y R y las salidas Q y Q (escribiendo en las casillas en blanco) en el siguiente diagrama.

Tabla de

Llena la tabla de la verdad de acuerdo al comportamiento

verdad

de las entradas Entradas S 0 0 1 1 R 0 1 0 1 CL K X salida s Q Q Comentario funcionamiento de

Diagrama de tiempos

Raye el cronograma de acuerdo al comportamiento de la tabla de verdad. Ejemplo de cmo llenar la cuadricula del diagrama de tiempos

Circuito combinacional

Funcionamiento de Flip-Flop Jk Ubica las entradas CLK, J y K y las salidas Q y Q (escribiendo en las casillas en blanco) en el siguiente diagrama.

Tabla de verdad

Llena la tabla de la verdad de acuerdo al comportamiento de las entradas

Entradas J 0 0 1 1 K 0 1 0 1 CL K

salidas Q Nc 0 1 Ca m Q Nc 1 0 ca m

Comentario funcionamiento EL ESTADO NO CAMBIA RESET SET Cambia Estado

de

Diagrama de tiempos

Raye el cronograma de acuerdo al comportamiento de la tabla de verdad. Ejemplo de cmo llenar la cuadricula del diagrama de tiempos

Actividad complementaria 3 Realice una lista de aplicaciones donde estn implcitos los flip-flop tipo D, T y maestro-esclavo. Aplicaciones de Flip-Flop Flip-Flop Aplicaciones

Tipo D

Aplicaciones contadores.

de

circuitos

secuenciales

como

registros,

Tipo T

Su aplicacin ms importante son los Contadores.

Maestro-esclavo

Transferencia de datos binarios.

You might also like

- 8-Sistemas Secuenciales SincronosDocument60 pages8-Sistemas Secuenciales SincronosJose Luis Lobo Lara100% (1)

- 10 BiestablesDocument45 pages10 BiestablesFERMINNo ratings yet

- Contadores J-KDocument14 pagesContadores J-KYessenia López0% (1)

- CIrcuitos SecuencialesDocument7 pagesCIrcuitos SecuencialesJasmany FaritNo ratings yet

- 1cuidar Al Que Cuida - Red PROSAMIC-BENTOLILADocument82 pages1cuidar Al Que Cuida - Red PROSAMIC-BENTOLILAFlavia Chiarelli100% (1)

- Influencia Del Cambio Climatico en El Fenotipo y GenotipoDocument21 pagesInfluencia Del Cambio Climatico en El Fenotipo y GenotipoJuvenal Huillcara YllaNo ratings yet

- Flip Flops tablas características y señal de sincroníaDocument17 pagesFlip Flops tablas características y señal de sincroníaChvd OzNo ratings yet

- Ejercicios de Integrales de Línea, Superficie y VolumenFrom EverandEjercicios de Integrales de Línea, Superficie y VolumenRating: 4 out of 5 stars4/5 (2)

- Teoría Circuitos SecuencialesDocument17 pagesTeoría Circuitos SecuencialesLuisma_plasenciaNo ratings yet

- Flip Flop Informe 4 Circuitos Electrónicos IIDocument13 pagesFlip Flop Informe 4 Circuitos Electrónicos IIDavid IturriagaNo ratings yet

- Apunte - Maritza Montero. Introducción A La Psicología Comunitaria. Cap 8 - La Participación en El Trabajo Comunitario.Document8 pagesApunte - Maritza Montero. Introducción A La Psicología Comunitaria. Cap 8 - La Participación en El Trabajo Comunitario.Belén Canteros0% (1)

- Circuitos Secuenciales BásicoDocument4 pagesCircuitos Secuenciales BásicoAnonymous bcbZ8VNo ratings yet

- Plan Integral de Seguridad y Accidentes EscolaresDocument17 pagesPlan Integral de Seguridad y Accidentes EscolaresYosen Barrera BravoNo ratings yet

- Unidad 1. Circuitos Secuenciales Básicos: Actividades ComplementariasDocument44 pagesUnidad 1. Circuitos Secuenciales Básicos: Actividades ComplementariasFelipe CortesNo ratings yet

- Actividad 1 Electronica Digital Secuencial-Andres DelgadoDocument14 pagesActividad 1 Electronica Digital Secuencial-Andres DelgadoAndresFelipeDelgadoGomezz100% (1)

- Act Complementarias U1Document5 pagesAct Complementarias U1mattgafaroNo ratings yet

- Circuitos secuenciales básicos - Tablas y diagramasDocument9 pagesCircuitos secuenciales básicos - Tablas y diagramasAlex Diego Rivera TorresNo ratings yet

- Circuitos secuenciales SENADocument5 pagesCircuitos secuenciales SENAAnthony Acosta SolanoNo ratings yet

- Electronica Secuenciales SENA, Act Com 1Document32 pagesElectronica Secuenciales SENA, Act Com 1leoncourt100% (1)

- So Luci On Taller PDFDocument6 pagesSo Luci On Taller PDFFabian ForeroNo ratings yet

- Actividades Complementarias 1 Electrónica Digital SecuencialDocument12 pagesActividades Complementarias 1 Electrónica Digital SecuencialJoseManuelFlorezMurilloNo ratings yet

- Desarrollo Actividad Complementaria U3 Diana MenesesDocument7 pagesDesarrollo Actividad Complementaria U3 Diana MenesesD Carolina MenesesNo ratings yet

- ºººººººººººººººººººººººººººººººººººººººººººººººDocument4 pagesºººººººººººººººººººººººººººººººººººººººººººººººOzkaar Ivaan Jr.No ratings yet

- Practica4 FCO Biestables 010918Document6 pagesPractica4 FCO Biestables 010918alejandravallesgalanNo ratings yet

- Act - Complementarias - U3 - ERNESTO PINTODocument21 pagesAct - Complementarias - U3 - ERNESTO PINTOSofia GomezNo ratings yet

- Electronica Secuenciales SENA, Actividad Com 3Document8 pagesElectronica Secuenciales SENA, Actividad Com 3leoncourtNo ratings yet

- Sistemas SecuencialesDocument13 pagesSistemas SecuencialesMeliandNo ratings yet

- Soldador 200Document4 pagesSoldador 200bran.luna5794No ratings yet

- Circuitos Secuenciales SincronosDocument7 pagesCircuitos Secuenciales SincronosAndrea RamosNo ratings yet

- 1Document15 pages1Benjamin AlonsoNo ratings yet

- Circuitos secuenciales: Latches y diagramas de tiempoDocument11 pagesCircuitos secuenciales: Latches y diagramas de tiempoDayana ArmendárizNo ratings yet

- Contadores secuencialesDocument7 pagesContadores secuencialesdarj01No ratings yet

- Actividades Complementarias Unidad 3Document7 pagesActividades Complementarias Unidad 3jenniferNo ratings yet

- Unidad 3 - SecuencialesDocument28 pagesUnidad 3 - SecuencialesLoreley DominguezNo ratings yet

- Electronica Secuenciales SENA Actividad Com 3Document7 pagesElectronica Secuenciales SENA Actividad Com 3AndresFelipeDelgadoGomezzNo ratings yet

- Diseño de Circuitos Secuenciales AsincronosDocument6 pagesDiseño de Circuitos Secuenciales AsincronoshectorfmirandaNo ratings yet

- Examen Flip FlopDocument14 pagesExamen Flip FlopJavier ParragaNo ratings yet

- Biestable 100217123621 Phpapp01Document23 pagesBiestable 100217123621 Phpapp01Aracely CuyuchNo ratings yet

- Guia 2A Grado Undecimo Diseño de ContadoresDocument10 pagesGuia 2A Grado Undecimo Diseño de ContadoresEstefanyNo ratings yet

- Flip Flops Und2Document9 pagesFlip Flops Und2cpyin88No ratings yet

- Detector de SecuenciaDocument3 pagesDetector de SecuenciaJorge IbarraNo ratings yet

- U4 Diseno Circuitos Secuenciales SincronosDocument13 pagesU4 Diseno Circuitos Secuenciales SincronosLizeth BenavidesNo ratings yet

- Practica 2 Flip FlopsDocument16 pagesPractica 2 Flip FlopsJean Carlos Colcas DueñasNo ratings yet

- Flip FlopDocument11 pagesFlip FlopJhon WilliamNo ratings yet

- Flip FlopsDocument12 pagesFlip FlopsArmando Galaviz100% (1)

- Marco TeoricoDocument20 pagesMarco TeoricoCarlos A. Pineda ChavarriaNo ratings yet

- Sistemas Electricos y ElectronicosDocument7 pagesSistemas Electricos y ElectronicosCristian LopezNo ratings yet

- Latch D y S-RDocument34 pagesLatch D y S-RSonia JiangNo ratings yet

- Act Complementaria 3Document5 pagesAct Complementaria 3Flor Stella Martinez HerediaNo ratings yet

- Prepa LDocument8 pagesPrepa LSaurumBlackNo ratings yet

- Contador BCD síncrono 4 bits con flip-flops J-KDocument9 pagesContador BCD síncrono 4 bits con flip-flops J-KLuis Alberto Sota OrellanaNo ratings yet

- Final N° 7 Flip FlopsDocument13 pagesFinal N° 7 Flip FlopsJohn PachecoNo ratings yet

- Contadores y RegistrosDocument19 pagesContadores y RegistrosElymar91No ratings yet

- Flipflop 27-11-13Document6 pagesFlipflop 27-11-13meoviedo2004No ratings yet

- Métodos Numéricos EjerciciosDocument14 pagesMétodos Numéricos EjerciciosahalonsoNo ratings yet

- Electrónica Digital IIDocument58 pagesElectrónica Digital IIDavid PiñaNo ratings yet

- Teoría de Máquinas de EstadoDocument15 pagesTeoría de Máquinas de EstadojulyandreagomezcamperosNo ratings yet

- Mi Parte Lab 8 ElectrónicaDocument4 pagesMi Parte Lab 8 ElectrónicaKnelson SalcedoNo ratings yet

- Ensayo SociologiaDocument4 pagesEnsayo SociologiaLouis CharlesNo ratings yet

- INFORME DE PASANTìAS REALIZADAS EN LA GOBERNACIoN DE SUCRE - Ultimate PDFDocument82 pagesINFORME DE PASANTìAS REALIZADAS EN LA GOBERNACIoN DE SUCRE - Ultimate PDFLouis Charles100% (1)

- Estadistica Paso 4Document20 pagesEstadistica Paso 4Louis Charles100% (2)

- El Modelo OsiDocument9 pagesEl Modelo OsiLouis CharlesNo ratings yet

- SuperStack II Hub ™ 10Document16 pagesSuperStack II Hub ™ 10Louis CharlesNo ratings yet

- Estadistica Paso 4Document20 pagesEstadistica Paso 4Louis Charles100% (2)

- INFORME DE PASANTÍAS REALIZADAS EN LA GOBERNACIÓN DE SUCRE - UltimateDocument87 pagesINFORME DE PASANTÍAS REALIZADAS EN LA GOBERNACIÓN DE SUCRE - UltimateLouis CharlesNo ratings yet

- Complement AriaDocument17 pagesComplement AriaLouis CharlesNo ratings yet

- Actividad 3Document9 pagesActividad 3Louis CharlesNo ratings yet

- Actividad Central U1Document12 pagesActividad Central U1Louis CharlesNo ratings yet

- Solucion - de - Guia 3 y 4Document15 pagesSolucion - de - Guia 3 y 4Louis CharlesNo ratings yet

- Algoritmo Ac4Document2 pagesAlgoritmo Ac4Louis CharlesNo ratings yet

- Act Complementarias U2Document12 pagesAct Complementarias U2Louis Charles20% (5)

- CentralDocument6 pagesCentralLouis Charles100% (1)

- Act Central U2Document9 pagesAct Central U2Louis Charles83% (6)

- Informe de Circuitos Logicos (Contadores) 4Document18 pagesInforme de Circuitos Logicos (Contadores) 4Louis Charles86% (7)

- El ComputadorDocument3 pagesEl ComputadorLouis CharlesNo ratings yet

- Actividad 4Document5 pagesActividad 4Louis CharlesNo ratings yet

- Flip FlopsDocument6 pagesFlip Flopsmono28No ratings yet

- Actividad 2Document6 pagesActividad 2Louis CharlesNo ratings yet

- GSMDocument10 pagesGSMLouis CharlesNo ratings yet

- CIRUITOS LOGICOS - InformeDocument16 pagesCIRUITOS LOGICOS - InformeLouis CharlesNo ratings yet

- Guía ZENERDocument6 pagesGuía ZENERLouis CharlesNo ratings yet

- Mantenimiento PreventivoDocument6 pagesMantenimiento PreventivoLouis CharlesNo ratings yet

- Informe de Circuitos Logico 1Document9 pagesInforme de Circuitos Logico 1Louis CharlesNo ratings yet

- Implementación de Un Latch RSDocument17 pagesImplementación de Un Latch RSLouis CharlesNo ratings yet

- Flip Flop InformeDocument14 pagesFlip Flop InformeLouis Charles100% (3)

- Contador Asincrono DecendenteDocument7 pagesContador Asincrono DecendenteLouis CharlesNo ratings yet

- Control ConvertidoresDocument7 pagesControl ConvertidoresLouis CharlesNo ratings yet

- Propiedas Físicas, Principio de Pierre CurieDocument15 pagesPropiedas Físicas, Principio de Pierre CurieRosmery LizNo ratings yet

- Buenas Prácticas Archivísticas Cuestionario 9Document8 pagesBuenas Prácticas Archivísticas Cuestionario 9JIMENA FLORES SANCHEZNo ratings yet

- Ensayos de Laboratorio - Dr2Document77 pagesEnsayos de Laboratorio - Dr2Carlos Alberto Torres TerronesNo ratings yet

- Fuente de alimentación regulada triple 1,2V-24V con salidas fijas de 5V y 12VDocument35 pagesFuente de alimentación regulada triple 1,2V-24V con salidas fijas de 5V y 12VFacundo HerreraNo ratings yet

- Prueba de Hipotesis de Chi CuadradoDocument49 pagesPrueba de Hipotesis de Chi CuadradoEriksen Mallma MoránNo ratings yet

- Agenda VI ENCUENTRO DE PRACTICANTES Y GRADUADOS EXITOSOS-1Document3 pagesAgenda VI ENCUENTRO DE PRACTICANTES Y GRADUADOS EXITOSOS-1Natalia GomezNo ratings yet

- Energía histórica: Fuentes y conversiónDocument4 pagesEnergía histórica: Fuentes y conversiónPamela BellendirNo ratings yet

- 0606 Sistemas Operativos 2003-2Document5 pages0606 Sistemas Operativos 2003-2iespaaNo ratings yet

- Acondicionadores de TejidoDocument18 pagesAcondicionadores de Tejidogdvrchpx52No ratings yet

- Investigacion FormativaDocument6 pagesInvestigacion FormativaaydeeNo ratings yet

- Planificación y Desarrollo de Los Destinos TurísticosDocument11 pagesPlanificación y Desarrollo de Los Destinos TurísticosEmma RamosNo ratings yet

- Estilos de aprendizaje VAKDocument6 pagesEstilos de aprendizaje VAKPsic Manuel de los SantosNo ratings yet

- Buscar valores en filas con BUSCARHDocument6 pagesBuscar valores en filas con BUSCARHViviana Jimenez SánchezNo ratings yet

- BO5002825 - E-Es - ACECUT 5503 Cutting FluidDocument9 pagesBO5002825 - E-Es - ACECUT 5503 Cutting FluidJamis Frank Silva ArmasNo ratings yet

- Informe 3 Analoga 1 Alay SebastianDocument3 pagesInforme 3 Analoga 1 Alay SebastianCallejas Ochoa Juan SebastianNo ratings yet

- Practica-N4-Resuelta Diseños ExperimentalesDocument63 pagesPractica-N4-Resuelta Diseños ExperimentalesAnder RuizNo ratings yet

- Organizadores de La Informacion-1Document18 pagesOrganizadores de La Informacion-1Héctor Adame ValdezNo ratings yet

- TC Electronic Toneprint Editor Manual EspañolDocument19 pagesTC Electronic Toneprint Editor Manual EspañolmatiasnancupanNo ratings yet

- Análisis PersonalDocument3 pagesAnálisis PersonalMarco MartínezNo ratings yet

- Cartel Inspeccion AmpostaDocument2 pagesCartel Inspeccion Ampostavideos gym VictorPascualNo ratings yet

- Tema 6 Teoría Unid. EstratigraficasDocument22 pagesTema 6 Teoría Unid. EstratigraficasCarlos Gonzalez VergaraNo ratings yet

- 02 Cinemática 1DDocument3 pages02 Cinemática 1DFrancis Nicole Huarcaya PalominoNo ratings yet

- Punch ListDocument1 pagePunch ListTomas VelasquezNo ratings yet

- Sistemas II Unidad 5Document36 pagesSistemas II Unidad 5Mariela Alvarez RuedaNo ratings yet

- Arjun Appadurai en Su Libro “La Modernidad Desbordada- Dimensiones Culturales de La Globalización” Plantea Una Teoría de La Ruptura, En La Cual Sostiene Que La Modernidad Es Una Etapa Reciente en Donde Grandes Flujos rDocument2 pagesArjun Appadurai en Su Libro “La Modernidad Desbordada- Dimensiones Culturales de La Globalización” Plantea Una Teoría de La Ruptura, En La Cual Sostiene Que La Modernidad Es Una Etapa Reciente en Donde Grandes Flujos rEmanuel AlejandroNo ratings yet

- Caso Practico Conciliación Bancaria 2Document3 pagesCaso Practico Conciliación Bancaria 2magaliNo ratings yet