Professional Documents

Culture Documents

Logic Design June 2010 ES

Uploaded by

Prasad C MOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Logic Design June 2010 ES

Uploaded by

Prasad C MCopyright:

Available Formats

I I I I I I I I I I I

Time: 3 hrs.

For More Question Papers Visit - http://pediawikiblog.blogspot.com 06ES33

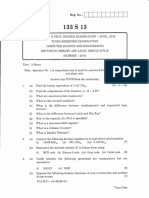

Third Semester B.E. Degree Examination, May/June 2010 Logic Design

Max. Marks: 100

Note: Answer any FIVE full questions, selecting at least TWO questions from each part.

PART-A

Simplify the following expressions using k - map. Implement the simplified expression using basic gates : i) T = f(wxyz) = l:m(2, 3, 4, 5, 13, 15) + l:d(8, 9, 10, 11) ii) R = f(abcd) = nM(2, 3, 4, 6, 7, 10, 11, 12). (12 Marks) . b. Place the following equations into proper canonical form : i) P = f(a, b, c)= ab' + ab' +be ii) T = f(a, b, c) (a+ b') (b' +c). (04 Marks) c. Define the following terms: i) Minimum iii) Canonical sum of products ii) Maximum iv) Canonical product of sum. (04 Marks) Simplify the logic function given below using variable entered mapping {VEM) technique : f(a, b, c, d)= l:m(2, 9, 10, 11, 13, 14, 15). (08 Marks) b. Simplify the following function using Quine-McClusky minimization technique: T = f(a, b, c, d)= l:m(O, 1, 2, 3, 6, 7, 8, 9, 14, 15). (12 Marks) Design a combinational logic circuit to output the 2's compliment of a 4-bit binary numbers: i) Construct the truth table ii) Simplify each output function using k-map and write reduced equations (12 Marks) iii) Draw the resulting logic diagram. b. Construct a scheme to obtain a 4-to-16line decoder using 74138 (3-8 line decoder). c. Write a note on encodes.

(OS Marks) (03 Marks)

a.

a.

a.

a. Realize the following Boolean function f(ABC) = 2:(0, 1, 3, 5, 7) using, i) 8 : lmux(74151) ii) 4: lmux(74153). (06 Marks) b. Design a comparator to check if two n-bit numbers are equal. Configure this using cascaded stage of 1 bit equality comparator. (08 Marks) c. Implement full subtractor using gates and write a truth table. (06 Marks)

PART-B

a. Explain the operation of SR latch. Explain one of its applications. b. Draw the logic diagrams for i) Gated SR latch iii) Master slave JK flip flop ii) Master slave SR flip flop iv) Positive edge triggered 'D' flip flop.

(12 Marks)

(08 Marks)

a. Differentiate between combinational logic circuit and sequential logic circuits. (03 Marks) b. Explain universal shift register with the help of logic diagram, mode control table and (09 Marks) symbol. c. Explain Jonson counter, with its circuit diagram, and timing diagram. (08 Marks)

For More Question Papers Visit - http://pediawikiblog.blogspot.com

For More Question Papers Visit - http://pediawikiblog.blogspot.com

a. b.

Explain Moore and Meclay models for clocked synchronous sequential circuits. Construct the excitation table, transition table, state table and state diagram, for sequential circuit shown in Fig. Q7(b).

Moore

~---r~---r---;5~

or-----o(..

~--~~~----~-4~

...ll.SL Fig. Q7(b)

a. b. c.

Write a note on construction of state diagram. (OS Marks) Design a counter using JK-flip flops whose counting sequence is 000,001, 100, 110, Ill, 101, 000 etc., by obtaining its minimal sum equations. (10 Marks) Write a note on characteristic equations. (OS Marks)

*****

For More Question Papers Visit - http://pediawikiblog.blogspot.com

You might also like

- Logic Design July 2009 ESDocument1 pageLogic Design July 2009 ESPrasad C MNo ratings yet

- Logic Design Jan 2010 OldDocument1 pageLogic Design Jan 2010 OldPrasad C MNo ratings yet

- Switching Theory and Logic Design Exam QuestionsDocument4 pagesSwitching Theory and Logic Design Exam QuestionsrangerNo ratings yet

- Logic Design Jan 2010 ESDocument2 pagesLogic Design Jan 2010 ESPrasad C MNo ratings yet

- Digital Logic DesignDocument4 pagesDigital Logic DesignShareef KhanNo ratings yet

- 07a4ec09 STLDDocument6 pages07a4ec09 STLDSRINIVASA RAO GANTANo ratings yet

- 9A04401 Switching Theory and Logic DesignDocument4 pages9A04401 Switching Theory and Logic DesignsivabharathamurthyNo ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- Digital Logic DesignDocument4 pagesDigital Logic DesignrppvchNo ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- Switching Theory and Logic DesignDocument6 pagesSwitching Theory and Logic DesignVijay MNo ratings yet

- WWW - Manaresults.Co - In: (Common To Ece, Eie, Etm)Document2 pagesWWW - Manaresults.Co - In: (Common To Ece, Eie, Etm)Anil Kumar BNo ratings yet

- 21 - 2010 - Nov - R09 - STLDDocument8 pages21 - 2010 - Nov - R09 - STLDvasuvlsiNo ratings yet

- KEE401 ASSIGNMENTS and QUESTION BANKDocument17 pagesKEE401 ASSIGNMENTS and QUESTION BANKPrince VermaNo ratings yet

- BCA I I Digital SystemDocument4 pagesBCA I I Digital SystemAmory Sabri AsmaroNo ratings yet

- II B.Tech II Semester, Regular Examinations, April - 2012 Switching Theory and Logic DesignDocument8 pagesII B.Tech II Semester, Regular Examinations, April - 2012 Switching Theory and Logic Design142545No ratings yet

- UNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Document18 pagesUNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Deepak NaiduNo ratings yet

- DPSDDocument16 pagesDPSDDhilip PrabakaranNo ratings yet

- Switching Theory and Logic DesignDocument8 pagesSwitching Theory and Logic DesignVenkat ChadalavadaNo ratings yet

- r05220403 Switching Theory and Logic DesignDocument8 pagesr05220403 Switching Theory and Logic DesignSRINIVASA RAO GANTANo ratings yet

- Digital Logic System CSC 201Document2 pagesDigital Logic System CSC 201hahnonimusNo ratings yet

- 9a04306-Digital Logic DesignDocument1 page9a04306-Digital Logic DesignSheikh Noor MohammadNo ratings yet

- EC2203 Digital Electronics Question BankDocument16 pagesEC2203 Digital Electronics Question BankSophiaKaviNo ratings yet

- Digital Electronics & Fundamentals of Microprocessor: B.E. (Information Technology) Third Semester (C.B.S.)Document2 pagesDigital Electronics & Fundamentals of Microprocessor: B.E. (Information Technology) Third Semester (C.B.S.)Hamit BisaneNo ratings yet

- Fourth Semester BE Degree Exam Model Question Paper Analysis and Design of AlgorithmsDocument4 pagesFourth Semester BE Degree Exam Model Question Paper Analysis and Design of AlgorithmsMohnish RajuNo ratings yet

- Module-1: Set No. 1Document2 pagesModule-1: Set No. 1Omkar MutalikNo ratings yet

- Department of EceDocument8 pagesDepartment of Ecerajendr_46No ratings yet

- Switching Theory and Logic DesignDocument8 pagesSwitching Theory and Logic DesignSubrahmanyam VjsNo ratings yet

- Switching Theory and Logic Design QuestionsDocument8 pagesSwitching Theory and Logic Design QuestionsvasuvlsiNo ratings yet

- WWW - Manaresults.Co - In: (Common To CSE, IT)Document2 pagesWWW - Manaresults.Co - In: (Common To CSE, IT)Sajjad KhanNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)kenny kannaNo ratings yet

- Logic and Switching TheoryDocument2 pagesLogic and Switching TheorySatish Bojjawar0% (1)

- MCA MGTDocument88 pagesMCA MGTAshfaq KhanNo ratings yet

- 08AB303 - DIGITAL LOGIC CIRCUITSDocument3 pages08AB303 - DIGITAL LOGIC CIRCUITSChandru RamaswamyNo ratings yet

- WWW - Manaresults.Co - In: II B. Tech I Semester Model Question Paper Oct/Nov - 2017 Switching Theory and Logic DesignDocument4 pagesWWW - Manaresults.Co - In: II B. Tech I Semester Model Question Paper Oct/Nov - 2017 Switching Theory and Logic Designbadiganti tejakrishnaNo ratings yet

- 3330 MergedDocument8 pages3330 MergedHamit BisaneNo ratings yet

- BT3RNOV2015Document79 pagesBT3RNOV2015balu56kv100% (1)

- Digital Electronics Question BankDocument3 pagesDigital Electronics Question BankNandha Kizor VNo ratings yet

- Jntuk 2 1 DLD Nov 2017 Q.PDocument5 pagesJntuk 2 1 DLD Nov 2017 Q.PRoopa Krishna ChandraNo ratings yet

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.Monica NareshNo ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- QBank DPSD cs2202Document6 pagesQBank DPSD cs2202kunarajNo ratings yet

- 2 IT201 Digital System Design - Supple - July 2017 1Document2 pages2 IT201 Digital System Design - Supple - July 2017 1Gayatri SharmaNo ratings yet

- STLDDocument2 pagesSTLDANUPAMA PonnuNo ratings yet

- Ecs-301 Digital Logic Design 2010-11Document4 pagesEcs-301 Digital Logic Design 2010-11Satyedra MauryaNo ratings yet

- Bcs302-Ddco Assign1Document1 pageBcs302-Ddco Assign1dwqvehmhtqofoizpsoNo ratings yet

- R7210504 Digital Logic DesignDocument1 pageR7210504 Digital Logic DesignsivabharathamurthyNo ratings yet

- Cs 60Document80 pagesCs 60Sirsendu RoyNo ratings yet

- ECE211 Digital ElectronicsDocument3 pagesECE211 Digital Electronicstejaputta6No ratings yet

- BCADocument76 pagesBCAArvinder SinghNo ratings yet

- Attainable Region Theory: An Introduction to Choosing an Optimal ReactorFrom EverandAttainable Region Theory: An Introduction to Choosing an Optimal ReactorNo ratings yet

- Let's Practise: Maths Workbook Coursebook 6From EverandLet's Practise: Maths Workbook Coursebook 6No ratings yet

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- 2nd PUC PhysicsJan 2016 PDFDocument2 pages2nd PUC PhysicsJan 2016 PDFPrasad C M90% (10)

- 2nd PUC Mathematics Mid Term Nov 2015 PDFDocument3 pages2nd PUC Mathematics Mid Term Nov 2015 PDFPrasad C M60% (10)

- 2nd PUC Physics Mid Term Nov 2015 PDFDocument1 page2nd PUC Physics Mid Term Nov 2015 PDFPrasad C M82% (11)

- 2nd PUC Kannada Jan 2016 PDFDocument2 pages2nd PUC Kannada Jan 2016 PDFPrasad C M81% (16)

- 2nd PUC Kannada Mide Term Nov 2015 PDFDocument2 pages2nd PUC Kannada Mide Term Nov 2015 PDFPrasad C M100% (5)

- 2nd PUC Mathematics Jan 2016 PDFDocument2 pages2nd PUC Mathematics Jan 2016 PDFPrasad C M100% (3)

- 2nd PUC English Jan 2016 PDFDocument4 pages2nd PUC English Jan 2016 PDFPrasad C M86% (14)

- 1st Year DIP Communication Skills in English - Dec 2015 PDFDocument4 pages1st Year DIP Communication Skills in English - Dec 2015 PDFPrasad C M100% (7)

- 2nd PUC Chemistry Jan 2016 PDFDocument2 pages2nd PUC Chemistry Jan 2016 PDFPrasad C M83% (6)

- 2nd PUC English Mid Term Nov 2015 PDFDocument4 pages2nd PUC English Mid Term Nov 2015 PDFPrasad C M78% (9)

- 2nd Sem DIP Appied Mathematics 2 - May 2015 PDFDocument4 pages2nd Sem DIP Appied Mathematics 2 - May 2015 PDFPrasad C M100% (8)

- 2nd PUC Biology Mid Term Nov 2015 PDFDocument1 page2nd PUC Biology Mid Term Nov 2015 PDFPrasad C M78% (9)

- 2nd PUC Chemistry Mid Term Nov 2015 PDFDocument2 pages2nd PUC Chemistry Mid Term Nov 2015 PDFPrasad C M100% (8)

- 2nd PUC Biology Jan 2016 PDFDocument2 pages2nd PUC Biology Jan 2016 PDFPrasad C M89% (9)

- 2nd Sem DIP Electrical Circuits - Dec 2015 PDFDocument3 pages2nd Sem DIP Electrical Circuits - Dec 2015 PDFPrasad C M100% (1)

- 2nd Sem DIP Applied Maths 2 - Dec 2015 PDFDocument4 pages2nd Sem DIP Applied Maths 2 - Dec 2015 PDFPrasad C M89% (9)

- 2nd Sem DIP Electrical Circuits - May 2015 PDFDocument4 pages2nd Sem DIP Electrical Circuits - May 2015 PDFPrasad C M100% (1)

- 2nd Sem DIP Electronics 1 - Dec 2015 PDFDocument3 pages2nd Sem DIP Electronics 1 - Dec 2015 PDFPrasad C MNo ratings yet

- 2nd Sem DIP Electrical Circuits - May 2013 PDFDocument3 pages2nd Sem DIP Electrical Circuits - May 2013 PDFPrasad C M100% (2)

- 2nd Sem DIP Electrical Circuits - May 2011 PDFDocument3 pages2nd Sem DIP Electrical Circuits - May 2011 PDFPrasad C MNo ratings yet

- 2nd SEM Electronics 1 - May 2011 PDFDocument2 pages2nd SEM Electronics 1 - May 2011 PDFPrasad C MNo ratings yet

- 2nd Sem DIP Electrical Circuits - Dec 2012 PDFDocument4 pages2nd Sem DIP Electrical Circuits - Dec 2012 PDFPrasad C MNo ratings yet

- 2nd Sem DIP Electrical Circuits - May 2010 PDFDocument3 pages2nd Sem DIP Electrical Circuits - May 2010 PDFPrasad C MNo ratings yet

- 2nd Sem DIP Electrical Circuits - Dec 2014 PDFDocument3 pages2nd Sem DIP Electrical Circuits - Dec 2014 PDFPrasad C MNo ratings yet

- 2nd Sem DIP Electrical Circuits - Dec 2013 PDFDocument3 pages2nd Sem DIP Electrical Circuits - Dec 2013 PDFPrasad C M100% (1)

- 2nd SEM Electronics 1 - Nov 2011 PDFDocument3 pages2nd SEM Electronics 1 - Nov 2011 PDFPrasad C MNo ratings yet

- 2nd SEM Electronics 1 - Dec 2014 PDFDocument3 pages2nd SEM Electronics 1 - Dec 2014 PDFPrasad C MNo ratings yet

- 2nd SEM Electronics 1 - May 2012 PDFDocument2 pages2nd SEM Electronics 1 - May 2012 PDFPrasad C MNo ratings yet

- Lc320wun SCB1Document44 pagesLc320wun SCB1fingersoundNo ratings yet

- GV 4095M 1 AVC Intra WhitepaperDocument10 pagesGV 4095M 1 AVC Intra WhitepaperJohn NaylorNo ratings yet

- BEL Catalog Type M2202i and MG2202iDocument2 pagesBEL Catalog Type M2202i and MG2202iUswatul HasanahNo ratings yet

- MA162 PanasonicSemiconductorDocument2 pagesMA162 PanasonicSemiconductorHasitha RatnayakeNo ratings yet

- M Spf20a (E14)Document106 pagesM Spf20a (E14)omar tlebNo ratings yet

- Diode Theory and The Semiconductor DiodeDocument21 pagesDiode Theory and The Semiconductor DiodeAnand JavierNo ratings yet

- CDJ 200 Service ManualDocument80 pagesCDJ 200 Service ManualbzrmiltosNo ratings yet

- The Main Circuit Board of A MicrocomputerDocument16 pagesThe Main Circuit Board of A Microcomputeramandeep123No ratings yet

- Chopper & SCRDocument11 pagesChopper & SCRSudipta DebnathNo ratings yet

- Commissioning and Maintenance of Electrical EquipmentDocument60 pagesCommissioning and Maintenance of Electrical Equipmentbisrat zerabirukNo ratings yet

- Amplifier Transistors: NPN SiliconDocument6 pagesAmplifier Transistors: NPN SilicondiegooliveiraEENo ratings yet

- AmoledDocument29 pagesAmoledShariq StreakNo ratings yet

- Windows Vista Installation GuideDocument8 pagesWindows Vista Installation GuideThi HaNo ratings yet

- Toshiba VF nC3 ManualDocument243 pagesToshiba VF nC3 ManualJoelson Geronimo CamposNo ratings yet

- YAMAHA RX-V393 User GuideDocument43 pagesYAMAHA RX-V393 User GuideJuan GutierrezNo ratings yet

- Enhancement Mode MOSFET (N-Channel)Document8 pagesEnhancement Mode MOSFET (N-Channel)De Jesus VillarroelNo ratings yet

- BCD to 7-Segment Decoder Converts NumbersDocument7 pagesBCD to 7-Segment Decoder Converts NumbersBOMMA SRI MUKHINo ratings yet

- Metalux Uhb Round Led High Bay SpecsheetDocument2 pagesMetalux Uhb Round Led High Bay SpecsheetAlejandro GrajedaNo ratings yet

- DKE667 ch14 PDFDocument25 pagesDKE667 ch14 PDFPhuRioNo ratings yet

- QHE in GrapheneDocument1 pageQHE in GrapheneSharan DevaiahNo ratings yet

- EE203 Electrical MeasurementsDocument2 pagesEE203 Electrical MeasurementsReeta DuttaNo ratings yet

- Catalogo Chekman 1Document32 pagesCatalogo Chekman 1Ramos JorgeNo ratings yet

- Smart Helmet PPT Final Year AdvancedDocument20 pagesSmart Helmet PPT Final Year AdvancedAnubhab DasNo ratings yet

- CP1 B9 Lecture No. 4 - Short Circuit Analysis PDFDocument195 pagesCP1 B9 Lecture No. 4 - Short Circuit Analysis PDFHillNo ratings yet

- TC906A, TC907A, TC908A: Eclipse™ Series: Intelligent Low-Profile Plug-In DetectorsDocument2 pagesTC906A, TC907A, TC908A: Eclipse™ Series: Intelligent Low-Profile Plug-In DetectorssureshNo ratings yet

- HTCdev - Unlock BootloaderDocument3 pagesHTCdev - Unlock BootloaderKripender SinghNo ratings yet

- Universal Synchronous Asynchronous Receive/Transmit USART: MSP430 Family USART Peripheral InterfaceDocument52 pagesUniversal Synchronous Asynchronous Receive/Transmit USART: MSP430 Family USART Peripheral InterfaceEnrico W. FebriardyNo ratings yet

- Moonlight Serenade - GuitarDocument1 pageMoonlight Serenade - Guitarscook6891No ratings yet

- Fanuc Intro UpDocument112 pagesFanuc Intro UpSakalrobo100% (2)

- KDocument32 pagesKFathimath SajahathNo ratings yet