Professional Documents

Culture Documents

4.hybrid Cascaded Multilevel Inverter

Uploaded by

Shareef KhanOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

4.hybrid Cascaded Multilevel Inverter

Uploaded by

Shareef KhanCopyright:

Available Formats

Hybrid Cascaded Multilevel Inverter with PWM Control Method

ABSTRACT

A hybrid cascaded multilevel inverter with PWM method is presented in this paper. It consists of a standard 3-leg inverter (one leg for each phase) and H-bridge in series with each inverter leg. It can use only a single DC power source to supply a standard 3-leg inverter along with three full H-bridges supplied by capacitors. Multilevel carrier based PWM method is used to produce a five-level phase voltage. The inverter can be used in hybrid electric vehicles (HEV) and electric vehicles (EV). A simulation model based on PSIM and

MATLAB/SIMULINK is developed. An experimental 5 kW prototype inverter is built and tested. The results experimentally validate the proposed PWM hybrid cascaded multilevel inverter

I. INTRODUCTION

The multilevel inverter has gained much attention in recent years due to its advantages in high power with low harmonics applications. The general function of the multilevel inverter is to synthesize a desired high voltage from several levels of dc voltages that can be batteries, fuel cells, etc. In this paper, the proposed hybrid cascaded multilevel inverter includes a standard 3-leg inverter (one leg for each phase) and H-bridge in series with each inverter leg. It can use only a

single DC power source to supply a standard 3-leg inverter along with three full H-bridges Supplied by capacitors traditionally, each H-bridge requires a DC power source [1-5]. Multilevel carrier based PWM method is used to produce a five level phase voltage. The inverter can be used in hybrid electric vehicles (HEV) and electric vehicles (EV). An HEV combines a conventional internal combustion engine, a battery pack, and an electric motor. An EV includes rechargeable batteries and an electric motor. The power inverter that Drives the electric motor is a key device of a HEV and EV. To develop the model of a hybrid multilevel inverter, a simulation is done based on PSIM and MATLAB/SIMULINK platforms. Their integration makes the design and analysis of a hybrid multilevel inverter more complete and detailed [6]. A 5 kW prototype has experimentally validated the proposed PWM hybrid cascaded multilevel inverter.

Multilevel Inverters

In recent years, industry has begun to demand higher power equipment, which now reaches the megawatt level. Controlled ac drives in the megawatt range are usually connected to the medium-voltage network. Today, it is hard to connect a single power semiconductor switch directly to medium voltage grids (2.3, 3.3, 4.16, or 6.9 kV). For these reasons, a new family of multilevel inverters has emerged as the solution for working with higher voltage levels [1][3]. Multilevel inverters include an array of power semiconductors and capacitor voltage sources, the output of which generate voltages with stepped waveforms. The commutation of the switches permits the addition of the capacitor voltages, which reach high voltage at the output, while the power semiconductors must withstand only reduced voltages. Fig. 1 shows a schematic diagram of one phase leg of inverters with different numbers of levels, for which the action of the power semiconductors is represented by an ideal switch with several positions. A two-level inverter generates an output voltage with two values (levels) with respect to the negative terminal of the capacitor [see Fig. 1(a)], while the three-level inverter generates three voltages, and so on. Considering that m is the number of steps of the phase voltage with respect to the negative terminal of the inverter, then the number of steps in the voltage between two phases of the load k is

and the number of steps p in the phase voltage of a three-phase load in wye connection is

The term multilevel starts with the three-level inverter introduced by Nabae et al. [4]. By increasing the number of levels in the inverter, the output voltages have more steps generating a staircase waveform, which has a reduced harmonic distortion. However, a high number of levels increases the control complexity and introduces voltage imbalance problems. Three different topologies have been proposed for multilevel inverters: diode-clamped (neutralclamped) ; capacitor- clamped (flying capacitors) ; and cascaded multi-cell with separate dc sources . In addition, several modulation and control strategies have been developed or adopted for multilevel inverters including the following: multilevel sinusoidal pulse width modulation (PWM), multilevel selective harmonic elimination, and space-vector modulation (SVM).

The most attractive features of multilevel inverters are as follows.

1) They can generate output voltages with extremely low distortion and lower 2) They draw input current with very low distortion. 3) They generate smaller common-mode (CM) voltage, thus reducing the stress in the motor bearings. In addition, using sophisticated modulation methods, CM voltages can be eliminated 4) they can operate with a lower switching frequency.

The results of a patent search show that multilevel inverter circuits have been around for more than 25 years. An early traceable patent appeared in 1975, in which the cascade inverter was first defined with a format that connects separately dc-sourced full-bridge cells in series to synthesize a staircase a output voltage. Through manipulation of the cascade inverter, with diodes blocking the sources, the diode-clamped multilevel Inverter was then derived. The diode-clamped inverter was also called the neutral-point clamped (NPC) inverter When it was first used in a three-level inverter in which the mid-voltage level was defined as the neutral point. Because the NPC inverter effectively doubles the device voltage level without

requiring precise voltage matching, the circuit topology prevailed in the 1980s. The application of the NPC inverter and its extension to multilevel converter was found in. Although the cascade inverter was invented earlier, its applications did not prevail until the mid1990s. Two major patents were filed to indicate the superiority of cascade inverters for motor drive and utility applications. Due to the great demand of medium-voltage high-power inverters, the cascade inverter has drawn tremendous interest ever since. Several patents were found for the use of cascade inverters in regenerative-type motor drive applications. The last entry for U.S. multilevel inverter patents, which were defined as the capacitor-clamped multilevel inverters, came in the 1990s. Today, multilevel inverters are extensively used in highpower applications with medium voltage levels. The field applications include use in laminators, mills, conveyors, pumps, fans, blowers, compressors, and so on. This paper presents state-of-theart multilevel technology, considering well-established and emerging topologies as well as their modulation and control techniques. Special attention is dedicated to the latest and more relevant industrial applications of these converters. Finally, the possibilities for future development are addressed.

INVERTER TOPOLOGIES

A. Diode-Clamped Inverter

A three-level diode-clamped inverter is shown in Fig. 2(a). In this circuit, the dc-bus voltage is split into three levels by two series-connected bulk capacitors, C1 and C2. The middle point of the two capacitors n can be defined as the neutral point. The output voltage Van has three states Vdc/2, 0, -Vdc/2 For voltage leve Vdc/2,switches S1 and S2 need to be turned on; for Vdc/2 switches S1 and S2 need to be switched on and for the 0 level S2 and S1 need to be turn on. The key components that distinguish this circuit from a conventional two-level inverter are D1 and D1. These two diodes clamp the switch voltage to half the level of the dcbus voltage. When both S1 and S2 turn on voltage across a and 0 is Vdc i.e Va0 = Vdc. In this case, D1 balances out

Diode-clamped multilevel inverter circuit topologies (a) three-level (b) Five-level the voltage sharing between S1 and S2 with S1 blocking the voltage across C1 and S2 blocking the voltage across C2. Notice that output voltage Van is ac, and Vao is DC. The difference between Van and Vao is the voltage across C2.which is Vdc/2. If the output is removed out between a and 0, then the circuit becomes a dc/dc converter, which has three output voltage levels: Fig. 2(b) shows a five-level diode-clamped converter in For dc-bus voltage Vdc, the

which the dc bus consists of four capacitors,

voltage across each capacitor is Vdc/4, and each device voltage stress will be limited to one capacitor voltage level Vdc/4 through clamping diodes. To explain how the staircase voltage is synthesized, the neutral point n is considered as the output phase voltage reference point. There are five switch combinations to synthesize five level voltages across a and n.

1) For voltage level 2) For voltage level switch S1

turn on all upper switches S1-S4 turn on three upper switches S2-S4 and one lower

3) For voltage level Van = 0 turn on two upper switches S3 and S4 and two lower switches

4) For voltage level switches S1 and S3 5) For voltage level

turn on one upper switch S4 and three lower turn on all lower switches S1-S4

Four complementary switch pairs exist in each phase. The complementary switch pair is defined such that turning on one of the switches will exclude the other from being turned on. In this example, the four complementary pairs are (S1, S1), (S2, S2), (S3, S3), and (S4, S4). Although each active switching device is only required to block a voltage level of vdc/(m-1), the clamping diodes must have different voltage ratings for reverse voltage blocking. Using D1' of Fig. 2(b) as an example, when lower devices S2' are turned on, D1' needs to block three capacitor voltages, or 3Vdc/4. Similarly, D2 and D2' need to block 2Vdc/4, and Da3 needs to block 3Vdc/4. Assuming that each blocking diode voltage rating is the same as the active device voltage rating, the number of diodes required for each phase will be (m-1)*(m-2). . This number represents a quadratic increase in m. When m is sufficiently high, the number of diodes required will make the system impractical to implement. If the inverter runs under PWM, the diode reverse recovery of these clamping diodes becomes the major design challenge in high-voltage high-power applications.

Capacitor-Clamped Inverter

Fig. 3 illustrates the fundamental building block of a phase-leg capacitor-clamped inverter. The circuit has been called the flying capacitor inverter [1], [5], [6] with independent capacitors clamping the device voltage to one capacitor voltage level. The inverter in Fig. 3(a) provides a three-level output across a and n i.e For voltage level

switches S1 and S2 need to be turned on; for Vdc/2, switches S1 and S2 need to be turned on; and for the 0 level, either pair needs to be turned on. Clamping

capacitor is C1 charged when S1 and S2 are turned on, and is discharged when and are turned on. The charge of C1 can be balanced by proper selection of the 0-level switch combination. The voltage synthesis in a five-level capacitor-clamped converter has more flexibility than a diode-clamped converter. Using Fig. 3(b) as the example, the voltage of the five-level phase-leg a output with respect to the neutral point n, Van, can be synthesized by the following switch combinations.

1) For voltage level 2) For voltage level

turn on all upper switches there are three combinations:

3) For voltage level

there are six combinations:

4) For voltage level

there are three combinations:

5) For voltage level

turn on all lower switches,

In the preceding description, the capacitors with positive signs are in discharging mode, while those with negative sign are in charging mode. By proper selection of capacitor combinations, it is possible to balance the capacitor charge. Similar to diode clamping, the capacitor clamping requires a large number of bulk capacitors to clamp the voltage. Provided that the voltage rating of each capacitor used is the same as that of the main power switch, an level converter will require a total of leg in addition to main dc-bus capacitors. clamping capacitors per phase

C. Cascaded Multi-cell Inverters

A different converter topology is introduced here, which is based on the series connection of single-phase inverters with separate dc sources [7]. Fig. 4 shows the power circuit for one phase leg of a nine-level inverter with four cells in each phase. The resulting phase voltage is synthesized by the addition of the voltages generated by the different cells. Each single-phase full-bridge inverter generates three voltages at the output: +Vdc, 0, and -Vdc. This is made possible by connecting the capacitors sequentially to the ac side via the four power switches. The resulting output ac voltage swings from - 4Vdc to +4Vdc with nine levels and the staircase waveform is nearly sinusoidal, even without filtering.

Another version of cascaded multilevel inverters using standard three-phase twolevel inverters has recently been proposed [8]. Its circuit, shown in Fig. 5, uses an output transformer to add the different voltages. In order for the inverter output voltages to be added up, the inverter outputs of the three modules need to be synchronized with a separation of 120 between each phase. For example, obtaining a three-level voltage between outputs a and b, the voltage is synthesized by the phase between b1 and a2 is

provided by a3 and b3 through an isolated transformer. With three inverters synchronized, the voltages are all in phase; thus, the output level is simply tripled.

D. Generalized Multilevel Cells

A generalized multilevel inverter topology has previously been presented [19]. The existing multilevel inverters such as

Fig. 4 Cascaded inverter circuit topology and its associated waveform

Fig. 5 Cascaded inverter with three-phase cells.

Diode-clamped and capacitor-clamped multilevel inverters can be derived from this generalized inverter topology. Moreover, the generalized multilevel inverter topology can balance each voltage level by itself regardless of load characteristics. Therefore, the generalized multilevel inverter topology provides a true multilevel structure that can balance each dc voltage level automatically at any number of levels, regardless of active or reactive power conversion, and without any assistance from other circuits. Thus, in principle, it provides a complete multilevel topology that embraces the existing multilevel inverters. Fig. 6 shows the P2 multilevel inverter structure per phase leg. Each switching device, diode, or capacitors voltage is 1Vdc, i.e. of

the dc-link voltage. Any inverter with any number of levels, including the conventional two-level inverter can be obtained using this generalized topology. As an application example, a four-level bidirectional dc/dc converter, shown in Fig. 7, is suitable for the dual-voltage system to be adopted in future automobiles. The four-level dc/dc converter has a unique feature, which is that no magnetic components are needed. From this generalized multilevel inverter topology, several new multilevel inverter structures can be derived

Fig. 6 Generalized P2 multilevel inverter structure

Application example: a four-level P2 converter for the dual-voltage system in automobiles.

E. Emerging Multilevel Inverter Topologies

1) Mixed-Level Hybrid Multilevel Cells:

For high-voltage high-power applications, it is possible to adopt multilevel diode-clamped or capacitor-clamped inverters to replace the full-bridge cell in a cascaded inverter. The reason for doing so is to reduce the amount of separate dc sources. The nine-level cascaded inverter shown in Fig. 4 requires four separate dc sources for one phase leg and twelve for a three-phase inverter. If a three-level inverter replaces the full-bridge cell, the voltage level is effectively doubled for each cell. Thus, to achieve the same nine voltage levels for each phase, only two separate dc sources are needed for one phase leg and six for a three-phase inverter. The configuration can be considered as having mixed-level hybrid multilevel cells because it embeds

multilevel cells as the building block of the cascaded inverter. Fig. 8 shows the nine-level cascaded inverter incorporating a three-level capacitor-clamped inverter as the cell. It is obvious that a diode-clamped inverter can replace the capacitor-clamped inverter to be a mixed-level hybrid multilevel cell.

2) Asymmetric Hybrid Multilevel Cells:

In previous descriptions, the voltage levels of the cascade inverter cells equal each other. However, it is possible to have different voltage levels among the cells and the circuit can be called as asymmetric hybrid multilevel inverter. Fig. 9 shows an example of having two separate dc-bus levels, one with , and the other with Vdc/2.

A mixed-level hybrid cell configuration using the thee-level diode-clamped inverter as the cascaded inverter cell to increase the voltage levels

Asymmetric hybrid cascaded inverter cell arrangement with different voltage levels.

Depending on the availability of dc sources, the voltage levels are not limited to a specific ratio. This feature allows more levels to be created in the output voltage, and thus reduces the harmonic contents with less cascaded cells required. Even with the same voltage level among them, it is also possible to use highfrequency PWM for one cell, while the other switches at a lower rate. Fig. 10 shows an example with two different devices. The top full-bridge cell uses the insulated gate bipolar transistor (IGBT), and the low cell uses the gate-turn-off thyristor (GTO) as its switching device. The GTO-based cell switches at a lower frequency, typically the fundamental frequency, and the IGBT-based cell switches at a PWM frequency to smooth the waveform

3) Soft-Switched Multilevel Inverters:

There are numerous ways of implementing soft-switching methods to reduce the switching loss and to increase efficiency for different multilevel inverters. For the cascaded inverter, because each inverter cell is a two-level circuit, the implementation of soft switching is not at all different from that of conventional two-level inverters

Asymmetric cascade inverter cell arrangement with different switching frequencies

Zero-voltage-switching capacitor-clamped inverter circuit

For capacitor- or diode-clamped inverters, however, the choices of soft-switching circuit can be found with different circuit combinations. Although zero-current switching is possible most literatures proposed zero-voltage-switching types including auxiliary resonant commutated pole (ARCP), coupled inductor with zero-voltage transition (ZVT), and their combinations. Fig. 11 shows an example of combining the ARCP and coupled-inductor ZVT techniques for a capacitor-clamped three-level inverter. The auxiliary switches switches S2 and S3 to achieve soft switching. With circuit formed by are used to assist the inner main as the coupled inductor, the bridge-type

and forms a two-level coupled-inductor ZVT. The basic

principle of a two-level ZVT can be found in. For the outer main switches, the soft switching relies on coupled inductor and split-capacitor pair C2 to

form an ARCP type soft-switching inverter. Detailed soft-switching circuit operation for inner devices and outer devices can be found in

III. CONTROL AND MODULATION STRATEGIES

A. Classification of Modulation Strategies

The modulation methods used in multilevel inverters can be classified according to switching frequency, as shown in Fig. 12. Methods that work with high switching frequencies have many commutations for the power semiconductors in one period of the fundamental output voltage.

. Classification of multilevel modulation methods

A very popular method in industrial applications is the classic carrier-based sinusoidal PWM (SPWM) that uses the phase-shifting technique to reduce the harmonics in the load voltage. Another interesting alternative is the SVM strategy, which has been used in three-level inverters. Methods that work with low switching frequencies generally perform one or two commutations of the power semiconductors during one cycle of the output voltages, generating a staircase waveform. Representatives of this family are the multilevel selective harmonic elimination and the space-vector control (SVC).

B. Multilevel SPWM

Several multicarrier techniques have been developed to reduce the distortion in multilevel inverters, based on the classical SPWM with triangular carriers. Some methods use carrier disposition and others use phase shifting of multiple carrier signals. Fig. 13(a) shows the typical voltage generated by one cell for the inverter shown in Fig. 4 by comparing a sinusoidal reference with a triangular carrier signal. A number of NC cascaded cells in one phase with their carriers shifted by an angle and using the same control voltage produce a load

voltage with the smallest distortion. The effect of this carrier phase-shifting technique can be clearly observed in Fig. 14. This result has been obtained for the multi-cell inverter in a sevenlevel configuration, which uses three series-connected cells in each phase. The smallest distortion is obtained when the carriers are shifted by an angle of A very

common practice in industrial applications for the multilevel inverter is the injection of a third harmonic in each cell, as shown in Fig. 13(b), to increase the output voltage. Another advantageous feature of multilevel SPWM is that the effective switching frequency of the load voltage is times the switching frequency of each cell, as determined by its carrier signal. This property allows a reduction in the switching frequency of each cell, thus reducing the switching losses.

II. OPERATION PRINCIPLE OF THE HYBRID MULTILEVEL INVERTER

Fig. 1 Topology of the hybrid cascaded multilevel inverter.

Fig. 2 Simplified single-phase topology of the hybrid cascaded multilevel inverter.

The topology of the proposed hybrid multilevel inverter is shown in Fig. 1. Fig. 2 shows a simplified single-phase topology. The bottom is one leg of a standard 3-leg inverter with a DC power source. The top is an H-bridge in series with each standard inverter leg. The H-bridge can use a separate DC power source or a capacitor as the dc power source

Fig. 3 Capacitor voltage regulation process

The output voltage v1 of this leg (with respect to the ground) is either +Vdc/2 (S5 closed) or Vdc/2 (S6 closed). This leg is connected in series with a full H-bridge that in turn is supplied by a capacitor voltage. If the capacitor is kept charged to Vdc/2, then the output voltage of the H bridge can take on the values +Vdc/2 (S1, S4 closed), 0 (S1, S2 closed or S3, S4 closed), or Vdc/2 (S2, S3 closed). An example output waveform that this topology can achieve is shown in Fig. 3 (a). When the output voltage v = v1 + v2 is required to be zero, one can either set v1 = +Vdc/2 and v2 = Vdc/2 or v1 = Vdc/2 and v2 = +Vdc/2. It is this flexibility in choosing how to make that output voltage zero that is exploited to regulate the capacitor voltage. When only a dc power source is used in the inverter, that is, the H-bridge uses a capacitor as the dc power source, the capacitors voltage regulation control details are illustrated

in Fig. 3. During 1! ! ", the output voltage in Fig. 2 is zero and the current i > 0. If S1, S4 are closed (so that v2 = +Vdc/2) along with S6 closed (so that v1 = Vdc/2), then the capacitor is discharging (ic = i < 0 see Fig. 3 (b)) and v = v1 + v2 = 0. On the other hand, if S2, S3 are closed (so that v2 = Vdc/2) and S5 is also closed (so that v1 = +Vdc/2), then the capacitor is charging (ic = I > 0 see Fig. 3 (c)) and v = v1+v2 = 0. The case i < 0 is accomplished by simply reversing the switch positions of the i > 0 case for charge and discharge of the capacitor. Consequently, the method consists of monitoring the output current and the capacitor voltage so that during periods of zero voltage output, either the switches S1, S4, and S6 are closed or the switches S2, S3, S5 are closed depending on whether it is necessary to charge or discharge the capacitor. As Fig. 3 illustrates, this method of regulating the capacitor voltage depends on the voltage and current not being in phase. That means one needs positive (or negative) current when the voltage is passing through zero in order to charge or discharge the capacitor. Consequently, the amount of capacitor voltage the scheme can regulate depends on the phase angle difference of output voltage and current. It is noted that the above capacitor voltage regulation method is described using a fundamental frequency modulation scheme because it is easier to illustrate [7]. The PWM scheme uses the same method as described in the next section.

III. PSIM AND SIMULINK CO-SIMULATION

The modulation control schemes for the multilevel inverter can be divided into two categories, fundamental switching frequency [1][4][8] and high switching frequency PWM [4][12-16] such as multilevel carrier based PWM, selective harmonic elimination and multilevel space vector PWM. Both PWM and fundamental frequency switching methods can be used for the hybrid multilevel inverter. Multilevel carrier based PWM strategies are the most popular methods because they are easily implemented. Three major carrier-based techniques that are used in a conventional inverter can be applied in a multilevel inverter: sinusoidal PWM (SPWM), third harmonic injection PWM (THPWM), and space vector PWM (SVM). SPWM is a popular method in industrial applications. It uses several triangle carrier signals, one carrier for each level and one reference, or modulation, signal per phase. In the proposed inverter, the top

H-bridge inverter is operated under the SPWM mode and the bottom standard 3-leg inverter is operated under square-wave mode in order to reduce switching loss. For an m-level inverter, the amplitude modulation index, ma, is defined as

Where, Am is the peak-to-peak reference waveform amplitude, Ac is the peak-to-peak carrier waveform amplitude.

In this paper, the simulation model is developed with PSIM and MATALB/SIMULINK. The PSIM model for the power circuit is shown in Fig. 4. Its control functions are completed in MATLAB/SIMULINK. One can therefore make full use of PSIMs capability in power simulation and MATLAB/SIMULINKs capability in control simulation in a complementary way. A key issue to realize the control method is that the capacitors voltages (VC) need to be kept regulated to one half of the DC voltage (Vdc/2). To regulate a capacitors voltage, if i > 0 and Vc < Vdc/2, the inverter controls the bottom inverter to output Vdc/2 and the top H-bridge to output Vdc/2 for inverters 0 voltage output; if i > 0 and Vc > Vdc/2, the inverter controls the bottom inverter to output Vdc/2 and the top H-bridge to output Vdc/2 for inverters 0 voltage output. The i < 0 situation is similar to the i > 0 situation, the controller just needs to reverse its switching signals. The top H-bridge and bottom standard 3-leg inverter output voltage waveform are shown in Fig. 5. Fig. 6 shows the simulation results, which include phase voltage, line-line voltage, and phase current. The output phase voltage is five-level and the output phase current is sinusoidal. Moreover, the PWM scheme makes the inverter output zero voltage for significant time intervals so that the capacitor can be charged or discharged during these periods.

Fig. 5 H-bridge (top) and standard inverter (bottom) output voltage

Fig. 6 Output line-line and phase voltage, phase current of the hybrid cascaded multilevel inverter (ma=0.8).

CONCLUSION

A simulation model for the hybrid multilevel inverter is developed in PSIM and SIMULINK co-simulation platform. The inverter output is a five level phase voltage. The paper presents the main circuit model in PSIM and simulation results in detail. The experiment and FFT analysis results verified the proposed hybrid cascaded multilevel inverter with a PWM control method.

You might also like

- Assistant Engineer Operation Section KrishnagiriDocument3 pagesAssistant Engineer Operation Section KrishnagiriShareef KhanNo ratings yet

- Operation and Maintenance of A Substation-Libre PDFDocument60 pagesOperation and Maintenance of A Substation-Libre PDFShareef KhanNo ratings yet

- Sharif ExpnDocument26 pagesSharif ExpnShareef KhanNo ratings yet

- Control of PV Array Based Distributed GeneratorDocument9 pagesControl of PV Array Based Distributed GeneratorShareef KhanNo ratings yet

- Vtiger Developer Recruitment (Round 1 Test For Freshers) November 22, 2014 From 11:00 AM To 12:30 PMDocument1 pageVtiger Developer Recruitment (Round 1 Test For Freshers) November 22, 2014 From 11:00 AM To 12:30 PMShareef KhanNo ratings yet

- 9.a Modular Fuel Cell, Modular DC DC ConverterDocument62 pages9.a Modular Fuel Cell, Modular DC DC ConverterShareef KhanNo ratings yet

- Modeling and Control of A Cascaded-Multilevel Converter Based StatcomDocument72 pagesModeling and Control of A Cascaded-Multilevel Converter Based StatcomShareef KhanNo ratings yet

- 0resume Tips-1: Getting It RightDocument8 pages0resume Tips-1: Getting It RightShareef KhanNo ratings yet

- 22.design and Implementation of A Shunt Active Power Filter With Reduced DC Link VoltageDocument9 pages22.design and Implementation of A Shunt Active Power Filter With Reduced DC Link VoltageShareef KhanNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Board Label Qty Manufacturer Part NumberDocument6 pagesBoard Label Qty Manufacturer Part NumberestrallatorNo ratings yet

- ES 403 - Portable Electrical Equipment Version 5Document24 pagesES 403 - Portable Electrical Equipment Version 5muhammad nomanNo ratings yet

- Lifetec LCD Monitor TransistorDocument9 pagesLifetec LCD Monitor TransistornegrusrlNo ratings yet

- DatasheetDocument104 pagesDatasheetkishore_bulli6666No ratings yet

- Single PhasingDocument6 pagesSingle PhasingQuek Swee XianNo ratings yet

- 2019 Winter Model Answer Paper (Msbte Study Resources)Document15 pages2019 Winter Model Answer Paper (Msbte Study Resources)Dipesh BaviskarNo ratings yet

- AEG AC Motor AMME 80Z BA2Document14 pagesAEG AC Motor AMME 80Z BA2TonyNo ratings yet

- Condensadores FrakoDocument12 pagesCondensadores FrakoEduard MachadoNo ratings yet

- EE 109 System ProtectionDocument4 pagesEE 109 System ProtectionIan Acuzar PunzalanNo ratings yet

- Daf Lf45 Lf55 Electrical Wiring DiagramDocument20 pagesDaf Lf45 Lf55 Electrical Wiring DiagramRonald98% (55)

- PPT Introduction To Power Electronics (Benny Yeung) PDFDocument32 pagesPPT Introduction To Power Electronics (Benny Yeung) PDFHamza Mustafa100% (1)

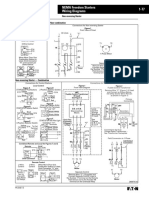

- Cuttler Hammer Wiring-DiagramsDocument9 pagesCuttler Hammer Wiring-DiagramsReggieNo ratings yet

- AON7410 30V N-Channel MOSFET: Features General DescriptionDocument6 pagesAON7410 30V N-Channel MOSFET: Features General Descriptiondreyes3773No ratings yet

- 31 TMSS 01 Rev01 PDFDocument29 pages31 TMSS 01 Rev01 PDFFazleMasoodNo ratings yet

- Cutler Hammer Spec SheetDocument30 pagesCutler Hammer Spec SheetAlcibiades MaytaNo ratings yet

- TCS Using Micom RelaysDocument26 pagesTCS Using Micom RelaysLê Văn PhúNo ratings yet

- 78DXXL: Unisonic Technologies Co., LTDDocument8 pages78DXXL: Unisonic Technologies Co., LTDSlava VanatNo ratings yet

- Chapter 3 GENERATION OF HIGH VOLTAGEDocument39 pagesChapter 3 GENERATION OF HIGH VOLTAGEHalifa AhmadNo ratings yet

- SM7352PC: Ÿ Constant Current Accuracy Is Less Than 5%Document8 pagesSM7352PC: Ÿ Constant Current Accuracy Is Less Than 5%Diogo RaulNo ratings yet

- 33 KV Amararaja Pmums - 122 - 15-16 - ManualDocument43 pages33 KV Amararaja Pmums - 122 - 15-16 - ManualVeera ChaitanyaNo ratings yet

- Usol 160Document2 pagesUsol 160Victor RosuNo ratings yet

- Insulation Resistance Test PDFDocument2 pagesInsulation Resistance Test PDFusman haroonNo ratings yet

- 3RT60251BB40 Datasheet enDocument6 pages3RT60251BB40 Datasheet enSanjaya FernandoNo ratings yet

- Triplexed Conductors in Air: Ampacity TablesDocument2 pagesTriplexed Conductors in Air: Ampacity TablesalbertoNo ratings yet

- Lesson 1 (Basic Principles of Protective Relays and Circuit Breaker Operations)Document11 pagesLesson 1 (Basic Principles of Protective Relays and Circuit Breaker Operations)kelotvNo ratings yet

- AOZ3013PI: General Description FeaturesDocument14 pagesAOZ3013PI: General Description FeaturesJohn KleinNo ratings yet

- Compact Fluorecent LampDocument11 pagesCompact Fluorecent LampKathleen Jhoren ReglosNo ratings yet

- Machine Lab Printable CompletedDocument97 pagesMachine Lab Printable Completedjinto007No ratings yet

- Afcons: Electrical Safety Inspection Checklist Re-Construction of North Jetty at Naval Base, Kochi On Epc Contract BasisDocument3 pagesAfcons: Electrical Safety Inspection Checklist Re-Construction of North Jetty at Naval Base, Kochi On Epc Contract Basisprabu lingamNo ratings yet

- Harris Cathode-Follower (Source-Follower) OscillatorsDocument2 pagesHarris Cathode-Follower (Source-Follower) OscillatorsJhorman Y'susNo ratings yet