Professional Documents

Culture Documents

Datasheet DS1216 DALLAS

Uploaded by

RICHIHOTS2Original Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Datasheet DS1216 DALLAS

Uploaded by

RICHIHOTS2Copyright:

Available Formats

DS1216

SmartWatch RAM DS1216B/C/D/H SmartWatch ROM DS1216E/F

www.maxim-ic.com

FEATURES

Keeps track of hundredths of seconds, seconds, minutes, hours, days, date of the month, months, and years Converts standard 2k x 8 up to 512k x 8 CMOS static RAMs into nonvolatile memory Embedded lithium energy cell maintains watch information and retains RAM data Watch function is transparent to RAM operation Month and year determine the number of days in each month; leap-year compensation valid up to 2100 Lithium energy source is electrically disconnected to retain freshness until power is applied for the first time Proven gas-tight socket contacts Full 10% operating range Operating temperature range: 0C to +70C Accuracy is better than 1 minute/month @ +25C

ORDERING INFORMATION

DS1216B, DS1216C, DS1216D, DS1216E, DS1216F, DS1216H (See Figure 2 for letter suffix

marking identification.)

RST 1 2 3 4 5 6 7 [A2] 8 9 [A0] 10 DQ0 11 12 13 GND 14 28 VCC 27 WE 26 VCCB 25 24 23 22 21 20 19 18 17 16 15 CE OE

PIN DESCRIPTION

RST

DQ0 A2 A0 GND

CE OE WE

Vcc VCCB VCCD

- RESET - Data Input/Output 0 [RAM] - Address Bit 2 (Read/Write [ROM]) - Address Bit 0 (Data Input [ROM]) - Ground - Conditioned Chip Enable - Output Enable - Write Enable - Switched VCC for 28-/32-Pin RAM - Switched VCC for 24-Pin RAM - Switched VCC for 28-Ppin RAM RAM/ROM RAM RAM RAM ROM ROM RAM RAM DENSITY 16k/64k 64k/256k 256k/1M 64k/256k 64k/256k/1M 1M/4M

1 of 13

DS1216B/C/D/E 28-Pin Intelligent Socket

PART DS1216B DS1216C DS1216D DS1216E DS1216F DS1216H

PCB MODIFICATION REQUIRED FOR DENSITY UPGRADE? No/Yes No No/Yes No No No

111901

DS1216

TYPICAL OPERATING CIRCUIT

RST 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 VCC

WE

[A2] [A0] DQ0

OE CE

GND

DS1216D/E/F/H 32-Pin Intelligent Socket

DESCRIPTION

The DS1216 SmartWatch RAM and SmartWatch ROM Sockets are 600mil-wide DIP sockets with a built-in CMOS watch function, an NV RAM controller circuit, and an embedded lithium energy source. The sockets provide an NV RAM solution for memory sized from 2k x 8 to 512k x 8 with package sizes from 26 pins to 32 pins. When a socket is mated with a CMOS SRAM, it provides a complete solution to problems associated with memory volatility and uses a common energy source to maintain time and date. The SmartWatch ROM sockets use the embedded lithium source to maintain the time and date only. A key feature of the SmartWatch is that the watch function remains transparent to the RAM. The SmartWatch monitors VCC for an out-of-tolerance condition. When such a condition occurs, an internal lithium energy source is automatically switched on and write protection is unconditionally enabled to prevent loss of watch and RAM data. Using the SmartWatch saves PC board space since the combination of SmartWatch and the mated RAM take up no more area than the memory alone. The SmartWatch uses the VCC, data I/O 0, CE , OE , and WE for RAM and watch control. All other pins are passed straight through to the socket receptacle. The SmartWatch provides timekeeping information including hundredths of seconds, seconds, minutes, hours, days, date, months, and years. The date at the end of the month is automatically adjusted for months with fewer than 31 days, including correction for leap years. The SmartWatch operates in either 24-hour or 12-hour format with an AM/PM indicator.

OPERATION

Communication with the SmartWatch RAM is established by pattern recognition on a serial bit stream of 64 bits that must be matched by executing 64 consecutive write cycles containing the proper data on DQ0. On the SmartWatch ROM, communication with the clock is established using A2 and A0, and either OE or CE. All accesses that occur prior to recognition of the 64-bit pattern are directed to memory.

2 of 13

DS1216

After the pattern match, the next 64 reads and/or writes are directed to the clock, and the RAM is disabled. Once the pattern is established, the next 64 read/write cycles will be directed to the RTC registers. When power is cycled, 64 reads should be executed prior to any writes to ensure that the RTC registers are not written. A pattern match is ignored if the RST bit is zero and the RST pin goes low during the match sequence. A pattern match is also terminated if a read occurs during the 64-bit match sequence.

PATTERN MATCHRAM

Data transfer to and from the timekeeping registers is accomplished with a serial bit stream under control of chip enable ( CE ), output enable ( OE ), and write enable ( WE ). Initially, a read cycle to any memory location using the CE and OE control of the SmartWatch starts the pattern recognition sequence by moving a pointer to the first bit of the 64-bit comparison register. Next, 64 consecutive write cycles are executed using the CE and WE control of the SmartWatch. These 64 write cycles are used only to gain access to the SmartWatch. Therefore, any address to the memory in the socket is acceptable. However, the write cycles generated to gain access to the SmartWatch are also writing data to a location in the mated RAM. The preferred way to manage this requirement is to set aside just one address location in RAM as a SmartWatch scratch pad. When the first write cycle is executed, it is compared to bit 0 of the 64-bit comparison register. If a match is found, the pointer increments to the next location of the comparison register and awaits the next write cycle. If a match is not found, the pointer does not advance and all subsequent write cycles are ignored. If a read cycle occurs at any time during pattern recognition, the present sequence is aborted and the comparison register pointer is reset. Pattern recognition continues for 64 write cycles as described above until all the bits in the comparison register have been matched (this bit pattern is shown in Figure 1). With a correct match for 64 bits, the SmartWatch is enabled and data transfer to or from the timekeeping registers can proceed. The next 64 cycles will cause the SmartWatch to either receive or transmit data on DQ0, depending on the level of the OE pin or the WE pin. Cycles to other locations outside the memory block can be interleaved with CE cycles without interrupting the pattern recognition sequence or data transfer sequence to the SmartWatch.

PATTERN MATCHROM

Communication with the SmartWatch is established by pattern recognition of a serial bit stream of 64 bits that must be matched by executing 64 consecutive write cycles, placing address bit A2 low with the proper data on address bit A0. The 64 write cycles are used only to gain access to the SmartWatch. Prior to executing the first of 64 write cycles, a read cycle should be executed by holding A2 high. The read cycle will reset the comparison register pointer within the SmartWatch, ensuring the pattern recognition starts with the first bit of the sequence. When the first write cycle is executed, it is compared to bit 0 of the 64-bit comparison register. If a match is found, the pointer increments to the next location of the comparison register and awaits the next write cycle. If a match is not found, the pointer does not advance and all subsequent write cycles are ignored. If a read cycle occurs at any time during pattern recognition, the present sequence is aborted and the comparison register pointer is reset. Pattern recognition continues for a total of 64 write cycles as described above, until all the bits in the comparison register have been matched (this bit pattern is shown in Figure 1). With a correct match for 64 bits, the SmartWatch is enabled and data transfer to or from the timekeeping registers can proceed. The next 64 cycles will cause the SmartWatch to either receive data on data in (A0) or transmit data on data out (DQ0), depending on the level of /WRITE READ (A2).

3 of 13

DS1216

SMARTWATCH COMPARISON REGISTER DEFINITION Figure 1

7 1 0 1 0 1 0 1 0 0 1 0 1 0 1 0 1 0

HEX VALUE C5 3A A3 5C C5 3A A3 5C

BYTE 0 BYTE 1 BYTE 2 BYTE 3 BYTE 4 BYTE 5 BYTE 6 BYTE 7

1 0 0 1 1 0 0 1

0 1 1 0 0 1 1 0

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

1 0 0 1 1 0 0 1

0 1 1 0 0 1 1 0

Note: The pattern recognition in Hex is C5, 3A, 5C, C5, 3A, A3, 5C. The odds of this pattern accidentally duplicating and causing inadvertent entry to the SmartWatch are less than 1 in 1019. This pattern is sent to the SmartWatch LSB to MSB. After power-up, the controller could be in the 64-bit clock register read/write sequence (from an incomplete access prior to power-down). Therefore, it is recommended that a 64-bit read be performed upon power-up to prevent accidental writes to the clock, and to prevent reading clock data when access to the RAM would otherwise be expected.

NONVOLATILE CONTROLLER OPERATION

The DS1216 SmartWatch performs circuit functions required to make a CMOS RAM nonvolatile. First, a switch is provided to direct power from the battery or VCC supply, depending on which voltage is greater. This switch has a voltage drop of less than 0.2V. The second function that the SmartWatch provides is power-fail detection, which occurs at VTP. The DS1216 constantly monitors the VCC supply. When VCC goes out of tolerance, a comparator outputs a power-fail signal to the chip-enable logic. The third function accomplishes write protection by holding the chip-enable signal to the memory within 0.2V of VCC or battery. During nominal power-supply conditions, the memory chip-enable signal will track the chipenable signal sent to the socket with a maximum propagation delay of 7ns for the 5V and 12ns for the 3.3V version.

FRESHNESS SEAL

Each DS1216 is shipped from Dallas Semiconductor with its lithium energy source disconnected, ensuring full energy capacity. When VCC is first applied at a level greater than the lithium energy source is enabled for battery-backup operation.

4 of 13

DS1216

SMARTWATCH REGISTER INFORMATION

The SmartWatch information is contained in eight registers of 8 bits, each of which is sequentially accessed one bit at a time after the 64-bit pattern recognition sequence has been completed. When updating the SmartWatch registers, each must be handled in groups of 8 bits. Writing and reading individual bits within a register could produce erroneous results. These read/write registers are defined in Figure 3. Data contained in the SmartWatch registers is in binary-coded decimal format (BCD). Reading and writing the registers is always accomplished by stepping through all eight registers, starting with bit 0 of register 0 and ending with bit 7 of register 7.

AMPM/12/24 MODE

Bit 7 of the hours register is defined as the 12-hour or 24-hour mode-select bit. When high, the 12-hour mode is selected. In the 12-hour mode, bit 5 is the AM/PM bit with logic high being PM. In the 24-hour mode, bit 5 is the second 10-hour bit (2023 hours).

OSCILLATOR AND RESET BITS

Bits 4 and 5 of the day register are used to control the RESET and oscillator functions. Bit 4 controls the RESET (pin 1). When the RESET bit is set to logic 1, the RESET input pin is ignored. When the RESET bit is set to logic 0, a low input on the RESET pin will cause the SmartWatch to abort data transfer without changing data in the watch registers. Bit 5 controls the oscillator. When set to logic 1, the oscillator is off. When set to logic 0, the oscillator turns on and the watch becomes operational. These bits are shipped from the factory set to logic 1.

ZERO BITS

Registers 1, 2, 3, 4, 5, and 6 contain one or more bits that will always read logic 0. When writing these locations, either a logic 1 or 0 is acceptable.

ADDITIONAL INFORMATION

Refer to Application Note 52 for information about using regarding optional modifications and the phantom clock contained within the SmartWatch.

5 of 13

DS1216

RESET AND MEMORY DENSITY OPTIONS Figure 2

The letter suffix of the SmartWatch is located on the PCB as shown above. The RESET pin on the controller has an internal pullup resistor. To disable the RESET function, the trace between pin 1 on the socket and pin 13 on the controller can be cut. In this case, the socket will ignore the RESET input, preventing address transitions from resetting the pattern match, even if the RST bit is enabled. On the DS1216B and DS1216D, the two VCC pins are connected together on the PCB. The switched VCC from the controller is connected to the two VCC pins that connect to the inserted RAM. No modifications are required if the lower density RAM is used. To use the higher density RAM, the trace by the lower density RAM VCC pin, identified by a hash mark labeled U, must be cut. The two square-metal pads, labeled G, must be shorted together. This disconnects switched VCC from the pin going to the inserted RAM, and connects it to the corresponding address input pin for the higher density RAM.

6 of 13

DS1216

SMARTWATCH REGISTER DEFINITION Figure 3

REGISTER 0 7 1 7 2 7 3 7 4 7 5 7 6 7 7 10 YEAR YEAR 0 0 0 10 MONTH MONTH 0 00-99 0 0 10 DATE DATE 0 01-12 0 0 OSC RST 0 DAY 0 01-31 12/24 0 10 A/P HR HOUR 0 01-07 00-23 0 10 MIN MINUTES 0 01-12 0 10 SEC SECONDS 0 00-59 7 0.1 SEC 0.01 SEC 0 00-59 0 RANGE (BCD) 00-99

7 of 13

DS1216

ABSOLUTE MAXIMUM RATINGS*

Voltage Range on any Pin Relative to Ground Operating Temperature Range Storage Temperature Range Soldering Temperature Range -0.3V to +7.0V for 5V 0C to +70C -40C to +70C See J-STD-020A Specification (Note 6)

* This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time can affect reliability.

RECOMMENDED DC OPERATING CONDITIONS

PARAMETER VCC Pin 5V Supply Logic 1 Logic 0 SYMBOL VCC VIH VIL MIN 4.5 2.2 -0.3 TYP 5.0 MAX 5.5 VCC + 0.3 +0.8

(0C to +70C)

UNITS V V V NOTES 1 8 8

DC ELECTRICAL CHARACTERISTICS

PARAMETER VCC Supply VCC Supply Voltage (ICCO = 80mA) Input Leakage Output Logic 1 Voltage (IOUT = -1.0mA) Output Logic 1 Voltage (IOUT = -1.0mA) Write Protection Voltage SYMBOL ICCI VCCO1(U) IIL VOH VOL VTP 4.25 VCC - 0.2 -1.0 2.4 MIN

(0C to +70C; VCC = 5.0 10%)

TYP MAX 5 UNITS mA V +1.0 mA V 0.4 4.5 V V NOTES 1, 2,3 1, 6 2,8,13

BACKUP POWER CHARACTERISTICS

PARAMETER SYMBOL MIN TYP

(0C to +70C; VCC < VTP)

MAX UNITS NOTES

CE Output VCC Supply Voltage (ICCO = 10A) RAM VCC (Battery) Voltage Recovery at Power-Up VCC Slew Rate fall CE Pulse Width

VOH(L) VCCO2(U) VBAT tREC tF tCE

VBAT - 0.2 VBAT - 0.2 2 0 1.5 3 3.6 2

V V V ms

ms ms

1 1, 6,14 1,15

8 of 13

DS1216

CAPACITANCE

PARAMETER SYMBOL MIN TYP MAX

(TA = +25C)

UNITS NOTES

Input Capacitance Output Capacitance

CIN COUT

5 7

pF pF

(TA = +25C)

PARAMETER SYMBOL MIN TYP MAX UNITS NOTES

Expected Data Retention

tDR

10

Years

14

AC ELECTRICAL CHARACTERISTICS

PARAMETER SYMBOL MIN

(0C to 70C; VCC = 4.5 to 5.5V)

TYPE MAX UNITS NOTES

Read Cycle Time CE Access Time OE Access Time CE to Output Low-Z OE to Output Low-Z CE to Output High-Z OE to Output High-Z Address Setup Time (ROM) Address Hold Time (ROM) Read Recovery Write Cycle Time Write Pulse Width Write Recovery Data Setup Time Data Hold Time CE Pulse Width RESET Pulse Width CE Propagation Delay CE High to Power-Fail

tRC tCO tOE tCOE tOEE tOD tODO tAS tAH tRR tWC tWP tWR tDS tDH tCW tRST tPD tPF

75 65 65 6 6 30 30 20 10 15 75 75 15 35 0 65 75 6 0

9 of 13

ns ns ns ns ns ns ns 11 12 ns ns ns ns ns ns ns ns ns ns 7 9 10 10

DS1216

TIMING DIAGRAM: READ CYCLE TO SMARTWATCH

TIMING DIAGRAM: WRITE CYCLE TO SMARTWATCH

TIMING DIAGRAM: RESET FOR SMARTWATCH

10 of 13

DS1216

TIMING DIAGRAM: POWER-DOWN

TIMING DIAGRAM: POWER-UP

Warning: Under no circumstances should negative undershoots of any amplitude be allowed when the device is in battery-backup mode. Water washing for flux removal will discharge internal lithium source because exposed voltage pins are present.

11 of 13

DS1216

NOTES:

1) Pin locations are designated U when a parameter definition refers to the socket receptacle and L when a parameter definition refers to the socket pin. 2) No memory inserted in the socket. 3) Pin 26L can be connected to VCC or left disconnected at the PC board. 4) SmartWatch sockets can be successfully processed through some conventional wave-soldering techniques as long as temperature exposure to the lithium energy source contained within does not exceed +85C. However, post-solder cleaning with water washing techniques is not permissible. Discharge to the lithium energy source can result, even if deionized water is utilized. It is equally imperative that ultrasonic vibration is not used in order to avert damage to the quartz crystal resonator employed by the oscillator circuit. 5) tCE max must be met to ensure data integrity on power loss. 6) VCCO1 is the maximum voltage drop from Vcc(L) to Vcc(U) while power is being supplied by Vcc(L). VCCO2 is the maximum voltage drop from VBAT to VCC(U) while the part is in battery backup. 7) Input pulse rise and fall times equal 10ns. 8) Applies to pins RST L, A2 L, A0 L, CE L, OE L, and WE L. 9) tWR is a functions of the latter occurring edge of WE or CE . 10) tDH and tDS are a function of the first occurring edge of WE or CE . 11) Tas is a function of the first occurring edge of OE or CE. 12) Tah is a function of the latter occurring edge of OE or CE 13) RST (Pin 1) has an internal pullup resistor. 14) Expected data retention is based on using an external SRAM with a data retention current of less than 0.5A at +25C. Expected data retention time (time while on battery) for a given RAM battery current can be calculated using the following formula: 0.045 / (current in amps) = data retention time in hours 15) The DS1216 products are shipped with the battery-backup power off. First power-up switches backup battery on to clock and RAM VCC pin upon power down.

12 of 13

DS1216

DS1216 28 SMARTWATCH

PKG DIM A IN. MM B IN. MM C IN. MM D IN. MM E IN. MM F IN. MM G IN. MM H IN. MM J IN. MM K IN. MM L IN. MM 28-PIN 32-PIN MIN MAX MIN MAX 1.390 1.420 1.580 1.620 35.31 36.07 40.13 41.14 0.690 0.720 0.690 0.720 17.53 18.29 17.53 18.29 0.420 0.470 0.400 0.470 10.67 11.94 10.16 11.94 0.035 0.065 0.035 0.065 0.89 1.65 0.89 1.65 0.055 0.075 0.055 0.075 1.39 1.90 1.39 1.90 0.120 0.160 0.120 0.160 3.04 4.06 3.04 4.06 0.090 0.110 0.090 0.110 2.29 2.79 2.29 2.79 0.590 0.630 0.590 0.630 14.99 16.00 14.99 16.00 0.008 0.012 0.008 0.012 0.20 0.30 0.20 0.30 0.015 0.021 0.015 0.021 0.38 0.53 0.38 0.53 0.380 0.420 0.380 0.420 9.65 10.67 9.65 10.67

13 of 13

You might also like

- Application Note 504: Design Considerations For Dallas Real-Time ClocksDocument8 pagesApplication Note 504: Design Considerations For Dallas Real-Time ClocksAyadNo ratings yet

- DS1243YDocument13 pagesDS1243YJose HernandezNo ratings yet

- DS1302 Real-Time Clock Chip with 31-Byte RAMDocument16 pagesDS1302 Real-Time Clock Chip with 31-Byte RAMJuan Isaac Rodriquez MaldonadoNo ratings yet

- DS1603Document8 pagesDS1603jnax101No ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- 24C64 BMDocument10 pages24C64 BMdonghungstbNo ratings yet

- 24LC02 A2 PDFDocument11 pages24LC02 A2 PDFJavier Thus GavilanNo ratings yet

- MT 48lc2m32b2 - 64mb x32 SdramDocument53 pagesMT 48lc2m32b2 - 64mb x32 SdramJannik SvenssonNo ratings yet

- Micro Controller Based Digital Clock With CalendarDocument8 pagesMicro Controller Based Digital Clock With CalendarPratyay Dhar33% (3)

- Practical Design of Digital Circuits: Basic Logic to MicroprocessorsFrom EverandPractical Design of Digital Circuits: Basic Logic to MicroprocessorsRating: 4.5 out of 5 stars4.5/5 (2)

- Welcome To International Journal of Engineering Research and Development (IJERD)Document6 pagesWelcome To International Journal of Engineering Research and Development (IJERD)IJERDNo ratings yet

- DS1302 Trickle-Charge Timekeeping ChipDocument13 pagesDS1302 Trickle-Charge Timekeeping ChipPravin MevadaNo ratings yet

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemFrom EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemNo ratings yet

- LLLDocument1 pageLLLmuhammadharisjamal2405No ratings yet

- DS1307 64 X 8 Serial Real-Time Clock: Features Pin AssignmentDocument12 pagesDS1307 64 X 8 Serial Real-Time Clock: Features Pin AssignmentTruck Bus ElectronicaNo ratings yet

- Summery:: Microcontroller AT89C51 Interfacing Serial EEPROM With 8051 LCDDocument3 pagesSummery:: Microcontroller AT89C51 Interfacing Serial EEPROM With 8051 LCDSurdeep ChaudharyNo ratings yet

- Using The MSSP Module To Interface I2CDocument16 pagesUsing The MSSP Module To Interface I2Csoft4gsmNo ratings yet

- PCF8583Document37 pagesPCF8583lady_iuNo ratings yet

- ECR MachineDocument37 pagesECR Machineapi-3721578100% (1)

- 24C02 24C04 24C08 24C16: Bookly MicroDocument10 pages24C02 24C04 24C08 24C16: Bookly MicroHùng Nguyễn VănNo ratings yet

- Circuit DiagramDocument10 pagesCircuit DiagramM Rameez Ur Rehman100% (1)

- AVR242: 8-Bit Microcontroller Multiplexing LED Drive and A 4 X 4 KeypadDocument26 pagesAVR242: 8-Bit Microcontroller Multiplexing LED Drive and A 4 X 4 KeypadDemeter Robert Es IzabellaNo ratings yet

- 2.1 LPC2129 Microcontroller: 2.1.1 FeaturesDocument14 pages2.1 LPC2129 Microcontroller: 2.1.1 FeaturesBhaskar Rao PNo ratings yet

- Micro Controller Based School TimerDocument5 pagesMicro Controller Based School Timera_kureelNo ratings yet

- Eeproms 24CXXDocument18 pagesEeproms 24CXXAlberto YepezNo ratings yet

- 64K 5.0V I C Smart Serial Eeprom: FeaturesDocument16 pages64K 5.0V I C Smart Serial Eeprom: FeaturesFerner BriceñoNo ratings yet

- Automatic College Bell REPORTDocument34 pagesAutomatic College Bell REPORTNagraj Tondchore50% (2)

- Training ReportDocument18 pagesTraining Reportpiyushji125No ratings yet

- Contactless Tachometer With Motor Speed ControlDocument30 pagesContactless Tachometer With Motor Speed Control27051977No ratings yet

- What Is A Digital Alarm Clock: LCD DisplayDocument7 pagesWhat Is A Digital Alarm Clock: LCD DisplayNarenthra BaalaNo ratings yet

- DS1307Document13 pagesDS1307Ezaú TalamantesNo ratings yet

- 64K (8Kx8) Parallel EEPROM With Page Write and Software Data Protection AT28C64BDocument21 pages64K (8Kx8) Parallel EEPROM With Page Write and Software Data Protection AT28C64BRoberto Kaled Silva ValdiviaNo ratings yet

- MEMORY SYSTEM OVERVIEWDocument68 pagesMEMORY SYSTEM OVERVIEWshiva100% (1)

- 256K SPI Bus Low-Power Serial SRAM: Device Selection TableDocument24 pages256K SPI Bus Low-Power Serial SRAM: Device Selection TableMarcinCholewaNo ratings yet

- Agribot Project PresentationDocument21 pagesAgribot Project Presentationumaiya1990100% (1)

- 2023 SDocument20 pages2023 SJames Smith ValderramaNo ratings yet

- Remote Digital ClockDocument79 pagesRemote Digital ClockArdhika Dhennis Putra AnandaNo ratings yet

- AT28HC64BDocument12 pagesAT28HC64BHamzah AlbrakaniNo ratings yet

- Real Time Clock: Features Pin AssignmentDocument17 pagesReal Time Clock: Features Pin AssignmentVu ThinhNo ratings yet

- Coin Based Mobile Charger Project ReportDocument49 pagesCoin Based Mobile Charger Project ReportAnonymous dyJj42aWMb92% (13)

- 24lc02 Application NoteDocument14 pages24lc02 Application NotePrashant GuptaNo ratings yet

- 09 - I2C Serial CommunicationsmDocument10 pages09 - I2C Serial CommunicationsmSorabh DungNo ratings yet

- CLG BellDocument24 pagesCLG BellNikhil Kumar SinghNo ratings yet

- Using The MSSP Module To Interface Spi™ Serial Eeproms With Pic18 DevicesDocument12 pagesUsing The MSSP Module To Interface Spi™ Serial Eeproms With Pic18 Deviceskraneak100% (3)

- Modernizing Track Occupancy Detection with MSDACDocument21 pagesModernizing Track Occupancy Detection with MSDACranvirsahiNo ratings yet

- DS1286 Watchdog Timekeeper: Features Pin AssignmentDocument13 pagesDS1286 Watchdog Timekeeper: Features Pin Assignmentjose goncalvesNo ratings yet

- 24AA254 Memory I2C With The XC8 C Compiler - AN1488ADocument24 pages24AA254 Memory I2C With The XC8 C Compiler - AN1488Aalexandre.oneill2479No ratings yet

- L24C32Document14 pagesL24C32mpapamicNo ratings yet

- Lab MC P1 1618200Document17 pagesLab MC P1 1618200luis gonzalezNo ratings yet

- 8085 MicroprocessorDocument38 pages8085 MicroprocessorPrateek PandeyNo ratings yet

- Irf640N/Irf640Ns/Irf640Nl: N-Channel Power Mosfets 200V, 18A, 0.15Document11 pagesIrf640N/Irf640Ns/Irf640Nl: N-Channel Power Mosfets 200V, 18A, 0.15RICHIHOTS2No ratings yet

- IRFP150Document8 pagesIRFP150RICHIHOTS2No ratings yet

- Alta FrecuenciaDocument3 pagesAlta FrecuenciaRICHIHOTS2No ratings yet

- Electronic Stethoscope-2 by Audioguru: Parts List: Total Qty. DescriptionDocument1 pageElectronic Stethoscope-2 by Audioguru: Parts List: Total Qty. Descriptionlabbams4uNo ratings yet

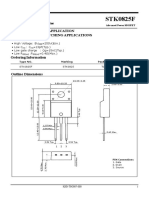

- STK0825F: DC-DC Converter Application High Voltage Switching Applications FeaturesDocument8 pagesSTK0825F: DC-DC Converter Application High Voltage Switching Applications FeaturesRICHIHOTS2No ratings yet

- Physiological StimulatorDocument20 pagesPhysiological StimulatorRICHIHOTS2No ratings yet

- STK086Document1 pageSTK086RICHIHOTS2No ratings yet

- IRF830A: Smps MosfetDocument8 pagesIRF830A: Smps MosfetRICHIHOTS2No ratings yet

- Irfp 450 RDocument8 pagesIrfp 450 Rpisy74No ratings yet

- Flyback TransformersDocument17 pagesFlyback TransformersRICHIHOTS2No ratings yet

- Mindstorms™ Heart Rate Monitor: Thanks To For The Photograph and Schematic (Updated By)Document5 pagesMindstorms™ Heart Rate Monitor: Thanks To For The Photograph and Schematic (Updated By)RICHIHOTS2No ratings yet

- Alta FrecuenciaDocument3 pagesAlta FrecuenciaRICHIHOTS2100% (1)

- Stim MuscularDocument4 pagesStim MuscularRICHIHOTS2No ratings yet

- High Voltage GenerationDocument6 pagesHigh Voltage Generationdp500100% (1)

- MIR Spirolab II - Service ManualDocument33 pagesMIR Spirolab II - Service ManualAugusto VieiraNo ratings yet

- Ferroresonance technical guideDocument30 pagesFerroresonance technical guideKrishna Venkataraman100% (2)

- Electronic Stethoscope-2 by Audioguru: Parts List: Total Qty. DescriptionDocument1 pageElectronic Stethoscope-2 by Audioguru: Parts List: Total Qty. Descriptionlabbams4uNo ratings yet

- Multiplier Design GuidelineDocument15 pagesMultiplier Design GuidelinedewiNo ratings yet

- Estimulador Electrico TranscutaneoDocument11 pagesEstimulador Electrico TranscutaneoRICHIHOTS2No ratings yet

- High-performance offline controller delivers lowest total cost solution in compact packagesDocument9 pagesHigh-performance offline controller delivers lowest total cost solution in compact packagesRICHIHOTS2No ratings yet

- Technical Guide: Microwave Ovens With InvertersDocument46 pagesTechnical Guide: Microwave Ovens With InvertersKybernetikum100% (1)

- Supresor de PicosDocument13 pagesSupresor de PicosRICHIHOTS2No ratings yet

- Ne-1022f SMDocument21 pagesNe-1022f SMRICHIHOTS2No ratings yet

- Fast Track Troubleshooting: Model: SMH1611 /XAADocument4 pagesFast Track Troubleshooting: Model: SMH1611 /XAARICHIHOTS2No ratings yet

- 43896Document28 pages43896RICHIHOTS2No ratings yet

- Tru Trac User ManualDocument41 pagesTru Trac User ManualRICHIHOTS2No ratings yet

- Switching Regulator BasicsDocument33 pagesSwitching Regulator BasicsUtpal100% (11)

- What Is A Constant Voltage TransformerDocument12 pagesWhat Is A Constant Voltage TransformerRICHIHOTS2No ratings yet

- Quasi-Resonant Topology Primary Switching Regulators: STR-W6765Document15 pagesQuasi-Resonant Topology Primary Switching Regulators: STR-W6765c434923No ratings yet

- CanbusDocument28 pagesCanbusZiad AlfawadlehNo ratings yet

- Common Computer AbbreviationsDocument6 pagesCommon Computer AbbreviationsJedediah PhiriNo ratings yet

- BBA-104 Unit-1 Fundamentals-of-Computers NotesDocument24 pagesBBA-104 Unit-1 Fundamentals-of-Computers NotesCoin Seller PrashantNo ratings yet

- Polytechnic University of The Philippines Lopez Quezon, BranchDocument17 pagesPolytechnic University of The Philippines Lopez Quezon, BranchPatrick Luis CantaraNo ratings yet

- Lesson 7: Multimedia & Ict: Molino 3, Bacoor, CaviteDocument3 pagesLesson 7: Multimedia & Ict: Molino 3, Bacoor, CaviteRaymond CanelaNo ratings yet

- Tugas B.Inggris 2Document37 pagesTugas B.Inggris 2bxcoolNo ratings yet

- Manual de Actualizacion de Firmware 452-3511 Download Toshiba EDocument6 pagesManual de Actualizacion de Firmware 452-3511 Download Toshiba Eherico201450% (2)

- OKI ML590 Service ManualDocument221 pagesOKI ML590 Service ManualRemigiuszNo ratings yet

- HANDY-ROM User's ManualDocument9 pagesHANDY-ROM User's ManualyokohamavlNo ratings yet

- Hex Lesson 1Document4 pagesHex Lesson 1samNo ratings yet

- Iees 103Document52 pagesIees 103amulya roulNo ratings yet

- GX Work 2Document9 pagesGX Work 2Hanafi HariyantoNo ratings yet

- Assignment 1 Computer SystemDocument6 pagesAssignment 1 Computer Systemmelissarich811No ratings yet

- Microprocessor Controlled Digital LockDocument53 pagesMicroprocessor Controlled Digital LockHayu BayisaNo ratings yet

- Uploading HP41 Plug in ModulesDocument13 pagesUploading HP41 Plug in ModulesluisproveNo ratings yet

- Cyiv 51003Document18 pagesCyiv 51003flo72afNo ratings yet

- Vizio P50HDMDocument131 pagesVizio P50HDMJuan Perez PerezNo ratings yet

- Sw1 Living in It EraDocument7 pagesSw1 Living in It EraJonathan Joshua FilioNo ratings yet

- Differences Between Primary and Secondary MemoryDocument14 pagesDifferences Between Primary and Secondary MemoryNageshwar YadavNo ratings yet

- UNIT-V-TMS320C54x-DSP ProcessorDocument47 pagesUNIT-V-TMS320C54x-DSP ProcessorVasant DivekarNo ratings yet

- IT 3100 SoftwareManualDocument284 pagesIT 3100 SoftwareManualRobert MachajekNo ratings yet

- Name: - DateDocument5 pagesName: - DateNereo ReoliquioNo ratings yet

- Fundamentals of Computer Mock Test QuestionsDocument17 pagesFundamentals of Computer Mock Test Questionsabdul gani khanNo ratings yet

- Technical Summary: Semiconductor MC68HC11A8 MC68HC11A1 MC68HC11A0 8-Bit MicrocontrollersDocument45 pagesTechnical Summary: Semiconductor MC68HC11A8 MC68HC11A1 MC68HC11A0 8-Bit MicrocontrollersElias CoronelNo ratings yet

- ICT Lab ManualDocument60 pagesICT Lab ManualAiza HabibNo ratings yet

- ITS 204 Hardware and Software InstallationDocument14 pagesITS 204 Hardware and Software Installationleah pileoNo ratings yet

- VLSI Syllabus 2013-14Document43 pagesVLSI Syllabus 2013-14Eric DharanNo ratings yet

- Huawei Quidway AR 19-13Document14 pagesHuawei Quidway AR 19-13EstebanNo ratings yet

- Openecu User Guide Simulink 3 1 0Document681 pagesOpenecu User Guide Simulink 3 1 0Adam TanNo ratings yet

- European Computer Driving Licence Syllabus Version 4.0Document30 pagesEuropean Computer Driving Licence Syllabus Version 4.0James O'ReillyNo ratings yet