Professional Documents

Culture Documents

RK Embedded Solutions B.Tech VLSI Project List

Uploaded by

Sundeep BujjiCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

RK Embedded Solutions B.Tech VLSI Project List

Uploaded by

Sundeep BujjiCopyright:

Available Formats

09652010150 | support@rkembedded.

in

VLSI - B.Tech Projects

S.NO

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18

PROJECT TITLE

A New VLSI Architecture of Parallel MultiplierAccumulator Based on Radix-2 Modified Booth Algorithm. (Verilog) An Efficient Architecture for 3-D Discrete Wavelet Transform. (Verilog) The Design of FIR Filter Base on Improved DA Algorithm and its FPGA Implementation. (Verilog) Design of On-Chip Bus with OCP Interface. (Verilog) Design of a Self-Motivated Arbitration Scheme for the Multilayer AHB Bus matrix. (Verilog) Low Complexity and Fast Computation for Recursive MDCT and IMDCT Algorithms An Efficient Architecture for 2-D Lifting-based Discrete Wavelet Transform. (Verilog) Power-Efficient Pipelined Reconfigurable Fixed-Width Baugh-Wooley Multipliers A Spurious-Power Suppression Technique for Multimedia/DSP Applications(Verilog) Design of AES (Advanced Encryption Standard) Encryption and Decryption Algorithm with 128bits Key Length (VHDL) DDR3 based lookup circuit for high-performance network processing. (Verilog) Multiplication Acceleration Through Twin Precision 32-bit RISC CPU Based on MIPS (VHDL) High Speed Hardware Implementation of 1D DCT/IDCT (Verilog) Efficient FPGA implementation of convolution High Speed VLSI Architecture for General Linear Feedback Shift Register (LFSR) Structures Implementation of a visible Watermarking in a secure still digital Camera using VLSI design Implementation of FFT/IFFT Blocks for OFDM

Projects List 2013

www.rkembedded.in

RK Embedded Solutions

09652010150 | support@rkembedded.in

S.NO

19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36

PROJECT TITLE

Design and Implementation of Efficient Systolic Array Architecture for DWT (Discrete Wavelet Transform) (Verilog) Design and Implementation of 10/100 Mbps (Mega bits per second) Ethernet Switch for Network applications (Verilog) Design and Implementation of USB 2.0 Transceiver Macro-cell Interface (UTMI) (VHDL) A Versatile Multimedia Functional Unit Design Using the Spurious Power Suppression Technique (Verilog) (Same as 9th Project) Design and Implementation of Digital low power base band processor for RFID Tags (Verilog) Design and Implementation of Reversible Watermarking for JPEG2000 Standard FPGA Implementation of 3D Discrete Wavelet Transform for Real-Time Medical Imaging (Same as 3D-DWT no 2 project) Design and Implementation of High Speed DDR SDRAM (Dual Data Rate Synchronously Dynamic RAM) Controller (VHDL) Design and Implementation of Lossless DWT/IDWT for Medical Images High Performance Complex Number Multiplier Using Booth-Wallace Algorithm High Speed Parallel CRC Implementation Based On Unfolding, Pipelining and Retiming Design of an Bus Bridge between OCP and AHB Protocol (VHDL) Design of Gigabit Ethernet MAC (Medium Access Control) Transmitter (VHDL) Design of an AMBA-Advanced High performance Bus (AHB) Protocol IP Block (VHDL) Design of Data Encryption Standard (DES) (Verilog) Design of Distributed Arithmetic FIR Filter (Verilog) Design of Universal Asynchronous Receiver Transmitter (UART) (VHDL) Design of Triple Data Encryption Standard (TDES) (Verilog)

Projects List 2013

www.rkembedded.in

RK Embedded Solutions

09652010150 | support@rkembedded.in

S.NO

37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56

PROJECT TITLE

Design of 16 Point Radix-4 FFT (Fast Fourier Transform) Algorithm (Verilog) Design of Dual Elevator Controller (Verilog) Design of an ATM (Automated Teller Machine) Controller (Verilog) Design of 8-Bit Pico Processor (VHDL) Design of JPEG Image compression standard (Verilog)

Design of Digital FM Receiver using PLL (Phase Locked Loop) (VHDL) Design of 16-bit QPSK (Quadrature Phase Shift Keying) (Verilog) Design of 16-bit QAM (Quadrature Amplitude Modulation) Modulator (Verilog) Design of AES (Advanced Encryption Standard) Encryption Algorithm with 128-bits Key Length(VHDL) Design of RS-232 System Controller (Same as UART) (Verilog) Design of Floating-Point Multiplier using IEEE-754 Standard (Verilog) Design of CRC (Cyclic Redundancy Check) Generator (Same as LFSR) (Verilog)

Design and Implementation of OFDM Transmitter (Same as FFT/IFFT Blocks for OFDM) (VHDL) Design of 8-bit Microcontroller (VHDL) An Efficient Implementation of Floating Point Multiplier An On-Chip AHB Bus Tracer With Real-Time Compression and Dynamic Multi-resolution Supports for SOC. Design and Characterization of Parallel Prefix Adders using FPGAs Radix-8 Booth Encoded Modulo 2n-1Multipliers With Adaptive Delay for High Dynamic Range Residue Number System. Reducing the Computation Time in (Short Bit-Width) Twos Complement Multipliers Self-Immunity Technique to Improve Register File Integrity against Soft Errors

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5795)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Understanding and Effectively Using The SEL MIRRORED BITS Protocol PDFDocument16 pagesUnderstanding and Effectively Using The SEL MIRRORED BITS Protocol PDFRafael Coats RamirezNo ratings yet

- Mobile Shop Management SystemDocument121 pagesMobile Shop Management Systemrajour29% (7)

- Technostream PDFDocument15 pagesTechnostream PDFraulkmainaNo ratings yet

- Cisco Multi Service IP-To-IP Gateway Application GuideDocument178 pagesCisco Multi Service IP-To-IP Gateway Application Guideharoon_niazNo ratings yet

- Illustrated Parts & Service Map: HP Compaq dc5850 Microtower Business PCDocument4 pagesIllustrated Parts & Service Map: HP Compaq dc5850 Microtower Business PCmrtaestNo ratings yet

- AC Project ReportDocument31 pagesAC Project ReportSharif Mohd ZakiNo ratings yet

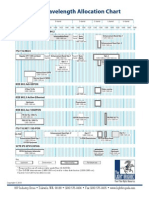

- FTTH Wavelength Allocation Chart: ITU-T G.983.1, G.983.3, and G.984.2Document1 pageFTTH Wavelength Allocation Chart: ITU-T G.983.1, G.983.3, and G.984.2Sohail MuhammadNo ratings yet

- VLab Demo - Using ASM For Web Vulnerabilities - V12.0.0.01Document21 pagesVLab Demo - Using ASM For Web Vulnerabilities - V12.0.0.01Marcos ValleNo ratings yet

- SCSI InterfaceDocument10 pagesSCSI InterfaceApol MaañoNo ratings yet

- Citizen Card System AbstractDocument4 pagesCitizen Card System Abstractarv_ku100% (1)

- Computer Networks Year Question BankDocument5 pagesComputer Networks Year Question Bankakhilek100% (1)

- FortiGate VPN GuideDocument116 pagesFortiGate VPN Guidefarooque_shaikh100% (1)

- Windows Display Driver Model EnhancementsDocument60 pagesWindows Display Driver Model EnhancementsPrashant GautamNo ratings yet

- Components On The MotherboardDocument2 pagesComponents On The MotherboardJIGSNo ratings yet

- 19ci Plan Your Visit1Document8 pages19ci Plan Your Visit1Partha BarmanNo ratings yet

- Hardware AccessoriesDocument2 pagesHardware Accessoriessam29760% (1)

- Introduction and SRS: Chapter-1Document38 pagesIntroduction and SRS: Chapter-1Akash MishraNo ratings yet

- Altiris - Deployment Solution 6.9 SP4 From Symantec Admin Guide - V1.0Document503 pagesAltiris - Deployment Solution 6.9 SP4 From Symantec Admin Guide - V1.0Teppo TestaajaNo ratings yet

- It Is A Very Efficient Method To Search The Exact Data Items Based On Hash TableDocument49 pagesIt Is A Very Efficient Method To Search The Exact Data Items Based On Hash TableDr. Salini SureshNo ratings yet

- 07 - Reading A ThermistorDocument2 pages07 - Reading A ThermistorAl InalNo ratings yet

- HTML5 AssignmentDocument21 pagesHTML5 AssignmentHuynh Phuong100% (1)

- HP t410 Smart Zero Client: Zero Management. Zero Configuration. Zero CompromiseDocument5 pagesHP t410 Smart Zero Client: Zero Management. Zero Configuration. Zero Compromisekonan09No ratings yet

- Real Mode MicroprocessorDocument3 pagesReal Mode MicroprocessorSaqib RaoNo ratings yet

- Dtb7600pt en Es PTDocument63 pagesDtb7600pt en Es PTboaideiaNo ratings yet

- ATN+910B English Version PDFDocument4 pagesATN+910B English Version PDFDeyaniraOjedaNo ratings yet

- PLC ExamDocument5 pagesPLC ExamS. Magidi100% (8)

- ePMP CLI User Guide v3.4.1 PDFDocument28 pagesePMP CLI User Guide v3.4.1 PDFalfonso lopezNo ratings yet

- MSS Config GuideV70Document752 pagesMSS Config GuideV70vhma21No ratings yet

- Design and Performance of Automatic Vending Machine Using VHDLDocument9 pagesDesign and Performance of Automatic Vending Machine Using VHDLIJCERT PUBLICATIONSNo ratings yet

- Xilinx UG230 Spartan-3E FPGA Starter Kit Board User GuideDocument166 pagesXilinx UG230 Spartan-3E FPGA Starter Kit Board User GuideMosu MisuNo ratings yet