Professional Documents

Culture Documents

Parallel Boost

Uploaded by

menguemengueOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Parallel Boost

Uploaded by

menguemengueCopyright:

Available Formats

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 29, NO.

2, FEBRUARY 2014 759

Efciency Optimization Through Current-Sharing

for Paralleled DCDC Boost Converters With

Parameter Estimation

Hugues Renaudineau, Azeddine Houari, Ahmed Shahin, Jean-Philippe Martin, Serge Pierfederici,

Farid Meibody-Tabar, and Bernard Gerardin

AbstractIn this paper, a new current sharing technique on a

general case of N paralleled DCDCboost converters is presented.

The proposed optimization is based on the knowledge of individual

boost parameters. Every loss through the structure are modeled by

equivalent resistors. Using an accurate online estimation of those

resistors, the losses through each individual converter can be de-

termined. Then, a newcurrent sharing scheme is dened aiming to

maximize the global efciency of the overall structure. To verify the

proposed method, simulations and experiments have been realized

on a three-parallel boost converters structure.

Index TermsBoost converters, current-sharing, parallel con-

verters, parameter estimation.

I. INTRODUCTION

P

ARALLELING dcdc converters is widely used since

it leads to many desirable features [1]. First, paralleling

dcdc converters allows a reduction of the size of components,

especially inductive ones. It also reduces stress among individ-

ual converters by segmenting the total power, leading to a better

global efciency. Furthermore, this leads to an enhanced relia-

bility, and allows possible recongurations when one or more of

the paralleled modules present malfunctioning. In nonisolated

applications, the boost converter is one of the most used since

it is well known and allows good efciency. In this paper, an N

parallel boost converters structure with one output capacitor is

considered, as shown in Fig. 1.

A good reliability of energy conversion is always needed. By

diagnosing the fault in its early stages, the reliability of the power

conversion systemcan be increased signicantly [2]. To achieve

this, it is very interesting to develop an efcient online parameter

estimation. Many parameter estimation techniques have already

Manuscript received July 10, 2012; revised September 20, 2012, December

21, 2012, and February 15, 2013; accepted March 18, 2013. Date of current

version August 20, 2013. Recommended for publication by Associate Editor

D. Vinnikov.

H. Renaudineau, A. Houari, J.-P. Martin, S. Pierfederici, and F. Meibody-

Tabar are with the Universit e de Lorraine Vandoeuvre-les-Nancy 54516, France

(e-mail: hugues.renaudineau@univ-lorraine.fr; azeddine.houari@ensem.

inpl-nancy.fr; jean-philippe.martin@ensem.inpl-nancy.fr; serge.pierfederici@

ensem.inpl-nancy.fr; farid.meibody-tabar@ensem.inpl-nancy.fr).

A. Shahin is with the El-Mansoura University, El-Mansoura 35516, Egypt

(e-mail: AHMED.SHAHIN@ENSEM.INPL-NANCY.FR).

B. Gerardin is with ATECH society, Ennery 57365, France (e-mail:

bernard.gerardin@atech-ing.com).

Color versions of one or more of the gures in this paper are available online

at http://ieeexplore.ieee.org.

Digital Object Identier 10.1109/TPEL.2013.2256369

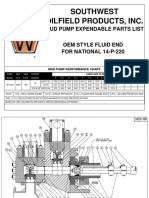

Fig. 1. N parallel boost converters structure with one output capacitor.

been proposed for dcdc boost converters. For example, in [3]

and [4] a method to estimate inductance, capacitor, capacitor

serial resistance, and load is presented. One of the main disad-

vantages of the proposed technique, as for those proposed in [5]

and [6], is that it requires a sampling frequency much higher

than switching frequency. For the present application, the sam-

pling frequency is kept equal to the switching frequency. For

this reason, Shahin et al. work [7] is of great interest. In this

paper, the authors proposed a method to model and estimate

losses of the boost converter through two equivalent resistors.

Note that even if loss modeling is only represented through re-

sistors, those parameters include every loss of the converter such

as capacitive or inductive ones.

Current sharing is an important functionality for parallel

power converters to ensure reliable and efcient operation [8].

A good review of current-sharing techniques has been proposed

by Chen et al. in [9] on different interconnection schemes. A

rst method for controlling parallel boost converters is to dene

one converter as the master which imposes output voltage while

others are slave and only current regulated. Masterslave con-

trol have been used in [1] and [10]. Unfortunately, this control

strategy is not suitable for a good reliability of the global sys-

tem since it might suffer from fault tolerance against the failure

of the master converter [1]. Another method found in the lit-

erature is to use current sharing to manage the output voltage

error as done in [11] by using synergetic control. In [12], current

0885-8993 2013 IEEE

760 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 29, NO. 2, FEBRUARY 2014

sharing is directly integrated in a nonlinear controller design on

the case of a double-input H-bridge-based buckboostbuckboost

converter. A last method which can be underlined is presented

in [13] where the sharing scheme is used to cancel circulating

current between parallel inverters.

However, in most of the applications, current reference is

equally divided between the parallel elements as done in [14]

[17]. Equal power repartition has for example been used in [18],

where the control is realized with a classical PID. Many studies

propose an equal repartition among many different structures,

as for example in [19] on paralleled dual active bridge dcdc

converters. This is also the case for classical control techniques

of paralleled inverters as done in [20] and [21]. Equal repartition

is also used while thinking in voltage mode controlled structures

with no current sensors as done in [22] and [23] on multiphase

buck converter structures.

In this paper, a new current-sharing method based on the

knowledge of estimated loss parameters is proposed. As previ-

ously mentioned, compared with the sharing techniques found

in the literature, the proposed method presents real advantages.

In most of the literature, the current repartition is only designed

in order to allow the system to work. However, as it will be un-

derline in this paper, the repartition can inuence on the global

structure efciency. Classically, this is not taken into account. In

this aim, the new sharing scheme proposed in this paper allows

us to maximize the global efciency of the overall structure.

II. STRUCTURE MODELING AND ESTIMATION

A. Model of the Structure

The system consists in N parallel boost converters with one

output capacitor as shown in Fig. 1. The considered modeling

equations (1a) and (1b) are a direct application of Shahin et al.

work [7]. In this paper, it is proposed to model losses through

a boost converter by adding N serial and one parallel resistors

in the conventional ideal model. For the considered application,

each individual boost converter model has a serial resistance

r

s

k

, while a unique parallel resistor R

p

includes all the rest

of the losses for the whole structure. This difference with the

method proposed in [7] comes from the nature of the structure

with only one output capacitor and one output current sensor.

The next section details the method to obtain an accurate online

estimation of the resistor values

L

k

di

k

dt

= V

in

r

s

k

i

k

(1 d

k

) V

o

(1a)

C

o

dV

o

dt

=

N

k=1

(1 d

k

) i

k

i

Load

V

o

R

p

(1b)

where d

k

represents the duty cycle corresponding to the PWM

output signal u

k

.

Even if the adopted loss modeling is only represented through

resistors, it is useful to underline that not only ohmic losses are

taken into account. In fact, every loss through the converter

is taken into account with those of equivalent resistors, such

as core hysteresis and eddy current losses, conduction ohmic

losses, and switching losses of semiconductors [7]. Particularly,

the parallel resistor R

p

does not only represent the capacitor

C

o

losses through its ESR. Indeed, it is well known the even

under zero power, boost converters still present losses, which

will be taken into account through parameter R

p

while serial

resistor is not able to model this behavior. Finally, parameters

r

s

k

and R

p

represent the overall losses through the structure.

This will be veried in the experimental part by checking that

calculated losses correspond to measurement. For a more detail

description of this loss modeling technique, the reader is invited

to read reference [7], where analytical study is presented, as

well has load dependence behavior of such a modeling in the

case of a single-boost converter.

It has to be noticed that the estimation of losses through the

converters can also been used for others purpose. As an exam-

ple, it can be used for verifying the ageing of the individual

converters by checking on the variations of the estimated equiv-

alent resistors. This aspect cannot be developed in this paper

since it is not its goal, but reader is again invited to read [7] for

more details on the estimation.

B. Parameters Online Estimation

Before designing control laws and current-sharing technique,

the system parameters need to be estimated. This has to be real-

ized by considering online sampled signals, namely, V

in

, i

k

, V

o

and i

Load

. As proposed in [7], it is possible to estimate the

equivalent loss resistors following (2) and (4).

Considering that the input power follows its reference P

in

=

P

ref

in

t, serial resistors will be estimated through (2). This con-

dition will be ensured with the current regulation presented in

Section III

d r

s

k

dt

=

s

k

_

P

out

k

P

out

k

_

_

V

in

P

in

k

_

2

. (2)

Wherepower P

out

k

and estimated power

P

out

k

follow(3), and

s

k

convergence coefcients corresponding to serial resistor r

s

k

P

out

k

= (1 d

k

) V

o

i

k

P

out

k

= P

in

k

r

s

k

_

P

in

k

V

in

_

2

.

(3)

Then, considering the output voltage perfectly regulated

(V

o

= V

ref

o

t), the parallel resistor will be estimated through

(4). This condition will be ensured through the energy regulation

presented in the following section

d

R

p

dt

=

p

_

i

d

i

d

_

R

2

p

V

o

. (4)

Where current i

d

=

k

(1 d

k

) i

k

, estimated current

i

d

=

i

Load

+

V

o

R

p

, and

p

convergence coefcient for parallel resistor

R

p

.

C. Stability of the Estimation

Exponential stability can be proved easily with the classical

Lyapunov approach [7]. The stability and dynamics of the pro-

posed estimations are determined by coefcients

s

k

and

p

.

In order to demonstrate their stability, the Lyapunov candidate

RENAUDINEAU et al.: EFFICIENCY OPTIMIZATION THROUGH CURRENT-SHARING FOR PARALLELED DCDC BOOST CONVERTERS 761

Fig. 2. Control strategy. Measurements are in green.

functions following (5) are dened as

V ( r

s

k

) =

1

2

_

P

out

k

P

out

k

_

2

V

_

R

p

_

=

1

2

_

i

d

i

d

_

2

.

(5)

For a positive input power, their derivative can be expressed

through (6)

V ( r

s

k

) =

_

P

out

k

P

out

k

_ d

_

P

out

k

P

out

k

_

d r

s

k

d r

s

k

dt

V

_

R

p

_

=

_

i

d

i

d

_ d

_

i

d

i

d

_

d

R

p

d

R

p

dt

(6)

The derivatives of Lyapunov functions (6) can be simplied

in view of (2) and (4), leading to (7)

V ( r

s

k

) =

s

k

_

P

out

k

P

out

k

_

2

2

s

k

V ( r

s

k

)

s

k

,

p

> 0

V

_

R

p

_

=

p

_

i

d

i

d

_

2

2

p

V

_

R

p

_

.

(7)

Then, by choosing those two parameters positive, it is demon-

strated that the estimation errors exponentially converge to 0.

III. CONTROL DESIGN

To ensure the control of the structure, it has been decided

to design a two-loop control scheme. A rst controller enables

voltage regulation through energy control. It is based on at-

ness control method. A second-loop controller, based on sliding

method, ensure the current regulation for each individual con-

verter. The proposed control strategy ensures asymptotic stabil-

ity, robustness against parameter variations, and high dynamics

regulation. A block schematic of the entire control is given in

Fig. 2.

A. Energy Control Loop Based on Flatness

Flatness was rstly dened by Fliess et al. [24] using the

formalism of differential algebra. It has been decided to indi-

rectly control the output voltage V

o

by regulating the energy E

(8) stored in the capacitor C

o

. As detailed in [25] and [7], it is

possible to demonstrate that E is a at output for the considered

system in view of (1a) and (1b)

E =

1

2

C

o

V

2

o

. (8)

To obtain a relationship between the input current references

i

ref

k

and the at output system E, the derivative

E is considered

as

E = P

out

P

Load

V

2

o

R

p

. (9)

To ensure reference tracking, a second-order control law as

(10) is proposed to cancel the static error

_

E

ref

E

_

+2

E

n

E

(E

ref

E)+

2

n

E

_

(E

ref

E) dt = 0.

(10)

The power P

out

is given as follows:

P

out

= P

in

N

k=1

r

s

k

_

k

P

in

V

in

_

2

. (11)

The parameters

k

are power repartition coefcients. In the

next section, a new current-sharing scheme aiming to maximize

the overall efciency will be detailed as a function of the pa-

rameters

k

. However, in order to transfer the needed power

through the structure, repartition coefcients must follow:

N

k=1

k

= 1

N

= 1

N1

k=1

k

. (12)

Finally, current references are deduced from (13). Parameter

P

ref

in

of this equation will be dened in Section IV

i

ref

k

=

k

P

ref

in

V

in

. (13)

B. Current Loops Designa Sliding Approach

To ensure current regulation, it has been decided to design a

sliding-based controller as used in [26]. Sliding based control

allows robust regulation and has been detailed in [27]. It has al-

ready been applied on the case of paralleled boosts in [28] where

robustness against inductor variations is underlined and guaran-

teed. For each individual boost converter, the sliding surface S

k

is dened as follows:

S

k

=

_

i

k

i

ref

k

_

+ K

i

k

_

_

i

k

i

ref

k

_

dt. (14)

The current i

k

will follow its reference i

ref

k

if the derivative

of the surface S

k

verify

S

k

=

i

k

S

k

. (15)

Equations (14) and (15) can be expressed as

k

+ (K

i

k

+

i

k

)

k

+ K

i

k

i

k

_

k

dt = 0 (16)

where K

i

k

and

i

k

are the current regulation parameters and

k

=

_

i

k

i

ref

k

_

. Comparing (16) with a second-order law, it is

762 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 29, NO. 2, FEBRUARY 2014

TABLE I

REGULATION PARAMETERS

possible to express current regulation pulsation

I

as

2

I

k

= K

i

k

i

k

. (17)

By combining (1) and (15), it is possible to determine the

equivalent duty cycle d

k

e q

allowing a good reference tracking

d

k

e q

= 1 +

1

V

o

_

r

s

k

i

k

V

in

+L

k

_

i

k

S

k

+

di

ref

k

dt

K

i

k

_

i

k

i

ref

k

_

_

_

. (18)

C. Regulation Parameters

For simulations and experimental validation, the switching

frequency is set to f

s

= 20 kHz. Table I shows parameters of

the controllers. Parameters

i

k

are chosen in order to verify

(19) which is necessary to ensure the validity of the used mean

model. In a two-loop control scheme, dynamics of the regulation

must be separated, then

n

E

is chosen in order to satisfy

_

s

= 2f

s

i

k

(19a)

i

k

n

E

.

(19b)

IV. REFERENCE POWER REPARTITION METHOD

By combining (9) and (11), the energy regulation gives the

expression (20) of the total input power reference P

ref

in

as a

function of repartition parameters

k

, with P

ref

out

calculated from

(9) as shown in Fig. 2

P

ref

in

=

V

2

in

_

V

4

in

4 P

ref

out

_

N

k=1

2

k

r

s

k

_

2

_

N

k=1

2

k

r

s

k

_ . (20)

Then, a new method to split the power between the parallel

boost converters is presented. The proposed repartition aims

to maximize the global efciency of the structure. Indeed, it

is possible to demonstrate that there is a unique point which

minimizes the total input power reference P

ref

in

. This can be

seen in Fig. 3, where total input power is presented as a function

of power repartition parameters on the case of three-parallel

boost converters with the same parameters as used in Section V.

Only two coefcients appear in this gure, while it is about a

three-parallel boost converter structure; the third one is indeed

directly imposed from (12).

As an example, in this case the minimum value differ from

equal repartition possibility. Then, the interest of the proposed

method appears easily compared to the most used current-

sharing technique. Therefore, it is needed to determine the repar-

Fig. 3. Input power function of power repartition coefcients for an imposed

load of 620 W.

tition parameters

k

, so that the input power reference P

ref

in

is

minimum for a given load reference P

ref

out

. In view of (12), P

ref

in

is a function of N 1 parameters. Minimizing this reference

power leads to solve

_

P

ref

in

k

= 0, k = {1, N 1} . (21)

The optimal values of parameters

k

minimizing the input

reference power can be expressed as (22), presenting the advan-

tage to be quite simple and so easily implementable. Under low

power, parameters r

s

k

can not be precisely dened (they tend to

innite for zero current). In this case, it is chosen to stop N 1

converters and uses only one

opt

k

=

N

j = 1

j = k

r

s

j

N

i=1

N

j = 1

j = i

r

s

j

. (22)

Then, knowing parameters

k

, the input power reference

is calculated from (20) so that it is possible to nd current

references for each individual converter as (13). If the paral-

lel converters have strictly the same parameters, the proposed

repartition leads to equal current references

k

=

1

N

. The main

interest in the proposed method appears when one converter or

more present a lower efciency compared to the others (result-

ing in differences on the estimated parameters r

s

k

). In this case,

the proposed repartition leads to a lower current reference for

the less efcient converter, leading to a benet on the global

efciency.

Finally, before presenting simulation and experimental val-

idation lets underline requirements for practical application of

the proposed method. First, while measuring some precautions

must be taken into account but such requirements are among the

classical thematic of digital control, and the proposed technique

does not require more accurate measurement than classically

used for controlling similar power conversion structures. Sec-

ond, in term of computational resources, it is obvious that this

current-sharing strategy requires more than a simple equal shar-

ing. However, additional calculations are quite simple and the

additional required computation time is not important. Then, in

most of the cases, implementing the proposed technique will

RENAUDINEAU et al.: EFFICIENCY OPTIMIZATION THROUGH CURRENT-SHARING FOR PARALLELED DCDC BOOST CONVERTERS 763

TABLE II

EXPERIMENTAL PARAMETERS

not require to be changed the digital controller for an improved

one.

V. SIMULATION RESULTS

Simulation on three-parallel boost converters have been real-

ized to verify the effectiveness of the proposed method. First,

the current repartition is set to

k

=

1

3

. At time t = 0.5 s, the

proposed power repartition is enabled. Parameters taken for

simulation are the same as those listed in Table II for experi-

mental verication. Serial and parallel resistors of the simulated

model are chosen constant for an easier computation. To vali-

date our purpose, the simulated paralleled boost converters on

which the proposed control is applied present different efcien-

cies for each individual converter. This is simulated by imposing

r

s

1

= 0.39 , r

s

2

= 0.39 , and r

s

3

= 1.40 traducing more

losses through the third individual converter. This difference be-

tween serial resistors is only one modeling of a poorer behavior

of the third converter. On a real boost converter, many reasons

can lead to such results, as many different losses are taken into

account through this resistor (see Section II-A and reference [7]

for more details).

First, it is ensured that the estimated resistors converge to

their simulated values. Then, from(22), it is possible to calculate

optimal repartition coefcients as

opt

1

= 0.439

opt

2

= 0.439

opt

3

= 0.122.

(23)

This results on different current references for each converter.

Fig. 4 shows current on the previously described control scheme.

Fig. 5 shows the efciency of the structure. In this gure, the ef-

ciency of the proposed current-sharing scheme can be observed.

Indeed, when total power is equally divide through elements

(t < 0.5 s), efciency is about 2.4% less than the efciency

with the proposed method. Note that the difference with respect

to experimental result comes from the hypothesis that estimated

resistors are constant. In practice, those resistors change with

respect to the power as well described in [7]. This is also the

reason why their is no long transitory in simulation, as explained

in the experimental part.

In view of these results, another advantage of the proposed

current sharing can be underlined. As shown in Fig. 4, the pro-

posed repartition leads to a lower current in the less efcient

converter. Then, this converter will suffer lower stress than bet-

Fig. 4. Simulated average input currents i

k

.

Fig. 5. Efciency of the structureSimulation result.

ter converters. Finally, it can be assumed that the proposed

current-sharing scheme leads to make uniform ageing of the

paralleled modules. Only ageing tests can corroborate this as-

sertion but this aspect will not be treated in this paper. This

property should have an effect on the structure health improv-

ing its long-term reliability and facilitating its maintenance. For

example, a three-parallel boost converter structure can be easily

realized using integrated circuits planned for inverters. In this

case, the ageing uniformity resulting fromthe proposed current-

sharing scheme, will ensure a replacement of the used module

when all the semiconductors are decient. On the other hand,

for classical methods, the replacement can be needed for only

one of the converters presenting malfunctioning.

VI. EXPERIMENTAL VERIFICATION

To verify the validity of the proposed method, experiments

are performed on a three-parallel boost converters structure.

Parameters of the tested structure are listed on Table II and

the experimental hardware step-up is shown in Fig. 6. Control

and estimation are realized with MATLAB-Simulink software

and implemented; thanks to the dSpace 1103 device. Sampling

is synchronized with the PWM signal; therefore, measurement

gives the mean values of the voltages and currents. In order

to validate the proposed method, one of the parallel boost is

articially aged by introducing a 1 resistor in series.

764 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 29, NO. 2, FEBRUARY 2014

Fig. 6. Experimental test bench.

Fig. 7. Convergence of estimated parameters r

s

k

Experimental result.

Fig. 8. Convergence of estimated parameter R

p

Experimental result.

A. Control and Losses Estimation Validations

First, the validity of losses estimation is veried. Figs. 7 and

8 attest the convergence of estimated resistors. As expected, one

of the serial resistor in about 1 higher than other, allowing to

verify the interest and validity of the proposed power repartition.

The correctness of those estimated parameters is also veried

as measured losses are equal to estimated ones.

Fig. 9. Verication of the energy regulationResult on the output voltage

V

o

Starting.

Fig. 10. Verication of the currents regulationMean values of the currents

for a load step.

Fig. 9 shows voltage response when the regulation starts.

At this time, output voltage varies from V

o

= V

in

= 48 V to

V

o

= 100 V as expected. Fig. 10 shows the validity of current

regulations for a step of load from R

Load

= 30 to R

Load

=

15 with equal power sharing between the three converters. In

this gure, only mean values of the currents are shown.

B. Current-Sharing Verication

In this section, the behavior of the proposed current-sharing

scheme is veried and compared with equal repartition. Those

results have been obtained with a constant resistive load

R

Load

= 15.15 . As previously done by simulation, the next

results have been obtained when power repartition passes from

equal (

k

=

1

3

) to the new optimal denition introduced in this

paper. Fig. 11 shows the evolution of the structure efciency,

and Fig. 12 the corresponding sampled currents i

k

. Repartition

parameters obtained with our method converge to the following

values:

opt

1

= 0.438

opt

2

= 0.440

opt

3

= 0.122.

(24)

RENAUDINEAU et al.: EFFICIENCY OPTIMIZATION THROUGH CURRENT-SHARING FOR PARALLELED DCDC BOOST CONVERTERS 765

Fig. 11. Efciency of the structureExperimental result.

Fig. 12. Sampled currents i

k

repartitionExperimental result.

Fig. 11 shows the validity of the proposed current-sharing

scheme in term of efciency, compared with the classical equal

sharing technique. In this gure, the system starts with equal

sharing between the converters, and when the proposed tech-

nique is enabled, values are those of (24). After, the proposed

repartition is enabled, the efciency converges to a higher value.

The transitory which can be seen in this gure comes to the fact

that estimated resistor values change with the functioning point,

then changing the repartition which itself changes the function-

ing point, and so forth, leading to a quite long transitory. This

long transitory is only present in the tested case, where reparti-

tion passes from equal to the proposed one to underline its ben-

et. In real application, this transitory will not exist while only

one of the two repartition scheme will be applied (the proposed

one). This transitory is also visible in Fig. 12, where currents

took time to denitely stabilize when the proposed approach is

applied. In this case, when all values have converged with the

proposed repartition, the new value of estimated resistors are

r

s1

= 0.356 , r

s2

= 0.354 and r

s1

= 1.459 , leading to

repartition parameters following (25). This difference explains

the transitory, and is also the cause of the difference with the

results shown in simulation where equivalent loss resistors have

been chosen constant with values equal to the one estimated

TABLE III

EXPERIMENTAL PARAMETERS

Fig. 13. Efciency load dependenceAdvantage of the proposed method.

with equal sharing

opt

1

= 0.443

opt

2

= 0.447

opt

3

= 0.108.

(25)

For the tested case, the global efciency of the structure in-

creases from = 78.7%to = 81.4%when the proposed strat-

egy is applied. Then, compared to equal sharing, which is the

most used power repartition scheme, the method detailed in this

paper allows a global efciency higher than 2.7%.

As mentioned viewing simulation results, the proposed tech-

nique should lead to make uniform ageing between parallel

elements. This can be visible in Fig. 12, where the current in the

converter presenting the more losses is the lower.

C. Load Dependence Experiment

In this part, the behavior of loss parameters and efciency

are experiment with respect to the load power. As explained

previously, estimated loss resistors change with respect to the

load. Then, advantage of the proposed method will depend on

the load power. Four level of power have been tested and are

listed in Table III.

The efciency of the converter with equal sharing and with the

proposed method are shown in Fig. 13. First, this result conrm

the attractivity of the proposed repartition scheme since it leads

to a gain in efciency on the entire load range from1.65%under

low power to 4.5% gain under higher power. It is also possible

to underline that the gain increases when power increases, and

that the maximum of efciency of the structure is higher with

the proposed method. Then, compared with the classical equal

sharing technique, the proposed method shows great advantage

on the structure efciency.

766 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 29, NO. 2, FEBRUARY 2014

VII. CONCLUSION

Anewcurrent-sharing technique on parallel dcdc boost con-

verters has been presented in this paper. Through online es-

timation, individual converter losses are deduced and power

repartition coefcients are redened in order to maximize the

efciency of the overall structure. Output voltage and individual

input currents are regulated through a two-loop control design

based on atness theory and sliding mode controllers.

Compared with the most used current-sharing technique con-

sisting in equal repartition, the proposed method shows its inter-

est when one or more converter in parallel present malfunction-

ing. In these conditions, the presented method allows a gain in

efciency up to 4.5% in the tested cases, depending on the load

power. Another benet of the proposed repartition is the fact

that it leads to uniform ageing between the paralleled elements.

This should have an effect on the structure health improving its

long-termreliability and facilitating its maintenance. Long-term

experimentations are required to attest this last assumption and

will be part of future works.

The presented current sharing has been discussed, veried,

and tested both by simulation and experiment. The validation

has been realized on the case of a three-parallel boost converter

structure, but the concept can easily be scaled to any number of

phases. Indeed, theoretical study has been led on the general case

of N converters in parallel. Practically, each phase will need its

own current regulation, its own serial resistor estimation, and

the repartition coefcients calculation will require only a few

more time as the number of converter increase.

REFERENCES

[1] A. Altowati, K. Zenger, and H. Koivo, Modeling and control design of

paralleled DCDC switching converters, presented at the Proc. Int. Conf.

Commun., Comput. Power, Sultan Qaboos University, Oman, 2009.

[2] A. Izadian and P. Khayyer, Application of Kalman lters in model-based

fault diagnosis of a DCDC boost converter, in Proc. I-36th Annu. Conf.

IEEE Ind. Electron. Soc., 2010, pp. 369372.

[3] G. Buiatti and A. Amaral, Parameter estimation of a dc/dc buck converter

using a continuous time model, in Proc. Eur. Conf. Power Electron. Appl.,

2007, pp. 18.

[4] G. Buiatti, A. Amaral, and A. Cardoso, An online technique for estimating

the parameters of passive components in non-isolated DC/DCconverters,

in Proc. IEEE Int. Symp. Ind. Electron., 2007, pp. 606610.

[5] B. Wang, Early oscillation detection for dc/dc converter fault diagnosis,

presented at the AIAA 9th Int. Energy Convers. Eng. Conf., San Diego,

CA, USA, 2011.

[6] Y.-T. Chang and Y.-S. Lai, Parameter tuning method for digital power

converter with predictive current-mode control, IEEE Trans. Power Elec-

tron., vol. 24, no. 12, pp. 29102919, Dec. 2009.

[7] A. Shahin, A. Payman, J.-P. Martin, S. Pierfederici, and F. Meibody-Tabar,

Approximate novel loss formulae estimation for optimization of power

controller of DCDC converter, in Proc. 36th Annu. Conf. IEEE Ind.

Electron. Soc., 2010, pp. 373378.

[8] J. Abu-Qahouq, Analysis and design of N-phase current-sharing auto-

tuning controller, IEEE Trans. Power Electron., vol. 25, no. 6, pp. 1641

1651, Jun. 2010.

[9] W. Chen, X. Ruan, H. Yan, and C. Tse, DCDC conversion systems con-

sisting of multiple converter modules: Stability, control, and experimental

verications, IEEETrans. Power Electron., vol. 24, no. 6, pp. 14631474,

Jun. 2009.

[10] P. Li and B. Lahman, A design method for paralleling current mode

controlled dc-dc converters, IEEE Trans. Power Electron., vol. 19, no. 3,

pp. 748756, May 2004.

[11] I. Kondratiev, E. Santi, and R. Dougal, Robust nonlinear synergetic con-

trol for m-parallel-connected DCDC boost converters, in Proc. IEEE

Power Electron. Spec. Conf., 2008, pp. 22222228.

[12] R. Ahmadi, H. Zargarzadek, and M. Ferdowsi, Nonlinear power sharing

controller for a double-input h-bridge-based buckboost-buckboost con-

verter, IEEE Trans. Power Electron., vol. 28, no. 5, pp. 24022414, May

2013.

[13] Y. Zhang, M. Yu, F. Liu, and Y. Kang, Instantaneous current-sharing

control strategy for parallel operation of ups modules using virtual

impedance, IEEE Trans. Power Electron., vol. 28, no. 1, pp. 432440,

Jan. 2013.

[14] R. Ayyanar, R. Giri, and N. Mohan, Active input-voltage and load-

current sharing in input-series and output-parallel connected modular

dc-dc converters using dynamic input-voltage reference scheme, IEEE

Trans. Power Electron., vol. 19, no. 6, pp. 14621473, Nov. 2004.

[15] J. Kimball, J. Mossoba, and P. Krein, Control technique for series input-

parallel output converter topologies, in Proc. -IEEE 36th Power Electron.

Spec. Conf., 2005, pp. 14411445.

[16] F. Garcia, J. Pomilio, and G. Spiazzi, Modelling and control design of the

six-phase interleaved double dual boost converter, in Proc. 9th IEEE/IAS

Int. Conf. Ind. Appl., 2010, pp. 16.

[17] P. Thounthong and B. Davat, Study of a multiphase interleaved step-up

converter for fuel cell high power applications, Energy Convers. Manag.,

vol. 51, pp. 826832, 2010.

[18] C.-H. Cheng, P.-J. Cheng, and M.-J. Xie, Current sharing of paralleled

DCDC converters using GA-based PID controllers, Expert Syst. Appl.,

vol. 37, pp. 733740, 2010.

[19] J. Shi, L. Zhou, and X. He, Common-duty-ratio control of input-parallel

output-parallel (ipop) connected DCDC converter modules with auto-

matic sharing of currents, IEEE Trans. Power Electron., vol. 27, no. 7,

pp. 32773291, Jul. 2012.

[20] A. Roslan, K. Ahmed, S. Finney, and B. Williams, Improved instan-

taneous average current-sharing control scheme for parallel-connected

inverter considering line impedance impact in microgrid networks, IEEE

Trans. Power Electron., vol. 26, no. 3, pp. 702716, Mar. 2011.

[21] D. Sha, Z. Guo, and X. Liao, Control strategy for input-parallel-output-

parallel connected high-frequency isolated inverter modules, IEEETrans.

Power Electron., vol. 26, no. 8, pp. 22372248, Aug. 2011.

[22] Y. Cho, A. Koran, H. Miwa, B. York, and J.-S. Lai, An active current

reconstruction and balancing strategy with DC-link current sensing for a

multi-phase coupled-inductor converter, IEEE Trans. Power Electron.,

vol. 27, no. 4, pp. 16971705, Apr. 2012.

[23] R. Foley, R. Kavanagh, and M. Egan, Sensorless current estimation and

sharing in multiphase buck converters, IEEE Trans. Power Electron.,

vol. 27, no. 6, pp. 29362946, Jun. 2012.

[24] M. Fliess, J. Levine, P. Martin, F. Ollivier, and P. Rouchon, Controlling

nonlinear systems by atness, in Systems and Control in the Twenty-

First Century, Progress in Systems and Control Theory, D. G. C. I Byrnes,

B. N. Datta, and C. Martin, Eds. Cambridge, MA, USA: Birkhauser,

1997.

[25] A. Payman, S. Pierfederici, and F. Meibody-Tabar, Energy management

in a fuel cell/supercapacitor multisource/multiload electrical hybrid sys-

tem, IEEE Trans. Power Electron., vol. 24, no. 12, pp. 26812691, Dec.

2009.

[26] G. Spiazzi, P. Mattavelli, L. Rossetto, and L. Malesani, Application of

sliding mode control to switch-mode power supplies, J. Circuits, Syst.,

Comput., vol. 5, pp. 337354, 1995.

[27] X. Yu and O. Kaynak, Sliding-mode control with soft computing: A

survey, IEEE Trans. Ind. Electron., vol. 56, no. 9, pp. 32753285, Sep.

2009.

[28] M. L opez, L. Garcia de Vicuna, M. Castilla, P. Gaya, and O. L opez, Cur-

rent distribution control design for paralleled DCDC converters using

sliding-mode control, IEEE Trans. Ind. Electron., vol. 51, no. 2, pp. 419

428, Apr. 2004.

Hugues Renaudineau received the M.S. degree

in electrical engineering from Ecole Nationale

Sup erieure d

Electricit, Nancy, France, in 2009. He

is currently working toward the the Ph.D. degree with

the Groupe de Recherche en Electrotechnique et Elec-

tronique de Nancy (GREEN), University of Lorraine,

Nancy, in partnership with ATECH society.

His main research interests are modeling, control,

and diagnosis on photovoltaic power systems.

RENAUDINEAU et al.: EFFICIENCY OPTIMIZATION THROUGH CURRENT-SHARING FOR PARALLELED DCDC BOOST CONVERTERS 767

Azeddine Houari received the Engineers degree in

2008 from Bejaia University, Bejaia, Algeria, and the

M.Sc. and Ph.D. degrees from the Institut National

Polytechnique de Lorraine, Vandoeuvre les Nancy,

France, in 2009 and 2012, respectively.

He is currently a Doctor with the Groupe de

Recherche en Electrotechnique et Electronique de

Nancy (GREEN), University of Lorraine, Nancy . His

current research interests include control of electri-

cal hybrid systems, renewable energies, and stability

study in microgrid applications.

Ahmed Shahin received the B.Sc. (rst class Hons.)

and M.Sc. degrees in electrical engineering from the

Department of Electrical Engineering, the Faculty of

Engineering, El-Mansoura University, El-Mansoura,

Egypt, in 2000 and 2004, respectively and the Ph.D.

degree in electrical engineering fromEcole Nationale

Sup erieure d

Electricit, Institut National Polytech-

nique de Lorraine, Nancy-University, Nancy, France,

in 2011.

Since 2012, he has been engaged as a Doctor at

Mansoura University, Egypt. His research interests

are modeling, digital control, power electronics, dcdc converters and active

lter, and fuel cell applications.

Jean-Philippe Martin received the Graduation de-

gree from the University of Nancy, Nancy, France,

and the Ph.D. degree fromInstitut National Polytech-

nique de Lorraine (INPL), University of Lorraine,

Nancy, in 2003.

Since 2004, he has been an Assistant Professor

at INPL. His research activities in GREEN Labora-

tory include the stability study of distributed power

system, electrical machine controls, static converter

architectures, and their interactions with new electri-

cal devices (fuel cell and photovoltaic system).

Serge Pierfederici received the Engineers de-

gree in electrical engineering from Ecole Nationale

Sup erieure d

Electricit e Nancy, France, in 1994, and

the Ph.D. degree fromInstitut National Polytechnique

de Lorraine (INPL), University of Lorraine, Nancy,

France, in 1998.

Since 2009, he has been a Professor at INPL.

His research activities deals with the stability study

of distributed power system and the control of multi

sources, and multiload systems.

FaridMeibody-Tabar received the Enginees degree

from Ecole Nationale dElectricit e et de M ecanique

(ENSEM), Nancy, France in 1982, the Ph.D. degree

and the Habilitation ` a diriger des recherches degree

in 1986 and 2000, both from the Institut National

Polytechnique de Lorraine, (INPL), University of

Lorraine, Nancy.

Since 2000, he has been a Professor at the Uni-

versity of Lorraine (ex. INPL). His research activi-

ties in GREEN laboratory (Groupe de Recherche en

Electrotechnique et Electronique de Nancy) deal with

electric machines, their supply, and their control and diagnosis.

Bernard Gerardin is the General Manager of ATECH society, Ennery, France,

since 2002 . He works on industrial applications dealing with electric devices,

automatism, and industrial computing. His main research interests include di-

agnosis on photovoltaic power systems.

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Power PhrasesDocument23 pagesPower Phrasesname isNo ratings yet

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Performance Appraisal Form For ManagerDocument12 pagesPerformance Appraisal Form For Managervandana_dubey15No ratings yet

- Oem National 14-P-220 7500psiDocument9 pagesOem National 14-P-220 7500psiandrew0% (1)

- Chapter-2 Keyless MotorcycleDocument27 pagesChapter-2 Keyless MotorcyclePatrick Jimenez100% (3)

- Content:: Saudi Arabian Oil Company (Saudi Aramco) General Instruction ManualDocument3 pagesContent:: Saudi Arabian Oil Company (Saudi Aramco) General Instruction Manualmalika_00No ratings yet

- Successful Advertising With Google AdWordsDocument157 pagesSuccessful Advertising With Google AdWordsJerrod Andrews100% (2)

- Civil Engineering and SocietyDocument23 pagesCivil Engineering and Societyyeah100% (3)

- Building Materials Reuse and RecycleDocument10 pagesBuilding Materials Reuse and RecyclemymalvernNo ratings yet

- Optical Nanoantennas PDFDocument6 pagesOptical Nanoantennas PDFmenguemengueNo ratings yet

- Multilayered Metamaterials PDFDocument8 pagesMultilayered Metamaterials PDFmenguemengueNo ratings yet

- Bifurc Coupled Osc PDFDocument9 pagesBifurc Coupled Osc PDFmenguemengueNo ratings yet

- Nanoradar Based On Nonlinear Dimer NanoantennaDocument3 pagesNanoradar Based On Nonlinear Dimer NanoantennamenguemengueNo ratings yet

- Soliton Interaction PDFDocument6 pagesSoliton Interaction PDFmenguemengueNo ratings yet

- Light Nanoantennas PDFDocument11 pagesLight Nanoantennas PDFmenguemengueNo ratings yet

- Rossby WavesDocument8 pagesRossby WavesmenguemengueNo ratings yet

- Multimode Waveguides PDFDocument3 pagesMultimode Waveguides PDFmenguemengueNo ratings yet

- Bose Einstein PDFDocument4 pagesBose Einstein PDFmenguemengueNo ratings yet

- Yu. S. Kivshar - Bright and Dark Spatial Solitons in Non-Kerr MediaDocument44 pagesYu. S. Kivshar - Bright and Dark Spatial Solitons in Non-Kerr Media23213mNo ratings yet

- FDTD Numerics PDFDocument4 pagesFDTD Numerics PDFmenguemengueNo ratings yet

- Intrinsic Modes PDFDocument6 pagesIntrinsic Modes PDFmenguemengueNo ratings yet

- Photonic Crystals PDFDocument3 pagesPhotonic Crystals PDFmenguemengueNo ratings yet

- A: Multistable Nonlinear Surface ModesDocument9 pagesA: Multistable Nonlinear Surface ModesmenguemengueNo ratings yet

- Soliton Perturbations PDFDocument4 pagesSoliton Perturbations PDFmenguemengueNo ratings yet

- Solitons Waveguides PDFDocument3 pagesSolitons Waveguides PDFmenguemengueNo ratings yet

- Vortex Optics PDFDocument9 pagesVortex Optics PDFmenguemengueNo ratings yet

- Bright Kerr PDFDocument3 pagesBright Kerr PDFmenguemengueNo ratings yet

- Plasmons Waveguides PDFDocument5 pagesPlasmons Waveguides PDFmenguemengueNo ratings yet

- Ferromagnets PDFDocument5 pagesFerromagnets PDFmenguemengueNo ratings yet

- Modes Frenkel PDFDocument15 pagesModes Frenkel PDFmenguemengueNo ratings yet

- Sine-Gordon Soliton PDFDocument3 pagesSine-Gordon Soliton PDFmenguemengueNo ratings yet

- Volume 111A, Number 8,9 Physics Letters 7 October 1985Document3 pagesVolume 111A, Number 8,9 Physics Letters 7 October 1985menguemengueNo ratings yet

- Competing Nonlinearities With MetamaterialsDocument4 pagesCompeting Nonlinearities With MetamaterialsmenguemengueNo ratings yet

- Chiral MetamaterialsDocument6 pagesChiral Metamaterialspobio-1No ratings yet

- Piezoelectric EffectDocument3 pagesPiezoelectric Effecteswar6280100% (1)

- Four Wave Mixing Meta PDFDocument6 pagesFour Wave Mixing Meta PDFmenguemengueNo ratings yet

- Torsional Meta PDFDocument16 pagesTorsional Meta PDFmenguemengueNo ratings yet

- Magnetoelastic Metamaterials PDFDocument5 pagesMagnetoelastic Metamaterials PDFmenguemengueNo ratings yet

- Convert Phase Noise To JitterDocument10 pagesConvert Phase Noise To JitterBo LuNo ratings yet

- Cascaded Transformers:: Figure 1.basic 3 Stage Cascaded TransformerDocument3 pagesCascaded Transformers:: Figure 1.basic 3 Stage Cascaded TransformeryugendraraoknNo ratings yet

- Silabus Reading VDocument4 pagesSilabus Reading VAndi AsrifanNo ratings yet

- Dimetra Ip CompactDocument2 pagesDimetra Ip CompactGrompolLopmorgNo ratings yet

- ValvesDocument1 pageValvesnikhilNo ratings yet

- OZONE 70W Programmable LED Drivers :: ROAL Living EnergyDocument12 pagesOZONE 70W Programmable LED Drivers :: ROAL Living EnergyroalscribdNo ratings yet

- Window/ Water Curtain Nozzle: Model CN & CnsDocument4 pagesWindow/ Water Curtain Nozzle: Model CN & CnsWirat WitaphanNo ratings yet

- AVEVA VPRM Internationalisation SupportDocument25 pagesAVEVA VPRM Internationalisation SupportShahfaraz Ahmad0% (1)

- Behringer FX2000-Product InfoDocument10 pagesBehringer FX2000-Product Infogotti45No ratings yet

- Alternator LSA42.3j enDocument12 pagesAlternator LSA42.3j enArdi Wiranata PermadiNo ratings yet

- Altman Fall Winter 2012 Product Showcase FlyerDocument32 pagesAltman Fall Winter 2012 Product Showcase FlyerИлия ГеоргиевNo ratings yet

- 1 Input Data: Profis Anchor 2.8.1Document7 pages1 Input Data: Profis Anchor 2.8.1Manu MohanNo ratings yet

- 165 NebulizerDocument2 pages165 NebulizerLotfi BahriNo ratings yet

- Challenges in Providing Leisure and RecreationDocument6 pagesChallenges in Providing Leisure and RecreationAnalyn CabilloNo ratings yet

- EV 10 Best Practice - Implementing Enterprise Vault On VMware (January 2012)Document31 pagesEV 10 Best Practice - Implementing Enterprise Vault On VMware (January 2012)TekkieNo ratings yet

- FLIX Luggage Tags 8055071906Document1 pageFLIX Luggage Tags 8055071906Bhargav RamNo ratings yet

- Ejemplitos de Latex: H Ector Manuel Mora Escobar Universidad Central, Bogot ADocument20 pagesEjemplitos de Latex: H Ector Manuel Mora Escobar Universidad Central, Bogot AAmanda GarciaNo ratings yet

- Física Básica II - René CondeDocument210 pagesFísica Básica II - René CondeYoselin Rodriguez C.100% (1)

- Motor Driver Board Tb6560-5axisDocument14 pagesMotor Driver Board Tb6560-5axisAli Asghar MuzzaffarNo ratings yet

- Fluid MechDocument2 pagesFluid MechJade Kristine CaleNo ratings yet

- Updated After 11th BoS Course Curriculum - B.tech CSEDocument120 pagesUpdated After 11th BoS Course Curriculum - B.tech CSEAnonymous 9etQKwWNo ratings yet

- LX Capacity Chart Hydrogen SCFM 10-2008 PDFDocument5 pagesLX Capacity Chart Hydrogen SCFM 10-2008 PDFZack AmerNo ratings yet

- Odisha Current Affairs 2019 by AffairsCloudDocument27 pagesOdisha Current Affairs 2019 by AffairsCloudTANVEER AHMEDNo ratings yet