Professional Documents

Culture Documents

SCAN Test: Each Portion of Integrated Circuit Is Tested Using ATPG Technique To Detect Intra

Uploaded by

humtum_shri5736Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

SCAN Test: Each Portion of Integrated Circuit Is Tested Using ATPG Technique To Detect Intra

Uploaded by

humtum_shri5736Copyright:

Available Formats

SCAN Test

The combinational network is easy to test ; just by applying test vector & observe output. In sequential network such thing is not sufficient ; here one should observe state of all flip-flops which is simplified by brute force approach in which sequential network is divided into combinational network ;but still it is not sufficient because it required much number of test vector ; which take much time for small design. One approach for sequential network would be to connect output of each flip-flops to next flip-flop which form shift register , then we could shift out the state of the flip-flops bit by bit using single serial pin of IC. which known as scan path testing. Each portion of integrated circuit is tested using ATPG technique to detect intraportion faults. But inter- portion faults are detected by SCAN test. In SCAN test there is scan chain containing:1. Memory elements in fan-in of the output of number of portion. 2. Memory elements in fan-out of the input of number of portion. 3. Memory elements connected to combinational logic propagating data input to the memory element. 4. Control signal. ATPG is most simple for combinational but much harder for sequential logic. So most common sequential structured test approach converts sequential logic to combinational logic. In full scan design we replace every sequential element with scan flip-flop. The result is an internal form of boundary scan & we can use IEEE1149.1 TAP to access an internal scan chain. In highly structured full scan allows test software to perform automatic scan insertion using scan design we can turn the output of each flip-flop into a pseudo primary input & input to each flipflop into pseudo primary output. ATPG software can then generate test vectors for the combinational logic between scan flip-flop .

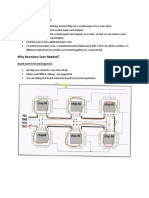

The following figure is showing scan path testing based on two state flip-flop. In the usual way, the sequential network separated into combinational part and state register composed of flip-flop.

In above circuit green path indicating test vector path via shift register. In normal mode (not scan mode) SE(scan enable) is active low; input are applied (1.6) & output (1..2) are generated when clock pulsed network goes to next state. In scan mode (test mode) :1. SE is active high. 2. By using test clock test vector passed via SDI(serial data input).

3. Then allow corresponding test values to input(16). 4. After sufficient time interval signal propagated through combination network then verify the output (1..2) . 5. Then make SE low and apply system clock to store new value( ) into flip-flop. 6. Scan out & verify Q(i) values by using clock; at same time new test vector is inserted via SDI. So generally in digital IC combinational & sequential circuit are separated & in order to scan test to IC , we need to replace flip-flop with two port flip-flop. Digital chip under test is shown below

When multiple ICs are mounted on a pc board ,it is possible to chain together the scan register in each IC so that the entire board can be tested using a single serial access point.

You might also like

- Generate Scan Chain and ATPG Patterns for DFTDocument2 pagesGenerate Scan Chain and ATPG Patterns for DFTMani KandanNo ratings yet

- Commerzbank. Frankfurt, Germany. Sir Norman Foster & PartnersDocument7 pagesCommerzbank. Frankfurt, Germany. Sir Norman Foster & PartnersRehana P NawassNo ratings yet

- Scan Chain: Scan Chain Is A Technique Used in DesignDocument7 pagesScan Chain: Scan Chain Is A Technique Used in DesignpraveenNo ratings yet

- Scan ChainsDocument3 pagesScan Chainsnehasoni100% (1)

- Tap ControllerDocument16 pagesTap ControllerMoin PashaNo ratings yet

- At-Speed Transition Fault Testing With Low Speed Scan EnableDocument6 pagesAt-Speed Transition Fault Testing With Low Speed Scan EnableSiva SreeramdasNo ratings yet

- Vlsi TV Lecture 10 BscanDocument37 pagesVlsi TV Lecture 10 BscanRana Babar AliNo ratings yet

- Hierarchical Scan and Atpg For Two Stage PDFDocument3 pagesHierarchical Scan and Atpg For Two Stage PDFNeusilica school of VLSINo ratings yet

- DRC OverviewDocument1 pageDRC OverviewIlaiyaveni IyanduraiNo ratings yet

- Week 3Document34 pagesWeek 3apoorvaNo ratings yet

- Scan InsertionDocument40 pagesScan InsertionAmena FarhatNo ratings yet

- DFT Tutorial PDFDocument5 pagesDFT Tutorial PDFVishwaNo ratings yet

- 15-Chapter 10 BSCAN 1500 PDFDocument81 pages15-Chapter 10 BSCAN 1500 PDFVeeranjaneyulu DhikondaNo ratings yet

- On The Detectability of Scan Chain Internal Faults - An Industrial Case StudyDocument6 pagesOn The Detectability of Scan Chain Internal Faults - An Industrial Case StudynagarjunaNo ratings yet

- Sns College of Technology: Department of Electronics & Communication EngineeringDocument24 pagesSns College of Technology: Department of Electronics & Communication EngineeringswamynathanNo ratings yet

- DFT Lbist PDFDocument10 pagesDFT Lbist PDFAman TyagiNo ratings yet

- An Introduction To Scan Test For Test Engineers: Part 1 of 2Document8 pagesAn Introduction To Scan Test For Test Engineers: Part 1 of 2Are VijayNo ratings yet

- Ramkumar PDFDocument5 pagesRamkumar PDFKiruthika MNo ratings yet

- Lab ReportDocument17 pagesLab ReportYashwanthKumarNo ratings yet

- Importent Document For DFT PDFDocument10 pagesImportent Document For DFT PDFBharathi MahadevacharNo ratings yet

- Tetramax DF DsDocument4 pagesTetramax DF DsBrijesh S DNo ratings yet

- Test PointsDocument21 pagesTest Pointsanusha killariNo ratings yet

- Assignment 1Document3 pagesAssignment 1dheeraj.d JainNo ratings yet

- Transition Delay Fault ATPG PDFDocument3 pagesTransition Delay Fault ATPG PDFanuNo ratings yet

- Paper-Loc and LosDocument5 pagesPaper-Loc and LosRUPIREDDY PRAVEENNo ratings yet

- Tessent Plltest User'S Manual: Software Version 2014.1 March 2014Document146 pagesTessent Plltest User'S Manual: Software Version 2014.1 March 2014Raghavendra MatturNo ratings yet

- Low-Power Design and Test, Lecture 8Document35 pagesLow-Power Design and Test, Lecture 8Mani KandanNo ratings yet

- L02 FaultModelingDocument15 pagesL02 FaultModelingAmit RohillaNo ratings yet

- Case12d ObservationDocument3 pagesCase12d ObservationsenthilkumarNo ratings yet

- DFT Insertion FlowDocument3 pagesDFT Insertion FlowamitwangooNo ratings yet

- At-Speed Test:: Improving Defect Detection For Nanometer DesignsDocument34 pagesAt-Speed Test:: Improving Defect Detection For Nanometer DesignsMotamarri AravindNo ratings yet

- LBIST - A Technique For Infield SafetyDocument4 pagesLBIST - A Technique For Infield Safetyrahul1990bhatiaNo ratings yet

- Cell AwareDocument21 pagesCell AwarekbkkrNo ratings yet

- Transition Delay Fault Testing Improved with Multiple Scan Enable SignalsDocument6 pagesTransition Delay Fault Testing Improved with Multiple Scan Enable Signalspravallika vysyarajuNo ratings yet

- Sample Vlsi ResumeDocument2 pagesSample Vlsi ResumePavan KumarNo ratings yet

- Automating P1500 Wrapper CreationDocument24 pagesAutomating P1500 Wrapper CreationKrish GokulNo ratings yet

- Streaming Scan NetworkDocument10 pagesStreaming Scan NetworkDeepak TiwariNo ratings yet

- Jtag BasicsDocument50 pagesJtag BasicsAkshay Kumar MNo ratings yet

- Syn_fifo design and code for synchronous FIFODocument5 pagesSyn_fifo design and code for synchronous FIFOVenky KoolchipNo ratings yet

- 10050-Sharing EDT Clock With Scan ClockDocument10 pages10050-Sharing EDT Clock With Scan ClockRathnambiga UnnikrishnanNo ratings yet

- Embedded Deterministic Test For Low-Cost Manufacturing: IEEE Design and Test of Computers October 2003Document10 pagesEmbedded Deterministic Test For Low-Cost Manufacturing: IEEE Design and Test of Computers October 2003pavithrNo ratings yet

- At-Speed Test Methods for LSSD and Mux Flip-Flop DesignsDocument5 pagesAt-Speed Test Methods for LSSD and Mux Flip-Flop DesignsAman TyagiNo ratings yet

- Lab1 DC Tmax 2012 1217 v1Document43 pagesLab1 DC Tmax 2012 1217 v1jasonturfNo ratings yet

- Testability - AssignmentDocument7 pagesTestability - Assignmentdwaraka.mn4926No ratings yet

- Scan Through TAPDocument10 pagesScan Through TAPajayg_lmgNo ratings yet

- Scan Insertion Lab ObservationsDocument3 pagesScan Insertion Lab ObservationssenthilkumarNo ratings yet

- IEEE P1687 Security Design Hides Instrument AccessDocument26 pagesIEEE P1687 Security Design Hides Instrument AccesssrikanthNo ratings yet

- Stuck at FaultDocument6 pagesStuck at Faultamy2chang_1No ratings yet

- DFT Scan Insertion: VLSI Testing and Design For TestabilityDocument19 pagesDFT Scan Insertion: VLSI Testing and Design For TestabilityHuzur AhmedNo ratings yet

- How To Use Embedded Instruments and IJTAG-JTAG An IEEE P1687 Tutorial PDFDocument10 pagesHow To Use Embedded Instruments and IJTAG-JTAG An IEEE P1687 Tutorial PDFAnjali TailorNo ratings yet

- Tetramax® Lab: Automatic Test Pattern Generation (Atpg) : Computer-Aided Vlsi System DesignDocument4 pagesTetramax® Lab: Automatic Test Pattern Generation (Atpg) : Computer-Aided Vlsi System Designkondalarao79No ratings yet

- CompressionDocument45 pagesCompressionRajesh DurisalaNo ratings yet

- VLSIGURU SCAN INSERTION LABDocument2 pagesVLSIGURU SCAN INSERTION LABsenthilkumarNo ratings yet

- Dftadvisor TutorialDocument36 pagesDftadvisor TutorialSrikiran DevarabhotlaNo ratings yet

- Logic BIST Case Studies and Real IssuesDocument10 pagesLogic BIST Case Studies and Real IssuesprakashthamankarNo ratings yet

- Jtag EXTEST OperationDocument2 pagesJtag EXTEST OperationsrikanthNo ratings yet

- Scan Insertion Lab ObservationsDocument2 pagesScan Insertion Lab ObservationssenthilkumarNo ratings yet

- EDT IMP QuestionsDocument1 pageEDT IMP QuestionsMayur MestryNo ratings yet

- Why Boundary Scan Needed?Document39 pagesWhy Boundary Scan Needed?srikanth100% (1)

- Serial Data Transmission Format DiagramDocument1 pageSerial Data Transmission Format Diagramhumtum_shri5736No ratings yet

- Dead LockDocument22 pagesDead Lockhumtum_shri5736No ratings yet

- ATM and Multimedia TrafficDocument10 pagesATM and Multimedia Traffichumtum_shri5736No ratings yet

- Context Switch Question AnswerDocument2 pagesContext Switch Question Answerhumtum_shri5736No ratings yet

- Assignment Number:-02 Name:-M.E. (VLSI & Embedded System) Roll No.:-, SEM:-I Sub: - Software Defined RadioDocument25 pagesAssignment Number:-02 Name:-M.E. (VLSI & Embedded System) Roll No.:-, SEM:-I Sub: - Software Defined Radiohumtum_shri5736No ratings yet

- Assignment No.1 Que-Explain in Detail With Flow Diagram Complete Extraction Flow in ASIC AnsDocument4 pagesAssignment No.1 Que-Explain in Detail With Flow Diagram Complete Extraction Flow in ASIC Anshumtum_shri5736No ratings yet

- Design ChecksDocument1 pageDesign Checkshumtum_shri5736No ratings yet

- Main Levels of Floor PlanningDocument3 pagesMain Levels of Floor Planninghumtum_shri5736No ratings yet

- Vlsi Lab ShripadDocument10 pagesVlsi Lab Shripadhumtum_shri5736No ratings yet

- Fault ModelDocument42 pagesFault ModelDamon SalvatoreNo ratings yet

- Q2Document3 pagesQ2humtum_shri5736No ratings yet

- Assignment Number:-02 Name:-M.E. (VLSI & Embedded System) Roll No.:-, SEM:-I Sub: - Software Defined RadioDocument25 pagesAssignment Number:-02 Name:-M.E. (VLSI & Embedded System) Roll No.:-, SEM:-I Sub: - Software Defined Radiohumtum_shri5736No ratings yet

- Memory CardDocument2 pagesMemory Cardhumtum_shri5736No ratings yet

- System PartitioningDocument3 pagesSystem Partitioninghumtum_shri5736No ratings yet

- Types of SimulationDocument3 pagesTypes of Simulationhumtum_shri573667% (3)

- Que: Explain With Block Diagram The Steps Involved in Post Layout Synthesis? Ans: SynthesisDocument4 pagesQue: Explain With Block Diagram The Steps Involved in Post Layout Synthesis? Ans: Synthesishumtum_shri5736No ratings yet

- Ece450 DspaDocument2 pagesEce450 Dspahumtum_shri5736No ratings yet

- IC Fabrication Process - How To Fabricate An Ic On A Silicon Chip and Its Diagrams?Document5 pagesIC Fabrication Process - How To Fabricate An Ic On A Silicon Chip and Its Diagrams?Tanvir Ahmad100% (3)

- High GainDocument1 pageHigh Gainhumtum_shriNo ratings yet

- ASIC Question PaperDocument1 pageASIC Question Paperhumtum_shri5736No ratings yet

- Synthe SizableDocument3 pagesSynthe Sizablehumtum_shri5736No ratings yet

- Basic - IIDocument17 pagesBasic - IIhumtum_shri5736No ratings yet

- High GainDocument1 pageHigh Gainhumtum_shriNo ratings yet

- CMOS IC Design Questions on Analog and Digital CircuitsDocument2 pagesCMOS IC Design Questions on Analog and Digital Circuitshumtum_shri5736No ratings yet

- ConflictDocument2 pagesConflicthumtum_shri5736No ratings yet

- MisDocument1 pageMishumtum_shri5736No ratings yet

- Spry 061Document8 pagesSpry 061Sinchu MithunNo ratings yet

- Stuck at FaultDocument6 pagesStuck at Faultamy2chang_1No ratings yet

- Psycho Yoga 12Document25 pagesPsycho Yoga 12merlin7magikNo ratings yet

- Design & Analysis of Mono Composite Leaf SpringDocument5 pagesDesign & Analysis of Mono Composite Leaf Springijsret100% (1)

- 2020 Agent Price ListDocument2,732 pages2020 Agent Price ListEngr XsadNo ratings yet

- Ap Art CrashcourseDocument19 pagesAp Art Crashcourseapi-298825724No ratings yet

- Mikhail Murashov: 2110 Applebrook Drive Commerce Township, MI 48382 (386) 569-8665 Personal Website: Mmurashov@adrian - EduDocument2 pagesMikhail Murashov: 2110 Applebrook Drive Commerce Township, MI 48382 (386) 569-8665 Personal Website: Mmurashov@adrian - Eduapi-242945986No ratings yet

- Numark Orbit - VirtualDJ 8 Operation GuideDocument13 pagesNumark Orbit - VirtualDJ 8 Operation GuideCasiLokoNo ratings yet

- 04 DM BLDG Glazed+Schedule V01+Document1 page04 DM BLDG Glazed+Schedule V01+Saahil KhaanNo ratings yet

- Quarter 1 Revision SheetsDocument7 pagesQuarter 1 Revision Sheetsghada kamalNo ratings yet

- Sap Master Data in Materials ManagementDocument13 pagesSap Master Data in Materials Managementedmondo77No ratings yet

- Kavindu Final.Document33 pagesKavindu Final.KavinduKarunarathnaNo ratings yet

- Object Relations Group PsychotherapyDocument6 pagesObject Relations Group PsychotherapyJonathon BenderNo ratings yet

- How To Write An EssayDocument4 pagesHow To Write An EssayShah BaibrassNo ratings yet

- Mcqs Pa OrignalDocument55 pagesMcqs Pa OrignalMuhammad Youneeb100% (1)

- FGD on Preparing Learning Materials at Old Cabalan Integrated SchoolDocument3 pagesFGD on Preparing Learning Materials at Old Cabalan Integrated SchoolRAQUEL TORRESNo ratings yet

- Dark Mode Log0Document2 pagesDark Mode Log0picochulo2381No ratings yet

- Book ReviewDocument1 pageBook ReviewBaidaNo ratings yet

- Introduction of MechatronicsDocument23 pagesIntroduction of MechatronicsSathish SatNo ratings yet

- Deutsche Bank Human Resources Report 2017Document57 pagesDeutsche Bank Human Resources Report 2017YamNo ratings yet

- Is It Worth Dropping One More Year For GATE - QuoraDocument6 pagesIs It Worth Dropping One More Year For GATE - QuoraRaJu SinGhNo ratings yet

- Aneka Cloud IntroductionDocument36 pagesAneka Cloud IntroductionPradeep Kumar Reddy ReddyNo ratings yet

- 3rd BeatitudeDocument18 pages3rd BeatitudeDonna ANo ratings yet

- Business Culture BriefingDocument9 pagesBusiness Culture BriefingSonia CamposNo ratings yet

- Assignment # 02: (Bearing Capacity Analysis)Document3 pagesAssignment # 02: (Bearing Capacity Analysis)kKhalid YousafNo ratings yet

- Chapter 07 4th Ed Gender&AgeDocument18 pagesChapter 07 4th Ed Gender&AgeCahaya Santi SianturiNo ratings yet

- Benefits of Audio-Visual Aids and Visual Learning Highlighted in ResearchDocument6 pagesBenefits of Audio-Visual Aids and Visual Learning Highlighted in ResearchAngelo Joshua FajamolinNo ratings yet

- Spitler McQuiston Lindsey 93 2Document11 pagesSpitler McQuiston Lindsey 93 2Shafawati ShahneelNo ratings yet

- Manpower MonitoringDocument6 pagesManpower MonitoringZandoval VillasiNo ratings yet

- ACS SCPI Programming Guide V1 0Document29 pagesACS SCPI Programming Guide V1 0Pedro Boanerges Paz RomeroNo ratings yet