Professional Documents

Culture Documents

74HC HCT193

Uploaded by

kjfenOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

74HC HCT193

Uploaded by

kjfenCopyright:

Available Formats

74HC193; 74HCT193

Presettable synchronous 4-bit binary up/down counter

Rev. 4 24 June 2013 Product data sheet

1. General description

The 74HC193; 74HCT193 is a 4-bit synchronous binary up/down counter. Separate up/down clocks, CPU and CPD respectively, simplify operation. The outputs change state synchronously with the LOW-to-HIGH transition of either clock input. If the CPU clock is pulsed while CPD is held HIGH, the device will count up. If the CPD clock is pulsed while CPU is held HIGH, the device will count down. Only one clock input can be held HIGH at any time to guarantee predictable behaviour. The device can be cleared at any time by the asynchronous master reset input (MR); it may also be loaded in parallel by activating the asynchronous parallel load input (PL). The terminal count up (TCU) and terminal count down (TCD) outputs are normally HIGH. When the circuit has reached the maximum count state of 15, the next HIGH-to-LOW transition of CPU will cause TCU to go LOW. TCU will stay LOW until CPU goes HIGH again, duplicating the count up clock. Likewise, the TCD output will go LOW when the circuit is in the zero state and the CPD goes LOW. The terminal count outputs can be used as the clock input signals to the next higher order circuit in a multistage counter, since they duplicate the clock waveforms. Multistage counters will not be fully synchronous, since there is a slight delay time difference added for each stage that is added. The counter may be preset by the asynchronous parallel load capability of the circuit. Information present on the parallel data inputs (D0 to D3) is loaded into the counter and appears on the outputs (Q0 to Q3) regardless of the conditions of the clock inputs when the parallel load (PL) input is LOW. A HIGH level on the master reset (MR) input will disable the parallel load gates, override both clock inputs and set all outputs (Q0 to Q3) LOW. If one of the clock inputs is LOW during and after a reset or load operation, the next LOW-to-HIGH transition of that clock will be interpreted as a legitimate signal and will be counted. Inputs include clamp diodes. This enables the use of current limiting resistors to interface inputs to voltages in excess of VCC.

2. Features and benefits

Input levels: For 74HC193: CMOS level For 74HCT193: TTL level Synchronous reversible 4-bit binary counting Asynchronous parallel load Asynchronous reset Expandable without external logic Complies with JEDEC standard no. 7A ESD protection: HBM JESD22-A114F exceeds 2000 V MM JESD22-A115-A exceeds 200 V.

NXP Semiconductors

74HC193; 74HCT193

Presettable synchronous 4-bit binary up/down counter

Multiple package options Specified from 40 C to +85 C and 40 C to +125 C.

3. Ordering information

Table 1. Ordering information Package Temperature range 74HC193D 74HC193DB 74HC193N 74HC193PW 74HCT193D 74HCT193DB 74HCT193N 74HCT193PW 40 C to +125 C 40 C to +125 C 40 C to +125 C 40 C to +125 C 40 C to +125 C 40 C to +125 C 40 C to +125 C 40 C to +125 C Name SO16 SSOP16 DIP16 TSSOP16 SO16 SSOP16 DIP16 TSSOP16 Description plastic small outline package; 16 leads; body width 3.9 mm plastic shrink small outline package; 16 leads; body width 5.3 mm plastic dual in-line package; 16 leads (300 mil) plastic thin shrink small outline package; 16 leads; body width 4.4 mm plastic small outline package; 16 leads; body width 3.9 mm plastic shrink small outline package; 16 leads; body width 5.3 mm plastic dual in-line package; 16 leads (300 mil) plastic thin shrink small outline package; 16 leads; body width 4.4 mm Version SOT109-1 SOT338-1 SOT38-4 SOT403-1 SOT109-1 SOT338-1 SOT38-4 SOT403-1 Type number

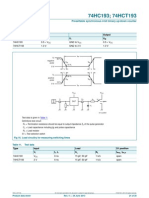

4. Functional diagram

15 D0 1 D1 10 D2 9 D3 TCU COUNTER TCD 12 13 CPU 14 MR FLIP-FLOPS Q0 3 2 Q1 6 Q2 7 Q3

001aag405

11 5 4

PL CPU CPD

PL 11 5 4 14 MR

D0 15

D1 1

D2 10

D3 9 12 13 TCU TCD

CPD

3 Q0

2 Q1

6 Q2

7 Q3

001aag409

Fig 1. Functional diagram

Fig 2. Logic symbol

74HC_HCT193

All information provided in this document is subject to legal disclaimers.

NXP B.V. 2013. All rights reserved.

Product data sheet

Rev. 4 24 June 2013

2 of 30

You might also like

- Water Treatments: Steam Water Cycle TreatmentDocument2 pagesWater Treatments: Steam Water Cycle TreatmentkjfenNo ratings yet

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenNo ratings yet

- Temperature Monitoring: FaizanDocument5 pagesTemperature Monitoring: FaizankjfenNo ratings yet

- Degree of Electrifi Cation Peak Load of One Household (KW) Portion of Peak Load Per Household P (KW) Degree of Simultaneous Usage G RemarksDocument10 pagesDegree of Electrifi Cation Peak Load of One Household (KW) Portion of Peak Load Per Household P (KW) Degree of Simultaneous Usage G RemarkskjfenNo ratings yet

- Selo 1Document26 pagesSelo 1kjfenNo ratings yet

- 74HC193 74HCT193: 17. Contact InformationDocument2 pages74HC193 74HCT193: 17. Contact InformationkjfenNo ratings yet

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenNo ratings yet

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenNo ratings yet

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenNo ratings yet

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenNo ratings yet

- 74HC193 74HCT193: 5. Pinning InformationDocument2 pages74HC193 74HCT193: 5. Pinning InformationkjfenNo ratings yet

- 74HC193 74HCT193: 10. Dynamic CharacteristicsDocument2 pages74HC193 74HCT193: 10. Dynamic CharacteristicskjfenNo ratings yet

- 74HC193 74HCT193: 14. AbbreviationsDocument2 pages74HC193 74HCT193: 14. AbbreviationskjfenNo ratings yet

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenNo ratings yet

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenNo ratings yet

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenNo ratings yet

- 74HC193 74HCT193: 13. Package OutlineDocument2 pages74HC193 74HCT193: 13. Package OutlinekjfenNo ratings yet

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenNo ratings yet

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenNo ratings yet

- 74HC193 74HCT193: 9. Static CharacteristicsDocument2 pages74HC193 74HCT193: 9. Static CharacteristicskjfenNo ratings yet

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenNo ratings yet

- Physical Dimensions: 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Package Number N14ADocument1 pagePhysical Dimensions: 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Package Number N14AkjfenNo ratings yet

- Function Tables Logic Diagram: BCD Count Sequence (Note 1) Outputs Q Q Q QDocument1 pageFunction Tables Logic Diagram: BCD Count Sequence (Note 1) Outputs Q Q Q QkjfenNo ratings yet

- Ac Switching Characteristics: 5vandtDocument1 pageAc Switching Characteristics: 5vandtkjfenNo ratings yet

- 44 A Practical Guide To Geomantic Divination 45 The Presiding GeniusDocument1 page44 A Practical Guide To Geomantic Divination 45 The Presiding GeniuskjfenNo ratings yet

- Absolute Maximum Ratings: Symbol Parameter Min Nom Max UnitsDocument1 pageAbsolute Maximum Ratings: Symbol Parameter Min Nom Max UnitskjfenNo ratings yet

- Geomantic AstrologyDocument1 pageGeomantic AstrologykjfenNo ratings yet

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5795)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Oracle Fusion Middleware 11g Build Applications With Adf IIDocument4 pagesOracle Fusion Middleware 11g Build Applications With Adf IIMohamedNo ratings yet

- Project Report On YONO SBI (Anirban Dutta)Document49 pagesProject Report On YONO SBI (Anirban Dutta)Music & Art88% (16)

- A Short Note On Transaction in Database Management SystemDocument4 pagesA Short Note On Transaction in Database Management SystemImran KabirNo ratings yet

- Sample Cover Letter Job Application Human ResourcesDocument9 pagesSample Cover Letter Job Application Human Resourcesrqaeibifg100% (1)

- Process Flow Diagram of Procurement:: ProductionDocument2 pagesProcess Flow Diagram of Procurement:: ProductionShah AlamNo ratings yet

- Mathematical Model For Cold Rolling and Temper Rolling Process of Thin Steel StripDocument7 pagesMathematical Model For Cold Rolling and Temper Rolling Process of Thin Steel StripRhushikeshNo ratings yet

- Input Output ModelsDocument4 pagesInput Output ModelsMaheen KhanNo ratings yet

- 07smspa cmENaDocument88 pages07smspa cmENamaheshNo ratings yet

- Mech-Intro 14.0 WS03.1 2DGearsDocument17 pagesMech-Intro 14.0 WS03.1 2DGearsSilva Junior, E. J.No ratings yet

- Oracle HCM Cloud Whats New For R8Document195 pagesOracle HCM Cloud Whats New For R8KishorKongaraNo ratings yet

- Format of Lab ReportDocument3 pagesFormat of Lab ReportNirbhayNo ratings yet

- Statistics Made Easy Presentation PDFDocument226 pagesStatistics Made Easy Presentation PDFAbhi ThakkarNo ratings yet

- Top 30 Companies in India (Sectorwise) - 23.4.2012Document34 pagesTop 30 Companies in India (Sectorwise) - 23.4.2012Gogol SarinNo ratings yet

- 1 N 52 XXBDocument2 pages1 N 52 XXB81968No ratings yet

- Ophthalmic and Physiological Optics Volume 36 Issue 2 2016 (Doi 10.1111/opo.12275) Tauste, Ana Ronda, Elena Molina, María-José Seguí, Mar - Effect of Contact Lens Use On Computer Vision SyndromeDocument8 pagesOphthalmic and Physiological Optics Volume 36 Issue 2 2016 (Doi 10.1111/opo.12275) Tauste, Ana Ronda, Elena Molina, María-José Seguí, Mar - Effect of Contact Lens Use On Computer Vision SyndromeAdhe WagiNo ratings yet

- Sparc Fjm12Document35 pagesSparc Fjm12Jose HernandezNo ratings yet

- Chatgpt For Beginners Features Foundations and Applications 1St Edition Eric Sarrion Full Chapter PDF ScribdDocument67 pagesChatgpt For Beginners Features Foundations and Applications 1St Edition Eric Sarrion Full Chapter PDF Scribdearl.santacruz576100% (4)

- Cs0207 Computer Organization and Architecture 2013Document4 pagesCs0207 Computer Organization and Architecture 2013Sharath Kumar KRNo ratings yet

- Users GuideDocument220 pagesUsers GuideRicardo PequenoNo ratings yet

- Qatar Chamber of Commerce Magazine 3rd EditionDocument42 pagesQatar Chamber of Commerce Magazine 3rd Editionthiwa karanNo ratings yet

- Collatz Conjecture ProofDocument6 pagesCollatz Conjecture ProofThiago da Silva VieiraNo ratings yet

- Oracle HCM Cloud OverviewDocument35 pagesOracle HCM Cloud OverviewAngelVillalobosNo ratings yet

- Lenovo Ideapad s10-2 (Kiun0, La-5071p)Document40 pagesLenovo Ideapad s10-2 (Kiun0, La-5071p)rasrozi5170No ratings yet

- CSC263 Spring 2011 Assignment 2 SolutionsDocument4 pagesCSC263 Spring 2011 Assignment 2 SolutionsyellowmoogNo ratings yet

- A53tp50d crdmh1Document234 pagesA53tp50d crdmh1LOUKILkarimNo ratings yet

- Nokia Airscale Wi-Fi Module Ac210M, Release 17ADocument26 pagesNokia Airscale Wi-Fi Module Ac210M, Release 17Aprashant gauravNo ratings yet

- L Edit TutorialDocument25 pagesL Edit TutorialHiren J VasavaNo ratings yet

- HP Mouse TestDocument8 pagesHP Mouse Testradiophon666No ratings yet

- De Thi Thu Tuyen Sinh Vao Lop 10 Mon Tieng Anh Huyen Lang Giang Bac Giang Nam Hoc 2015 2016Document3 pagesDe Thi Thu Tuyen Sinh Vao Lop 10 Mon Tieng Anh Huyen Lang Giang Bac Giang Nam Hoc 2015 2016Ngọc BíchNo ratings yet

- Magic Cube enDocument2 pagesMagic Cube enCoreyNo ratings yet