Professional Documents

Culture Documents

74HC HCT193

Uploaded by

kjfenOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

74HC HCT193

Uploaded by

kjfenCopyright:

Available Formats

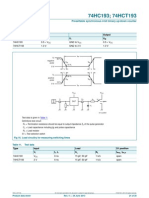

NXP Semiconductors

74HC193; 74HCT193

Presettable synchronous 4-bit binary up/down counter

10. Dynamic characteristics

Table 8. Symbol tpd Dynamic characteristics type 74HC193 Parameter propagation delay Conditions Min CPU, CPD to Qn; see Figure 9 VCC = 2.0 V VCC = 4.5 V VCC = 6.0 V CPU to TCU; see Figure 10 VCC = 2.0 V VCC = 4.5 V VCC = 6.0 V CPD to TCD; see Figure 10 VCC = 2.0 V VCC = 4.5 V VCC = 6.0 V PL to Qn; see Figure 11 VCC = 2.0 V VCC = 4.5 V VCC = 6.0 V MR to Qn; see Figure 12 VCC = 2.0 V VCC = 4.5 V VCC = 6.0 V Dn to Qn; see Figure 11 VCC = 2.0 V VCC = 4.5 V VCC = 6.0 V PL to TCU, PL to TCD; see Figure 14 VCC = 2.0 V VCC = 4.5 V VCC = 6.0 V MR to TCU, MR to TCD; see Figure 14 VCC = 2.0 V VCC = 4.5 V VCC = 6.0 V

74HC_HCT193

25 C Typ Max

[1]

40 C to +85 C 40 C to +125 C Unit Min Max Min Max

63 23 18 215 43 37 270 54 46 325 65 55 ns ns ns

39 14 11

125 25 21

155 31 26

190 38 32

ns ns ns

39 14 11

125 25 21

155 31 26

190 38 32

ns ns ns

69 25 20

220 44 37

275 55 47

330 66 56

ns ns ns

58 21 17

200 40 34

250 50 43

300 60 51

ns ns ns

69 25 20

210 42 36

265 53 45

315 63 54

ns ns ns

80 29 23

290 58 49

365 73 62

435 87 74

ns ns ns

74 27 22

285 57 48

355 71 60

430 86 73

ns ns ns

All information provided in this document is subject to legal disclaimers.

NXP B.V. 2013. All rights reserved.

Product data sheet

Rev. 4 24 June 2013

13 of 30

NXP Semiconductors

74HC193; 74HCT193

Presettable synchronous 4-bit binary up/down counter

Table 8. Symbol tpd

Dynamic characteristics type 74HC193 continued Parameter propagation delay Conditions Min Dn to TCU, Dn to TCD; see Figure 14 VCC = 2.0 V VCC = 4.5 V VCC = 6.0 V 80 29 23 19 7 6 19 7 6 290 58 49 75 15 13 75 15 13 365 73 62 95 19 16 95 19 16 435 87 74 110 22 19 110 22 19 ns ns ns ns ns ns ns ns ns 25 C Typ Max 40 C to +85 C 40 C to +125 C Unit Min Max Min Max

tTHL

HIGH to LOW see Figure 12 output transition VCC = 2.0 V time VCC = 4.5 V VCC = 6.0 V LOW to HIGH see Figure 12 output transition VCC = 2.0 V time VCC = 4.5 V VCC = 6.0 V pulse width CPU, CPD (HIGH or LOW); see Figure 9 VCC = 2.0 V VCC = 4.5 V VCC = 6.0 V MR (HIGH); see Figure 12 VCC = 2.0 V VCC = 4.5 V VCC = 6.0 V PL (LOW); see Figure 11 VCC = 2.0 V VCC = 4.5 V VCC = 6.0 V

tTLH

tW

100 20 17

22 8 6

125 25 21

150 30 26

ns ns ns

100 20 17

25 9 7

125 25 21

150 30 26

ns ns ns

100 20 17

19 7 6

125 25 21

150 30 26

ns ns ns

trec

recovery time

PL to CPU, CPD; see Figure 11 VCC = 2.0 V VCC = 4.5 V VCC = 6.0 V MR to CPU, CPD; see Figure 12 VCC = 2.0 V VCC = 4.5 V VCC = 6.0 V 50 10 9 0 0 0 65 13 11 75 15 13 ns ns ns 50 10 9 8 3 2 65 13 11 75 15 13 ns ns ns

74HC_HCT193

All information provided in this document is subject to legal disclaimers.

NXP B.V. 2013. All rights reserved.

Product data sheet

Rev. 4 24 June 2013

14 of 30

You might also like

- Modern Control of DC-Based Power Systems: A Problem-Based ApproachFrom EverandModern Control of DC-Based Power Systems: A Problem-Based ApproachNo ratings yet

- VSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsFrom EverandVSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsNo ratings yet

- Model Predictive Control for Doubly-Fed Induction Generators and Three-Phase Power ConvertersFrom EverandModel Predictive Control for Doubly-Fed Induction Generators and Three-Phase Power ConvertersNo ratings yet

- 74HC04 74HCT04: 1. General DescriptionDocument18 pages74HC04 74HCT04: 1. General DescriptionDistribuidorIBoolPedregalDeSantoDomingoNo ratings yet

- 74HC4520Document8 pages74HC4520pnlinh28No ratings yet

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenNo ratings yet

- 74HC14 74HCT14: 1. General DescriptionDocument21 pages74HC14 74HCT14: 1. General DescriptionDao Nguyen Trong TinNo ratings yet

- 74HC4040 12 Stage Binary Ripple CounterDocument8 pages74HC4040 12 Stage Binary Ripple CounterPablo RosasNo ratings yet

- 74 HC 73Document7 pages74 HC 73Jorge Alberto100% (1)

- 74HC08 74HCT08: 1. General DescriptionDocument15 pages74HC08 74HCT08: 1. General DescriptionFlavio KwiecinskiNo ratings yet

- General Description: Quad Bistable Transparant LatchDocument20 pagesGeneral Description: Quad Bistable Transparant LatchCesar VilledaNo ratings yet

- 74HC4020 74HCT4020: 1. General DescriptionDocument20 pages74HC4020 74HCT4020: 1. General DescriptionaboalfotohNo ratings yet

- 74HC02 74HCT02: 1. General DescriptionDocument15 pages74HC02 74HCT02: 1. General DescriptionAnonymous xTGQYFrNo ratings yet

- Integrated Circuits Data Sheet for 74HC/HCT125 Quad BufferDocument6 pagesIntegrated Circuits Data Sheet for 74HC/HCT125 Quad BufferAndes IndrayantoNo ratings yet

- 74HC273 74HCT273: 1. General DescriptionDocument20 pages74HC273 74HCT273: 1. General DescriptionAsif ShahNo ratings yet

- 74HC132 74HCT132: 1. General DescriptionDocument19 pages74HC132 74HCT132: 1. General DescriptionAnonymous xTGQYFrNo ratings yet

- 74hc126 74hct126Document6 pages74hc126 74hct126shatruddha123No ratings yet

- 74HC190Document13 pages74HC190Enzo Paolo D'Angelo0% (1)

- 74HC190 DatasheetDocument14 pages74HC190 Datasheetmym786No ratings yet

- 74HC74 74HCT74: 1. General DescriptionDocument21 pages74HC74 74HCT74: 1. General DescriptionGermán BergerNo ratings yet

- 74HC00 74HCT00: 1. General DescriptionDocument16 pages74HC00 74HCT00: 1. General DescriptionvanlongsportNo ratings yet

- 74HC4040 74HCT4040: 1. General DescriptionDocument24 pages74HC4040 74HCT4040: 1. General Descriptiontt884211No ratings yet

- Integrated Circuits Data Sheet - Hex Inverting Schmitt TriggerDocument8 pagesIntegrated Circuits Data Sheet - Hex Inverting Schmitt Triggerdragon-red0816No ratings yet

- Integrated Circuits Data Sheet - 74HC/HCT574 Octal D-Type Flip-FlopDocument8 pagesIntegrated Circuits Data Sheet - 74HC/HCT574 Octal D-Type Flip-Flopthinh040No ratings yet

- 74HC HCT365 CNV 2Document8 pages74HC HCT365 CNV 2Mini Veiga AlbánNo ratings yet

- General Description: Quad Buffer/line Driver 3-StateDocument15 pagesGeneral Description: Quad Buffer/line Driver 3-Statesinner86No ratings yet

- 74HC10-Q100 74HCT10-Q100: 1. General DescriptionDocument13 pages74HC10-Q100 74HCT10-Q100: 1. General DescriptionNelson RodriguezNo ratings yet

- 74HC4040 74HCT4040: 1. General DescriptionDocument20 pages74HC4040 74HCT4040: 1. General DescriptionWilliamNo ratings yet

- 74HC4017 74HCT4017: 1. General DescriptionDocument24 pages74HC4017 74HCT4017: 1. General DescriptionIvan BabicNo ratings yet

- 74HC4543Document12 pages74HC4543Anung PriyantoNo ratings yet

- 74HC4094Document11 pages74HC4094Gustavo BarcasnegrasNo ratings yet

- 74HC32-Q100 74HCT32-Q100: 1. General DescriptionDocument16 pages74HC32-Q100 74HCT32-Q100: 1. General Descriptiongotcha75No ratings yet

- Integrated Circuits Data Sheet: 8-bit Parallel-In/Serial-Out Shift RegisterDocument11 pagesIntegrated Circuits Data Sheet: 8-bit Parallel-In/Serial-Out Shift RegisterNegru P. PlantatieNo ratings yet

- 74HCT4060Document12 pages74HCT4060shamshim2000No ratings yet

- 74 HC 4060Document13 pages74 HC 4060anyenkts2No ratings yet

- 74HC03 74HCT03: 1. General DescriptionDocument16 pages74HC03 74HCT03: 1. General DescriptionDistribuidorIBoolPedregalDeSantoDomingoNo ratings yet

- 74HC02 74HCT02: 1. General DescriptionDocument16 pages74HC02 74HCT02: 1. General DescriptionCesar VilledaNo ratings yet

- 74 Ls 244Document16 pages74 Ls 244Abednego TariganNo ratings yet

- HEF4013B: 1. General DescriptionDocument15 pagesHEF4013B: 1. General DescriptionMuhammad Iqbal RasyidiNo ratings yet

- 74HCT75 PDFDocument7 pages74HCT75 PDFDeni KhanNo ratings yet

- 7473Document8 pages7473Merényi OszkárNo ratings yet

- mc14518bcp en PDFDocument8 pagesmc14518bcp en PDFdellcoNo ratings yet

- 74 HC 4067Document15 pages74 HC 4067김경원No ratings yet

- 74HC573Document21 pages74HC573ric_napigkitNo ratings yet

- 47HC00 NandDocument17 pages47HC00 NandWilliams Paredes CNo ratings yet

- Hex Inverters: Features DescriptionDocument22 pagesHex Inverters: Features DescriptionJoseph BernardNo ratings yet

- 8 Bit Shift Register With Output Latches (3 State) : Order CodesDocument16 pages8 Bit Shift Register With Output Latches (3 State) : Order CodesQuyet Pham DangNo ratings yet

- 78 hct14Document16 pages78 hct14Bruno AlvesNo ratings yet

- 74HC175 74HCT175: 1. General DescriptionDocument19 pages74HC175 74HCT175: 1. General DescriptionJulio CésarNo ratings yet

- CD 74 HC 194Document18 pagesCD 74 HC 194rrebollarNo ratings yet

- 74HC244 74HCT244: 1. General DescriptionDocument18 pages74HC244 74HCT244: 1. General DescriptionCesar VilledaNo ratings yet

- 74HC08 74HCT08: 1. General DescriptionDocument16 pages74HC08 74HCT08: 1. General DescriptionCesar VilledaNo ratings yet

- C.I 74HC365Document7 pagesC.I 74HC365DOMINGOS ALADIRNo ratings yet

- Datasheet Pc74hc123Document18 pagesDatasheet Pc74hc123Diego HenriqueNo ratings yet

- SN54HC573A, SN74HC573A Octal Transparent D-Type Latches With 3-State OutputsDocument7 pagesSN54HC573A, SN74HC573A Octal Transparent D-Type Latches With 3-State OutputsMadhukar PuliNo ratings yet

- 74ahc Ahct1g14Document15 pages74ahc Ahct1g14Ignacio ScalisiNo ratings yet

- 74 HC 93Document7 pages74 HC 93Brzata PticaNo ratings yet

- 74 HC 191Document10 pages74 HC 191Ravi RathodNo ratings yet

- Selo 1Document26 pagesSelo 1kjfenNo ratings yet

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenNo ratings yet

- 7SA522 CatalogueDocument53 pages7SA522 CataloguePhilip D'cruzNo ratings yet

- Water Treatments: Steam Water Cycle TreatmentDocument2 pagesWater Treatments: Steam Water Cycle TreatmentkjfenNo ratings yet

- 74HC193 74HCT193: 17. Contact InformationDocument2 pages74HC193 74HCT193: 17. Contact InformationkjfenNo ratings yet

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenNo ratings yet

- 7 Ways Signal Noise Can Impact Your Electrical EquipmentDocument5 pages7 Ways Signal Noise Can Impact Your Electrical EquipmentkjfenNo ratings yet

- Temperature Monitoring: FaizanDocument5 pagesTemperature Monitoring: FaizankjfenNo ratings yet

- REG670Document88 pagesREG670Rafael Hoffmann PaludoNo ratings yet

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenNo ratings yet

- Load Forecasting and Standardized Load CurvesDocument10 pagesLoad Forecasting and Standardized Load CurveskjfenNo ratings yet

- 74HC193 74HCT193: 14. AbbreviationsDocument2 pages74HC193 74HCT193: 14. AbbreviationskjfenNo ratings yet

- Sub 131Document10 pagesSub 131kjfenNo ratings yet

- 555 Timer Tutorial - How to Build CircuitsDocument1 page555 Timer Tutorial - How to Build CircuitskjfenNo ratings yet

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenNo ratings yet

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenNo ratings yet

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenNo ratings yet

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenNo ratings yet

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenNo ratings yet

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenNo ratings yet

- 74HC193 74HCT193: 13. Package OutlineDocument2 pages74HC193 74HCT193: 13. Package OutlinekjfenNo ratings yet

- 74HC HCT193Document2 pages74HC HCT193kjfenNo ratings yet

- 74HC193 74HCT193: 10. Dynamic CharacteristicsDocument2 pages74HC193 74HCT193: 10. Dynamic CharacteristicskjfenNo ratings yet

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenNo ratings yet

- 74HC193 74HCT193: 9. Static CharacteristicsDocument2 pages74HC193 74HCT193: 9. Static CharacteristicskjfenNo ratings yet

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenNo ratings yet

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenNo ratings yet

- 74HC193 74HCT193: 5. Pinning InformationDocument2 pages74HC193 74HCT193: 5. Pinning InformationkjfenNo ratings yet