Professional Documents

Culture Documents

Wide Range Soft Switching PWM Three-Level DC-DC Converters Suitable For Industrial Applications

Uploaded by

strngr06Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Wide Range Soft Switching PWM Three-Level DC-DC Converters Suitable For Industrial Applications

Uploaded by

strngr06Copyright:

Available Formats

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 29, NO.

2, FEBRUARY 2014

603

Wide Range Soft Switching PWM Three-Level DCDC Converters Suitable for Industrial Applications

Yong Shi and Xu Yang, Member, IEEE

AbstractThis paper discusses wide range soft switching solutions to a pulse width modulation (PWM) three-level (TL) dcdc converter suitable for industrial applications, and proposes four kinds of new PWM TL dcdc converters. The presented topologies have the following desirable features: all switches in each circuit sustain only half of the input voltage; off state voltage of the switches is directly clamped by the input capacitors and no added primary clamping devices, such as clamping diodes, ying capacitors, are required; and phase shifted control method can be used to achieve wide output range. The leading switches in the converters can only realize zero-voltage switching (ZVS), while the lagging switches can obtain ZVS or zero-current switching in different converters. Principle of operation and theoretical analysis are discussed. Experimental results are included to verify the feasibility and advantages of the new topologies. Index TermsIndustrial application, three-level (TL) dcdc converter, zero-current switching (ZCS), zero-voltage switching (ZVS).

I. INTRODUCTION EW topology for high input voltage dcdc power conversion is a hot researching issue in power electronics because of much existing or potential demand, i.e., the second stage dcdc converter after the 3 power factor correction (PFC) circuit, dcdc converters for micro grid, renewable energy, and distributed power system [1][4]. Commonly, the input voltage of these dcdc converters may be 800 V or higher to achieve better system performance [1]. Although, 1700 V or higher voltage rating commercial IGBTs are available, their performances under high frequency operation are worse than 1200 V or 600 V IGBTs. Therefore, it is still a hard job to select appropriate power modules for high input voltage dcdc converter [5][7]. In 1992, a novel PWM TL dcdc converter was rst proposed to lower the voltage stress applied on the switches [5]. In the paper [8], a family of PWM TL dcdc converters were proposed and comprehensive comparison was made. The authors in [9] proposed a zero-voltage and zero-current switching (ZVZCS) TL dcdc converter, wherein a ying capacitor is added to assist ZVS for the leading switches and an auxiliary circuit in

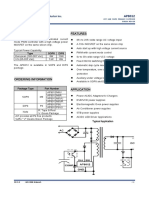

Fig. 1. Primary circuits of PWM dcdc converters. (a) Converter in paper [6]. (b) Diode clamped ZVS TL converter. (c) Two-level PS FB converter.

Manuscript received December 16, 2012; revised February 20, 2013; accepted April 7, 2013. Date of current version August 20, 2013. Recommended for publication by Associate Editor P. Barbosa. Y. Shi is with Xian Action Power Electrical Company, Ltd., Xian 710119, China (e-mail: shi.yong@cnaction.com). X. Yang is with the School of Electrical Engineering, Xian Jiaotong University, Xian 710049, China (e-mail: yangxu@mail.xjtu.edu.cn). Digital Object Identier 10.1109/TPEL.2013.2258357

the secondary is utilized to reset the primary current during the freewheeling stage to achieve ZCS for the lagging switches. The soft switching PWM technique for the PWM TL dcdc converters was systematically discussed in [10], and nine modulation strategies were presented. And then, many other good research works have been published on the topics of new topology, soft switching technique, and controlling strategy [11][29]. All the studies mentioned above have made the TL dcdc converter more usable. For a topology widely used in industrial application, following good features should be tted: 1) simple and compact power circuit; 2) easy controlling; 3) safe and reliable operation especially for the power electronics devices; 4) good performance. In the paper [6], a new PWM TL dcdc converter was proposed, which features Vin /2 on each switch, capacitive turn-off, and zero-voltage turned on. Fig. 1 shows the primary circuits of the converter in [6], diode clamped ZVS TL dcdc converter, and two-level FB dcdc converter. As shown in Fig. 1(a), only one more wire between the midpoint of the input capacitors and switching pairs is required to fabricate TL structure. Thus,

0885-8993 2013 IEEE

604

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 29, NO. 2, FEBRUARY 2014

compared with diode clamped ZVS TL dcdc converter, the converter in [6] has simpler and more compact structure with the same output performance, and this is the most attractive feature for an industrial application. As illustrated in [6], with PS switching scheme, off state voltage of the switches is directly clamped by the bulky input capacitors in each operation stage. So, the voltage stress of the four switches during the operation can be safely sustained. Furthermore, compared to other clamping devices, the bulky input capacitors can absorb more resonant energy stored in the parasitic inductances, which means the active switches can be kept in the safe operating area (SOA) even under fast dynamic transition instant. At last, the removed clamping devices can reduce the total BOM cost. The structure comparison between converter in [6] and traditional two-level FB dcdc converter is depicted in Fig. 1(a) and (c). Both of the converters have the simple and compact structure. But, off state voltage of the switches in Fig. 1(a) is only half of input voltage, which means 500600 V MOSFETs or IGBTs can be used in 500800 V dc input voltage applications to improve the total power density and achieve better overall system performance. As the aforementioned reasons, the converter in [6] is a more suitable topology for industrial applications compared to its competitors in either high or medium input voltage dcdc power conversion. However, it is also pointed out in [6] that the soft switching characteristic for the lagging switches is worse than the leading switches especially under small load current condition. Therefore, it is still an interesting and valuable task to nd wide range soft switching solutions to this converter. In this paper, a systematical discussion about wide range soft switching solutions to the converter in [6] is provided, and four kinds of novel topologies are proposed. The presented topologies have the following common attractive features: all switches in the circuit sustain only half of the input voltage; off state voltage of the switches is directly clamped by input capacitors and no added primary clamping devices, such as clamping diodes and ying capacitors, are required; and PS control method can be utilized to achieve wide output range. The leading switches in each converter can only realize ZVS, while the lagging switches can achieve ZVS or ZCS in different converters.

Fig. 2. La .

Current comparison of magnetizing inductor L m and CAC inductor

II. WIDE RANGE SOFT SWITCHING PWM TL CONVERTERS With PS modulation switching scheme, the four switches in Fig. 1(a) can be divided into two complementary switching pairs, i.e., S1 ,S2 , and S3 ,S4 . The output voltage is regulated by shifting the phase angle between the switching pairs. According to different switching patterns, the switches in each switching pair can be treated as either leading switches or lagging switches. The main disadvantage of this converter is the use of the energy stored in the transformer leakage inductance to obtain ZVS for the lagging switches. There are two methods to solve this problem, which are improved ZVS (IZVS) or ZCS. It is well known that ZVS is a quasi-resonant period between inductances referring to the primary of the transformers and intrinsic capacitances of the switches, and the energy stored in the inductances must be large enough to conduct the anti-paralleled diodes of the coming switches. As this energy is dened as LI2 /2, IZVS extends the ZVS range by either increasing the value of the primary equivalent inductance or increasing the

current of the switches. The rst approach increases circulating energy, which adds more conduction loss. Furthermore, a reduction of the effective duty ratio and a severe parasitic ringing may occur, which degrades the performance of the converter. In the second way, the current of the switches can be enlarged by either increasing the magnetizing current of the transformer or adding commutation auxiliary circuit (CAC) [30][32]. The current comparison of CAC inductor La and magnetizing inductor Lm is illustrated in Fig. 2. Compared to iLm , the peak value of iLa is only inuenced by the input voltage and switching period, which means more resonant energy can be provided with increasing of the input voltage in wide PS angle range. As the La is larger than the leakage inductance, the added current RMS value of the switches is not much higher, which means small conduction loss may add after introducing CACs. Aforementioned features mean the converter with CAC will not cause much conduction loss, and can signicantly enlarge the ZVS range for the corresponding switches. Therefore, the converter with CAC may be a better solution to achieve IZVS, especially in high voltage application. The lagging switches can also realize ZCS by resetting the primary current during the free-wheeling mode. According to the different reset voltage generated methods, the ZCS circuits can be concluded into two main kinds, which are primary reset and secondary reset [10]. Commonly, ZCS technology is more suitable for the converter with IGBTs because of large tailing current during switching commutation. A. ZVS TL PWM Converter With One CAC Per Module As illustrated in Fig. 3, ZVS PWM TL converter with one CAC per module is composed of two dcdc modules with mirror structure. The second module is introduced to balance the dc link voltage. Each module is built of four switches, one high frequency transformer, and one dc-blocking capacitor. Cin1 to Cin4 are common dc link capacitors with same value and large enough to share the input voltage evenly, i.e., VC in1 = VC in2 =

SHI AND YANG: WIDE RANGE SOFT SWITCHING PWM THREE-LEVEL DCDC CONVERTERS SUITABLE FOR INDUSTRIAL APPLICATIONS

605

Fig. 5.

ZVZCS type TL PWM converter.

Fig. 3.

ZVS TL PWM converter with one CAC per module.

Fig. 4.

ZVS TL PWM converter with two CACs per module.

Fig. 6.

ZVZCS TL PWM converter with one CAC per module.

VC in3 = VC in4 = Vin /4. L1 and L2 are CAC inductances to extend ZVS load range for the lagging switches. Llk1 and Llk2 are the leakage inductances of T1 and T2 . Full wave rectiers are adopted in the topology, and Do 1 Do 4 are rectier diodes. During the operation, the eight switches can be divided into four switching pairs, i.e., S1 and S2 , S3 and S4 , S5 and S6 , S7 and S8 . The switches in each switching pair are operated in complementary mode. S4 and S5 are switched simultaneously to balance the voltage of input capacitors, while S3 and S6 are switched simultaneously with the same purpose. The two CACs can provide more energy to assist ZVS of S3 , S4 , S5 , and S6 . Vo 1 is regulated by the phase angle between S1 and S4 , and Vo 2 is regulated by the phase angle between S5 and S8 . Thus, the two dc-dc modules can power either single load or two independent loads. B. ZVS TL PWM Converters With Two CACs Per Module Fig. 4 depicts a ZVS TL PWM converter with two CACs per module. This converter is composed of four switches, one high frequency transformer, and one dc-blocking capacitor. Cin1 Cin4 are common dc link capacitors with same value and large enough to share the input voltage evenly, i.e., VC in1 = VC in2 = VC in3 = VC in4 = Vin /4. L1 and L2 are CAC inductances to extend ZVS load range for the leading and lagging switches. Llk is the leakage inductance. Full wave rectier is adopted in the topology, and Do 1 and Do 2 are rectier diodes. With proper designing, all the switches can achieve ZVS even down to no load.

C. ZVZCS TL PWM Converters Fig. 5 shows a ZVZCS TL PWM converter. As illustrated in Fig. 5, it is composed of the switches S1 S4 , cutoff diodes D3 and D4 , high frequency transformer T1 , dc-blocking capacitor CBL . CBL is large enough to sustain the average voltage of Vin /2 during the whole operation stages and the voltage ripple of this capacitor is designed to a specied value to assist ZCS of the lagging switches. Cin1 and Cin2 are dc link capacitors with same value and large enough to share the input voltage evenly, i.e., VC in1 = VC in2 = Vin /2. Llk is the leakage inductance of T1 . A full wave rectier is adopted in the topology, and Do 1 and Do 2 are rectier diodes. The output lter is built of Lo and Co , and Ro is the load resistance. D. ZVZCS TL PWM Converter With One CAC Per Module Fig. 6 shows a kind of ZVZCS with one CAC per module, and it is a combination of the converter in Figs. 3 and 5. The leading switches can obtain ZVS with wide load range after introducing the CACs, while ZCS technology is applied to lagging switches. Just as the converter in Fig. 3, Vo 1 and Vo 2 can power either single load or two independent loads. III. PRINCIPLE OF OPERATION The operation principle of the converters in Figs. 3 and 5 is discussed as an example in this part. Before the analysis, some assumptions should be set to clarify the explanation: all the components in the topologies are ideal; the voltage ripple on the dc link capacitors can be neglected; the voltage ripple of

606

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 29, NO. 2, FEBRUARY 2014

The time of this period is given by T10 = kT 1 Vin Cos . Io 1 (3)

When the vrect1 decays to zero, T1 will be operated in the free-wheeling mode. iL 1 and iL 2 keep increasing. Stage 3 [Fig. 8(c)]: At instant t1 , D2 is conducted naturally. S4 , S5 , and S8 are kept ON. T1 is operated in the free-wheeling mode, and T2 powers load through Do 3 . Do 1 , Do 2 , and Do 3 are conducted, while Do 4 is OFF; vrect1 = 0, vrect2 = Vin /2kT 2 . During this stage, S2 must be turned ON to obtain ZVS. According to Fig. 7, S2 is turned ON at instant t4 . S1 and S6 are clamped by Cin1 and Cin2 , while S3 and S7 are clamped by Cin3 and Cin4 . Stage 4 [Fig. 8(d)]: At instant t2 , S8 is turned OFF at zero voltage due to the existence of C8 . iT 2p charges C8 and discharges C7 linearly with time. This stage ends until vC 8 equals to Vin /2, and vC 7 decays to zero. The voltage of point K can be represented by

Fig. 7. Ideal waveforms of the ZVS PWM TL converters with one CAC per module.

vK (t) =

Io 2 t. 2kT 2 Cos

(4)

The time of this period can be given by blocking capacitors of the converter in Fig. 3 can be neglected, while the voltage ripple of blocking capacitor of the converter in Fig. 5 is designed to a specied value to reset the primary voltage; output lter and load is instead by constant current source; L1 equals L2 and is represented by LCAC in the following deducted equations; the output capacitance of each switch is with the same value and represented by Cos in the following deducted equations. A. ZVS PWM TL Converter With One CAC Per Module The corresponding key waves are illustrated in Fig. 7. Fig. 8 highlights the eight switching stages during the rst half switching cycle and the other switching states for the remaining half switching cycle are similar to the rst eight switching stages. Stage 1 [Fig. 8(a)]: Before t0 , the circuit is operated in a steady condition and power is transferred from the input source through T1 and T2 to the loads. S1 , S4 , S5 , and S8 are turned ON; Do 1 and Do 3 are conducted, while Do 2 and Do 4 are off; vGH = vJK = Vin /2; vrect1 = Vin /2kT 1 , and vrect2 = Vin /2kT 2 ; iT 1p = Io 1 /kT 1 , iT 2p = Io 2 /kT 2 . S2 and S6 are directly clamped by Cin1 and Cin2 , while S3 and S7 are directly clamped by Cin3 and Cin4 . iL 1 and iL 2 increase with time linearly; the slope of the currents is determined by diL 1 diL 2 Vin Vin = = = . dt dt 2 (L1 + L2 ) 4LCAC (1) T23 = kT 2 Vin Cos . Io 2 (5)

When the vrect2 decays to zero, T2 will be operated in the free-wheeling mode. Stage 5 [Fig. 8(e)]: At instant t3 , D7 is conducted naturally. S4 and S5 are kept ON. T1 and T2 stay in the free-wheeling mode. iT 1p ows through Cin3 , Cin4 , S4 , D2 , CBL1 , T1 ; iT 2p ows through Cin1 , Cin2 , S5 , D7 , CBL2 , T2 ; vrect1 = vrect2 = 0. During this stage, S7 must be turned ON to obtain ZVS. According to Fig. 7, S7 is turned ON at instant t5 . S1 and S6 are clamped by Cin1 and Cin2 , while S3 and S8 are clamped by Cin 3 and Cin 4 . Stage 6 [Fig. 8(f)]: At t6 , S4 and S5 are turned OFF at zero voltage due to the existence of C4 and C5 ; iL 1 and iT 2p charge C5 and discharge C6 linearly with time; iL 2 and iT 1p charge C3 and discharge C4 linearly with time. iL 1 and iL 2 reach their maximum value and keep this value during the stage. Thanks to the energy stored in L1 and L2 , S3 and S6 can achieve ZVS. The peak value of iL 1 and iL 2 is given by IL 1 m ax = IL 2 m ax = Vin Ts . 16LCAC (6)

From stages 16, iL 1 (t) and iL 2 (t) are represented by iL 1 (t) = iL 2 (t) = Vin Ts Vin + (t t0 ). 16LCAC 4LCAC (7)

Stage 2 [Fig. 8(b)]: At the instant t0 , S1 is turned OFF at zero-voltage due to the existence of C1 . iT 1p charges C1 and discharges C2 linearly with time. This stage continues until vC 2 equals to zero, and vC 1 increases to Vin /2. The voltage of point F is vF (t) = Vin Io 1 t. 2kT 1 Cos (2)

Stage 7 [Fig. 8(g)]: At t8 , D3 and D6 are transferred to the ON status naturally. The circuit keeps in the free-wheeling mode, iT 1p , iT 2p , iL 1 , and iL 2 decay due to negative voltage applied to the terminals of Llk1 , Llk2 , L1 , and L2 . During this stage, S3 and S6 must be turned ON to ensure ZVS. According to Fig. 7, S3 and S6 are turned ON at t9 . S1 and S5 are clamped by Cin1 and Cin2 , while S4 and S8 are clamped by Cin3 and Cin4 . Stage 8 [Fig. 8(h)]: At instant t9 , S3 and S6 are gated ON. S2 and S7 have been turned ON. The primary currents of the

SHI AND YANG: WIDE RANGE SOFT SWITCHING PWM THREE-LEVEL DCDC CONVERTERS SUITABLE FOR INDUSTRIAL APPLICATIONS

607

Fig. 8.

Equivalent circuits of the ZVS PWM TL converters with one CAC per module.

transformers increase in the inverse direction, after these currents reach to Io 1 /kT 1 and Io 2 /kT 2 , respectively; the freewheeling modes of T1 and T2 are over. Power is transferred from the input source to the load continually. vGH = vJK = Vin /2; vrect1 = Vin /2kT 1 , and vrect2 = Vin /2kT 2 ; iT 1p = Io 1 /kT 1 , iT 2p = Io 2 /kT 2 . iL 1 and iL 2 increase linearly in the reverse direction with time; the slope of the currents is given by diL 1 diL 2 Vin = = . dt dt 4LCAC (8)

From now, iL 1 (t) and iL 2 (t) are given by iL 1 (t) = iL 2 (t) = Vo 1 is represented by Vo 1 = Do 1 Vin 2 (10) Vin Ts Vin (t t9 ). 16LCAC 4LCAC (9)

where Do 1 is the duty ratio of module 1.

608

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 29, NO. 2, FEBRUARY 2014

TABLE I OFF VOLTAGE OF THE SWITCHES OF THE ZVS PWM TL CONVERTERS WITH ONE CAC PER MODULE

ON at instant t2 ; vrect = 0. The voltage of CBL can be treated as a constant voltage source represented as VCBLP during this stage and it is fully applied to Llk to reset the primary side current. The expression of ip in this stage can be given by ip (t) = Io VCBLP Vin /2 (t t1 ). kT Llk (15)

This stage ends until ip decays to zero, and the time of this stage is T31 = Io Llk . kT (VCBLP Vin /2) (16)

Vo 2 is represented by Vin (11) 2 where Do 2 is the duty ratio of module 2. From stage 8, the circuit is operated in the second half period. The voltage stress of the switches during each operation state is shown in Table I. The currents owing through the four input capacitors are depicted in Table II. Vo 2 = Do 2 B. ZVZCS TL PWM Converter Fig. 9 shows the six switching stages of the converter in Fig. 5 during the rst half switching cycle, and the corresponding key waves are depicted in Fig. 10. Stage 1 [Fig. 9(a)]: Before t0 , the circuit operates in the steady condition and power is transferred from input source to the load. S1 and S4 are turned ON; Do 1 is conducted while Do 2 is OFF; the voltage of CBL increases linearly with time, and the slope of vCBL is given by dvCBL Io = . dt kT CBL (12)

Stage 4 [Fig. 9(d)]: At instant t3 , ip decays to zero. Due to the existence of D4 , the primary current cannot be conducted in the reverse direction. After the instant of t3 , ip keeps the value zero, so S4 can achieve ZCS turned OFF. The voltage of CBL keeps constant. Stage 5 [Fig. 9(e)]: At instant t4 , S3 is gated ON, and S3 can achieve ZCS turned ON due to the existence of the Llk ; S2 has been turned ON at instant t2 ; ip increases linearly with time in the reverse direction, and the circuits is still in the free-wheeling modes until ip reaches to Io /kT . ip in this stage is given by ip (t) = vCBL (t t4 ). Llk (17)

The voltage of CBL decreases due to discharging current ip vCBL (t) = VCBLP And the expression of vCBL (t) is vCBL (t) = VCBLP e 2 L l k C B L . Substituting (19) into (17) yields VCBLP e 2 L l k C B L (t t4 ) . ip = Llk

( t t 4 ) 2 ( t t 4 ) 2

ip (t)dt.

t4

(18)

During this stage, vBC = Vin vCBL ; vrect = (Vin vCBL )/ kT ; and ip = Io /kT . Stage 2 [Fig. 9(b)]: At instant t0 , S1 is turned OFF at zero voltage due to the existence of C1 ; vCBL keeps increasing during this stage, and reaches its peak value VCBLP at the end of this stage; ip keeps constant value of Io /kT during this intervals, and charges C1 and discharges C2 linearly with time. This stage continues until vC 1 equals to Vin /2 and vC 2 decays to zero. The voltage of point A is given by Io vA (t) = Vin (t t0 ). 2kT Cos is T10 = kT Cos Vin . Io (14) (13)

(19)

(20)

This interval ends until ip = Io /kT , so the time of this interval can be computed according to (20). As for the value of

( t t 4 ) 2

At instant t1 , vA deceases to Vin /2 and the time of this interval

e 2 L l k C B L is much smaller referenced to the value of VCBLP , so the time of this interval can be roughly predicted by T54 = Llk Io . kT VCBLP (21)

Stage 3 [Fig. 9(c)]: At instant t1 , D2 is conducted naturally; the circuit is operated in the free-wheeling mode; both of the rectier diodes are conducted; During this stage, S2 must be gated ON to achieve ZVS, and according to Fig. 10, S2 is turned

Stage 6 [Fig. 9(f)]: At instant t5 , ip reaches to Io /kT ; the free-wheeling mode is over. Primary powers the load from the energy stored in CBL through S2 , D3 , S3 , the transformer, and

SHI AND YANG: WIDE RANGE SOFT SWITCHING PWM THREE-LEVEL DCDC CONVERTERS SUITABLE FOR INDUSTRIAL APPLICATIONS

609

TABLE II CURRENTS FLOWING THROUGH EACH INPUT CAPACITOR OF THE ZVS PWM TL CONVERTERS WITH ONE CAC PER MODULE

Fig. 9.

Equivalent circuits of the ZVZCS TL PWM converter.

output rectier and lter. vBC = vCBL ; vrect = vCBL /kT ; ip = Io /kT . From stage 6, the circuit is operated in the second half period. As illustrated in Table III, voltage across the switches is not larger than Vin /2 at each operation state. Table IV shows the current owing through input capacitors during the rst half period.

IV. SOFT SWITCHING CHARACTERISTICS A. ZVS for the Leading Switches 1) Turn-Off Intervals: Due to the existing output capacitance or the capacitor parallel-connected with leading switches, the leading switches can be achieved zero-voltage turn-off. When a

610

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 29, NO. 2, FEBRUARY 2014

So, leading switches can be always turned ON at zero voltage. S2 in Fig. 3 is selected as an example. As shown in Fig. 8(b), ZVS criteria for S2 can be represented as 1 L 2 p Io 1 kT 1

2

Cos

Vin 2

(22)

2 where Lp is equal to Llk 1 + kT 1 Lo 1 . The minimum load current to realize ZVS for S2 is

Io 1m in = kT 1 Vin

2(Llk1

Cos 2 L ). + kT 1 o1

(23)

3) Turn-On Intervals With CAC: As CAC is added into the circuits, the leading switches can achieve ZVS even with no load current. S2 in Fig. 4 is chosen as an example. The ZVS criteria for S2 can be given by

Fig. 10. Key waveforms of the ZVZCS TL PWM converter. TABLE III OFF VOLTAGE OF THE SWITCHES OF THE ZVZCS TL PWM CONVERTER

1 L 2 p

Io kT

1 2 + LCAC ILCAC Cos 2

Vin 2

(24)

2 where Lp is equal to Llk1 +kT Lo . Let Io = 0. Equation (24) can be simplied as 2 LCAC ILCAC

Cos (Vin )2 . 2 V in Ts . 16LCAC

(25)

According to (6), ILCACm ax is ILCACm ax = (26)

Substituting (26) into (25) gives

TABLE IV CURRENTS FLOWING THROUGH EACH INPUT CAPACITOR OF THE ZVZCS TL PWM CONVERTER

LCAC

Ts2 . 8Cos

(27)

During the commutation, the quasi-resonant period should nish before the driven signal of the coming switches. The dead time between the switches is set to 0.05Ts . Thus, the following equation should be observed to keep safe ZVS IL C A C Vin Cos . 2 (0.05Ts ) (28)

Substituting (26) into (28) gives LCAC LCACm in is LCACm in = min {(29), (27)} . switch is gated to OFF, the current owing through this switch is transferred to the parallel-connected capacitor. As the voltage of the capacitors cannot be changed suddenly, its voltage rises progressively until the nal voltage. Thus, the cross-production of the voltage and current in the switch is decreased and the losses during the turned off intervals can be reduced [6]. 2) Turn-On Intervals Without CAC: During this commutation instant, the output inductance together with leakage inductance of the transformer charges or discharges related intrinsic capacitance of leading switches, and energy is large enough to drive the anti-parallel diode to conduct even at the light load. (30) Ts2 . 160Cos (29)

LCAC should be designed as (30) to conrm safe ZVS operation down to no load, and the peak current of S3 is ISp = Io Vin Ts + . kT 16LCAC (31)

In order to achieve higher light load efciency, larger CAC inductors current is preferred, but the full load efciency will decrease due to added conduction loss. Thus, the value of LCAC should be designed as a tradeoff between light load efciency and full load efciency [32].

SHI AND YANG: WIDE RANGE SOFT SWITCHING PWM THREE-LEVEL DCDC CONVERTERS SUITABLE FOR INDUSTRIAL APPLICATIONS

611

B. ZVS for the Lagging Switches With CAC The turn-off conditions of the lagging switches are quite similar with leading switches, and thanks to the parallel-connected capacitor, the voltage across the switch is not increasing sharply. Therefore, the turn-off losses can be signicantly reduced. As CAC is added into the circuit, the lagging switches can obtain ZVS even with no load current. The analysis of the required LCAC is quite similar to the leading switches with CACs, and the detail information is not provided here. C. ZCS for the Lagging Switches 1) Turn-Off Intervals: As illustrated in Fig. 10, the lagging switches should be turned OFF after ip decays to zero and the interval is dened as T31 in (16). When IGBTs are used as lagging switches, the minority carriers in the component can be combined within a specic time, and this interval is determined by the component itself and dened as TCOM . Therefore, in order to keep safe ZCS operation for the IGBTs, the following equation should be conrmed: T31 + TCOM Treset . (32)

Fig. 11.

iL C A C and its effect on the voltage of C in 1 .

The maximum CBL should be limited to conrm ZCS under Dm ax , and the value is given by CBL (Ts 2Treset ) (Treset TCOM ) . 2Llk (39)

2) Turn-On Intervals: Due to the existed leakage inductance, the switch can be achieved zero-current turn-on. When a switch is gated ON, the current owing through this switch cannot be changed suddenly, and its value rises progressively until the nal current. Thus, the cross-production of the voltage and current in the switch is decreased and the losses during the turned on intervals can be reduced. V. VOLTAGE BALANCE PRINCIPLE OF INPUT CAPACITORS AND BLOCKING CAPACITORS A general explanation of the voltage balance principle of input capacitors and blocking capacitors is provided in this section. As proved in [6], the load currents cannot inuence the voltage distribution among the input capacitors with PS modulation strategy. Thus, only currents of CACs may change the voltage balance among input capacitors. The effect of the currents of CACs to input capacitor is rst discussed. And then, the analysis of blocking capacitors is provided. A. Description of Input Capacitor in the Converters With CACs The converter in Fig. 3 is selected as an example. The initial voltage distribution among the input capacitors is evenly due to circuit conguration. If we want to sustain the voltage of the input capacitors, the following equation should be tted in one switching cycle:

T T T T

During normal operation, the average voltage of CBL is Vin /2. So, the peak voltage value of CBL can be given by VCBLP = vC B L pp + Vin /2. 2 (33)

where vC B L pp is the peak to peak value of the voltage ripple of CBL . Substituting (33) into (16) gives T31 = 2Io Llk . kT vC B L PP (34)

The value of CBL should be designed keeping safe ZCS at maximum duty ratio, and the Dm ax is given by Dm ax = 1 Substituting (35) into (12) gives vC B L pp Io (Ts 2Treset ) = . kT CBL (36) Treset . Ts /2 (35)

iC i n 1 (t) =

0 0

iC i n 2 (t) =

0

iC i n 3 (t) =

0

iC i n 4 (t) = 0.

Substituting (36) into (34) gives T31 = 2Llk CBL . (Ts 2Treset ) (37)

Substituting (37) into (32) yields 2Llk CBL + TCOM Treset . (Ts 2Treset ) (38)

(40) As shown in Table II, Cin2 and Cin3 are charged by CACs with the current dened as (7) in the rst half switching period, while Cin1 and Cin4 are discharged by CACs with the same current slope dened as (7). By examining the second half switching period, Cin2 and Cin3 are discharged by CACs with the current dened as (9), and Cin1 and Cin4 are charged by CACs with the same current slope. Therefore, all input capacitors have discharge and charge states in one switching cycle, and the absolute value of the current owing through the capacitors in the half switching period is identical. Fig. 11 shows iLCAC and its effect on the voltage of Cin1 . The current integral of Cin1 in

612

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 29, NO. 2, FEBRUARY 2014

TABLE V COMPONENTS COMPARISON AMONG THE PROPOSED CONVERTERS (COMPONENT NO. PER MODULE)

Fig. 12.

Ideal current and voltage of C B L .

one switching cycle is

T Ts / 2

iC i n 1 (t) =

0 0 Ts / 2

Vin Vin Ts + t dt 16LCAC 4LCAC Vin Ts Vin t dt (41) 16LCAC 4LCAC voltage. In addition, two modules are required under normal operation to balance the dc link voltage; thus, it is not suitable for small power rating single output applications. The converter in Fig. 4 features wide ZVS load range for either leading switches or lagging switches and only one module is required during the operation. As the tailing current of IGBTs is a serious problem during the operation, ZVZCS is more suitable for applications with IGBTs. In order to minimize the switching loss of the leading switches in ZVZCS converters, a combined structure is introduced in Fig. 6. The leading switches can be switched with ZVS down to zero load current, and the lagging switches can be achieved ZCS within maximum duty ratio. If the soft switching range for the leading switches is not a key point, the converters in Figs. 4 and 5 may be a better choice due to simpler structure. The converters in Figs. 3 and 6 can also be applied to dual-output applications. Fig. 13 shows a recommendation of the component selection for each converter with respect to the input voltage and switch current. According to the datasheet of the devices producer, 500600 V MOSFETs have overall good performance compared to higher voltage rating MOSFETs. Thus, the converters in Figs. 3 or 4 with MOSFET components are more likely used with 500800 V input voltage. With respect to the dissipating power limitation, the switch current of these type converters should be limited around 50 A. The maximum voltage rating of converters with MOSFETs can be extended to 1400 V, but the handling power will decrease with limitation of the device dissipating power, and the converter in Fig. 4 is more suitable in this application because the switching loss of all switches must be minimized. The converter in Fig. 3 may extend the MOSFETs to 100 A applications due to inherent two modules. The IGBTs are more suitable for the remaining zone in Fig. 13. With an increase in the input voltage, Fig. 4 shows more advantage, while the converter in Figs. 5 and 6 may gain more good results in high switch current applications. VII. EXPERIMENTAL RESULTS Experiments are carried out on a general purpose test setup for the new dcdc converter topologies built by our company, and the main parameters of the setup are shown in Table VII. The basic operation principle is proved by the converters in Figs. 3

+

0

In an ideal situation, the current integral of Cin1 in one switching cycle is zero, and the voltage of Cin1 can be stabled. The voltage of other input capacitors can also be stabled under the ideal situation. More detail information about the voltage balance method of input capacitors exceeds the scope of this paper, and this will be done in the future work. B. Description of the Blocking Capacitors Take the converter in Fig. 5 as an example. Before normal operation, the four switches are OFF, and the voltage of CBL increases with input voltage. The nal voltage of CBL is Vin /2 due to the conguration of the circuit. Then, the four switches can be controlled in the PS mode to begin output soft-start transition. Thus, the output rectier diodes suffer even voltage stress as normal isolated dcdc converter under normal operation modes. During the operation, the voltage of CBL can be sustained by observing the following equation in one switching cycle:

T

iC B L (t) = 0.

0

(42)

As shown in Fig. 12, the primary current ows through CBL with constant value during the power transfer state, and keeps zero during freewheeling intervals. The time of the positive current interval is identical to the time of the negative current in one switching cycle. Thus, the voltage of CBL can be stabled during normal operation. The value of CBL can be designed according to the following equation: CBL = Io (t1 t0 ). kT vCBL (43)

VI. COMPARISON AMONG THE PROPOSED CONVERTERS Comparison among the proposed converters is shown in Tables V and VI. According to Table V, the components number per module of the converter in Fig. 3 is smallest among the four types of the presented converters. But the leading switches of this kind of converter cannot achieve ZVS under zero load condition, and the switching loss will also increase under high input

SHI AND YANG: WIDE RANGE SOFT SWITCHING PWM THREE-LEVEL DCDC CONVERTERS SUITABLE FOR INDUSTRIAL APPLICATIONS

613

TABLE VI SOFT SWITCHING CHARACTERISTICS FOR EACH TYPE CONVERTER

TABLE VII MAIN PARAMETERS OF THE PROTOTYPE

Fig. 13. Recommendation of components selection for the proposed converters.

and 5. The efciency test is carried out among the converters in Figs. 35. Fig. 14 shows the voltage stresses of the active switches of the converter in Fig. 5. It is clearly that the voltage stress on the switch is Vin /2, and the difference of the maximum voltage stress among the switches is smaller than 5% of the total input voltage. Off voltage of switches of other converters shows the similar character and the waves are not provided in this paper for simplication. The basic operation principles of the converter in Fig. 5 are illustrated from Figs. 1518. Fig. 15 shows the primary side voltage waves of the transformers. Fig. 16 depicts the primary side current of the transformer, and it is reset and kept zero during the freewheeling stage which agrees well with the theoretical analysis. The voltage of CBL is also shown in Fig. 16, and the voltage ripple conrms the perdition of (43). The voltage across the rectier diode and the current of the output inductor are provided in Figs. 17 and 18 respectively. Soft switching characteristics of the converter in Fig. 5 are shown in Figs. 19 and 20, and the leading switch is tested at 30% load current and the lagging switch is tested at 70% load current. From Fig. 19, we can conclude that the leading switches can obtain ZVS with wide load range. As illustrated in Fig. 20, the lagging switches can achieve ZCS as theoretically predicted with wide load range. The basic operation principles of the converter in Fig. 3 are illustrated from Figs. 2124. Fig. 21 shows the primary side voltage and current waves of the transformer. Fig. 22 depicts the voltage and current of the CAC inductor. From Figs. 23 and

Fig. 14.

Voltage across S1 and S4 .

614

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 29, NO. 2, FEBRUARY 2014

Fig. 20. Fig. 15. Voltage across the primary sides of the transformer.

Zero-current switching of S4 at 70% load.

Fig. 21. Fig. 16. Voltage ripple of CB L versus ip .

Primary side voltage and current waves of T1 .

Fig. 22.

Voltage and current of CAC inductor L 1 .

Fig. 17.

Voltage across the rectier diode.

Fig. 23.

Zero-voltage turned on of S3 at 10% load.

Fig. 18.

Current of output inductor.

Fig. 19.

Zero-voltage switching of S1 at 30% load.

24, we can conclude that the lagging switches can achieve ZVS with wide range. In the efciency test, converter in [6] is also tested for comparison, and the primary circuit is given in Fig. 1(a). The switches and rectier diodes used in the converter [6] are identical to the aforementioned setup. During the test, the loss of uncontrolled rectier, the auxiliary power to the controller and driver are taken into account in the efciency test, while the loss of cooling unit used in the setup is not included. Fig. 25 shows the efciency comparison under different load currents with 600 V input voltage. As all the switches can obtain ZVS down to zero current, the efciency of the converter in Fig. 4 is higher than other circuits at the light load zone. The maximum efciency of the converter in Fig. 5 is a little higher than others. As the

SHI AND YANG: WIDE RANGE SOFT SWITCHING PWM THREE-LEVEL DCDC CONVERTERS SUITABLE FOR INDUSTRIAL APPLICATIONS

615

TABLE VIII ADDED COST OF THE CONVERTERS IN THE EXPERIMENT COMPARED TO THE CONVERTER IN [6]

Fig. 24.

Zero-voltage turned off of S3 at 10% load.

VIII. CONCLUSION This paper discusses wide range soft switching range solutions to a PWM TL dcdc converter suitable for industrial applications, and four kinds of soft switching PWM TL dcdc converters are presented and analyzed in this paper. The principle of operation and theoretical analysis of the proposed circuit are discussed, and a general prototype is built to verify the circuits. Experimental results supported the theoretical predictions properly. After discussion, following conclusions can be derived: 1) all the switches suffer Vin /2 voltage stress without added clamping devices; 2) CAC is a better solution to enlarge ZVS load range, especially in high input applications; 3) two CAC units are required to balance the input voltage, and the two CACs can be included in either one module or two modules, respectively; 4) the leading switches can only achieve ZVS, while the lagging switches can obtain ZVS or ZCS; 5) a common PS control method can be used, which makes these topologies more applicable; 6) the converter in Figs. 3 and 6 can be used in dual-output applications; 7) these converters can also be used in middle or lower input dcdc power conversion. The drawbacks of the proposed converters are also listed as follows. 1) In order to achieve higher light load efciency, larger CAC inductors current is preferred, but the full load efciency will decrease due to added conduction loss. Thus, the value of CAC inductors should be selected as a tradeoff between the light load efciency and the full load efciency. 2) The proposed converters are still two-level converter from the view of the output, and a large output inductance may be required to reduce the output current ripple, resulting in lower power density and slower system dynamic response. Further work on this topology may include the following: 1) more efciency test should be done to well identify the suitable applications for each converter; 2) topologies with MOSFETs should be investigated and a comparison should be made with the traditional two-level FB converter, especially in normal 3 acdc applications; 3) the voltage balance method of input capacitors after introducing CACs should be investigated in detail;

Fig. 25. voltage.

Efciency comparison with different load current and constant input

Fig. 26. current.

Efciency comparison with different input voltage and constant load

RMS value of iL C A C is smaller in the experiment, there does not exist obviously efciency drop at the full load of the converters in Figs. 3 and 4, and the four converters show similar full load efciency. The efciency comparison under different input voltages at the constant load is provided in Fig. 26. The efciency of the three converters decreases with an increase in the input voltage, but the slope is different. As two CACs are added to assist switching commutation of all the switches, the converter in Fig. 4 can achieve higher efciency compared to its competitors. The added cost of the converters in Figs. 35 compared to the converter in [6] is shown in Table VIII. The added cost per module of the converters in Fig. 3 is lowest; however, as two modules are required to balance input voltage, it is not an optimum choice for single module or single output applications.

616

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 29, NO. 2, FEBRUARY 2014

4) 1000 V or higher input voltage prototype with fault detection strategy should be designed and tested; 5) new topologies based on [6] with wide soft switching range, simple switching scheme, and TL output characteristic should be investigated. REFERENCES

[1] P. M. Barbosa and F. C. Lee, Design aspects of parallel three-phase DCM boost rectiers, in Proc. IEEE Power Electron. Spec. Conf. Rec., 1999, pp. 331336. [2] F. Blaabjerg, Z. Chen, and S. B. Kjaer, Power electronics as efcient interface in dispersed power generation systems, IEEE Trans. Power Electron., vol. 19, no. 5, pp. 11841194, Sep. 2004. [3] L. M. Tolbert and F. Z. Peng, Multilevel converters as a utility interface for renewable energy systems, in Proc. Power Eng. Soc. Summer Meet., 2000, vol. 2, pp. 12711274. [4] D. Li, F. Gao, P. C. Loh, M. Zhu, and F. Blaabjerg, Hybrid-source impedance networks: Layouts and generalized cascading concepts, IEEE Trans. Power Electron., vol. 26, no. 7, pp. 20282040, Jul. 2011. [5] J. R. Pinheiro and I. Barbi, The three-level ZVS PWM convertera new concept in high-voltage DC-to-DC conversion, in Proc. IEEE Int. Conf. Ind. Electron. Control Instrum. Autom., 1992, pp. 173178. [6] I. Barbi, R. Gules, R. Redl, and N. O. Sokal, DC/DC converter: Four switches Vp k = Vin /2, capacitive turn-off snubbing, ZV turn-on, IEEE Trans. Power Electron., vol. 19, no. 4, pp. 918927, Jul. 2004. [7] X. Ruan, B. Li, Q. Chen, S. Tan, and C. K. Tse, Fundamental considerations of three-level DCDC converters: topologies, analyses, and control, IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 55, no. 11, pp. 37333743, Dec. 2008. [8] E. Deschamps and I. Barbi, A comparison among three-level ZVS-PWM isolated DC-to-DC converters, in Proc. Annu. Conf. IEEE Ind. Electron. Soc., 1998, pp. 10241029. [9] F. Canales, P. M. Barbosa, and F. C. Lee, A zero-voltage and zero currentswitching three level DC/DC converter, IEEE Trans. Power Electron., vol. 17, no. 6, pp. 898904, Nov. 2002. [10] X. Ruan, L. Zhou, and Y. Yan, Soft-switching PWM three-level converters, IEEE Trans. Power Electron., vol. 16, no. 5, pp. 612622, Sep. 2001. [11] D. V. Ghodke, K. Chatterjee, and B. G. Fernandes, Modied softswitched three-phase three-level DC-DC converter for high-power applications having extended duty cycle range, IEEE Trans. Ind. Electron., vol. 59, no. 9, pp. 33623372, Sep. 2012. [12] I.-O. Lee, S.-Y. Cho, and G.-W. Moon, Three-level resonant converter with double LLC resonant tanks for high-input-voltage applications, IEEE Trans. Ind. Electron., vol. 59, no. 9, pp. 34503463, Sep. 2012. [13] F. Liu, J. Yan, and X. Ruan, Zero-voltage and zero-current-switching PWM combined three-level DC/DC converter, IEEE Trans. Ind. Electron., vol. 57, no. 5, pp. 16441654, May 2010. [14] S. Busquets-Monge, S. Alepuz, and J. Bordonau, A bidirectional multilevel boostbuck DCDC converter, IEEE Trans. Power Electron., vol. 26, no. 8, pp. 21722183, Aug. 2011. [15] A. Lopez, R. Diez, G. Perilla, and D. Patino, Analysis and comparison of three topologies of the ladder multilevel DC/DC converter, IEEE Trans. Power Electron., vol. 27, no. 7, pp. 31193127, Jul. 2012. [16] C. Yoon, J. Kim, and S. Choi, Multiphase DCDC converters using a boost-half-bridge cell for high-voltage and high-power applications, IEEE Trans. Power Electron., vol. 26, no. 2, pp. 381388, Feb. 2011. [17] S. Vighetti, J.-P. Ferrieux, and Y. Lembeye, Optimization and design of a cascaded DC/DC converter devoted to grid-connected photovoltaic systems, IEEE Trans. Power Electron., vol. 27, no. 4, pp. 20182027, Apr. 2012. [18] S. Chen, T. Liang, L. Yang, and J. Chen, A cascaded high step-up DCDC converter with single switch for microsource applications, IEEE Trans. Power Electron., vol. 26, no. 4, pp. 11461153, Apr. 2011. [19] H. Sheng, F. Wang, and C. W. Tipton, A fault detection and protection scheme for three-level DC-DC converters based on monitoring ying capacitor voltage, IEEE Trans. Power Electron., vol. 27, no. 2, pp. 685 697, Feb. 2012. [20] H. Wang, H. S.-H. Chung, and A. Ioinovici, A new concept of highvoltage DCDC conversion using asymmetric voltage distribution on the switch pairs and hybrid ZVSZCS scheme, IEEE Trans. Power Electron., vol. 27, no. 5, pp. 22422259, May 2012.

[21] W. Li, P. Li, H. Yang, and X. He, Three-level forward-yback phase-shift ZVS converter with integrated series-connected coupled inductor, IEEE Trans. Power Electron., vol. 27, no. 6, pp. 28462856, Jun. 2012. [22] E. Agostini and I. Barbi, Three-phase three-level PWM DC-DC converter, IEEE Trans. Power Electron., vol. 26, no. 7, pp. 18471856, Jul. 2011. [23] M. Narimani and G. Moschopoulos, A new single-phase single-stage three-level power factor correction AC-DC converter, IEEE Trans. Power Electron., vol. 27, no. 6, pp. 28882899, Jun. 2012. [24] I.-O. Lee and G.-W. Moon, Analysis and design of a three-level LLC series resonant converter for high- and wide-input-voltage applications, IEEE Trans. Power Electron., vol. 27, no. 6, pp. 29662979, Jun. 2012. [25] D.-Y. Kim, J.-K. Kim, and G.-W Moon, A three-level converter with reduced lter size using two transformers and ying capacitors, IEEE Trans. Power Electron., vol. 28, no. 1, pp. 4653, Jan. 2013. [26] F. Deng and Z. Chen, Control of improved full-bridge three-level DC/DC converter for wind turbines in a DC grid, IEEE Trans. Power Electron., vol. 28, no. 1, pp. 314324, Jan. 2013. [27] M. Schweizer and J. W. Kolar, Design and implementation of a highly efcient three-level T-type converter for low-voltage applications, IEEE Trans. Power Electron., vol. 28, no. 2, pp. 899907, Feb. 2013. [28] J. L. Duarte, J. Lokos, and F. B. M. van Horck, Phase-shift-controlled three-level converter with reduced voltage stress featuring ZVS over the full operation range, IEEE Trans. Power Electron., vol. 28, no. 5, pp. 21402150, May 2013. [29] L. Shi, B. P. Baddipadiga, M. Ferdowsi, and M. L. Crow, Improving the dynamic response of a ying-capacitor three-level buck converter, IEEE Trans. Power Electron., vol. 28, no. 5, pp. 23562365, May 2013. [30] R. W. De Doncker and J. P. Lyons, The auxiliary resonant commutated pole converter, in Proc. Ind. Appl. Soc. Annu. Meet., 1990, vol. 2, pp. 12281235. [31] R. Teichmann and S. Bernet, Investigation and comparison of auxiliary resonant commutated pole converter topologies, in Proc. IEEE Power Electron. Spec. Conf. Rec., 1998, pp. 1523. [32] J. R. Pinheiro and I. Barbi, Wide load range three-level ZVS-PWM DC-to-DC converter, in Proc. IEEE Power Electron. Spec. Conf., 1993, pp. 171177.

Yong Shi was born in Henan, China, in 1974. He received the B.S. degree in industrial electrical automation from Xian Architecture and Technology University, Xian, China, and the M.Sc. and Ph.D. degrees in electrical engineering from Xian Jiaotong University, Xian, in 2002 and 2005, respectively. From 2005 to 2007, he was a Lecturer at Shanghai Jiaotong University, Shanghai, China. Since 2007, he has been a Senior Engineer with Xian Action Power Electrical Company, Ltd., Xian. He has published more than 20 papers in journals and conferences in power electronics. His main research interests include soft-switching dc/dc converters, power factor correction converters, matrix converter, and multilevel converter.

Xu Yang (M99) was born in China in 1972. He received the B.S. and Ph.D. degrees in electrical engineering from Xian Jiaotong University, Xian, China, in 1994 and 1999, respectively. Since 1999, he has been a Faculty Member of the School of Electrical Engineering, Xian Jiaotong University, where he is currently a Professor. From November 2004 to November 2005, he was with the Center of Power Electronics Systems, Virginia Polytechnic Institute and State University, Blacksburg, VA, USA, as a Visiting Scholar. He then rejoined Xian Jiaotong University, and began teaching and doing research in the areas of power electronics and industrial automation. His current research interests include soft-switching topologies, pulse width modulation control techniques, power electronic integration, and packaging technologies.

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- High-Efficiency Active-Clamp Forward Converter With Transient Current Build-Up (TCB) ZVS TechniqueDocument9 pagesHigh-Efficiency Active-Clamp Forward Converter With Transient Current Build-Up (TCB) ZVS TechniquekerblaNo ratings yet

- DC-DC High-Voltage-Gain Converters With Low Count of Switches and Common GroundDocument22 pagesDC-DC High-Voltage-Gain Converters With Low Count of Switches and Common GroundSzymon FNo ratings yet

- A New Soft-Switching Technique For Buck, BoostDocument8 pagesA New Soft-Switching Technique For Buck, BoostVisu TamilNo ratings yet

- High-Efficient Multilevel Half-Bridge ConverterDocument9 pagesHigh-Efficient Multilevel Half-Bridge Converter'Mantas PuhtėjavasNo ratings yet

- ZVS Boost Converter With A Flyback Snubber CircuitDocument8 pagesZVS Boost Converter With A Flyback Snubber Circuitmishranamit2211No ratings yet

- Topic Assignment14Document6 pagesTopic Assignment14cuongakamarineNo ratings yet

- Ijert Ijert: Novel DC-DC Converter For PV System With High Voltage GainDocument7 pagesIjert Ijert: Novel DC-DC Converter For PV System With High Voltage GainrauolNo ratings yet

- Ircuit Onfiguration and Perating OdesDocument3 pagesIrcuit Onfiguration and Perating OdesMukul DasNo ratings yet

- 6high Power Full-Bridge DC-DC Converter Using A Center-Tapped Transformer and A Full-Wave Type Rectifier PDFDocument12 pages6high Power Full-Bridge DC-DC Converter Using A Center-Tapped Transformer and A Full-Wave Type Rectifier PDFmajidNo ratings yet

- A Novel Soft-Switching Single-Phase AC-DC-AC Converter Using New ZVS-PWM StrategyDocument2 pagesA Novel Soft-Switching Single-Phase AC-DC-AC Converter Using New ZVS-PWM Strategyskumar_61719No ratings yet

- High Power Topology: "AlbacomDocument7 pagesHigh Power Topology: "AlbacomRaveendhra IitrNo ratings yet

- 3939 Ijet IjensDocument9 pages3939 Ijet IjensGarudaOzoNo ratings yet

- Single-Switch High Step-Up Converters With Built-In Transformer Voltage Multiplier CellDocument11 pagesSingle-Switch High Step-Up Converters With Built-In Transformer Voltage Multiplier CellsathishNo ratings yet

- Novel Sngle Phase ZCSDocument7 pagesNovel Sngle Phase ZCSAntonio Hadade NetoNo ratings yet

- A New Single-Phase Single-Stage Three-LevelDocument12 pagesA New Single-Phase Single-Stage Three-LevelGururaj BandaNo ratings yet

- Bidirectional LLC Resonant Converter For Energy Storage ApplicationsDocument7 pagesBidirectional LLC Resonant Converter For Energy Storage ApplicationsRodrigo MesquitaNo ratings yet

- Non Isolated Bidirectional DC DC ConverterDocument6 pagesNon Isolated Bidirectional DC DC ConverterAnuja VargheseNo ratings yet

- Sepic ReportDocument55 pagesSepic ReportHEERAVATHINo ratings yet

- Performance Enhancement of A Novel Interleaved Boost Converter by Using A Soft-Switching TechniqueDocument10 pagesPerformance Enhancement of A Novel Interleaved Boost Converter by Using A Soft-Switching TechniqueHaijun GuNo ratings yet

- A New Single-Phase Single-Stage Three-Level Power Factor Correction AC-DC ConverterDocument12 pagesA New Single-Phase Single-Stage Three-Level Power Factor Correction AC-DC Convertersurya_v988No ratings yet

- Soft Switching DC DC ConvertersDocument114 pagesSoft Switching DC DC ConvertersRAJESHNo ratings yet

- A High Efficiency Full-Bridge ConverterDocument17 pagesA High Efficiency Full-Bridge ConverterPratzzzzNo ratings yet

- Digital Simulation of ZVS DC To DC Converter Using Simulink: AbstractDocument13 pagesDigital Simulation of ZVS DC To DC Converter Using Simulink: AbstractAshok KumarNo ratings yet

- A New Method For DC-AC Conversion Using Simplified Multilevel Inverter - Design and Analysis Using PSIM 1. V.Gowri Shankar, 2.C.UdhayashankarDocument7 pagesA New Method For DC-AC Conversion Using Simplified Multilevel Inverter - Design and Analysis Using PSIM 1. V.Gowri Shankar, 2.C.UdhayashankarraghuevmNo ratings yet

- Zero-Voltage Switching For Three-Level Capacitor Clamping InverterDocument11 pagesZero-Voltage Switching For Three-Level Capacitor Clamping InverterTiền Hoàng VănNo ratings yet

- 9.eee Ijeee Two Phase Interleaved DC SumalathaDocument16 pages9.eee Ijeee Two Phase Interleaved DC Sumalathaiaset123No ratings yet

- Design and Implementation of ZCS BUCK CONVERTERDocument51 pagesDesign and Implementation of ZCS BUCK CONVERTERAriful Haque100% (1)

- IEEE POWER ELECTRONICS 2015 Matlab Projectlist Mtech BeDocument4 pagesIEEE POWER ELECTRONICS 2015 Matlab Projectlist Mtech BeKumar RajNo ratings yet

- Design and Analysis of ZVZCS Converter With Active ClampingDocument11 pagesDesign and Analysis of ZVZCS Converter With Active Clampingeditor9891No ratings yet

- Electrical AnalyzerDocument8 pagesElectrical AnalyzerrhusheinNo ratings yet

- International Journal of Engineering Research and Development (IJERD)Document9 pagesInternational Journal of Engineering Research and Development (IJERD)IJERDNo ratings yet

- Heavy Load Light Load Conversion ReportDocument41 pagesHeavy Load Light Load Conversion ReportSanjivee SachinNo ratings yet

- A Novel Soft-Switching Synchronous Buck Converter For Portable ApplicationsDocument8 pagesA Novel Soft-Switching Synchronous Buck Converter For Portable ApplicationsPavan Kumar MaddukuriNo ratings yet

- Implementation of ZVS-ZCS Combined Snubber NetworkDocument6 pagesImplementation of ZVS-ZCS Combined Snubber NetworkYuiophjklNo ratings yet

- An Improved Soft-Switching Buck Converter With Coupled InductorDocument7 pagesAn Improved Soft-Switching Buck Converter With Coupled InductorSanthosh GuduruNo ratings yet

- DC-DC Converter: Four Switches V V 2, Capacitive Turn-Off Snubbing, ZV Turn-OnDocument10 pagesDC-DC Converter: Four Switches V V 2, Capacitive Turn-Off Snubbing, ZV Turn-OnRomitan AlexandraNo ratings yet

- Zero-Voltage Switching Technique in DC/DC Converters: Abstruct-ADocument12 pagesZero-Voltage Switching Technique in DC/DC Converters: Abstruct-ARushikeshKatkarNo ratings yet

- Paper Modulacion PWM With AN-42026Document16 pagesPaper Modulacion PWM With AN-42026DuckTronixNo ratings yet

- IET Power Electronics Volume 4 Issue 9 2011 [Doi 10.1049_iet-Pel.2010.0363] Jung, J.-h.; Ahmed, S. -- Flyback Converter With Novel Active Clamp Control and Secondary Side Post Regulator for Low Standby Power Consumption Under HighDocument10 pagesIET Power Electronics Volume 4 Issue 9 2011 [Doi 10.1049_iet-Pel.2010.0363] Jung, J.-h.; Ahmed, S. -- Flyback Converter With Novel Active Clamp Control and Secondary Side Post Regulator for Low Standby Power Consumption Under HighTuấn Anh PhạmNo ratings yet

- Bridgetopology 72 400Document8 pagesBridgetopology 72 400sravaniNo ratings yet

- Implementation of Single Stage Three Level Power Factor Correction AC-DC Converter With Phase Shift ModulationDocument6 pagesImplementation of Single Stage Three Level Power Factor Correction AC-DC Converter With Phase Shift ModulationseventhsensegroupNo ratings yet

- A Fixed-Frequency Soft-Switched Interleaved 3-Phase AC-to-DC ConverterDocument6 pagesA Fixed-Frequency Soft-Switched Interleaved 3-Phase AC-to-DC ConvertersasikalaNo ratings yet

- Matteini PHD Part1Document15 pagesMatteini PHD Part1Anonymous EnggrUsmNo ratings yet

- CombinandodutyratioyfrequenceDAB DC ACDocument11 pagesCombinandodutyratioyfrequenceDAB DC ACfiboNo ratings yet

- Quasi-Parallel Resonant DC Link Inverter With Improved PWM CapabilityDocument2 pagesQuasi-Parallel Resonant DC Link Inverter With Improved PWM CapabilityfatyfroisNo ratings yet

- Performance Evaluation of The Single-Phase Split-Source Inverter Using An Alternative Dc-Ac ConfigurationDocument4 pagesPerformance Evaluation of The Single-Phase Split-Source Inverter Using An Alternative Dc-Ac ConfigurationBrightworld ProjectsNo ratings yet

- A New Full Bridge DC/DC Converter Topology With ZVZCS FeaturesDocument9 pagesA New Full Bridge DC/DC Converter Topology With ZVZCS FeaturesAshok KumarNo ratings yet

- Four Novel PWM Shoot-Through Control Methods For Impedance Source DC-DC ConvertersDocument10 pagesFour Novel PWM Shoot-Through Control Methods For Impedance Source DC-DC ConvertersUtkarsh PrakashNo ratings yet

- A Simple Structure of Zero-Voltage Switching Zero Current Switching Buck ConverterDocument9 pagesA Simple Structure of Zero-Voltage Switching Zero Current Switching Buck Convertersang young soNo ratings yet

- High-Efficiency, High Step-Up DC-DC ConvertersDocument9 pagesHigh-Efficiency, High Step-Up DC-DC ConvertersC_hakan_CNo ratings yet

- Soft Switching InverterDocument5 pagesSoft Switching InverterBhushan MandvalNo ratings yet

- Trubitsyn High Efficiency ECCEDocument8 pagesTrubitsyn High Efficiency ECCEprabu2991991No ratings yet

- BuckConverter Design Jpe10Document13 pagesBuckConverter Design Jpe10joviflocasNo ratings yet

- Two-Stage Micro-Grid Inverter With High PDFDocument10 pagesTwo-Stage Micro-Grid Inverter With High PDFacostaricciNo ratings yet

- A State Space Modeling of Non-Isolated BidirectionDocument11 pagesA State Space Modeling of Non-Isolated BidirectionabdullahshahidNo ratings yet

- Lawler Trans Pe Jan 2004 PDFDocument12 pagesLawler Trans Pe Jan 2004 PDFAshok KumarNo ratings yet

- High Efficiency Bi-Directional Converter For Flywheel Energy Storage ApplicationsDocument10 pagesHigh Efficiency Bi-Directional Converter For Flywheel Energy Storage Applicationsmridul mpNo ratings yet

- Design of Transformer-Less DC To AC Converter Using PWM TechniqueDocument6 pagesDesign of Transformer-Less DC To AC Converter Using PWM TechniqueHariesh WaranNo ratings yet

- Final EE435 1st 28-29Document3 pagesFinal EE435 1st 28-29Adhere LoveNo ratings yet

- Challenges and Solutions of Protecting Variable Speed Drive Motors-NOTA TECNICADocument8 pagesChallenges and Solutions of Protecting Variable Speed Drive Motors-NOTA TECNICAEdgardo Kat ReyesNo ratings yet

- Upstation GXT Series 230V Models Upstation GXT Series 230V ModelsDocument161 pagesUpstation GXT Series 230V Models Upstation GXT Series 230V ModelsalgenygNo ratings yet

- Lab Manual For Control Lab PDFDocument95 pagesLab Manual For Control Lab PDFrakheep123No ratings yet

- Four Quadrant OperationDocument9 pagesFour Quadrant OperationMOTILAL SUTHAR215291No ratings yet

- Predicting Iron Losses in Soft Magnetic Materials With Arbitrary Voltage Supply An Engineering ApproachDocument9 pagesPredicting Iron Losses in Soft Magnetic Materials With Arbitrary Voltage Supply An Engineering Approachmayur isameNo ratings yet

- Question Bank-EE2352 - Solid State DrivesDocument4 pagesQuestion Bank-EE2352 - Solid State Drivesdgsgovind100% (1)

- LG Display Datasheet LC550WUDDocument43 pagesLG Display Datasheet LC550WUDScatter ManiaNo ratings yet

- Lecture 2 DC To Ac InverterDocument50 pagesLecture 2 DC To Ac InverterMohamed AhmedNo ratings yet

- Functions of ArduinoDocument2 pagesFunctions of ArduinojamillaphilipNo ratings yet

- FDS6690 PDFDocument6 pagesFDS6690 PDFBengkel Kompu7erNo ratings yet

- Experiment 2 - Pulse Amlitude ModulationDocument5 pagesExperiment 2 - Pulse Amlitude ModulationImaizumi RieNo ratings yet

- SSP 272 Phaeton ObpsDocument27 pagesSSP 272 Phaeton Obpsภูเก็ต เป็นเกาะNo ratings yet

- Inovance - MD300Document85 pagesInovance - MD300bernabasNo ratings yet

- Celik 11Document412 pagesCelik 11Mohammed NizamuddinNo ratings yet

- Speed Control Test Cat C15Document8 pagesSpeed Control Test Cat C15Mantenimiento La Punta100% (1)

- Me Ped LabDocument1 pageMe Ped LabBalasubramaniNo ratings yet

- VW Audi 1.8T Plugin ManualDocument22 pagesVW Audi 1.8T Plugin Manualnegg 3480% (1)

- LCL-Filter Design For Robust Active DampingDocument12 pagesLCL-Filter Design For Robust Active DampingbibiNo ratings yet

- CM6800GIPDocument18 pagesCM6800GIPAndré Frota PaivaNo ratings yet

- PIC18F24K40 MicrochipDocument822 pagesPIC18F24K40 MicrochipDiego OliveiraNo ratings yet

- Modulation Strategies For Three Level PWM Converter - Fed Induction Machine DrivesDocument101 pagesModulation Strategies For Three Level PWM Converter - Fed Induction Machine DrivesPelmus LiviuNo ratings yet

- ISL6263C IntersilDocument18 pagesISL6263C IntersilCer CerNo ratings yet

- Chipown: Low Standby-Power Quasi-Resonant Primary-Side ConverterDocument10 pagesChipown: Low Standby-Power Quasi-Resonant Primary-Side ConverterJoaquin Andres AlarconNo ratings yet

- Description Features: Ait Semiconductor IncDocument10 pagesDescription Features: Ait Semiconductor IncMaktum KamatNo ratings yet

- Tcg057vglaaann-Gn20 PDFDocument20 pagesTcg057vglaaann-Gn20 PDFYouness Ben TibariNo ratings yet

- IoT Based Robot ArmDocument39 pagesIoT Based Robot ArmJayashree R100% (1)

- Datasheet: Inteligen NTC BaseboxDocument4 pagesDatasheet: Inteligen NTC BaseboxsantoNo ratings yet

- Report - Intelligent Air Care (Iac) System Using IotDocument51 pagesReport - Intelligent Air Care (Iac) System Using IotAakash Kumar MNo ratings yet

- N-Mos BS107Document7 pagesN-Mos BS107Paolo RossiNo ratings yet

![IET Power Electronics Volume 4 Issue 9 2011 [Doi 10.1049_iet-Pel.2010.0363] Jung, J.-h.; Ahmed, S. -- Flyback Converter With Novel Active Clamp Control and Secondary Side Post Regulator for Low Standby Power Consumption Under High](https://imgv2-2-f.scribdassets.com/img/document/220209509/149x198/8baf096670/1429428106?v=1)