Professional Documents

Culture Documents

Development of TSMC 0.25 M Standard Cell Library

Uploaded by

hex0x1Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Development of TSMC 0.25 M Standard Cell Library

Uploaded by

hex0x1Copyright:

Available Formats

Development of TSMC 0.

25m Standard Cell Library

Jeannette Donan Djigbenou, Thien Van Nguyen, Cheng Wei Ren, and Dong Sam Ha Virginia Tech VLSI for Telecommunications (VTVT) Group Bradley Department of Electrical and Computer Engineering Virginia Polytechnic Institute and State University Blacksburg, VA 24061 {jddjig01, thieng71, cren, ha}@vt.edu Abstract

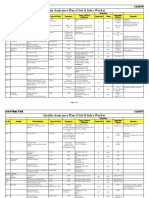

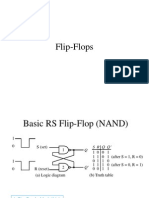

Standard library cells are basic building blocks for ASIC (Application-Specific Integrated Circuit) design, which improves designers productivity through reduced design time and debugging. In this paper, we present the development of a CMOS standard cell library by the VTVT (Virginia Tech for VLSI and Telecommunications) Lab. Keywords: VLSI design, CAD tools, Standard cell library. Table 1: List of VTVTs Representative Library Cells Cell Name Description Non-inverting buffer, drive buf_[1,2,4] strength 1, 2, or 4 inv_[1,2,4] Inverter, drive strength 1, 2 or 4 and3_[1,2,4] 3-input AND gate, drive strength 1, 2, or 4 2-input OR gate, drive strength 1, or2_[1,2,4] 2, or 4 nand4_[1,2,4] 4-input NAND gate, drive strength 1, 2, or 4 nor2_[1,2,4] 2 input NOR gate, drive strength 1, 2, or 4 xor2_[1,2] 2 input XOR gate, drive strength 1 or 2 xnor2_[1,2] 2 input XNOR gate, drive strength 1 or 2 mux2_[1,2,4] 2-to-1 multiplexer, drive strength 1, 2, or 4 fulladder One-bit ripple-carry adder, drive strength 1 invzp_[1,2,4] inverting tristate buffer, low enabled, drive strength 1, 2, or 4 ABnorC (ip1*ip2+ip3) drive strength 1 not_ab_or_c_or_d (ip1*ip2+ip3+ip4) drive strength 1 cd_16 clock driver, drive strength 16 lp_[1,2] high lrsp_[1, 2, 4] high dp_[1,2,4] rising drp_[1,2,4] active D latch, drive strength 1 or 2 active D latch with asynchronous low edge triggered D flip rising-edge triggered D flip-flop with asynchronous low-active reset (1, 2, or 4 drive strength) rising-edge triggered JK flip-flop with asynchronous active-low reset and extra inverted output, drive strength 2.

1. Introduction

Commercial library cells are companies proprietary information, and understandably, companies usually impose certain restrictions on the access and use of their library cells. Those restrictions on commercial library cells severely hamper VLSI research and teaching activities of academia. To address the problem, the VTVT (Virginia Tech for VLSI and Telecommunications) Lab of Virginia Tech has developed a TSMC 0.25 m CMOS standard cell library under the sponsorship of the National Science Foundation and distributed it to over 258 universities worldwide [1].

2. Features of VTVTs Standard Cell Library

The VTVTs cell library intends to support a cellbased VLSI design flow starting from a behavioral description to a layout. Specifically, it supports major tasks such as logic simulation and synthesis, place and routing (P&R), and layout versus schematic (LVS). The VTVTs cell library has been targeted and tested with Synopsys tools for logic simulation and synthesis, and with Cadence tools for P&R and physical design. It has 84 cells including both combinational and sequential cells with different drive strengths. Some of the representative cells are listed in Table 1. Figure 1 through Figure 3 show cell views of 2input AND gates with different driving strengths.

jkrp_2

1-4244-1029-0/07/$25.00 2007 IEEE.

566

dtsp_1

rising-edge triggered D flip-flop with asynchronous active high set input and serial scan input.

Figure 3: 2-input AND gate with driving strength 4

3. Cell Library Design

Figure 1: 2-input AND gate with driving strength 1 The major tasks for development of a cell library are: layout of cells, characterization, and LEF files generation. Our cells were laid out with Cadence Virtuoso and follow MOSIS DEEP rules (SCN5M_DEEP). TSMC 0.25 m CMOS technology supports 5 metal layers, but the layout of cells is limited to only two metal layers, metal 1 and metal 2. This constraint allows P&R tools to use the remaining metal layers for routing. In addition to the design rules, the layout of cells follows rules shown in Table 2, which are necessary for P&R.

Table 2: Rules for Cell Layouts Cell Design Settings Values Cell Height 108 Cell Width Multiple of 9 9 for metal 1 through Metal Pitch metal 4, 18 for metal 5 Metal Width 4 for all layers Metal Offset 0 for all layers Power/Ground Pins/Rails 11 for VDD and VSS Note: is 0.12 m.

Figure 2: 2-input AND gate with driving strength 2

Characterization of cells consists of capturing key parameters of cells such as propagation delay, rise and fall delays, and power dissipation. It was performed by extracting SPICE netlists from layouts and then simulating them using a SPICE simulator, HSPICE. The simulation results were ported into a .lib file and compiled by Synopsys Library Compiler for logic simulation and synthesis.

567

A LEF file for the cell library was generated for a P&R tool, specifically Cadence SOC Encounter. The extraction of abstract views and the generation of a LEF file were performed using Cadence Abstract. Mapping files, which enable Cadence Virtuoso to import the layouts from Cadence SOC Encounter, were generated manually based on the Cadence SOC Encounter mapping format.

5. Symbol Library

A symbol library allows users to view customized cell symbols rather than generic symbols, typically black boxes. Symbols were drawn using Cadence Virtuoso Schematic and Symbol editing tools. Then, symbols were exported into an EDIF file, which was compiled into an ASCII symbol library and eventually .sdb file using Synopsys Design Compiler, Figure 4 shows the process for generating a symbol library.

Export EDIF file from Cadence Environment (*.edif file) Generate ASCII Symbol Library file in Synopsys dc_shell (*.slib) Generate Symbol Library Database file in Synopsys dc_shell (*.sdb)

Figure 5: Design Flow Adopted by VTVT Lab

7. Summary

Figure 4: Generation of a Symbol Library A symbol library also allows synthesized designs to be exported back from the synthesis tools into CAD tools for further design verification. This process of verification is part of the design flow approach that has been used by the VTVT Lab to test and use the standard cell libraries. We presented basic features of TSMC 0.25 m CMOS standard cell library developed by the VTVT lab and the design flow. We plan to develop cell libraries for more advanced technologies such as TSMC 0.18 m and TSMC 0.10 m and RAM compilers in the next two years. Finally, any university can obtain our cell library at no cost. For details, refer to [1].

6. VTVTs Design Flow Using the Standard Cell Library

The design entry is a VHDL description, which is simulated and then synthesized into a gate level netlist in verilog. The verilog netlist is imported into Cadence ICFB as a schematic view, and Cadence SOC Encounter performs P&R and generates the P&R layout view. Finally, the layout is verified against the synthesized schematic. The design flow is shown in Figure 5. For details, refer to [2].

Acknowledgement:

This material is based upon work supported by the National Science Foundation under Grant No. 0551652.

References:

1. http://www.vtvt.ece.vt.edu/vlsidesign/cell.php 2. http://www.vtvt.ece.vt.edu/vlsidesign/designFlow. php

568

You might also like

- TSR 9440 - Ruined KingdomsDocument128 pagesTSR 9440 - Ruined KingdomsJulien Noblet100% (15)

- Quality Assurance Plan - CivilDocument11 pagesQuality Assurance Plan - CivilDeviPrasadNathNo ratings yet

- Using Ms-Dos 6.22Document1,053 pagesUsing Ms-Dos 6.22lorimer78100% (3)

- Latch-Up Prevention in CMOS Logics - Team VLSIDocument13 pagesLatch-Up Prevention in CMOS Logics - Team VLSIKaifeng LiuNo ratings yet

- Management of StutteringDocument182 pagesManagement of Stutteringpappu713100% (2)

- LabcbvDocument9 pagesLabcbvRAZNo ratings yet

- Cognitive Coaching AdelaideDocument3 pagesCognitive Coaching AdelaideBusiness-Edu100% (2)

- Asic Design Cadence DR D Gracia Nirmala RaniDocument291 pagesAsic Design Cadence DR D Gracia Nirmala RaniAdline RiniNo ratings yet

- Latch UpDocument3 pagesLatch UpKishore CkNo ratings yet

- MOSFET Scaling: Dr. Rajan Pandey Associate Professor, SENSEDocument6 pagesMOSFET Scaling: Dr. Rajan Pandey Associate Professor, SENSEVibha M VNo ratings yet

- ThriuuuDocument46 pagesThriuuuThiruNo ratings yet

- Cell Characterization ConceptsDocument70 pagesCell Characterization Conceptshex0x1No ratings yet

- 10-Bit C2C DAC Design in 65nm CMOS TechnologyDocument88 pages10-Bit C2C DAC Design in 65nm CMOS TechnologyRodrigo SantosNo ratings yet

- Integrated Management System 2016Document16 pagesIntegrated Management System 2016Mohamed HamedNo ratings yet

- Kpolovie and Obilor PDFDocument26 pagesKpolovie and Obilor PDFMandalikaNo ratings yet

- CMOS Power Dissipation and Trends: R. AmirtharajahDocument60 pagesCMOS Power Dissipation and Trends: R. AmirtharajahmarshaldvtNo ratings yet

- Low-Power VlsiDocument110 pagesLow-Power Vlsisweet2shineNo ratings yet

- DDRDocument9 pagesDDRnivinNo ratings yet

- Yocto TutorialDocument16 pagesYocto Tutorialhex0x1No ratings yet

- Product How To Fully Utilize TSMC S 28HPC ProcessDocument8 pagesProduct How To Fully Utilize TSMC S 28HPC ProcessvpsampathNo ratings yet

- Smic Confidential: Semiconductor Manufacturing International CorporationDocument282 pagesSmic Confidential: Semiconductor Manufacturing International CorporationMarshall100% (1)

- 018 RF Model Document V2d2Document91 pages018 RF Model Document V2d2Rogelio Manuel Higuera GonzalezNo ratings yet

- VLSI TrendsDocument18 pagesVLSI TrendsShibendu BhowmickNo ratings yet

- IO Design, ESDDocument18 pagesIO Design, ESDashishmanyanNo ratings yet

- Silicon On Insulator TechnologyDocument32 pagesSilicon On Insulator TechnologyJayanth bemesettyNo ratings yet

- Signal and Design Integrity: Cadence Design Systems, IncDocument56 pagesSignal and Design Integrity: Cadence Design Systems, IncJyothi Nath100% (1)

- PD FlowDocument6 pagesPD FlowUTtNo ratings yet

- Corporate Members List Iei Mysore Local CentreDocument296 pagesCorporate Members List Iei Mysore Local CentreNagarjun GowdaNo ratings yet

- Vlsi Design AutomationDocument31 pagesVlsi Design AutomationNischita KeerthiNo ratings yet

- Vector-Based Peak Current Analysis During Wafer Test of Flip-Chip DesignsDocument206 pagesVector-Based Peak Current Analysis During Wafer Test of Flip-Chip DesignsLakshman YandapalliNo ratings yet

- Evidence Based Practice in Nursing Healthcare A Guide To Best Practice 3rd Edition Ebook PDFDocument62 pagesEvidence Based Practice in Nursing Healthcare A Guide To Best Practice 3rd Edition Ebook PDFwilliam.tavares69198% (50)

- Exam Ref 70 483 Programming in C by Wouter de Kort PDFDocument2 pagesExam Ref 70 483 Programming in C by Wouter de Kort PDFPhilNo ratings yet

- SOIDocument25 pagesSOIDavis AbrahamNo ratings yet

- ASHRAE Final Operating Room 508 PDFDocument13 pagesASHRAE Final Operating Room 508 PDFSilisteanu AndreiNo ratings yet

- Single-Mask Double-Patterning Lithography: Rani S. Ghaida, George Torres, and Puneet GuptaDocument21 pagesSingle-Mask Double-Patterning Lithography: Rani S. Ghaida, George Torres, and Puneet GuptaRenju TjNo ratings yet

- TSMC AdvdDocument9 pagesTSMC AdvdsidramareddyNo ratings yet

- XilinxDocument20 pagesXilinxAvila Cruz JaimeNo ratings yet

- How To Use Composite Current Source Modeling For Crosstalk Noise AnalysisDocument12 pagesHow To Use Composite Current Source Modeling For Crosstalk Noise AnalysisStudentNo ratings yet

- Chapter A 1Document3 pagesChapter A 1Kiran ShettyNo ratings yet

- Mississippi State University Dallas Semiconductor: Standard Cell TutorialDocument133 pagesMississippi State University Dallas Semiconductor: Standard Cell Tutorialthink_ashokgargNo ratings yet

- Flip FlopsDocument25 pagesFlip FlopsNagul MeeraNo ratings yet

- Chapter 4Document100 pagesChapter 4khgvouy hvogyflNo ratings yet

- DDR SdramDocument36 pagesDDR Sdramajmalpm333No ratings yet

- Willson MirrorDocument7 pagesWillson Mirrorsandeep_mastiNo ratings yet

- Antenna Diode Vlsi Operation Positive ChargeDocument21 pagesAntenna Diode Vlsi Operation Positive ChargeNegin HashemiNo ratings yet

- 4G WirelessDocument4 pages4G Wirelessaminkhan83No ratings yet

- TSMC 180 NMDocument5 pagesTSMC 180 NMtsmc12345No ratings yet

- Lec20 RTL DesignDocument40 pagesLec20 RTL DesignPrabhu_gudimaneNo ratings yet

- Mod1VLSI TECHNOLOGY1Document65 pagesMod1VLSI TECHNOLOGY1Jomon VargheseNo ratings yet

- Vlsi FabDocument8 pagesVlsi FabhaheNo ratings yet

- Expanding The Synopsys Primetime Solution With Power AnalysisDocument7 pagesExpanding The Synopsys Primetime Solution With Power AnalysisRamakrishnaRao SoogooriNo ratings yet

- Techfile Vs TLUPlus File Extraction Difference in ICCDocument2 pagesTechfile Vs TLUPlus File Extraction Difference in ICCrashmi sNo ratings yet

- 32k-Bit Sleepy SramDocument18 pages32k-Bit Sleepy Sramapi-19668941No ratings yet

- Timing Aware Dummy Metal Fill MethodologyDocument3 pagesTiming Aware Dummy Metal Fill MethodologyraveneyesdeadNo ratings yet

- CMOSedu PDFDocument1 pageCMOSedu PDFJorge SequeiraNo ratings yet

- Physical DesignDocument52 pagesPhysical Designsandyp21No ratings yet

- Gsa Dac 2011 3dic GuideDocument62 pagesGsa Dac 2011 3dic Guideyucl_98792No ratings yet

- Vlsi Design Test and TestabilityDocument17 pagesVlsi Design Test and TestabilitySuravarapu ArunaNo ratings yet

- System On Chip SoC ReportDocument14 pagesSystem On Chip SoC Reportshahd dawood100% (1)

- CMFB DesignDocument4 pagesCMFB Designaminkhan83No ratings yet

- Ccs Power Char Guide 081216Document35 pagesCcs Power Char Guide 081216刘振声No ratings yet

- Migration in Solid State MaterialsDocument15 pagesMigration in Solid State MaterialsNitin PatelNo ratings yet

- EE520 ASIC Design PDFDocument44 pagesEE520 ASIC Design PDFthiendoan_bkNo ratings yet

- LamdaDocument23 pagesLamdaparrotpanduNo ratings yet

- Webinar 60-GHz RDK Agilent-TSMC 03may2012 FinalDocument43 pagesWebinar 60-GHz RDK Agilent-TSMC 03may2012 FinalusrppriyankaNo ratings yet

- Asic Design Flow (PD Flow)Document34 pagesAsic Design Flow (PD Flow)ShwethNo ratings yet

- Level Shifter PDFDocument6 pagesLevel Shifter PDFKAMARUDHEEN KPNo ratings yet

- A Seminar Report On Vlsi FloorplanningDocument17 pagesA Seminar Report On Vlsi FloorplanningPARAG100% (1)

- PrimeTime 2011 Webinar-Advanced OCVDocument32 pagesPrimeTime 2011 Webinar-Advanced OCVSourabh Aditya SwarnkarNo ratings yet

- Synopsys Open Educational Design KitDocument5 pagesSynopsys Open Educational Design KitAbhishek AvNo ratings yet

- AnswersDocument24 pagesAnswershex0x1No ratings yet

- A 4thOrder Continuous-Time ΔΣADCDocument30 pagesA 4thOrder Continuous-Time ΔΣADChex0x1No ratings yet

- Yocto Project Quick StartDocument5 pagesYocto Project Quick Starthex0x1No ratings yet

- UNP NoiseDocument12 pagesUNP Noisejofinjv3194No ratings yet

- Presentation Marking TableDocument1 pagePresentation Marking Tablehex0x1100% (1)

- PCBDesign ParametersDocument24 pagesPCBDesign Parametersthe1969bulldogNo ratings yet

- 1996 08Document18 pages1996 08hex0x1No ratings yet

- Data ReceptacleDocument1 pageData Receptaclehex0x1No ratings yet

- Vlsi Lab Manual PDFDocument73 pagesVlsi Lab Manual PDFpathmakerpkNo ratings yet

- CH 19Document7 pagesCH 19vijeyezNo ratings yet

- Tutorial COFDMDocument43 pagesTutorial COFDMSara YaserNo ratings yet

- Using Ipc Temp ChartsDocument5 pagesUsing Ipc Temp Chartshex0x1No ratings yet

- WWW - Iis.ee - Ethz.ch Stud Area Vorlesungen Aic Uebungen Uebung6 Aktuell Uebung6Document10 pagesWWW - Iis.ee - Ethz.ch Stud Area Vorlesungen Aic Uebungen Uebung6 Aktuell Uebung6hex0x1No ratings yet

- How To Convert A Project From CDB To OADocument3 pagesHow To Convert A Project From CDB To OAhex0x1No ratings yet

- Description Features: Ltc2942 Battery Gas Gauge With Temperature, Voltage MeasurementDocument18 pagesDescription Features: Ltc2942 Battery Gas Gauge With Temperature, Voltage Measurementhex0x1No ratings yet

- Switching Charger For 1-Cell and 2-Cell Li-Ion Batteries: ISL9220, ISL9220ADocument15 pagesSwitching Charger For 1-Cell and 2-Cell Li-Ion Batteries: ISL9220, ISL9220Ahex0x1No ratings yet

- PCBDesign ParametersDocument24 pagesPCBDesign Parametersthe1969bulldogNo ratings yet

- CC 3000Document17 pagesCC 3000Sát Thủ Vô TìnhNo ratings yet

- Par Soc EncounterDocument24 pagesPar Soc EncounterRavi Kumar DasariNo ratings yet

- Yocto Project Board Support Package Developer's GuideDocument14 pagesYocto Project Board Support Package Developer's Guidehex0x1No ratings yet

- Design SpaceDocument184 pagesDesign Spacehex0x1No ratings yet

- 3 The Wiener FilterDocument15 pages3 The Wiener FilterManish VohraNo ratings yet

- BSN SummaryDocument6 pagesBSN Summaryhex0x1No ratings yet

- Clock CrossingDocument7 pagesClock CrossingPradeep Manigandan100% (1)

- 3 The Wiener FilterDocument15 pages3 The Wiener FilterManish VohraNo ratings yet

- Science City Showcase Event: Research Group News Power Electronics, Machines & Drives GroupDocument4 pagesScience City Showcase Event: Research Group News Power Electronics, Machines & Drives Grouphex0x1No ratings yet

- Comparison of Multi-Coil and Diaphragm Spring ClutchesDocument3 pagesComparison of Multi-Coil and Diaphragm Spring Clutchesmasb_994077No ratings yet

- ISP SFD PDFDocument73 pagesISP SFD PDFNamo SlimanyNo ratings yet

- Turbine Flowmeters-Commonly Asked Questions and Answers: For Chemical Composition Information.)Document8 pagesTurbine Flowmeters-Commonly Asked Questions and Answers: For Chemical Composition Information.)Alexander KlmNo ratings yet

- LNWH Alcohol GUIDELINE SUMMARY 2018Document1 pageLNWH Alcohol GUIDELINE SUMMARY 2018Ai Hwa LimNo ratings yet

- 0n9) O6..,w48j-GDocument14 pages0n9) O6..,w48j-GMocha FurrerNo ratings yet

- Pepsi Mix Max Mox ExperimentDocument2 pagesPepsi Mix Max Mox Experimentanon_192325873No ratings yet

- Unit 6B - PassiveDocument18 pagesUnit 6B - PassiveDavid EstrellaNo ratings yet

- Know Your TcsDocument8 pagesKnow Your TcsRocky SinghNo ratings yet

- Class 12 Unit-2 2022Document4 pagesClass 12 Unit-2 2022Shreya mauryaNo ratings yet

- Vmware It Academy Program May2016Document26 pagesVmware It Academy Program May2016someoneNo ratings yet

- Excel Lesson 5 QuizDocument5 pagesExcel Lesson 5 Quizdeep72No ratings yet

- Submitted By: S.M. Tajuddin Group:245Document18 pagesSubmitted By: S.M. Tajuddin Group:245KhurshidbuyamayumNo ratings yet

- 7 Ways To Support Your Babys Learning Today Monti KidsDocument19 pages7 Ways To Support Your Babys Learning Today Monti KidsMareim A HachiNo ratings yet

- State Common Entrance Test Cell: 3001 Jamnalal Bajaj Institute of Management Studies, MumbaiDocument9 pagesState Common Entrance Test Cell: 3001 Jamnalal Bajaj Institute of Management Studies, MumbaiSalman AnwarNo ratings yet

- La La Mei Seaside Resto BAR: Final PlateDocument4 pagesLa La Mei Seaside Resto BAR: Final PlateMichael Ken FurioNo ratings yet

- Week1 TutorialsDocument1 pageWeek1 TutorialsAhmet Bahadır ŞimşekNo ratings yet

- New Client QuestionnaireDocument13 pagesNew Client QuestionnairesundharNo ratings yet

- Promotion of Coconut in The Production of YoghurtDocument4 pagesPromotion of Coconut in The Production of YoghurtԱբրենիկա ՖերլինNo ratings yet

- Color Coding Chart - AHGDocument3 pagesColor Coding Chart - AHGahmedNo ratings yet