Professional Documents

Culture Documents

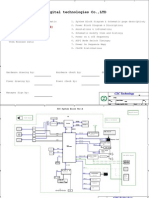

PBL10 Project Compal Confidential: LA-6731P Schematic REV1.0

Uploaded by

AssiseletroOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

PBL10 Project Compal Confidential: LA-6731P Schematic REV1.0

Uploaded by

AssiseletroCopyright:

Available Formats

5

Compal Confidential

s

e

.

PBL10 Project

e

s

er

iv

n

U

LA-6731P REV1.0

Schematic

k

o

o

b

e

t

o

Intel

Bridge/Cougar Point(UMA)

N Sandy2010-12-06

Rev 1.0

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2010/05/17

Issued Date

Deciphered Date

2011/05/17

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

SCHEMATICS,MB A6731

Document Number

Rev

D

401968

Wednesday, March 09, 2011

Sheet

1

of

45

CK505

Compal Confidential

Model Name : PBL10

File Name : LA-6731P

Fan Control

page 5

Clock Generator

ICS9LRS Page 14

Mobile Sandy Bridge

CPU Dual Core

Memory BUS(DDRIII)

Socket-rPGA989

page 5,6,7,8,9,10,11

37.5mm*37.5mm

204pin DDRIII-SO-DIMM X2

Dual Channel

DMI X4

1.5V DDRIII 1066/1333

BANK 0, 1, 2, 3

FDI X4

LCD Conn.

USB/B Right USB/B Left

page 15

USB port 0,1

USB port 2

s

e

.

page 29

CRT

page 16

page 17

RTS5138 3IN1

USB port 11

USB port 3

page 15

Intel Cougar Point

page 17

FCBGA989

25mm*25mm

PCIeMini Card

WLAN & BT 2.0

o

b

te

USB port 5

PCIe port 2

page 29

RJ45

USB&Audio/B

page 30

page 29

Power/B

o

N

RTL8111E Giga

RTL8105E 10/100

PCIe 1x

SATA port 1

U

k

o

USB

5V 1.5GHz(150MB/s)

SATA port 4

5V 1.5GHz(150MB/s)

1.5V 2.5GHz(250MB/s)

page 29

Int. Camera

e

s

r

e

niv

USB

HDMI

Level Shifter

HDMI Conn.

page 12,13

page 32

SATA HDD0

page 27

SATA ODD

page 27

SPI ROM

page 28

B

PCIe 1x

1.5V 2.5GHz(250MB/s)

page 18,19,20,21

22,23,24,25,26

PCIe port 3

page 30

HD Audio

3.3V 24.576MHz/48Mhz

HDA Codec

page 34

ALC259

page 31

Touch Pad/B

page 34

ENE KB930

page 33

RTC CKT.

Int.

MIC CONN

page 15

page 36

DC/DC Interface CKT.

page 32

2010/05/17

Issued Date

Deciphered Date

Compal Electronics, Inc.

2011/05/17

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

page 36,37,38,39,

40,41,42,43,44

Date:

SPK CONN

page 31

page 32

Compal Secret Data

Security Classification

Power Circuit DC/DC

HP CONN

page 29

SPI ROM

Int.KBD

page 35

MIC CONN

page 29

SCHEMATICS,MB A6731

Document Number

Rev

D

401968

Wednesday, March 09, 2011

Sheet

1

of

45

POK

B+

+3VL

+5VL

+5VALW

UP6182CQAG

B+

+VSB

TP0610K

+CPU_CORE

SUSP

ISL95831CRZ

+5VS

SI4800BDY

+VGFX_CORE

SYSON

+HDMI_5V_OUT

RB161M

+1.5V

G5603RU1U

SUSP

+CRT_VCC

RB491D

USB_EN#

SUSP#

USB_EN#

+USB_VCCB

RT9715BGS

SUSP

e

v

i

SUSP#

UP7711U8

+1.8VS

SY8033BDBC

n

U

k

o

o

b

+3VALW

PCH_PWR_EN#

SI4800BDY

+0.75VS

SUSP#

G5603RU1U

+VCCSA

+3VALW_PCH

e

t

o

N

VGA_ENVDD

+1.05VS_VCCP

e

s

r

G5603RU1U

SUSP

s

e

.

+USB_VCCA

RT9715BGS

SI4800BDY

+1.5VS

SI4856ADY

AO3413

+3VS

+LCD_VDD

+3V_LAN

2010/05/17

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2011/05/17

Deciphered Date

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

SCHEMATICS,MB A6731

Document Number

Rev

D

401968

Wednesday, March 09, 2011

Sheet

1

of

45

Voltage Rails

Power Plane

Description

EC SM Bus1 address

S1

S3

S5

VIN

Adapter power supply (19V)

N/A

N/A

N/A

BATT+

Battery power supply (12.6V)

N/A

N/A

N/A

B+

AC or battery power rail for power circuit.

N/A

N/A

N/A

+CPU_CORE

Core voltage for CPU

ON

OFF

OFF

+VGA_CORE

Core voltage for GPU

ON

OFF

OFF

+VGFX_CORE

Core voltage for UMA graphic

ON

OFF

OFF

+0.75VS

+0.75VP to +0.75VS switched power rail for DDR terminator

ON

OFF

OFF

+1.0VSDGPU

+1.0VSPDGPU to +1.0VSDGPU switched power rail for GPU

ON

OFF

OFF

+1.05VS_VCCP

+1.05VS_VCCPP to +1.05VS_VCCP switched power rail for CPU

ON

OFF

OFF

+1.05VS_PCH

+1.05VS_VCCP to +1.05VS_PCH power for PCH

ON

OFF

OFF

+1.5V

+1.5VP to +1.5V power rail for DDRIII

ON

ON

OFF

+1.5VS

+1.5V to +1.5VS switched power rail

ON

OFF

OFF

+1.5VSDGPU

+1.5VS to +1.5VSDGPU switched power rail for GPU

ON

OFF

OFF

+1.8VS

(+5VALW or +3VALW) to 1.8V switched power rail to PCH & GPU ON

OFF

OFF

+3VALW

+3VALW always on power rail

ON

ON

ON*

+3VALW_EC

+3VALW always to KBC

ON

ON

ON*

+3V_LAN

+3VALW to +3V_LAN power rail for LAN

ON

ON

ON*

+3VALW_PCH

+3VALW to +3VALW_PCH power rail for PCH (Short Jumper)

ON

ON

ON*

+3VS

+3VALW to +3VS power rail

ON

OFF

OFF

+5VALW

+5VALWP to +5VALW power rail

ON

ON

ON*

+5VALW_PCH

+5VALW to +5VALW_PCH power rail for PCH (Short resister)

ON

ON

ON*

+5VS

+5VALW to +5VS switched power rail

ON

OFF

OFF

+VSB

+VSBP to +VSB always on power rail for sequence control

ON

ON

ON*

+RTCVCC

RTC power

ON

ON

ON

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

STATE

HIGH

HIGH

HIGH

HIGH

S1(Power On Suspend)

LOW

HIGH

HIGH

HIGH

S3 (Suspend to RAM)

LOW

LOW

HIGH

HIGH

S4 (Suspend to Disk)

LOW

LOW

LOW

HIGH

S5 (Soft OFF)

LOW

LOW

LOW

LOW

Full ON

SLP_S1# SLP_S3# SLP_S4# SLP_S5#

+VS

Clock

ON

ON

ON

ON

e

t

o

N

ON

ON

ON

OFF

ON

OFF

OFF

ON

OFF

OFF

Device

Device

Address

Clock Generator (9LVS3199AKLFT,

RTM890N-631-VB-GRT)

1101 0010b

DDR DIMM0

1001 000Xb

DDR DIMM2

1001 010Xb

BOM configu table

SKU

Bom config

46196830L01

DA6@/HDMI@/8105E@/PCH@

46196830L02

s

r

e

v

ni

3

4

DA6@/HDMI@/8111E@/PCH@

U

k

o

o

b

+V

ON

0001 011X b

7

8

s

e

e.

LOW

Bom configu(HDMI@/8105E@/8111E@/DA6@/DAZ@/45@)

OFF

PCH And PCBA table

OFF

OFF

Address

PCH SM Bus address

+VALW

ON

Address

Smart Battery

SIGNAL

Device

EC SM Bus2 address

Description

C

PBL10 UMA DUAL 10-100

PBL10 UMA DUAL GIGA LAN

U4

BD82HM65 SLH9D B2 FCBGA 989P PCH

PCH@

PCH

ZZZ

DAZ@

ZZZ

DA6@

ZZZ

DA4@

ZZZ

DA2@

PCB

PCB LA-6731P REV10

PCB LA-6731P REV10

PCB LS-6732P REV10

PCB LS-6731P REV10

Compal Secret Data

Security Classification

Issued Date

2010/05/17

2011/05/17

Deciphered Date

Title

Compal Electronics, Inc.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

Custom

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

SCHEMATICS,MB A6731

Rev

D

401968

Date:

Wednesday, March 09, 2011

Sheet

1

of

45

H_PM_SYNC

PM_SYS_PWRGD_BUF

BUF_CPU_RST#

T5

23,33

2@

0.1U_0402_16V4Z

2@

0.1U_0402_16V4Z

1

C238

1

C243

H_PECI

1 62_0402_5%

H_CATERR#

H_PECI_ISO

1

10K_0402_5%

23 H_THRMTRIP#

R54

0_0402_5%

1

2

H_THEMTRIP#_R

AN32

THERMTRIP#

20 H_PM_SYNC

23 H_CPUPWRGD

R64

0_0402_5%

1

2

H_PM_SYNC_R

H_CPUPWRGD_R

R60

75_0402_5%

U2

R66

43_0402_1%

1

2 BUF_CPU_RST#

BUFO_CPU_RST#

NC

A

e

t

o

N

+1.05VS_VCCP

C82

0.1U_0402_16V4Z

SN74LVC1G07DCKR_SC70-5

@

R68

0_0402_5%

UNCOREPWRGOOD

SM_DRAMPWROK

AR33

RESET#

20 PM_DRAM_PWRGD

33

+1.5V_CPU_VDDQ

EN_DFAN1

10mil

+1.05VS_VCCP

H_DRAMRST# 7

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

AK1

A5

A4

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PRDY#

PREQ#

AP29

AP27

TCK

TMS

TRST#

AR26

AR27

AP30

XDP_TCK

XDP_TMS

XDP_TRST#

TDI

TDO

AR28

AP26

XDP_TDI_R

XDP_TDO_R

s

e

.

SM_RCOMP0 R49

1 140_0402_1%

SM_RCOMP1 R51

1 25.5_0402_1%

SM_RCOMP2 R53

1 200_0402_1%

XDP_TMS

e

s

r

e

v

ni

DBR#

AL35

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

AT28

AR29

AR30

AT30

AP32

AR31

AT31

AR32

+1.05VS_VCCP

R55

1 51_0402_5%

XDP_TDI_R R56

1 51_0402_5%

XDP_TDO_R R57

1 51_0402_5%

XDP_TCK

R59

1 51_0402_5%

XDP_TRST# R62

1 51_0402_5%

R266 1K_0402_5%

1

2

+3VS

XDP_DBRESET#

XDP_DBRESET# 18,20

JFAN

1

U3

74AHC1G09GW_TSSOP5

R81

200_0402_5%

EN

VIN

VOUT

VSET

+FAN1

1

2

3

1

2

3

@ C864

@C864

1000P_0402_50V7K

4

5

GND

GND

2

GND

GND

GND

GND

8

7

6

5

ACES_85205-03001

CONN@

G996P11U SOP 8P

C17

10U_0805_10V4Z

R219

2

10K_0402_5%

1

+3VS

FAN_SPEED1 33

PM_SYS_PWRGD_BUF

G

3

C865@

0.01U_0402_25V7K

20 SYS_PWROK

1 2

@

R83

39_0402_5%

35,42

SUSP

SUSP

Compal Secret Data

Security Classification

D

2

G

3

1

2

3

4

+FAN1

CLK_CPU_DMI 19

CLK_CPU_DMI# 19

2

C863

10U_0805_10V4Z

+3VALW

R82

0_0402_5%

1

2

2 0_0402_5%

2 0_0402_5%

1A

U58

C83

0.1U_0402_16V4Z

CLK_BUF_CPU_BCLK 14

CLK_BUF_CPU_BCLK# 14

FAN Control Circuit

PLT_RST# 22,29,30,33

Follow DG 0.71

2 0_0402_5%

2 0_0402_5%

+5VS

PLT_RST# 2

V8

PM_SYNC

Sandy Bridge_rPGA_Rev1p0

CONN@

Buffered reset to CPU

AP33

1

1

2 1K_0402_5%

2 1K_0402_5%

H_DRAMRST#

R8

SM_DRAMRST#

U

k

o

o

b

H_CPUPWRGD_R

2

330P_0402_50V7K

CLOSE TO PCH, EMI DEMAND

+3VS

AM34

R43

R44

@

@

PU/PD for JTAG signals

H_PROCHOT#

PECI

PROCHOT#

R58

0_0402_5%

1

2

A16 R234 1

A15 R240 1

DPLL_REF_CLK

DPLL_REF_CLK#

1

1

DDR3 Compensation Signals

AL32

R65

130_0402_5%

PM_SYS_PWRGD_BUF 1

2 PM_DRAM_PWRGD_R

1

C312

AN33

CLK_CPU_DMI_R

CLK_CPU_DMII#_R

A28

A27

R41

R42

CATERR#

H_PROCHOT#_R

BUF_CPU_RST#

2

R50

AL33

SKTOCC#

33 H_PROCHOT#

Processor Pullups

2

AN34

R52

56_0402_5%

1

2

R47

PAD

R48

0_0402_5%

1

2

EMI Demand

+1.05VS_VCCP

SKTOCC#

CLOCKS

H_THRMTRIP#

PAD

DDR3

MISC

2@

0.1U_0402_16V4Z

2@

0.1U_0402_16V4Z

2@

0.1U_0402_16V4Z

1

C234

1

C235

1

C236

BCLK

BCLK#

JTAG & BPM

T68

H_PROCHOT#

PROC_SELECT#

THERMAL

C26

22 H_SNB_IVB#

PWR MANAGEMENT

MISC

JCPUB

@

Q4

2N7002_SOT23

Issued Date

2010/05/17

2011/05/17

Deciphered Date

Title

Compal Electronics, Inc.

SCHEMATICS,MB A6731

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Rev

D

401968

Date:

Sheet

Wednesday, March 09, 2011

1

of

45

+1.05VS_VCCP

20

20

20

20

DMI_CRX_PTX_P0

DMI_CRX_PTX_P1

DMI_CRX_PTX_P2

DMI_CRX_PTX_P3

B28

B26

A24

B23

DMI_RX[0]

DMI_RX[1]

DMI_RX[2]

DMI_RX[3]

20

20

20

20

DMI_CTX_PRX_N0

DMI_CTX_PRX_N1

DMI_CTX_PRX_N2

DMI_CTX_PRX_N3

G21

E22

F21

D21

DMI_TX#[0]

DMI_TX#[1]

DMI_TX#[2]

DMI_TX#[3]

20

20

20

20

DMI_CTX_PRX_P0

DMI_CTX_PRX_P1

DMI_CTX_PRX_P2

DMI_CTX_PRX_P3

G22

D22

F20

C21

DMI_TX[0]

DMI_TX[1]

DMI_TX[2]

DMI_TX[3]

20

20

20

20

20

20

20

20

FDI_CTX_PRX_N0

FDI_CTX_PRX_N1

FDI_CTX_PRX_N2

FDI_CTX_PRX_N3

FDI_CTX_PRX_N4

FDI_CTX_PRX_N5

FDI_CTX_PRX_N6

FDI_CTX_PRX_N7

A21

H19

E19

F18

B21

C20

D18

E17

FDI0_TX#[0]

FDI0_TX#[1]

FDI0_TX#[2]

FDI0_TX#[3]

FDI1_TX#[0]

FDI1_TX#[1]

FDI1_TX#[2]

FDI1_TX#[3]

20

20

20

20

20

20

20

20

FDI_CTX_PRX_P0

FDI_CTX_PRX_P1

FDI_CTX_PRX_P2

FDI_CTX_PRX_P3

FDI_CTX_PRX_P4

FDI_CTX_PRX_P5

FDI_CTX_PRX_P6

FDI_CTX_PRX_P7

A22

G19

E20

G18

B20

C19

D19

F17

FDI0_TX[0]

FDI0_TX[1]

FDI0_TX[2]

FDI0_TX[3]

FDI1_TX[0]

FDI1_TX[1]

FDI1_TX[2]

FDI1_TX[3]

20 FDI_FSYNC0

20 FDI_FSYNC1

J18

J17

FDI0_FSYNC

FDI1_FSYNC

20 FDI_INT

H20

FDI_INT

20 FDI_LSYNC0

20 FDI_LSYNC1

J19

H17

FDI0_LSYNC

FDI1_LSYNC

R185 1

A18

A17

B16

eDP_COMPIO

eDP_ICOMPO

eDP_HPD

C15

D15

eDP_AUX

eDP_AUX#

C17

F16

C16

G15

eDP_TX[0]

eDP_TX[1]

eDP_TX[2]

eDP_TX[3]

C18

E16

D16

F15

eDP_TX#[0]

eDP_TX#[1]

eDP_TX#[2]

eDP_TX#[3]

2 1K_0402_5%

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

J22

J21

H22

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

K33

M35

L34

J35

J32

H34

H31

G33

G30

F35

E34

E32

D33

D31

B33

C32

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

J33

L35

K34

H35

H32

G34

G31

F33

F30

E35

E33

F32

D34

E31

C33

B32

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

M29

M32

M31

L32

L29

K31

K28

J30

J28

H29

G27

E29

F27

D28

F26

E25

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

M28

M33

M30

L31

L28

K30

K27

J29

J27

H28

G28

E28

F28

D27

E26

D25

PEG_COMP

s

e

.

e

s

r

e

niv

U

k

o

o

b

e

t

o

N

EDP_COMP

+1.05VS_VCCP

DMI

DMI_RX#[0]

DMI_RX#[1]

DMI_RX#[2]

DMI_RX#[3]

Intel(R) FDI

B27

B25

A25

B24

PCI EXPRESS* - GRAPHICS

R18

24.9_0402_1%

2

eDP_COMPIO and ICOMPO signals

should be shorted near balls

and routed with typical

impedance <25 mohms

+1.05VS_VCCP

DMI_CRX_PTX_N0

DMI_CRX_PTX_N1

DMI_CRX_PTX_N2

DMI_CRX_PTX_N3

eDP

20

20

20

20

PEG_ICOMPI and RCOMPO signals should be

shorted and routed

with - max length = 500 mils - typical

impedance = 43 mohms

PEG_ICOMPO signals should be routed with max length = 500 mils

- typical impedance = 14.5 mohms

R17

24.9_0402_1%

JCPUA

Sandy Bridge_rPGA_Rev1p0

CONN@

Compal Secret Data

Security Classification

Issued Date

2010/05/17

2011/05/17

Deciphered Date

Title

Compal Electronics, Inc.

SCHEMATICS,MB A6731

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Rev

D

401968

Date:

Sheet

Wednesday, March 09, 2011

1

of

45

JCPUC

JCPUD

12 DDR_A_BS0

12 DDR_A_BS1

12 DDR_A_BS2

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

AE10

AF10

V6

SA_BS[0]

SA_BS[1]

SA_BS[2]

AE8

AD9

AF9

SA_CAS#

SA_RAS#

SA_WE#

12 DDR_A_CAS#

12 DDR_A_RAS#

12 DDR_A_WE#

SA_CLK[0]

SA_CLK#[0]

SA_CKE[0]

AB6

AA6

V9

M_CLK_DDR0 12

M_CLK_DDR#0 12

DDR_CKE0_DIMMA 12

SA_CLK[1]

SA_CLK#[1]

SA_CKE[1]

AA5

AB5

V10

M_CLK_DDR1 12

M_CLK_DDR#1 12

DDR_CKE1_DIMMA 12

RSVD_TP[1]

RSVD_TP[2]

RSVD_TP[3]

AB4

AA4

W9

RSVD_TP[4]

RSVD_TP[5]

RSVD_TP[6]

AB3

AA3

W10

SA_CS#[0]

SA_CS#[1]

RSVD_TP[7]

RSVD_TP[8]

AK3

AL3

AG1

AH1

DDR_CS0_DIMMA# 12

DDR_CS1_DIMMA# 12

SA_ODT[0]

SA_ODT[1]

RSVD_TP[9]

RSVD_TP[10]

AH3

AG3

AG2

AH2

M_ODT0 12

M_ODT1 12

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

C4

G6

J3

M6

AL6

AM8

AR12

AM15

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

D4

F6

K3

N6

AL5

AM9

AR11

AM14

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDR_A_DQS[0..7]

DDR_A_MA[0..15]

12

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

C9

A7

D10

C8

A9

A8

D9

D8

G4

F4

F1

G1

G5

F5

F2

G2

J7

J8

K10

K9

J9

J10

K8

K7

M5

N4

N2

N1

M4

N5

M2

M1

AM5

AM6

AR3

AP3

AN3

AN2

AN1

AP2

AP5

AN9

AT5

AT6

AP6

AN8

AR6

AR5

AR9

AJ11

AT8

AT9

AH11

AR8

AJ12

AH12

AT11

AN14

AR14

AT14

AT12

AN15

AR15

AT15

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

AE2

AD2

R9

M_CLK_DDR2 13

M_CLK_DDR#2 13

DDR_CKE2_DIMMB 13

SB_CLK[1]

SB_CLK#[1]

SB_CKE[1]

AE1

AD1

R10

M_CLK_DDR3 13

M_CLK_DDR#3 13

DDR_CKE3_DIMMB 13

RSVD_TP[11]

RSVD_TP[12]

RSVD_TP[13]

AB2

AA2

T9

RSVD_TP[14]

RSVD_TP[15]

RSVD_TP[16]

AA1

AB1

T10

SB_CS#[0]

SB_CS#[1]

RSVD_TP[17]

RSVD_TP[18]

AD3

AE3

AD6

AE6

DDR_CS2_DIMMB# 13

DDR_CS3_DIMMB# 13

SB_ODT[0]

SB_ODT[1]

RSVD_TP[19]

RSVD_TP[20]

AE4

AD4

AD5

AE5

M_ODT2 13

M_ODT3 13

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

D7

F3

K6

N3

AN5

AP9

AK12

AP15

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

C7

G3

J6

M3

AN6

AP8

AK11

AP14

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

AA8

T7

R7

T6

T2

T4

T3

R2

T5

R3

AB7

R1

T1

AB10

R5

R4

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

s

e

.

e

s

r

e

niv

12

U

k

o

o

b

e

t

o

N

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AD10

W1

W2

W7

V3

V2

W3

W6

V1

W5

AD8

V4

W4

AF8

V5

V7

DDR_A_DQS#[0..7]

SB_CLK[0]

SB_CLK#[0]

SB_CKE[0]

13 DDR_B_D[0..63]

12

13 DDR_B_BS0

13 DDR_B_BS1

13 DDR_B_BS2

13 DDR_B_CAS#

13 DDR_B_RAS#

13 DDR_B_WE#

Sandy Bridge_rPGA_Rev1p0

CONN@

AA9

AA7

R6

SB_BS[0]

SB_BS[1]

SB_BS[2]

AA10

AB8

AB9

SB_CAS#

SB_RAS#

SB_WE#

DDR SYSTEM MEMORY B

C5

D5

D3

D2

D6

C6

C2

C3

F10

F8

G10

G9

F9

F7

G8

G7

K4

K5

K1

J1

J5

J4

J2

K2

M8

N10

N8

N7

M10

M9

N9

M7

AG6

AG5

AK6

AK5

AH5

AH6

AJ5

AJ6

AJ8

AK8

AJ9

AK9

AH8

AH9

AL9

AL8

AP11

AN11

AL12

AM12

AM11

AL11

AP12

AN12

AJ14

AH14

AL15

AK15

AL14

AK14

AJ15

AH15

DDR SYSTEM MEMORY A

12 DDR_A_D[0..63]

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_B_DQS#[0..7]

DDR_B_DQS[0..7]

DDR_B_MA[0..15]

13

13

13

Sandy Bridge_rPGA_Rev1p0

CONN@

+1.5V

R85

1K_0402_5%

2

@ R84

0_0402_5%

1

2

H_DRAMRST#

DDR3_DRAMRST#_R

1

Q5

BSS138_NL_SOT23-3

3

2

5 H_DRAMRST#

R89

33 DRAMRST_CNTRL_EC

DDR3_DRAMRST# 12,13

R88

0_0402_5%

1

2

19 DRAMRST_CNTRL_PCH

R86

1K_0402_5%

2

R87

4.99K_0402_1%

DRAMRST_CNTRL

Compal Secret Data

Security Classification

2 0_0402_5%

1

Issued Date

C84

0.047U_0402_16V4Z

2010/05/17

2011/05/17

Deciphered Date

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Rev

D

401968

Date:

Compal Electronics, Inc.

SCHEMATICS,MB A6731

Sheet

Wednesday, March 09, 2011

1

of

45

CFG Straps for Processor

JCPUE

PEG Static Lane Reversal - CFG2 is for the 16x

T63

T60

T62

T59

T61

T74

T76

T75

T78

T80

T77

T85

T83

T84

T82

T79

T81

PAD

PAD

PAD

PAD

PAD

PAD

PAD

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

AK28

AK29

AL26

AL27

AK26

AL29

AL30

AM31

AM32

AM30

AM28

AM26

AN28

AN31

AN26

AM27

AK31

AN29

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

L7

AG7

AE7

AK2

W8

RSVD33

RSVD34

RSVD35

AT26

AM33

AJ27

RSVD37

RSVD38

RSVD39

RSVD40

T8

J16

H16

G16

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

AR35

AT34

AT33

AP35

AR34

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

B34

A33

A34

B35

C35

1: Normal Operation; Lane #

socket pin map definition

CFG2

definition matches

0:Lane Reversed

Display Port Presence Strap

1 : Disabled; No Physical Display Port

attached to Embedded Display Port

CFG4

s

e

.

*

e

s

r

0 : Enabled; An external Display Port device is

connected to the Embedded Display Port

PCIE Port Bifurcation Straps

T6

T7

T8

T9

PAD

PAD

PAD

PAD

AJ31

AH31

AJ33

AH33

VAXG_VAL_SENSE

VSSAXG_VAL_SENSE

VCC_VAL_SENSE

VSS_VAL_SENSE

AJ26

RSVD5

B4

D1

RSVD6

RSVD7

CPU_RSVD6

CPU_RSVD7

R93

1K_0402_1%

2

R92

1K_0402_1%

F25

F24

F23

D24

G25

G24

E23

D23

C30

A31

B30

B29

D30

B31

A30

C29

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

J20

B18

A19

RSVD24

RSVD25

VCCIO_SEL

J15

RSVD27

e

v

ni

U

k

o

o

b

te

o

N

RESERVED

RSVD51

RSVD52

AJ32

AK32

VCC_DIE_SENSE

AH27

RSVD54

RSVD55

AN35

AM35

disabled

01: Reserved - (Device 1 function 1 disabled ; function

2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

PEG DEFER TRAINING

CFG7

1: (Default) PEG Train immediately following xxRESETB

de assertion

0: PEG Wait for BIOS for training

CFG7

PAD

11: (Default) x16 - Device 1 functions 1 and 2 disabled

CFG[6:5] *10: x8, x8 - Device 1 function 1 enabled ; function 2

T10

R187 1

2 1K_0402_5%

CLK_RES_ITP 19

CLK_RES_ITP# 19

B

RSVD56

RSVD57

RSVD58

KEY

AT2

AT1

AR1

B1

Sandy Bridge_rPGA_Rev1p0

CONN@

Compal Secret Data

Security Classification

Issued Date

2010/05/17

2011/05/17

Deciphered Date

Title

Compal Electronics, Inc.

SCHEMATICS,MB A6731

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Rev

D

401968

Date:

Sheet

Wednesday, March 09, 2011

1

of

45

POWER

+CPU_CORE

s

e

.

SVID

1

+

2

1

+ @ C122

330U_D2_2V_Y

2

R98

75_0402_5%

R99

43_0402_1%

1

2

R100 1

2 0_0402_5%

R101 1

2 0_0402_5%

VR_SVID_ALRT# 44

VR_SVID_CLK 44

VR_SVID_DAT 44

Place the PU

resistors close to VR

B

Place the PU

resistors close to CPU

+CPU_CORE

R102

100_0402_1%

VCC_SENSE

VSS_SENSE

AJ35 VCCSENSE_R

AJ34 VSSSENSE_R

R103 1

R104 1

2

2

0_0402_5%

0_0402_5%

VCCSENSE 44

VSSSENSE 44

1

SENSE LINES

1

2

1

2

CORE SUPPLY

H_CPU_SVIDALRT#

H_CPU_SVIDCLK

H_CPU_SVIDDAT

+1.05VS_VCCP

1

2

2

1

2

change C137 from 440U to 330U for PWR demand--1201

C105

22U_0805_6.3V6M

e

t

o

N

C121

330U_D2_2V_Y

C114

22U_0805_6.3V6M

R97

130_0402_5%

AJ29

AJ30

AJ28

+1.05VS_VCCP

VIDALERT#

VIDSCLK

VIDSOUT

e

s

r

e

niv

U

k

o

o

b

C92

22U_0805_6.3V6M

Bottom Socket Edge

J23

C117

330U_D2_2V_Y

C140

330U_D2_2V_Y

C139

470U_D2_2VM_R4.5M

C138

330U_D2_2V_Y

C137

330U_D2_2VM_R4.5M

VCCIO40

C113

22U_0805_6.3V6M

+CPU_CORE

E11

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

C91

22U_0805_6.3V6M

VCCIO25

VCCIO26

VCCIO27

VCCIO28

VCCIO29

VCCIO30

VCCIO31

VCCIO32

VCCIO33

VCCIO34

VCCIO35

VCCIO36

VCCIO37

VCCIO38

VCCIO39

C112

22U_0805_6.3V6M

C136

22U_0805_6.3V6M

C132

22U_0805_6.3V6M

C127

22U_0805_6.3V6M

C120

22U_0805_6.3V6M

C135

22U_0805_6.3V6M

C131

22U_0805_6.3V6M

C126

22U_0805_6.3V6M

C119

22U_0805_6.3V6M

C134

22U_0805_6.3V6M

C133

22U_0805_6.3V6M

C130

22U_0805_6.3V6M

C129

22U_0805_6.3V6M

C125

22U_0805_6.3V6M

C118

22U_0805_6.3V6M

C124

22U_0805_6.3V6M

C128

22U_0805_6.3V6M

C116

22U_0805_6.3V6M

C123

22U_0805_6.3V6M

1

C

C115

22U_0805_6.3V6M

C104

22U_0805_6.3V6M

10U_0805_6.3V6M

C111

22U_0805_6.3V6M

C98

10U_0805_6.3V6M

Top Socket Edge 22U * 11

Top Socket Cavity 22U * 8

1

C110

22U_0805_6.3V6M

10U_0805_6.3V6M

C97

C109

22U_0805_6.3V6M

10U_0805_6.3V6M

C96

+1.05VS_VCCP

1

C108

22U_0805_6.3V6M

C95

AH13

AH10

AG10

AC10

Y10

U10

P10

L10

J14

J13

J12

J11

H14

H12

H11

G14

G13

G12

F14

F13

F12

F11

E14

E12

C107

22U_0805_6.3V6M

C94

VCCIO1

VCCIO2

VCCIO3

VCCIO4

VCCIO5

VCCIO6

VCCIO7

VCCIO8

VCCIO9

VCCIO10

VCCIO11

VCCIO12

VCCIO13

VCCIO14

VCCIO15

VCCIO16

VCCIO17

VCCIO18

VCCIO19

VCCIO20

VCCIO21

VCCIO22

VCCIO23

VCCIO24

C106

22U_0805_6.3V6M

C93

10U_0805_6.3V6M

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC80

VCC81

VCC82

VCC83

VCC84

VCC85

VCC86

VCC87

VCC88

VCC89

VCC90

VCC91

VCC92

VCC93

VCC94

VCC95

VCC96

VCC97

VCC98

VCC99

VCC100

C90

22U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

+CPU_CORE

C100

10U_0805_6.3V6M

C103

22U_0805_6.3V6M

10U_0805_6.3V6M

C87

+1.05VS_VCCP

C89

22U_0805_6.3V6M

C86

C88

22U_0805_6.3V6M

C85

AG35

AG34

AG33

AG32

AG31

AG30

AG29

AG28

AG27

AG26

AF35

AF34

AF33

AF32

AF31

AF30

AF29

AF28

AF27

AF26

AD35

AD34

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AD26

AC35

AC34

AC33

AC32

AC31

AC30

AC29

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

Y35

Y34

Y33

Y32

Y31

Y30

Y29

Y28

Y27

Y26

V35

V34

V33

V32

V31

V30

V29

V28

V27

V26

U35

U34

U33

U32

U31

U30

U29

U28

U27

U26

R35

R34

R33

R32

R31

R30

R29

R28

R27

R26

P35

P34

P33

P32

P31

P30

P29

P28

P27

P26

C102

22U_0805_6.3V6M

C99

10U_0805_6.3V6M

Top Socket Cacity 22U *9

Bottom Socket Cacity 22U *10

C101

22U_0805_6.3V6M

10U_0805_6.3V6M

8.5A

PEG AND DDR

94A

Bottom Socket Cacity

JCPUF

VCCIO_SENSE

VSSIO_SENSE

B10

A10

1

R117

R105

100_0402_1%

VCCIO_SENSE 41

2

10_0402_5%

Sandy Bridge_rPGA_Rev1p0

CONN@

Compal Secret Data

Security Classification

Issued Date

2010/05/17

2011/05/17

Deciphered Date

Title

Compal Electronics, Inc.

SCHEMATICS,MB A6731

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Rev

D

401968

Date:

Sheet

Wednesday, March 09, 2011

1

of

45

+1.5V_CPU_VDDQ Source

+1.5V

Q6

AO4728L_SO8

+VSB

+3VALW

R107

470_0603_5%

RUN_ON_CPU1.5VS3

R108

100K_0402_5%

+1.5V_CPU_VDDQ

+1.5V

D

R106

100K_0402_5%

+1.5V_CPU_VDDQ

1

2

3

8

7

6

5

R109

330K_0402_5%

Q7A

2N7002DW-T/R7_SOT363-6

C142

S

0.1U_0402_16V4Z

DDR3 -1.5V RAILS

SA RAIL

C156

0.1U_0402_16V4Z

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

AF7

AF4

AF1

AC7

AC4

AC1

Y7

Y4

Y1

U7

U4

U1

P7

P4

P1

R114

1K_0402_1%

+V_SM_VREF

@Q9

@

Q9

AP2302GN-HF_SOT23-3

R115

1K_0402_1%

RUN_ON_CPU1.5VS3

2

SENSE

LINES

e

s

r

+V_SM_VREF_CNT

+1.5V_CPU_VDDQ

+1.5V

PJ4

10A

1

+

@ JUMP_43X118

C169

330U_D2_2V_Y

PJ5

2

@ JUMP_43X118

Bottom Socket Edge

B

6A

VCCSA1

VCCSA2

VCCSA3

VCCSA4

VCCSA5

VCCSA6

VCCSA7

VCCSA8

VCCSA_SENSE

+VCCSA

+VCCSA

M27

M26

L26

J26

J25

J24

H26

H25

H23

R116

2 0_0402_5%

VCCSA_SENSE

1

+

C174

330U_D2_2V_Y

VCCSA_SENSE 43

C22 H_FC_C22

C24

VCCSA_SEL 43

1

FC_C22

VCCSA_VID1

Bottom Socket Cacity 10U *2

Bottom Socket Edge 10U *1

C173

10U_0603_6.3V6M

MISC

AL1

+1.5V_CPU_VDDQ

R113

0_0402_5%

2

1

C172

10U_0603_6.3V6M

VCCPLL1

VCCPLL2

VCCPLL3

SM_VREF

C171

10U_0603_6.3V6M

R119

10K_0402_5%

Sandy Bridge_rPGA_Rev1p0

CONN@

@R120

@

R120

0_0402_5%

B6

A6

A2

s

e

.

+V_SM_VREF should

have 20 mil trace width

C170

10U_0603_6.3V6M

C178

1U_0402_6.3V6K

C177

1U_0402_6.3V6K

C176

10U_0603_6.3V6M

C175

330U_D2_2V_Y

42

C168

10U_0603_6.3V6M

+1.8VS_VCCPLL

1 0.1U_0402_10V7K

C167

10U_0603_6.3V6M

R118

0_0805_5%

1

2

1

C166

10U_0603_6.3V6M

C237

0.1U_0402_16V4Z

@

EMI DEMAND

+1.8VS

C143

C165

10U_0603_6.3V6M

1 0.1U_0402_10V7K

Follow DG 0.71 page 6

VCC_AXG_SENSE 44

VSS_AXG_SENSE 44

C164

10U_0603_6.3V6M

AK35

AK34

e

v

ni

U

k

o

o

b

e

t

o

N

2

VAXG_SENSE

VSSAXG_SENSE

C163

10U_0603_6.3V6M

VAXG1

VAXG2

VAXG3

VAXG4

VAXG5

VAXG6

VAXG7

VAXG8

VAXG9

VAXG10

VAXG11

VAXG12

VAXG13

VAXG14

VAXG15

VAXG16

VAXG17

VAXG18

VAXG19

VAXG20

VAXG21

VAXG22

VAXG23

VAXG24

VAXG25

VAXG26

VAXG27

VAXG28

VAXG29

VAXG30

VAXG31

VAXG32

VAXG33

VAXG34

VAXG35

VAXG36

VAXG37

VAXG38

VAXG39

VAXG40

VAXG41

VAXG42

VAXG43

VAXG44

VAXG45

VAXG46

VAXG47

VAXG48

VAXG49

VAXG50

VAXG51

VAXG52

VAXG53

VAXG54

GRAPHICS

AT24

AT23

AT21

AT20

AT18

AT17

AR24

AR23

AR21

AR20

AR18

AR17

AP24

AP23

AP21

AP20

AP18

AP17

AN24

AN23

AN21

AN20

AN18

AN17

AM24

AM23

AM21

AM20

AM18

AM17

AL24

AL23

AL21

AL20

AL18

AL17

AK24

AK23

AK21

AK20

AK18

AK17

AJ24

AJ23

AJ21

AJ20

AJ18

AJ17

AH24

AH23

AH21

AH20

AH18

AH17

1.8V RAIL

C162

22U_0805_6.3V6M

C233

0.1U_0402_16V4Z

@

C152

22U_0805_6.3V6M

C148

22U_0805_6.3V6M

C232

0.1U_0402_16V4Z

@

C161

22U_0805_6.3V6M

+VGFX_CORE

C151

22U_0805_6.3V6M

Bottom Socket Edge

B

C147

22U_0805_6.3V6M

C160

22U_0805_6.3V6M

C155

22U_0805_6.3V6M

C146

22U_0805_6.3V6M

C159

22U_0805_6.3V6M

C154

22U_0805_6.3V6M

C158

470U_D2_2VM_R4.5M

C157

470U_D2_2VM_R4.5M

C150

22U_0805_6.3V6M

C149

22U_0805_6.3V6M

C145

22U_0805_6.3V6M

C144

22U_0805_6.3V6M

C153

22U_0805_6.3V6M

POWER

JCPUG

26A

VREF

+VGFX_CORE

Top Socket Cacity 22U *2

Top Socket Edge 22U *6

Bottom Socket Cacity 22U *2

Bottom Socket Edge 22U *6

C141

RUN_ON_CPU1.5VS3#

2 RUN_ON_CPU1.5VS3#

G

Q8

2N7002E-T1-GE3_SOT23-3

@ R111

@R111

0_0402_5%

1

2

28,33,35,39,41,43 SUSP#

1

3

RUN_ON_CPU1.5VS3#

6

33 CPU1.5V_S3_GATE

Q7B

2N7002DW-T/R7_SOT363-6

R110

0_0402_5%

1

2

Bottom Socket Edge

Compal Secret Data

Security Classification

Issued Date

2010/05/17

2011/05/17

Deciphered Date

Title

Compal Electronics, Inc.

SCHEMATICS,MB A6731

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Rev

D

401968

Date:

Sheet

Wednesday, March 09, 2011

1

10

of

45

JCPUH

D

AT35

AT32

AT29

AT27

AT25

AT22

AT19

AT16

AT13

AT10

AT7

AT4

AT3

AR25

AR22

AR19

AR16

AR13

AR10

AR7

AR4

AR2

AP34

AP31

AP28

AP25

AP22

AP19

AP16

AP13

AP10

AP7

AP4

AP1

AN30

AN27

AN25

AN22

AN19

AN16

AN13

AN10

AN7

AN4

AM29

AM25

AM22

AM19

AM16

AM13

AM10

AM7

AM4

AM3

AM2

AM1

AL34

AL31

AL28

AL25

AL22

AL19

AL16

AL13

AL10

AL7

AL4

AL2

AK33

AK30

AK27

AK25

AK22

AK19

AK16

AK13

AK10

AK7

AK4

AJ25

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

JCPUI

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AJ22

AJ19

AJ16

AJ13

AJ10

AJ7

AJ4

AJ3

AJ2

AJ1

AH35

AH34

AH32

AH30

AH29

AH28

AH26

AH25

AH22

AH19

AH16

AH7

AH4

AG9

AG8

AG4

AF6

AF5

AF3

AF2

AE35

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE9

AD7

AC9

AC8

AC6

AC5

AC3

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

Y9

Y8

Y6

Y5

Y3

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

U9

U8

U6

U5

U3

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

P9

P8

P6

P5

P3

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

M34

L33

L30

L27

L9

L8

L6

L5

L4

L3

L2

L1

K35

K32

K29

K26

J34

J31

H33

H30

H27

H24

H21

H18

H15

H13

H10

H9

H8

H7

H6

H5

H4

H3

H2

H1

G35

G32

G29

G26

G23

G20

G17

G11

F34

F31

F29

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

s

e

.

e

s

r

e

v

ni

U

k

o

o

b

e

t

o

N

Sandy Bridge_rPGA_Rev1p0

CONN@

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

VSS277

VSS278

VSS279

VSS280

VSS281

VSS282

VSS283

VSS284

VSS285

VSS

F22

F19

E30

E27

E24

E21

E18

E15

E13

E10

E9

E8

E7

E6

E5

E4

E3

E2

E1

D35

D32

D29

D26

D20

D17

C34

C31

C28

C27

C25

C23

C10

C1

B22

B19

B17

B15

B13

B11

B9

B8

B7

B5

B3

B2

A35

A32

A29

A26

A23

A20

A3

Sandy Bridge_rPGA_Rev1p0

CONN@

Compal Secret Data

Security Classification

Issued Date

2010/05/17

2011/05/17

Deciphered Date

Title

Compal Electronics, Inc.

SCHEMATICS,MB A6731

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Rev

D

401968

Date:

Sheet

Wednesday, March 09, 2011

1

11

of

45

+1.5V

+1.5V

DDR_A_DM0

DDR_A_D2

DDR_A_D3

DDR_A_D8

DDR_A_D9

DDR_A_DQS#1

DDR_A_DQS1

R123

1K_0402_1%

DDR_A_D10

DDR_A_D11

DDR_A_D16

DDR_A_D17

DDR_A_DQS#2

DDR_A_DQS2

7 DDR_A_BS0

DDR_A_MA10

DDR_A_BS0

7 DDR_A_WE#

7 DDR_A_CAS#

DDR_A_WE#

DDR_A_CAS#

DDR_A_D48

DDR_A_D49

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_D50

DDR_A_D51

DDR_A_D56

DDR_A_D57

+3VS

DDR_A_DM7

D_CK_SDATA

+3VS

2

G

3

D_CK_SCLK

Q2

2N7002E-T1-GE3_SOT23-3

R135

10K_0402_5%

R134

10K_0402_5%

19 PCH_SMBCLK

C200

2.2U_0603_6.3V6K

R4

4.7K_0402_5%

1

2

+3VS

C199

0.1U_0402_16V4Z

+3VS

A

+0.75VS

Q1

2N7002E-T1-GE3_SOT23-3

DDR_A_D58

DDR_A_D59

19 PCH_SMBDATA

2

G

R1

4.7K_0402_5%

1

2

+3VS

205

G1

G2

206

DDR_A_MA6

DDR_A_MA4

DDR_A_MA2

DDR_A_MA0

M_CLK_DDR1

M_CLK_DDR#1

M_CLK_DDR1 7

M_CLK_DDR#1 7

DDR_A_BS1

DDR_A_RAS#

DDR_A_BS1 7

DDR_A_RAS# 7

DDR_CS0_DIMMA#

M_ODT0

DDR_CS0_DIMMA# 7

M_ODT0 7

M_ODT1

M_ODT1

DDR_A_D38

DDR_A_D39

+1.5V

1

+

2

R124

1K_0402_1%

Layout Note:

Place near JDIMM1.203,204

DDR_A_D44

DDR_A_D45

+0.75VS

R125

1K_0402_1%

DDR_A_DQS#5

DDR_A_DQS5

DDR_A_D46

DDR_A_D47

DDR_A_D52

DDR_A_D53

DDR_A_DM6

DDR_A_D54

DDR_A_D55

DDR_A_D60

DDR_A_D61

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS#7

DDR_A_DQS7

DDR_A_D62

DDR_A_D63

D_CK_SDATA

D_CK_SCLK

D_CK_SDATA 13,14,29

D_CK_SCLK 13,14,29

+0.75VS

A

LCN_DAN06-K4526-0101

CONN@

Compal Secret Data

Security Classification

Issued Date

2010/05/17

2011/05/17

Deciphered Date

Title

Compal Electronics, Inc.

SCHEMATICS,MB A6731

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Rev

D

401968

Date:

+1.5V

+VREF_CA

DDR_A_D36

DDR_A_D37

DDR_A_DM4

C198

1U_0402_6.3V6K

DDR_A_D42

DDR_A_D43

e

s

r

e

niv

DDR_A_MA11

DDR_A_MA7

C197

1U_0402_6.3V6K

DDR_A_DM5

s

e

.

DDR_CKE1_DIMMA 7

DDR_A_MA15

DDR_A_MA14

C196

1U_0402_6.3V6K

DDR_A_D40

DDR_A_D41

DDR_CKE1_DIMMA

C195

1U_0402_6.3V6K

DDR_A_D34

DDR_A_D35

DDR_A_D30

DDR_A_D31

C194

0.1U_0402_16V4Z

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_DQS#3

DDR_A_DQS3

C193

2.2U_0603_6.3V6K

t

o

N

DDR_A_D32

DDR_A_D33

DDR_A_D28

DDR_A_D29

U

k

o

o

b

e

7 DDR_CS1_DIMMA#

DDR_A_MA13

DDR_CS1_DIMMA#

DDR_A_D22

DDR_A_D23

C191

10U_0603_6.3V6M

7 M_CLK_DDR0

7 M_CLK_DDR#0

M_CLK_DDR0

M_CLK_DDR#0

DDR_A_DM2

C190

10U_0603_6.3V6M

DDR_A_MA3

DDR_A_MA1

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

204

+1.5V

C189

10U_0603_6.3V6M

DDR_A_MA8

DDR_A_MA5

CKE1

VDD2

A15

A14

VDD4

A11

A7

VDD6

A6

A4

VDD8

A2

A0

VDD10

CK1

CK1#

VDD12

BA1

RAS#

VDD14

S0#

ODT0

VDD16

ODT1

NC2

VDD18

VREF_CA

VSS28

DQ36

DQ37

VSS30

DM4

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

DM6

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

EVENT#

SDA

SCL

VTT2

Layout Note:

Place near JDIMM1

DDR_A_D20

DDR_A_D21

C188

10U_0603_6.3V6M

DDR_A_MA12

DDR_A_MA9

CKE0

VDD1

NC1

BA2

VDD3

A12/BC#

A9

VDD5

A8

A5

VDD7

A3

A1

VDD9

CK0

CK0#

VDD11

A10/AP

BA0

VDD13

WE#

CAS#

VDD15

A13

S1#

VDD17

NCTEST

VSS27

DQ32

DQ33

VSS29

DQS#4

DQS4

VSS32

DQ34

DQ35

VSS34

DQ40

DQ41

VSS36

DM5

VSS37

DQ42

DQ43

VSS39

DQ48

DQ49

VSS41

DQS#6

DQS6

VSS44

DQ50

DQ51

VSS46

DQ56

DQ57

VSS48

DM7

VSS49

DQ58

DQ59

VSS51

SA0

VDDSPD

SA1

VTT1

DDR3_DRAMRST# 7,13

DDR_A_D14

DDR_A_D15

C187

10U_0603_6.3V6M

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

201

203

DDR_A_DM1

DDR3_DRAMRST#

C186

10U_0603_6.3V6M

DDR_A_BS2

7 DDR_A_BS2

DDR_A_D12

DDR_A_D13

C185

10U_0603_6.3V6M

7 DDR_CKE0_DIMMA

DDR_A_D[0..63]

DDR_A_MA[0..15]

C192

330U_B2_2.5VM_R15M

DDR_CKE0_DIMMA

DDR_A_D6

DDR_A_D7

C184

1U_0402_6.3V6K

DDR_A_D26

DDR_A_D27

DDR_A_DQS#0

DDR_A_DQS0

DDR_A_DQS[0..7]

C183

1U_0402_6.3V6K

DDR_A_DM3

DDR_A_DQS#[0..7]

DDR_A_D4

DDR_A_D5

C182

1U_0402_6.3V6K

DDR_A_D24

DDR_A_D25

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

C181

1U_0402_6.3V6K

DDR_A_D18

DDR_A_D19

VSS1

DQ4

DQ5

VSS3

DQS#0

DQS0

VSS6

DQ6

DQ7

VSS8

DQ12

DQ13

VSS10

DM1

RESET#

VSS12

DQ14

DQ15

VSS14

DQ20

DQ21

VSS16

DM2

VSS17

DQ22

DQ23

VSS19

DQ28

DQ29

VSS21

DQS#3

DQS3

VSS24

DQ30

DQ31

VSS26

DDR_A_D0

DDR_A_D1

VREF_DQ

VSS2

DQ0

DQ1

VSS4

DM0

VSS5

DQ2

DQ3

VSS7

DQ8

DQ9

VSS9

DQS#1

DQS1

VSS11

DQ10

DQ11

VSS13

DQ16

DQ17

VSS15

DQS#2

DQS2

VSS18

DQ18

DQ19

VSS20

DQ24

DQ25

VSS22

DM3

VSS23

DQ26

DQ27

VSS25

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

1

2

All VREF traces should

have 10 mil trace width

C180

0.1U_0402_16V4Z

+V_DDR_REF

+1.5V

+V_DDR_REF

C179

2.2U_0603_6.3V6K

R122

1K_0402_1%

JDIMM1

+V_DDR_REF

Sheet

Wednesday, March 09, 2011

1

12

of

45

+V_DDR_REF

+1.5V

+1.5V

JDIMM2

+V_DDR_REF

C202

0.1U_0402_16V4Z

All VREF traces should

have 10 mil trace width

C201

2.2U_0603_6.3V6K

DDR_B_D0

DDR_B_D1

DDR_B_DM0

DDR_B_D2

DDR_B_D3

DDR_B_D8

DDR_B_D9

DDR_B_DQS#1

DDR_B_DQS1

DDR_B_D10

DDR_B_D11

DDR_B_D16

DDR_B_D17

DDR_B_D26

DDR_B_D27

7 DDR_B_WE#

7 DDR_B_CAS#

DDR_B_WE#

DDR_B_CAS#

DDR_B_D48

DDR_B_D49

DDR_B_DQS#6

DDR_B_DQS6

+3VS

+3VS

C222

2.2U_0603_6.3V6K

C221

0.1U_0402_16V4Z

DDR_B_D56

DDR_B_D57

1

R149

10K_0402_5%

DDR_B_D50

DDR_B_D51

DDR_B_DM7

DDR_B_D58

DDR_B_D59

205

G1

G2

206

DDR_B_DQS#3

DDR_B_DQS3

DDR_B_D30

DDR_B_D31

DDR_CKE3_DIMMB

Layout Note:

Place near JDIMMB

s

e

.

DDR_CKE3_DIMMB 7

DDR_B_MA15

DDR_B_MA14

DDR_B_MA11

DDR_B_MA7

DDR_B_MA6

DDR_B_MA4

DDR_B_MA2

DDR_B_MA0

M_CLK_DDR3

M_CLK_DDR#3

M_CLK_DDR3 7

M_CLK_DDR#3 7

DDR_B_BS1

DDR_B_RAS#

DDR_B_BS1 7

DDR_B_RAS# 7

DDR_CS2_DIMMB#

M_ODT2

DDR_CS2_DIMMB# 7

M_ODT2 7

M_ODT3

M_ODT3

DDR_B_D36

DDR_B_D37

DDR_B_DM4

DDR_B_D38

DDR_B_D39

DDR_B_D44

DDR_B_D45

+1.5V

<BOM

1 Structure>

+

2

Layout Note:

Place near JDIMMB.203,204

+0.75VS

7

+VREF_CA

DDR_B_DQS#5

DDR_B_DQS5

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_D46

DDR_B_D47

DDR_B_D52

DDR_B_D53

DDR_B_DM6

DDR_B_D54

DDR_B_D55

DDR_B_D60

DDR_B_D61

DDR_B_DQS#7

DDR_B_DQS7

DDR_B_D62

DDR_B_D63

D_CK_SDATA

D_CK_SCLK

D_CK_SDATA 12,14,29

D_CK_SCLK 12,14,29

+0.75VS

+0.75VS

C218

1U_0402_6.3V6K

DDR_B_D42

DDR_B_D43

C217

1U_0402_6.3V6K

DDR_B_DM5

DDR_B_D28

DDR_B_D29

C216

1U_0402_6.3V6K

DDR_B_D40

DDR_B_D41

C215

1U_0402_6.3V6K

DDR_B_D34

DDR_B_D35

DDR_B_D22

DDR_B_D23

C220

0.1U_0402_16V4Z

t

o

N

DDR_B_DQS#4

DDR_B_DQS4

DDR_B_DM2

C219

2.2U_0603_6.3V6K

o

b

e

DDR_B_D32

DDR_B_D33

+1.5V

DDR_B_D20

DDR_B_D21

e

s

r

e

niv

U

k

o

DDR_B_MA13

DDR_CS3_DIMMB#

7 DDR_CS3_DIMMB#

DDR_B_D14

DDR_B_D15

C213

10U_0603_6.3V6M

7 DDR_B_BS0

DDR_B_MA10

DDR_B_BS0

DDR3_DRAMRST# 7,12

C212

10U_0603_6.3V6M

7 M_CLK_DDR2

7 M_CLK_DDR#2

DDR_B_DM1

DDR3_DRAMRST#

C211

10U_0603_6.3V6M

DDR_B_MA3

DDR_B_MA1

M_CLK_DDR2

M_CLK_DDR#2

DDR_B_MA[0..15]

C210

10U_0603_6.3V6M

DDR_B_MA8

DDR_B_MA5

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

204

7

7

DDR_B_D12

DDR_B_D13

C209

10U_0603_6.3V6M

DDR_B_MA12

DDR_B_MA9

CKE1

VDD2

A15

A14

VDD4

A11

A7

VDD6

A6

A4

VDD8

A2

A0

VDD10

CK1

CK1#

VDD12

BA1

RAS#

VDD14

S0#

ODT0

VDD16

ODT1

NC2

VDD18

VREF_CA

VSS28

DQ36

DQ37

VSS30

DM4

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

DM6

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

EVENT#

SDA

SCL

VTT2

DDR_B_D[0..63]

DDR_B_D6

DDR_B_D7

C208

10U_0603_6.3V6M

CKE0

VDD1

NC1

BA2

VDD3

A12/BC#

A9

VDD5

A8

A5

VDD7

A3

A1

VDD9

CK0

CK0#

VDD11

A10/AP

BA0

VDD13

WE#

CAS#

VDD15

A13

S1#

VDD17

NCTEST

VSS27

DQ32

DQ33

VSS29

DQS#4

DQS4

VSS32

DQ34

DQ35

VSS34

DQ40

DQ41

VSS36

DM5

VSS37

DQ42

DQ43

VSS39

DQ48

DQ49

VSS41

DQS#6

DQS6

VSS44

DQ50

DQ51

VSS46

DQ56

DQ57

VSS48

DM7

VSS49

DQ58

DQ59

VSS51

SA0

VDDSPD

SA1

VTT1

DDR_B_DQS[0..7]

C207

10U_0603_6.3V6M

DDR_B_BS2

7 DDR_B_BS2

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149