Professional Documents

Culture Documents

VN750B5

Uploaded by

Yonatan RivadeneyraCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

VN750B5

Uploaded by

Yonatan RivadeneyraCopyright:

Available Formats

VN750-E / VN750S-E VN750PT-E / VN750B5-E

HIGH SIDE DRIVER

Table 1. General Features

Type VN750-E VN750B5-E VN750S-E VN750PT RDS(on) 60 m IOUT VCC

Figure 1. Package

6A

36 V

SO-8 CMOS COMPATIBLE INPUT ON STATE OPEN LOAD DETECTION I OFF STATE OPEN LOAD DETECTION I SHORTED LOAD PROTECTION I UNDERVOLTAGE AND OVERVOLTAGE SHUTDOWN I PROTECTION AGAINST LOSS OF GROUND I VERY LOW STAND-BY CURRENT

I I I I

PENTAWATT

P2PAK

PPAK

REVERSE BATTERY PROTECTION (*) IN COMPLIANCE WITH THE 2002/95/EC EUROPEAN DIRECTIVE DESCRIPTION The VN750-E, VN750S-E, VN750PT-E, VN750B5-E are a monolithic device designed in STMicroelectronics VIPower M0-3 Technology, intended for driving any kind of load with one side connected to ground. Active VCC pin voltage clamp protects the device against low energy spikes (see ISO7637 transient compatibility table).

Active current limitation combined with thermal shutdown and automatic restart protect the device against overload. The device detects open load condition both is on and off state. Output shorted to VCC is detected in the off state. Device automatically turns off in case of ground pin disconnection.

Table 2. Order Codes

Package PENTAWATT SO-8 P PAK PPAK

Note: (*) See application schematic at page 9.

2

Tube VN750-E VN750S-E VN750B5-E VN750PT-E -

Tape and Reel

VN750STR-E VN750B5TR-E VN750PTTR-E

Rev. 1 October 2004 1/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

Figure 2. Block Diagram

VCC

VCC CLAMP

OVERVOLTAGE DETECTION UNDERVOLTAGE DETECTION

GND Power CLAMP

INPUT LOGIC

DRIVER OUTPUT CURRENT LIMITER

STATUS

ON STATE OPENLOAD DETECTION OVERTEMPERATURE DETECTION

OFF STATE OPENLOAD AND OUTPUT SHORTED TO VCC DETECTION

Table 3. Absolute Maximum Ratings

Symbol VCC - VCC - Ignd IOUT - IOUT IIN ISTAT Parameter DC Supply Voltage Reverse DC Supply Voltage DC Reverse Ground Pin Current DC Output Current Reverse DC Output Current DC Input Current DC Status Current Electrostatic Discharge (Human Body Model: R=1.5K; C=100pF) VESD - INPUT - STATUS - OUTPUT - VCC Maximum Switching Energy (L=1.8mH; RL=0; Vbat=13.5V; Tjstart=150C; IL=9A) Maximum Switching Energy (L=2.46mH; RL=0; Vbat=13.5V; Tjstart=150C; IL=9A) Power Dissipation TC=25C Junction Operating Temperature Case Operating Temperature Storage Temperature 4000 4000 5000 5000 100 138 4.2 60 60 Internally Limited - 40 to 150 - 55 to 150 138 60 V V V V mJ mJ W C C C SO-8 Value PENTAWATT P2PAK 41 - 0.3 - 200 Internally Limited -6 +/- 10 +/- 10 PPAK Unit V V mA A A mA mA

EMAX EMAX Ptot Tj Tc Tstg

2/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

Figure 3. Configuration Diagram (Top View) & Suggested Connections for Unused and N.C. Pins

VCC OUTPUT OUTPUT VCC

N.C. STATUS INPUT GND

4 3 2 1

OUTPUT STATUS VCC INPUT GND

SO-8

PPAK / P2PAK

PENTAWATT

Connection / Pin Status Floating X To Ground

N.C. X X

Output X

Input X Through 10K resistor

Figure 4. Current and Voltage Conventions

IS VF IIN INPUT ISTAT STATUS GND VIN VSTAT IGND VOUT OUTPUT IOUT VCC

VCC

Table 4. Thermal Data

Symbol Rthj-case Rthj-lead Rthj-amb Parameter Thermal Resistance Junction-case Thermal Resistance Junction-lead Max Max S0-8 30 93 (1) 82 (2) Value PENTAWATT P2PAK 2.1 2.1 62.1 52.1 (3) 62.1 37 (4) PPAK 2.1 77.1 (3) 44 (4) Unit C/W C/W C/W C/W

Thermal Resistance Junction-ambient Max

(1) When mounted on a standard single-sided FR-4 board with 0.5cm2 of Cu (at least 35m thick) connected to all VCC pins. Horizontal mounting and no artificial air flow. (2) When mounted on a standard single-sided FR-4 board with 2cm2 of Cu (at least 35m thick) connected to all VCC pins. Horizontal mounting and no artificial air flow. (3) When mounted on a standard single-sided FR-4 board with 0.5cm 2 of Cu (at least 35m thick). Horizontal mounting and no artificial air flow. (4) When mounted on a standard single-sided FR-4 board with 6cm2 of Cu (at least 35m thick). Horizontal mounting and no artificial air flow.

3/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

ELECTRICAL CHARACTERISTICS (8V<VCC<36V; -40C<Tj<150C unless otherwise specified) Table 5. Power

Symbol VCC VUSD VUSDhyst VOV RON Parameter Operating Supply Voltage Undervoltage Shut-down Undervoltage Shut-down Hysteresis Overvoltage Shut-down On State Resistance IOUT=2A; Tj=25C; VCC>8V IOUT=2A; VCC>8V Off State; VCC=13V; VIN=VOUT=0V IS Supply Current Off State; VCC=13V; VIN=VOUT=0V; Tj=25C On State; VCC=13V; VIN=5V; IOUT=0A IL(off1) IL(off2) IL(off3) IL(off4) Off State Output Current Off State Output Current Off State Output Current Off State Output Current VIN=VOUT=0V VIN=0V; VOUT=3.5V VIN=VOUT=0V; VCC=13V; Tj =125C VIN=VOUT=0V; VCC=13V; Tj =25C 0 -75 36 (#) 10 10 2 (#) 60 120 25 20 3.5 50 0 5 3 Test Conditions Min. 5.5 3 Typ. 13 4 0.5 Max. 36 5.5 Unit V V V V m m A A mA A A A A

Table 6. Switching (VCC =13V)

Symbol td(on) td(off) dVOUT/ dt(on) dVOUT/ dt(off) Parameter Turn-on Delay Time Turn-off Delay Time Turn-on Voltage Slope Turn-off Voltage Slope Test Conditions RL=6.5 from VIN rising edge to VOUT=1.3V RL=6.5 from VIN falling edge to VOUT=11.7V RL=6.5 from VOUT=1.3V to VOUT=10.4V RL=6.5 from VOUT=11.7V to VOUT=1.3V Min. Typ. 40 30 (#) (#) Max. Unit s s V/s V/s

Table 7. Input Pin

Symbol VIL IIL VIH IIH Vhyst VICL Parameter Input Low Level Low Level Input Current Input High Level High Level Input Current Input Hysteresis Voltage Input Clamp Voltage IIN=1mA IIN=-1mA VIN=3.25V 0.5 6 VIN=1.25V 1 3.25 Test Conditions Min. Typ. (#) (#) (#) (#) (#) 6.8 -0.7 8 10 Max. 1.25 Unit V A V A V V V

Note: (#) See relative diagram

4/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

ELECTRICAL CHARACTERISTICS (continued) Table 8. VCC - Output Diode

Symbol VF Parameter Forward on Voltage Test Conditions -IOUT=1.3A; Tj=150C Min. Typ. Max. 0.6 Unit V

Table 9. Status Pin

Symbol VSTAT ILSTAT CSTAT VSCL Parameter Test Conditions Status Low Output Voltage ISTAT=1.6mA Status Leakage Current Normal Operation; VSTAT=5V Status Pin Input Normal Operation; VSTAT=5V Capacitance ISTAT=1mA Status Clamp Voltage ISTAT=-1mA Min Typ (#) (#) Max 0.5 10 100 6 6.8 -0.7 8 Unit V A pF V V

Table 10. Protections (see note 1)

Symbol TTSD TR Thyst tSDL Ilim Vdemag Parameter Shut-down Temperature Reset Temperature Thermal Hysteresis Status delay in overload condition Current limitation Turn-off Output Clamp Voltage Test Conditions Min 150 135 7 Typ 175 15 20 6 9 15 15 VCC-41 VCC-48 VCC-55 Max 200 Unit C C C s A A V

Tj>Tjsh 9V<VCC<36V 5V<VCC<36V IOUT=2A; VIN=0V; L=6mH

Note: 1. To ensure long term reliability under heavy overload or short circuit conditions, protection and related diagnostic signals must be used together with a proper software strategy. If the device is subjected to abnormal conditions, this software must limit the duration and number of activation cycles.

Table 11. Openload Detection

Symbol IOL tDOL(on) Parameter Openload ON State Detection Threshold Openload ON State Detection Delay Openload OFF State Voltage Detection Threshold Openload Detection Delay at Turn Off Test Conditions VIN=5V IOUT=0A Min 50 Typ (#) Max 200 200 Unit mA s

VOL

VIN=0V

1.5

(#)

3.5

V s

tDOL(off)

1000

Note: (#) See relative diagram

5/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

Figure 5.

OPEN LOAD STATUS TIMING (with external pull-up) IOUT< IOL VOUT > VOL VIN VIN OVERTEMP STATUS TIMING Tj > Tjsh

VSTAT

VSTAT

tDOL(off)

tDOL(on)

tSDL

tSDL

Table 12. Truth Table

CONDITIONS Normal Operation INPUT L H L H H L H L H L H L H L H OUTPUT L H L X X L L L L L L H H L H STATUS H H H (Tj < TTSD) H (Tj > TTSD) L H L X X H H L H H L

Current Limitation

Overtemperature Undervoltage Overvoltage Output Voltage > VOL Output Current < IOL

Figure 6. Switching time Waveforms

VOUTn 90% 80%

dVOUT/dt(on)

dVOUT/dt(off)

10% t VINn

td(on)

td(off)

6/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

Table 13. Electrical Transient Requirements On VCC Pin

ISO T/R 7637/1 Test Pulse 1 2 3a 3b 4 5 ISO T/R 7637/1 Test Pulse 1 2 3a 3b 4 5 CLASS C E I C C C C C C I -25 V +25 V -25 V +25 V -4 V +26.5 V II -50 V +50 V -50 V +50 V -5 V +46.5 V TEST LEVELS III -75 V +75 V -100 V +75 V -6 V +66.5 V TEST LEVELS RESULTS II III C C C C C E C C C C C E IV -100 V +100 V -150 V +100 V -7 V +86.5 V Delays and Impedance 2 ms 10 0.2 ms 10 0.1 s 50 0.1 s 50 100 ms, 0.01 400 ms, 2

IV C C C C C E

CONTENTS All functions of the device are performed as designed after exposure to disturbance. One or more functions of the device is not performed as designed after exposure to disturbance and cannot be returned to proper operation without replacing the device.

7/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

Figure 7. Waveforms

NORMAL OPERATION INPUT LOAD VOLTAGE STATUS UNDERVOLTAGE VCC VUSD INPUT LOAD VOLTAGE STATUS undefined VUSDhyst

OVERVOLTAGE VCC<VOV VCC INPUT LOAD VOLTAGE STATUS OPEN LOAD with external pull-up INPUT LOAD VOLTAGE STATUS VOUT>VOL VOL VCC>VOV

OPEN LOAD without external pull-up INPUT LOAD VOLTAGE STATUS

Tj INPUT LOAD CURRENT STATUS

TTSD TR

OVERTEMPERATURE

8/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

Figure 8. Application Schematic

+5V

+5V

Rprot STATUS

VCC

Dld C Rprot INPUT OUTPUT

GND

RGND VGND DGND

GND PROTECTION REVERSE BATTERY

NETWORK

AGAINST

Solution 1: Resistor in the ground line (RGND only). This can be used with any type of load. The following is an indication on how to dimension the RGND resistor. 1) RGND 600mV / (IS(on)max). 2) RGND (VCC) / (-IGND) where -IGND is the DC reverse ground pin current and can be found in the absolute maximum rating section of the devices datasheet. Power Dissipation in RGND (when VCC<0: during reverse battery situations) is: PD= (-VCC)2/RGND This resistor can be shared amongst several different HSD. Please note that the value of this resistor should be calculated with formula (1) where IS(on)max becomes the sum of the maximum on-state currents of the different devices. Please note that if the microprocessor ground is not common with the device ground then the RGND will produce a shift (IS(on)max * RGND) in the input thresholds and the status output values. This shift will vary depending on many devices are ON in the case of several high side drivers sharing the same RGND. If the calculated power dissipation leads to a large resistor or several devices have to share the same resistor then the ST suggests to utilize Solution 2 (see below). Solution 2: A diode (DGND) in the ground line. A resistor (RGND=1k) should be inserted in parallel to DGND if the device will be driving an inductive load. This small signal diode can be safely shared amongst several different HSD. Also in this case, the presence of

the ground network will produce a shift (j600mV) in the input threshold and the status output values if the microprocessor ground is not common with the device ground. This shift will not vary if more than one HSD shares the same diode/resistor network. Series resistor in INPUT and STATUS lines are also required to prevent that, during battery voltage transient, the current exceeds the Absolute Maximum Rating. Safest configuration for unused INPUT and STATUS pin is to leave them unconnected.

LOAD DUMP PROTECTION

Dld is necessary (Voltage Transient Suppressor) if the load dump peak voltage exceeds VCC max DC rating. The same applies if the device will be subject to transients on the VCC line that are greater than the ones shown in the ISO T/R 7637/1 table.

C I/Os PROTECTION:

If a ground protection network is used and negative transients are present on the VCC line, the control pins will be pulled negative. ST suggests to insert a resistor (Rprot) in line to prevent the C I/Os pins to latch-up. The value of these resistors is a compromise between the leakage current of C and the current required by the HSD I/Os (Input levels compatibility) with the latch-up limit of C I/Os. -VCCpeak/Ilatchup Rprot (VOHC-VIH-VGND) / IIHmax Calculation example: For VCCpeak= - 100V and Ilatchup 20mA; VOHC 4.5V 5k Rprot 65k. Recommended Rprot value is 10k.

9/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

OPEN LOAD DETECTION IN OFF STATE

Off state open load detection requires an external pull-up resistor (RPU) connected between OUTPUT pin and a positive supply voltage (VPU) like the +5V line used to supply the microprocessor. The external resistor has to be selected according to the following requirements: 1) no false open load indication when load is connected: in this case we have to avoid VOUT to be higher than VOlmin; this results in the following condition VOUT=(VPU/(RL+RPU))RL<VOlmin. 2) no misdetection when load is disconnected: in this case the VOUT has to be higher than VOLmax; this results in the following condition RPU<(VPUVOLmax)/ IL(off2). Because Is(OFF) may significantly increase if Vout is pulled high (up to several mA), the pull-up resistor RPU should be connected to a supply that is switched OFF when the module is in standby. The values of VOLmin, VOLmax and IL(off2) are available in the Electrical Characteristics section.

Figure 9. Open Load detection in off state

V batt.

VPU

VCC RPU INPUT DRIVER + LOGIC OUT + R STATUS VOL RL IL(off2)

GROUND

10/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

Figure 10. Off State Output Current

IL(off1) (uA)

3 2.5 2 1.5 4 1 3 0.5 0 -0.5 -1 -50 -25 0 25 50 75 100 125 150 175 2

Figure 11. High Level Input Current

Iih (uA)

7

Off state Vcc=36V Vin=Vout=0V

Vin=3.25V

5

0 -50 -25 0 25 50 75 100 125 150 175

Tc (C)

Tc (C)

Figure 12. Input Clamp Voltage

Vicl (V)

8 7.8

Figure 14. Status Leakage Current

Ilstat (uA)

0.05

Iin=1mA

7.6 7.4 7.2 7 6.8 6.6 6.4 6.2 6 -50 -25 0 25 50 75 100 125 150 175

0.04

Vstat=5V

0.03

0.02

0.01

0 -50 -25 0 25 50 75 100 125 150 175

Tc (C)

Tc (C)

Figure 13. Status Low Output Voltage

Vstat (V)

0.6

Figure 15. Status Clamp Voltage

Vscl (V)

8 7.8

0.5

Istat=1mA

7.6

Istat=1.6mA

0.4 7.4 7.2 0.3 7 6.8 0.2 6.6 6.4 6.2 0 -50 -25 0 25 50 75 100 125 150 175 6 -50 -25 0 25 50 75 100 125 150 175

0.1

Tc (C)

Tc (C)

11/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

Figure 16. On State Resistance Vs Tcase

Ron (mOhm)

140

Figure 17. On State Resistance Vs VCC

Ron (mOhm)

120 110

120

100

Iout=2A Vcc=8V; 13V; 36V

Iout=2A

100

Tc= 150C

90 80

80

Tc= 125C

70 60 50

60

40

Tc= 25C

40

20 30 0 -50 -25 0 25 50 75 100 125 150 175 20 5 10 15 20 25

Tc= - 40C

30

35

40

Tc (C)

Vcc (V)

Figure 18. Openload On State Detection Threshold

Iol (mA)

220 200 180 160 140 120

Figure 20. Openload Off State Voltage Detection Threshold

Vol (V)

5 4.5

Vcc=13V Vin=5V

Vin=0V

4 3.5 3

100 80 60 40 20 0 -50 -25 0 25 50 75 100 125 150 175 1.5 1 -50 -25 0 25 50 75 100 125 150 175 2.5 2

Tc (C)

Tc (C)

Figure 19. Input High Level

Vih (V)

3.6 3.4 3.2 3

Figure 21. Input Low Level

Vil (V)

2.8 2.6 2.4 2.2 2

2.8 1.8 2.6 1.6 2.4 2.2 2 -50 -25 0 25 50 75 100 125 150 175 1.4 1.2 1 -50 -25 0 25 50 75 100 125 150 175

Tc (C)

Tc (C)

12/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

Figure 22. Turn-on Voltage Slope

dVout/dt/(on) (V/ms)

1000 900 800 700 600 500 400 300 200 100 0 -50 -25 0 25 50 75 100 125 150 175

Figure 25. Turn-off Voltage Slope

dVout/dt(off) (V/ms)

500 450

Vcc=13V Rl=6.5Ohm

400 350 300 250 200 150 100 50 0 -50 -25

Vcc=13V Rl=6.5Ohm

25

50

75

100

125

150

175

Tc (C)

Tc (C)

Figure 23. Overvoltage Shutdown

Vov (V)

50 48 46 44 42 40 38 36 34 32 30 -50 -25 0 25 50 75 100 125 150 175

Figure 26. ILIM Vs Tcase

Ilim (A)

20 18

Vcc=13V

16 14 12 10 8 6 4 2 0 -50 -25 0 25 50 75 100 125 150 175

Tc (C)

Tc (C)

Figure 24. Input Hysteresis Voltage

Vhyst (V)

1.5 1.4 1.3 1.2 1.1 1 0.9 0.8 0.7 0.6 0.5 -50 -25 0 25 50 75 100 125 150 175

Tc (C)

13/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

Figure 27. SO-8 Maximum turn off current versus load inductance

ILMAX (A) 100

10

A B C

1 0.1 1 L(mH)

A = Single Pulse at TJstart=150C B= Repetitive pulse at TJstart=100C C= Repetitive Pulse at TJstart=125C Conditions: VCC=13.5V VIN, IL Demagnetization Demagnetization Demagnetization Values are generated with RL=0 In case of repetitive pulses, Tjstart (at beginning of each demagnetization) of every pulse must not exceed the temperature specified above for curves B and C.

10

100

14/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

Figure 28. PPAK, P2PAK Maximum turn off current versus load inductance

ILMAX (A) 100

10

A B C

1 0.1 1 L(mH)

A = Single Pulse at TJstart=150C B= Repetitive pulse at TJstart=100C C= Repetitive Pulse at TJstart=125C Conditions: VCC=13.5V VIN, IL Demagnetization Demagnetization Demagnetization Values are generated with RL=0 In case of repetitive pulses, Tjstart (at beginning of each demagnetization) of every pulse must not exceed the temperature specified above for curves B and C.

10

100

15/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

SO-8 Thermal Data Figure 29. SO-8 PC Board

Layout condition of Rth and Zth measurements (PCB FR4 area= 58mm x 58mm, PCB thickness=2mm, Cu thickness=35m, Copper areas: 0.14cm2, 0.8cm2, 2cm2).

Figure 30. Rthj-amb Vs PCB copper area in open box free air condition

RTHj_amb (C/W)

SO-8 at 2 pins connected to TAB

110 105 100 95 90 85 80 75 70 0 0.5 1 1.5 2 2.5

PCB Cu heatsink area (cm^2)

16/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

P2PAK Thermal Data Figure 31. P2PAK PC Board

Layout condition of Rth and Zth measurements (PCB FR4 area= 60mm x 60mm, PCB thickness=2mm, Cu thickness=35m, Copper areas: 0.97cm2, 8cm2).

Figure 32. Rthj-amb Vs PCB copper area in open box free air condition

RTHj_amb (C/W)

55

Tj-Tamb=50C

50 45 40 35 30

0 2 4 6 8 10

PCB Cu heatsink area (cm^2)

17/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

PPAK Thermal Data Figure 33. PPAK PC Board

Layout condition of Rth and Zth measurements (PCB FR4 area= 60mm x 60mm, PCB thickness=2mm, Cu thickness=35m, Copper areas: 0.44cm2, 8cm2).

Figure 34. Rthj-amb Vs PCB copper area in open box free air condition

RTHj_amb (C/W)

90 80 70 60 50 40 30 20 10 0 0 2 4 6 8 10

PCB Cu heatsink area (cm^2)

18/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

Figure 35. SO-8 Thermal Impedance Junction Ambient Single Pulse

ZTH (C/W) 1000

100

0.5 cm2 2 cm2

10

0.1

0.01 0.0001 0.001 0.01 0.1 1 Time (s) 10 100 1000

Figure 36. Thermal fitting model of a single channel HSD in SO-8

Pulse calculation formula

TH

= R TH + Z THtp ( 1 ) = tp T

where

Table 14. Thermal Parameter

Tj

R1 R2 R3 R4 R5 R6 C1 C2 C3 C4 C5 C6

C1

C2

C3

C4

C5

C6

R1

R2

R3

R4

R5

R6

Pd

T_amb

Area/island (cm2) (C/W) (C/W) ( C/W) (C/W) (C/W) (C/W) (W.s/C) (W.s/C) (W.s/C) (W.s/C) (W.s/C) (W.s/C)

0.5 0.05 0.8 3.5 21 16 58 0.006 2.60E-03 0.0075 0.045 0.35 1.05

28

19/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

Figure 37. PPAK Thermal Impedance Junction Ambient Single Pulse

ZT H (C/W) 1000

100

0.44 cm2 6 cm2

10

0.1 0.0001 0.001 0.01 0.1 1 T ime (s) 10 100 1000

Figure 38. Thermal fitting model of a single channel HSD in PPAK

Pulse calculation formula

TH

= R TH + Z THtp ( 1 ) = tp T

where

Table 15. Thermal Parameter

Tj

R1 R2 R3 R4 R5 R6 C1 C2 C3 C4 C5 C6

C1

C2

C3

C4

C5

C6

R1

R2

R3

R4

R5

R6

Pd

T_amb

Area/island (cm2) (C/W) (C/W) ( C/W) (C/W) (C/W) (C/W) (W.s/C) (W.s/C) (W.s/C) (W.s/C) (W.s/C) (W.s/C)

0.5 0.15 0.7 1.6 2 15 61 0.0006 0.0025 0.08 0.3 0.45 0.8

24

20/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

Figure 39. P2PAK Thermal Impedance Junction Ambient Single Pulse

ZTH (C/W) 1000

100

0.5 cm2 6 cm2

10

0.1 0.0001 0.001 0.01 0.1 1 Time (s) 10 100 1000

Figure 40. Thermal fitting model of a single channel HSD in P2PAK

Pulse calculation formula

TH

= R TH + Z THtp ( 1 ) = tp T

where

Table 16. Thermal Parameter

Tj

R1 R2 R3 R4 R5 R6 C1 C2 C3 C4 C5 C6

C1

C2

C3

C4

C5

C6

R1

R2

R3

R4

R5

R6

Pd

T_amb

Area/island (cm2) (C/W) (C/W) ( C/W) (C/W) (C/W) (C/W) (W.s/C) (W.s/C) (W.s/C) (W.s/C) (W.s/C) (W.s/C)

0.5 0.15 0.7 0.7 4 9 37 0.0006 0.0025 0.055 0.4 2 3

22

21/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

PACKAGE MECHANICAL Table 17. SO-8 Mechanical Data

Symbol

A a1 a2 a3 b b1 C c1 D E e e3 F L M S L1 0.8 8 (max.) 1.2 3.8 0.4 4.8 5.8 1.27 3.81 4 1.27 0.6 0.65 0.35 0.19 0.25 45 (typ.) 5 6.2 0.1

millimeters Min Typ Max

1.75 0.25 1.65 0.85 0.48 0.25 0.5

Figure 41. SO-8 Package Dimensions

22/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

PACKAGE MECHANICAL Table 18. PENTAWATT (VERTICAL) Mechanical Data

Symbol

A C D D1 E F F1 G G1 H2 H3 L L1 L2 L3 L5 L6 L7 M M1 Diam. 3.65 2.6 15.1 6 4.5 4 3.85 10.05 17.85 15.75 21.4 22.5 3 15.8 6.6 2.4 1.2 0.35 0.8 1 3.2 6.6 3.4 6.8

millimeters Min Typ Max

4.8 1.37 2.8 1.35 0.55 1.05 1.4 3.6 7 10.4 10.4

Figure 42. PENTAWATT (VERTICAL) Package Dimensions

23/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

PACKAGE MECHANICAL Table 19. P2PAK Mechanical Data

Symbol

A A1 A2 b c c2 D D2 E E1 e e1 L L2 L3 L5 R V2 Package Weight 0 1.40 Gr (typ) 3.20 6.60 13.70 1.25 0.90 1.55 0.40 8 10.00 8.50 3.60 7.00 14.50 1.40 1.70 2.40

millimeters Min

4.30 2.40 0.03 0.80 0.45 1.17 8.95 8.00 10.40

Typ

Max

4.80 2.80 0.23 1.05 0.60 1.37 9.35

Figure 43. P2PAK Package Dimensions

P010R

24/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

PACKAGE MECHANICAL Table 20. PPAK Mechanical Data

Symbol

A A1 A2 B B2 C C2 D1 D E E1 e G G1 H L2 L4 R V2 Package Weight 0 Gr. 0.3 0.60 0.2 8 4.90 2.38 9.35 0.8 6.00 6.40 4.7 1.27 5.25 2.70 10.10 1.00 1.00

millimeters Min

2.20 0.90 0.03 0.40 5.20 0.45 0.48 5.1 6.20 6.60

Typ

Max

2.40 1.10 0.23 0.60 5.40 0.60 0.60

Figure 44. PPAK Package Dimensions

P032T1

25/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

Figure 45. SO-8 TUBE SHIPMENT (no suffix)

Base Q.ty Bulk Q.ty Tube length ( 0.5) A B C ( 0.1)

All dimensions are in mm.

100 2000 532 3.2 6 0.6

Figure 46. SO-8 TAPE AND REEL SHIPMENT (suffix TR) REEL DIMENSIONS

Base Q.ty Bulk Q.ty A (max) B (min) C ( 0.2) F G (+ 2 / -0) N (min) T (max)

2500 2500 330 1.5 13 20.2 12.4 60 18.4

All dimensions are in mm.

TAPE DIMENSIONS

According to Electronic Industries Association (EIA) Standard 481 rev. A, Feb 1986

Tape width Tape Hole Spacing Component Spacing Hole Diameter Hole Diameter Hole Position Compartment Depth Hole Spacing

W P0 ( 0.1) P D ( 0.1/-0) D1 (min) F ( 0.05) K (max) P1 ( 0.1)

12 4 8 1.5 1.5 5.5 4.5 2

End

All dimensions are in mm.

Start Top cover tape 500mm min Empty components pockets saled with cover tape. User direction of feed 500mm min No components Components No components

26/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

Figure 47. PENTAWAT TUBE SHIPMENT (no suffix)

Base Q.ty Bulk Q.ty Tube length ( 0.5) A B C ( 0.1)

All dimensions are in mm.

50 1000 532 18 33.1 1

27/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

Figure 48. P2PAK TUBE SHIPMENT (no suffix)

Base Q.ty Bulk Q.ty Tube length ( 0.5) A B C ( 0.1)

All dimensions are in mm.

50 1000 532 18 33.1 1

Figure 49. P2PAK TAPE AND REEL SHIPMENT (suffix TR)

REEL DIMENSIONS

Bulk Q.ty A (max) B (min) C ( 0.2) F G (+ 2 / -0) N (min) T (max)

1000 330 1.5 13 20.2 24.4 60 30.4

All dimensions are in mm.

TAPE DIMENSIONS

According to Electronic Industries Association (EIA) Standard 481 rev. A, Feb 1986

Tape width Tape Hole Spacing Component Spacing Hole Diameter Hole Diameter Hole Position Compartment Depth Hole Spacing

W P0 ( 0.1) P D ( 0.1/-0) D1 (min) F ( 0.05) K (max) P1 ( 0.1)

24 4 16 1.5 1.5 11.5 6.5 2

End

All dimensions are in mm.

Start Top cover tape 500mm min Empty components pockets saled with cover tape. User direction of feed 500mm min No components Components No components

28/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

Figure 50. PPAK SUGGESTED PAD LAYOUT and TUBE SHIPMENT (no suffix)

A C

Base Q.ty Bulk Q.ty Tube length ( 0.5) A B C ( 0.1)

All dimensions are in mm.

75 3000 532 6 21.3 0.6

1.8

6.7

Figure 51. PPAK TAPE AND REEL SHIPMENT (suffix TR)

REEL DIMENSIONS

Base Q.ty Bulk Q.ty A (max) B (min) C ( 0.2) F G (+ 2 / -0) N (min) T (max)

2500 2500 330 1.5 13 20.2 16.4 60 22.4

All dimensions are in mm.

TAPE DIMENSIONS

According to Electronic Industries Association (EIA) Standard 481 rev. A, Feb 1986

Tape width Tape Hole Spacing Component Spacing Hole Diameter Hole Diameter Hole Position Compartment Depth Hole Spacing

W P0 ( 0.1) P D ( 0.1/-0) D1 (min) F ( 0.05) K (max) P1 ( 0.1)

16 4 8 1.5 1.5 7.5 2.75 2

End

All dimensions are in mm.

Start Top cover tape 500mm min Empty components pockets saled with cover tape. User direction of feed 500mm min No components Components No components

29/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

REVISION HISTORY Table 21. Revision History

Date

Oct. 2004

Revision

1 - First Issue.

Description of Changes

30/31

VN750-E / VN750S-E / VN750PT-E / VN750B5-E

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics. The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners 2004 STMicroelectronics - All rights reserved STMicroelectronics group of companies Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America www.st.com

31/31

This datasheet has been download from: www.datasheetcatalog.com Datasheets for electronics components.

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (120)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- QSC RMX5050Document8 pagesQSC RMX5050Yonatan RivadeneyraNo ratings yet

- 55th BMA Special Course Priliminary Question - 14 - Aug - 2020 - Signal (EEE, ECE, EECE)Document3 pages55th BMA Special Course Priliminary Question - 14 - Aug - 2020 - Signal (EEE, ECE, EECE)Sohag KhanNo ratings yet

- Atlas v2Document288 pagesAtlas v2Ashok GadhwalNo ratings yet

- General Description Product Summary: 30V P-Channel MOSFETDocument5 pagesGeneral Description Product Summary: 30V P-Channel MOSFETYonatan RivadeneyraNo ratings yet

- Description: Telecom Surge ProtectorsDocument15 pagesDescription: Telecom Surge ProtectorsYonatan RivadeneyraNo ratings yet

- AO4411Document6 pagesAO4411Yonatan RivadeneyraNo ratings yet

- 2SC1623 L4 L5 L6 L7Document4 pages2SC1623 L4 L5 L6 L7Yonatan RivadeneyraNo ratings yet

- AO3401Document5 pagesAO3401Yonatan RivadeneyraNo ratings yet

- Model En12 12Mm Rotary Encoder 2 Bits Gray Code Incremental/Contacting Type Metal Bushing/Plastic Shaft Push-On Switch Option Rohs CompliantDocument3 pagesModel En12 12Mm Rotary Encoder 2 Bits Gray Code Incremental/Contacting Type Metal Bushing/Plastic Shaft Push-On Switch Option Rohs CompliantYonatan RivadeneyraNo ratings yet

- Code Resistor - SMDDocument5 pagesCode Resistor - SMDYonatan RivadeneyraNo ratings yet

- BTM182Document6 pagesBTM182jmsosanNo ratings yet

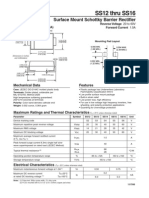

- SS12 Thru SS16: Surface Mount Schottky Barrier RectifierDocument2 pagesSS12 Thru SS16: Surface Mount Schottky Barrier RectifierYonatan RivadeneyraNo ratings yet

- MM-DT10 20060613105208703 DT10 12SchDocument4 pagesMM-DT10 20060613105208703 DT10 12SchYonatan RivadeneyraNo ratings yet

- HT8950 V 110Document10 pagesHT8950 V 110aliamservice6231No ratings yet

- 1N5822 - DatasheetDocument3 pages1N5822 - Datasheetjohny_mlNo ratings yet

- EEE 53 NotesDocument11 pagesEEE 53 NotesmiuhasdaNo ratings yet

- Ee2259 Set1Document11 pagesEe2259 Set1kaliappan45490No ratings yet

- An-9052 Design Guide For Selection of Bootstrap ComponentsDocument4 pagesAn-9052 Design Guide For Selection of Bootstrap Componentsディエゴ水上No ratings yet

- Dvd-s35 Manual TecnicoDocument78 pagesDvd-s35 Manual TecnicoCarlos Sanchez RiveraNo ratings yet

- ZMM 1... ZMM200: Silicon Planar Zener DiodesDocument8 pagesZMM 1... ZMM200: Silicon Planar Zener DiodesMu YuNo ratings yet

- Isolated Power SupplyDocument20 pagesIsolated Power SupplyHoangNo ratings yet

- CLASS XII PRE BOARD Physics QP 2023-24Document19 pagesCLASS XII PRE BOARD Physics QP 2023-24suprajabhupalanNo ratings yet

- Rain AlarmDocument3 pagesRain AlarmSebastin AshokNo ratings yet

- Auraton 2020 2020txplus en PDFDocument29 pagesAuraton 2020 2020txplus en PDFNikoletta GólyaNo ratings yet

- Joam 20 (5-6) (2018) 319 - 325Document7 pagesJoam 20 (5-6) (2018) 319 - 325Pankaj SharmaNo ratings yet

- Bio MEMSDocument52 pagesBio MEMSShobhit SinghNo ratings yet

- 2SK241Document7 pages2SK241ytnateNo ratings yet

- Transistor Curve TracerDocument26 pagesTransistor Curve TracerpecceriniNo ratings yet

- National Electric CodeDocument10 pagesNational Electric CodeRen MariNo ratings yet

- Fiber Optics Ece Board ExamDocument7 pagesFiber Optics Ece Board ExamSharon CarilloNo ratings yet

- Multi VibratorsDocument8 pagesMulti VibratorsAnshitNo ratings yet

- Laboratory 6 - VCODocument2 pagesLaboratory 6 - VCOAriana Ribeiro LameirinhasNo ratings yet

- Rework ProfilesDocument30 pagesRework ProfilesJean TiepoNo ratings yet

- Sram 6TDocument5 pagesSram 6Taashish kumarNo ratings yet

- Electromechanical Energy Conversion II: Dr. Ali M. EltamalyDocument43 pagesElectromechanical Energy Conversion II: Dr. Ali M. EltamalyYacine BendjeddouNo ratings yet

- Research Areas For Mechatronics EngineeringDocument2 pagesResearch Areas For Mechatronics EngineeringRohithGiridharan100% (1)

- Leakage Current Measurement BasicsDocument4 pagesLeakage Current Measurement Basicsyasararafat12010100% (1)

- Irgp 50 B 60 PD 1Document11 pagesIrgp 50 B 60 PD 1pufipufi5No ratings yet

- MPMC University Question Papaers PDFDocument15 pagesMPMC University Question Papaers PDFRajasekar PichaimuthuNo ratings yet

- FIG. locus of - 1+Aβ - =1: vf V VDocument13 pagesFIG. locus of - 1+Aβ - =1: vf V VMohanNo ratings yet

- Aplicatii LM339 PDFDocument36 pagesAplicatii LM339 PDFone_blanche6175100% (1)

- Kramer DriveDocument42 pagesKramer DriveSenthil Kumar100% (1)

- Inverter-Based Resource Performance Guideline NERCDocument97 pagesInverter-Based Resource Performance Guideline NERCSubhadeep PaladhiNo ratings yet