Professional Documents

Culture Documents

VLSI LAB Questions

Uploaded by

krishnagdeshpandeCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

VLSI LAB Questions

Uploaded by

krishnagdeshpandeCopyright:

Available Formats

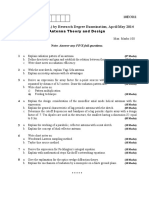

Q. No. 1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

Description a) Write a Verilog Code to simulate SR- Flip/Flop and JK- Master- Slave Flip/Flop and Synthesize the design for 1ns timing constraints. b) Design a CMOS Differential Amplifier with proper aspect ratio to amplify 5mv of 1KHz and 10mv of 1KHz inputs and perform Transient & DC Analysis. a) Write a Verilog Code to simulate 4- Bit Serial Adder and Synthesize the design for 1ns timing constraints. b) Design a CMOS Inverter with proper aspect ratio and perform Transient & DC Analysis for a input signal of pulse period 30ns and pulse width 20ns. a) Write a Verilog Code to simulate 4- Bit Successive Approximation register[SAR] and Synthesize the design for 1ns timing constraints. b) Design a CMOS Common- Drain Amplifier with proper aspect ratio to amplify 5mv of 1KHz and perform Transient & DC Analysis. a) Write a Verilog Code to simulate 4- Bit Synchronous UP Counter and Synthesize the design for 1ns timing constraints. b) Design a CMOS Common- Source Amplifier with proper aspect ratio to amplify 100mv of 2KHz and perform Transient & DC Analysis. a) Write a Verilog Code to simulate 4- Bit Synchronous UP Counter and Synthesize the design for 1ns timing constraints. b) Design a CMOS Common- Source Amplifier with proper aspect ratio to amplify 500mv of 2KHz and perform Transient & DC Analysis. a) Write a Verilog Code to simulate 4- Bit Asynchronous UP Counter and Synthesize the design for 1ns timing constraints. b) Design a CMOS Common- Drain Amplifier with proper aspect ratio to amplify 5mv of 1KHz and perform Transient & DC Analysis. a) Write a Verilog Code to Simulate 4- Bit Serial-In & Serial Out Shift register and Synthesize the design for 1ns timing constraints. b) Design a CMOS Common- Source Amplifier with proper aspect ratio to amplify 500mv of 2KHz and perform Transient & DC Analysis. a) Write a Verilog Code to simulate 5- Bit Parallel Adder to add 32 and 30. b) Design a CMOS Op- Amp with proper aspect ratio to amplify 10mv of 2KHz and 5mv of 2KHz inputs and perform Transient & DC Analysis. a) Write a Verilog Code to simulate Ex-OR Gate using minimum number of NAND Gates Using Switch Level Description. b) Design a CMOS Op- Amp with proper aspect ratio to amplify 5mv of 5KHz and 3mv of 5KHz inputs and perform Transient & DC Analysis. a) Write a Verilog Code to simulate 4- Bit Asynchronous Down Counter and Synthesize the design for 1ns timing constraints. b) Design a CMOS Common- Drain Amplifier with proper aspect ratio to amplify 100mv of 10KHz and perform Transient & DC Analysis. a) Write a Verilog Code to simulate 3- input AND & OR Gates using Switch Level Description. b) Design a CMOS Differential Amplifier with proper aspect ratio to amplify 5mv of 1KHz and 2mv of 1KHz inputs and perform Transient & DC Analysis.

You might also like

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Engg Cutoff GenDocument33 pagesEngg Cutoff GenkrishnagdeshpandeNo ratings yet

- Cooperative User Scheduling in Massive MIMO SystemsDocument14 pagesCooperative User Scheduling in Massive MIMO SystemskrishnagdeshpandeNo ratings yet

- TopicsDocument3 pagesTopicskrishnagdeshpandeNo ratings yet

- 10EC011Document1 page10EC011krishnagdeshpandeNo ratings yet

- Vision Group On Science and Technology Call For Proposals Under VGST For Fy 2017-18Document10 pagesVision Group On Science and Technology Call For Proposals Under VGST For Fy 2017-18krishnagdeshpandeNo ratings yet

- Visvesvaraya Technological University, Belgaum: Semester Regular Exam FeeDocument1 pageVisvesvaraya Technological University, Belgaum: Semester Regular Exam FeekrishnagdeshpandeNo ratings yet

- Realization of All Logic Gates With HDL CodeDocument58 pagesRealization of All Logic Gates With HDL CodekrishnagdeshpandeNo ratings yet

- DSPLab99 DSPBasicDocument34 pagesDSPLab99 DSPBasickrishnagdeshpandeNo ratings yet

- Basics of DSPA NotesDocument59 pagesBasics of DSPA NotesBhushanHumneyNo ratings yet

- M.A.M. College of Engineering Trichy Ec2314 Digital Signal Processing Unit Ii Discrete Time System AnalysisDocument12 pagesM.A.M. College of Engineering Trichy Ec2314 Digital Signal Processing Unit Ii Discrete Time System AnalysiskrishnagdeshpandeNo ratings yet

- 1 Basics DSP AV IntroDocument36 pages1 Basics DSP AV IntroUbaid UmarNo ratings yet

- PCM 30dd02Document41 pagesPCM 30dd02krishnagdeshpandeNo ratings yet

- Computer-Integrated Manufacturing (CIM) Is An Umbrella Term For The Total IntegrationDocument1 pageComputer-Integrated Manufacturing (CIM) Is An Umbrella Term For The Total IntegrationkrishnagdeshpandeNo ratings yet

- Generic Sensing Hardware and Real-Time Reconstruction For Structured Analog SignalsDocument4 pagesGeneric Sensing Hardware and Real-Time Reconstruction For Structured Analog SignalskrishnagdeshpandeNo ratings yet

- Ph.D./M.Sc. (Engg.) by Research Program: 2014-15: BranchDocument2 pagesPh.D./M.Sc. (Engg.) by Research Program: 2014-15: BranchkrishnagdeshpandeNo ratings yet

- Matlab CodesDocument6 pagesMatlab CodeskrishnagdeshpandeNo ratings yet

- Matrix QRDDocument12 pagesMatrix QRDkrishnagdeshpandeNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- 5 WattsDocument4 pages5 WattsRabbia SalmanNo ratings yet

- Pretest in Grade 9 ScienceDocument3 pagesPretest in Grade 9 ScienceEj Rafael58% (12)

- Datasheet ArcMate-50iD-7LDocument1 pageDatasheet ArcMate-50iD-7LSocrates Orion Martinez OvalleNo ratings yet

- Crown Micro Tech 600 1200 2400 Operation ManualDocument28 pagesCrown Micro Tech 600 1200 2400 Operation ManualŞahin AşkarNo ratings yet

- APC Easy UPS On-Line SRV 1000VA 230V: Technical SpecificationsDocument3 pagesAPC Easy UPS On-Line SRV 1000VA 230V: Technical SpecificationsLucia EsaineNo ratings yet

- Control Ningbo NBSL Nsfc01-01 Control System (4sw)Document14 pagesControl Ningbo NBSL Nsfc01-01 Control System (4sw)Winderson Macauran89% (18)

- 02-2 Excitation CourseDocument31 pages02-2 Excitation CourseFulki Kautsar S100% (1)

- Nikola Tesla - by Sara Ester GredeljDocument18 pagesNikola Tesla - by Sara Ester GredeljJosé María TrinidadNo ratings yet

- HNC AUTOMATION HSM Series AC 220V Servo Motor CatalogDocument6 pagesHNC AUTOMATION HSM Series AC 220V Servo Motor CatalogTodi FindraNo ratings yet

- La 78040 NDocument4 pagesLa 78040 NIpuc Caguán NeivaNo ratings yet

- NLPWM v2.0 and v2.1 / Firmware 2.2 (Compatible With 2.0 and 2.1 Boards)Document1 pageNLPWM v2.0 and v2.1 / Firmware 2.2 (Compatible With 2.0 and 2.1 Boards)gaudeamus13No ratings yet

- RS485 - MODBUS Communication Protocol - EPM - 125KDocument14 pagesRS485 - MODBUS Communication Protocol - EPM - 125KSuray MittalNo ratings yet

- Vector Controller Based Speed Control of Induction Motor Drive With 3-Level SVPWM Based Inverter PDFDocument11 pagesVector Controller Based Speed Control of Induction Motor Drive With 3-Level SVPWM Based Inverter PDF1balamanianNo ratings yet

- Siemens HardwawreDocument5 pagesSiemens HardwawreDanilo CarvalhoNo ratings yet

- Mentor IIDocument107 pagesMentor IIMOHD AKHALAK AHAMADNo ratings yet

- DLL Design Examples, Design Issues - TipsDocument56 pagesDLL Design Examples, Design Issues - TipsdinsulpriNo ratings yet

- Temples of African GodsDocument10 pagesTemples of African Godsjeflinders80% (5)

- Fault ModelingDocument21 pagesFault ModelingRamarao ChNo ratings yet

- Deasystem Sliding Gate Livi 900kgDocument3 pagesDeasystem Sliding Gate Livi 900kgapi-306712365No ratings yet

- Era 1 PDFDocument2 pagesEra 1 PDFElektroninis PastasNo ratings yet

- TC4066BFDocument11 pagesTC4066BFdonghungstbNo ratings yet

- Aiwa NSX-VC58Document41 pagesAiwa NSX-VC580000AbdielNo ratings yet

- Splandek EsdDocument3 pagesSplandek Esdkiranmisale7No ratings yet

- ThermoweldDocument276 pagesThermoweldReginald D. De GuzmanNo ratings yet

- FEE 422 - Telecommunications and Electroacoustics B - Notes 2022 - Part 1Document86 pagesFEE 422 - Telecommunications and Electroacoustics B - Notes 2022 - Part 1Peter JumreNo ratings yet

- Ak56 Service ManualDocument50 pagesAk56 Service Manualnita_alecsandru100% (1)

- Witricity PresentationDocument26 pagesWitricity PresentationSamarth J Parikh100% (1)

- Catálogo Theft Deterrent Composite Cable (TDCC - LT21426)Document2 pagesCatálogo Theft Deterrent Composite Cable (TDCC - LT21426)Sergio Ortiz GarayNo ratings yet

- Temperature SwitchDocument6 pagesTemperature Switchkriss05No ratings yet

- 1 - Charges and Coulomb's Law: Electrostatics NotesDocument3 pages1 - Charges and Coulomb's Law: Electrostatics NotesMarina XuNo ratings yet