Professional Documents

Culture Documents

Eletronica Digital

Uploaded by

will0engCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Eletronica Digital

Uploaded by

will0engCopyright:

Available Formats

Eletrnica Digital

Lgica Combinacional e Seqencial

Conselho Regional do SENAI-CE

Jorge Parente Frota Jnior

Presidente

Ivan Rodrigues Bezerra

Vice-Presidente

Alexandre Pereira Silva

Joo Fernandes Fontenelle

Francisco de Assis Alves de Almeida

Delegados das Atividades Industriais

Hermano Frank Jnior

Jos Fernando Castelo Banco Ponte

Marcos Pinheiro de Oliveira Cavalcante

Suplentes dos Delegados das Atividades Industriais

Samuel Brasileiro Filho

Representante do Ministrio da Educao e Cultura

Franco de Magalhes Neto

Suplente do Ministrio da Educao e Cultura

Alberto Fernandes de Farias Neto

Representante do Ministrio do Trabalho

Jos Nunes Passos

Suplente do Ministrio do Trabalho

Departamento Regional do SENAI-CE

Francisco das Chagas Magalhes

Diretor Regional

Cid Fraga

Gerente do Centro de Formao Profissional Waldyr Diogo de Siqueira

Federao das Indstrias do Estado do Cear

Servio Nacional de Aprendizagem Industrial

Departamento Regional do Cear

Centro de formao Profissional

Waldyr Diogo de Siqueira

Eletrnica Digital

Lgica Combinacional e Seqencial

Fortaleza-Cear

2004

2004. SENAI. Departamento Regional do Cear

Qualquer parte desta obra poder ser reproduzida, desde que citada a fonte.

SENAI/CE

Centro de Formao Profissional Waldyr Diogo de Siqueira CFP WDS

Ncleo de Educao Profissional NEP

Este projeto foi elaborado por colaboradores desta unidade de negcios cujos nomes esto

relacionados na folha de crditos.

Ficha Catalogrfica

S474 SENAI. CE. CFP. WDS. Eletrnica Digital. Fortaleza, 2004. 177p. il

1 ELETRNICA DIGITAL I TTULO

CDU 621.3

SENAI Departamento Av. Francisco S, 7221

Servio Nacional Regional do Cear Barra do Cear

de Aprendizagem 60.310-003 Fortaleza Cear

Industrial Telefax: (85) 485-7888

e-mail: senai-wds@sfiec.org.br

SUMRIO

1. SISTEMA DE NUMERAO

1.1 Introduo

1.2 O Sistema Binrio de Numerao

1.3 Odmetro Decimal

1.4 Odmetro Binrio

1.5 Converso do Sistema Binrio para o Sistema Decimal

1.6 Converso do Sistema Decimal para o Sistema Binrio

1.7 O Sistema Octal de Numerao

1.8 Converso do Sistema Octal para o Sistema Decimal

1.9 Converso do Sistema Decimal para o Sistema Octal

1.10 O Sistema Hexadecimal de Numerao

1.11 Converso do Sistema Hexadecimal para o Sistema Decimal

1.12 Converso do Sistema Decimal para o Sistema Hexadecimal

2. FUNES E PORTAS LGICAS

2.1 Introduo

2.2 Funes Lgicas E, OU, NO NE e NOU

2.3 Funo E OU AND

2.4 Funo OU ou OR

2.5 Funo NO ou NOT

2.6 Funo NO E, NOU ou NAND

2.7 Funo NO OU, NOU ou NOR

2.8 Bloco OU EXCLUSIVO

2.9 Bloco COINCIDNCIA

2.10 Quadro Resumo

3. LGEBRA DE BOOLE E SIMPLIFICAO DE CIRCUITOS

LGICOS

3.1 Introduo

3.2 Variveis e Expresses na lgebra de Boole

10

10

10

10

11

13

14

16

17

18

18

19

20

21

21

21

22

24

25

26

27

28

29

30

32

32

32

3.3 Postulados

3.4 Simplificao de Expresses Booleanas

4. DIAGRAMAS DE VEITCH-KARNAUGH

4.1 Mtodo da Soma de Produtos

4.2 Equao da Soma de Produtos

4.3 Circuito Lgico

4.4 Tabela-Verdade para Mapa de Karnaugh

4.5 Mapas de Trs Variveis

4.6 Mapas de Quatro Variveis

4.7 Pares, Quadros e Octetos

4.8 Quadros

4.9 O Octeto

4.10 Simplificaes de Karnaugh

4.11 Sobrepondo Grupos

4.12 Enrolando o Mapa

5. CIRCUITOS COMBINACIONAIS (1 PARTE)

5.1 Introduo

5.2 Projetos de Circuitos Combinacionais

5.3 Circuitos com 2 Variveis

5.4 Circuitos com 3 Variveis

6. CIRCUITOS COMBINACIONAIS (2 PARTE)

6.1 Introduo

6.2 Cdigos

6.3 Cdigos BCD 8421

6.4 Codificadores e Decodificadores

6.5 Codificadores Decimais / Binrios

6.6 Decodificadores Binrios / Decimais

32

34

36

36

36

37

38

39

40

40

41

41

41

42

43

44

44

44

45

46

48

48

48

48

49

50

51

6.7 Decodificador para Display de 7 Segmentos

6.8 Circuitos Aritmticos

6.9 Meio Somador

6.10 Somador Completo

6.11 Meio Subtrator

6.12 Subtrator Completo

6.13 Somador / Subtrator Completo

7. FLIP FLOP REGISTRADORES E CONTADORES

7.1 Introduo

7.2 Flip Flops

7.3 Flip Flop RS Bsico

7.4 Flip Flop RS com Entrada Clock

7.5 Flip Flop JK

7.6 Flip Flop JK com Entradas Preset e Clear

7.7 Flip Flop JK Mestre-Escravo

7.8 Flip Flop JK Mestre-Escravo com Entrada Preset e Clear

7.9 Flip Flop Tipo T

7.10 Flip Flop Tipo D

7.11 Registradores de Deslocamento

7.12 Conversor Srie-Paralelo

7.13 Conversor Paralelo-Srie

7.14 Contadores

7.15 Contadores Utilizados em Circuitos Temporizadores

8. CIRCUITOS MULTIPLEX E DEMULTIPLEX

8.1 Introduo

8.2 Multiplex

8.3 Projeto do Circuito de um Multiplex

8.4 Amplificao da Capacidade de um Sistema Multiplex

53

56

56

57

60

62

64

66

66

66

67

68

70

70

71

72

73

74

75

75

77

78

85

87

87

87

88

89

8.4 Amplificao da Capacidade de um Sistema Multiplex

8.5 Demultiplex

8.6 Projeto do Circuito de um Demultiplex

8.7 Ampliao da Capacidade de um Circuito Demultiplex

8.8 Multiplex e Demultiplex Utilizados na Transmisso de Dados

9. FAMLIAS DE CIRCUITOS LGICOS

9.1 Nveis de Tenso e de Corrente

9.2 Caractersticas Gerais e Parmetros da Famlia TTL

9.3 Verses dos Circuitos TTL

9.4 Caractersticas Gerais e Parmetros da Famlia CMOS

9.5 Circuitos Integrados CMOS

9.6 Circuitos Integrados TTL

10. ENSAIOS DE ELETRNICA DIGITAL

10.1 Ensaio 1 Introduo a Eletrnica Digital

10.2 Ensaio 2 Portas Lgicas

10.3 Ensaio 3 lgebra Booleana

10.4 Ensaio 4 Circuitos Combinacionais

10.5 Ensaio 5 Decodificador BCD 8421 para Display de 7 Segmentos

10.6 Ensaio 6 Circuitos Aritmticos

10.7 Ensaio 7 Flip-Flops

10.8 Ensaio 8 Contadores Assncronos

10.9 Ensaio 9 Contadores Sncronos

10.10 Ensaio 10 Multiplex / Demultiplex

10.11 Ensaio 11 Registradores de Deslocamento

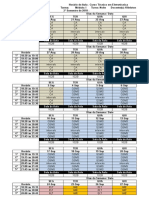

11. DIGITAL INTEGRATED CIRCUITS

11.1 Function Selection Chart

11.2 Functional Diagrams

11.3 Packages and Ordering Information

89

92

92

94

95

97

97

98

99

100

101

102

103

103

106

109

110

116

117

119

121

124

127

131

133

133

136

149

11.4 Comparisan Table for Integrated Circuits

11.5 TTL Series (Transistor-Transistor-Logic)

11.6 LSL-Series (Low-Speed Noise- Immune Logic)

REFERNCIAS BIBLIOGRFICAS

150

151

171

1 SISTEMA DE NUMERAO

1.1 Introduo

O homem, atravs dos tempos, sentiu a necessidade da utilizao de sistemas

numricos.

Existem vrios sistemas numricos, dentre os quais se destacam: o sistema decimal,

o binrio, o octal e o hexadecimal.

O sistema decimal utilizado por ns no dia-a-dia e , sem dvida, o mais

importante dos sistemas numricos. Trata-se de um sistema que possui dez

algarismos, com os quais podemos formar qualquer nmero, atravs da lei de

formao.

Os sistemas: binrio, octal e hexadecimal so muito importantes na rea de tcnicas

digitais e computao.

1.2 O Sistema Binrio de Numerao

O sistema binrio de numerao um sistema no qual existem apenas dois

algarismos:

- O algarismo 0 (zero), e

- O algarismo 1 (um).

1.3 Odmetro Decimal

Para entender como contar com nmeros binrios vamos ver como um odmetro

(indicador de quilmetros de um carro) conta com nmeros decimais. Quando o

carro novo, seu odmetro comea com:

0 0 0 0 0

Aps um quilmetro a leitura se torna:

10

0 0 0 0 1

Quilmetros sucessivos produzem 00002, 00003 e assim por diante, at:

0 0 0 0 9

Algo familiar ocorre ao final do dcimo quilmetro. Quando a roda das unidades

comuta de 9 outra vez para 0, um pino nessa roda fora a roda das dezenas a

avanar de 1. por isso que o nmero muda para:

0 0 0 1 0

A roda das unidades foi colocada em 0 e enviou um vai-um para a roda das

dezenas. Chamemos esse processo familiar de zeragem e vai-um. As outras rodas

de um odmetro tambm so zeradas e enviam-um. Por exemplo, aps 999

quilmetro mostra:

0 0 9 9 9

O que o prximo quilmetro faz? A roda das unidades zerada e envia-um, a roda

das dezenas zerada e envia-um, roda das centenas zerada e envia-um, e a roda

dos milhares avana de 1, para obter:

0 1 0 0 0

1.4 Odmetro Binrio

Imagine um odmetro binrio, um dispositivo cujas rodas tem somente dois dgito, 0

e 1. Quando cada roda comuta, ele mostra 0, depois 1, novamente 0, e o ciclo se

repete. Um odmetro binrio de quatro dgitos comea com:

0 0 0 0

11

Aps um quilmetro ele indica:

0 0 0 1

O prximo quilmetro fora a roda das unidades a zerar e enviar-um; assim os

nmeros mudam para:

0 0 1 0

O terceiro quilmetro resulta em:

0 0 1 1

Aps quatro quilmetro, a roda das unidades zera e envia-um, a segunda roda zera

e envia-um, e a terceira roda avana de 1:

0 1 0 0

A tabela mostra todos os nmeros binrios de 0000 a 1111, equivalentes aos

decimais de 0 a 15.

Decimal Binrio Decimal Binrio

0

1

2

3

4

5

6

7

0000

0001

0010

0011

0100

0101

0110

0111

8

9

10

11

12

13

14

15

1000

1001

1010

1011

1100

1101

1110

111

12

1.5 Converso do Sistema Binrio para o Sistema Decimal

Para explicar a converso vamos utilizar um nmero decimal qualquer, por exemplo,

o nmero 594. Este nmero significa:

5 x 100 + 9 x 10 + 4 x 1 = 594

+ + +

Centena dezena unidade

q q q

5 x 10

2

+ 9 x 10

1

+ 4 x 10

0

= 594

Esquematicamente, temos:

100 10 1

5 9 4

10

2

10

1

10

0

5 9 4

Neste exemplo podemos notar que o algarismo menos significativo (4) multiplica a

unidade (1 ou 100), o segundo algarismo (9) multiplica a dezena (10 ou 101) e o

mais significativo (5) multiplica a centena (100 ou 102). A soma desses resultados ir

representar o nmero.

Podemos notar ainda, que a regra bsica de formao de um nmero consiste no

somatrio de cada algarismo correspondente multiplicado pela base (no exemplo o

nmero dez) elevada por ndice conforme o posicionamento do algarismo no

nmero.

Vamos agora utilizar um nmero binrio qualquer, por exemplo, o nmero 101. Pela

tabela notamos que este nmero equivale ao nmero 5 no sistema decimal.

13

5 x 100 + 9 x 10 + 4 x 1 = 594

5 x 10

2

+ 9 x 10

1

+ 4 x 10

0

= 594

Utilizando o conceito bsico de formao de um nmero, podemos obter a mesma

equivalncia, convertendo assim o nmero para o sistema decimal.

2

2

2

1

2

0

1 0 1

1 x 2

2

+ 0 x 2

1

+ 1 x 2

0

= 5

1 x 4 + 0 x 2 + 1 x 1 = 5

O nmero 101 na base 2 igual ao nmero 5 na base 10.

Daqui por diante, para melhor identificao do nmero, colocar como ndice base

do sistema ao qual o nmero pertence. Assim sendo, para o exemplo podemos

escrever:

101

2

= 5

10

Exerccios

1 Converta o nmero 01110

2

em decimal.

2 Converta o nmero 1010

2

em decimal.

3 Converta o nmero 1100110001

2

em decimal.

1.6 Converso do Sistema Decimal para o Sistema Binrio

Como vimos necessidade da converso sistema binrio para decimal evidente,

pois, se tivermos um nmero grande no sistema binrio, fica difcil perceber a

quantidade que este representa. Transformando-se este nmero para decimal, o

problema desaparece.

Veremos agora a transformao inversa, ou seja, a converso de um nmero do

sistema decimal para o sistema binrio.

14

Para demonstrar o processo, vamos utilizar um nmero decimal qualquer, por

exemplo, o nmero 47.

Dividindo o nmero 47 por 2, temos:

Dividindo agora 23 por 2, temos:

Dividindo agora 11 por 2, temos:

Dividindo agora 5 por 2, temos:

Dividindo agora 2 por 2, temos:

Mtodo das divises sucessivas consiste em efetuar-se sucessivas divises pela

base a ser convertida (no caso 2) at o ltimo quociente possvel. O nmero

transformado ser composto por este quociente (algarismo mais significativo) e,

todos os restos, na ordem inversa s divises. Dessa forma, temos:

15

47 2

1 23

1 resto

23 2

1 11

2 resto

11 2

1 5

3 resto

5 2

1 2

4 resto

2 2

0 1

5 resto ltimo quociente

MSB LSB

1 0 1 1 1 1

ltimo 5 4 3 2 1

Quociente resto resto resto resto resto

101111

2

= 47

10

Na prtica o bit menos significativo de um nmero binrio recebe a notao de LSB

(em ingls: Least Significant Bit) e o bit mais significativo de MSB (Most Significant

Bit).

Exerccios:

1 Converta o nmero 21

10

em binrio.

2 Converta o nmero 552

10

em binrio.

3 Converta o nmero 715

10

em binrio.

1.7 O Sistema Octal de Numerao

O sistema octal de numerao um sistema no qual existem oito algarismos:

0, 1, 2, 3, 4, 5, 6, 7

Para representarmos a quantidade oito, agimos do mesmo modo, visto

anteriormente, para nmeros binrios e decimais. Colocamos o algarismo 1 seguido

do algarismo 0.

Atualmente, o sistema Octal praticamente pouco utilizado no campo da Eletrnica

Digital, tratando apenas de um sistema numrico intermedirio dos sistemas binrio

e hexadecimal.

16

A tabela mostra a seqncia de numerao do sistema octal.

Decimal Octal Decimal Octal

0

1

2

3

4

5

6

7

8

9

0

1

2

3

4

5

6

7

10

11

10

11

12

13

14

15

16

17

18

19

12

13

14

15

16

17

20

21

22

23

1.8 Converso do Sistema Octal para o Sistema Decimal

Para convertermos um nmero octal em decimal, utilizamos o conceito bsico de

formao de um nmero, conforme j visto.

Vamos, por exemplo, converter o nmero 144

8

em decimal:

8

2

8

1

8

0

1 4 4

1 x 8

2

+ 4 x 8

1

+ 4 x 8

0

=

1 x 64 + 4 x 8 + 4 x 1 = 64 + 32 + 4 = 100

10

144

8

= 100

10

Exerccios

17

1 Converta o nmero 77

8

em decimal.

2 Converta o nmero 100

8

em decimal.

3 Converta o nmero 476

8

em decimal.

1.9 Converso do Sistema Decimal para o Sistema Octal

O processo anlogo converso do sistema decimal para o binrio, somente que

neste caso, utilizaremos a diviso por 8, pois sendo o sistema octal, sua base igual

a 8.

Para exemplificar, vamos converter o nmero 92

10

para o sistema octal:

92

10

= 134

8

Exerccios

1 Converta o nmero 74

10

em octal.

2 Converta o nmero 512

10

em octal.

3 Converta o nmero 719

10

em octal.

1.10 O Sistema Hexadecimal de Numerao

O sistema hexadecimal possui dezesseis algarismos, sendo sua base igual a 16. Os

algarismos so assim enumerados:

0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F

Notamos que a letra A representa o algarismo A, que por sua vez representa a

quantidade dez. A letra B representa o algarismo B, que representa a quantidade

onze, e assim sucede-se at a letra F que representa a quantidade quinze.

18

92 8

1 11 8

3 1

2 resto

1 resto

ltimo quociente

Para representarmos a quantidade dezesseis, colocamos o algarismo 1 (um)

seguido do algarismo 0 (zero).

Aps esta introduo, podemos escrever a seqncia de numerao hexadecimal.

Decimal Hexadecimal Decimal Hexadecimal

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

F

10

11

12

13

14

15

16

17

18

19

1A

1B

1C

1D

Este sistema muito utilizado em microprocessadores e tambm no mapeamento de

memrias de mquinas digitais com palavras 4, 8, 16 ou 32 bits.

1.11 Converso do Sistema Hexadecimal para o Sistema Decimal

A regra de converso anloga de outros sistemas, somente que neste caso, a

base 16. Como exemplo, vamos utilizar o nmero 3 F

16

e convert-lo em decimal:

16

1

16

0

3 F

2 x 16

1

+ F x 16

0

=

Sendo F

16

= 15

10

, substituindo temos:

3 x 16

1

+ 15 x 16

0

= 3 x 16 + 15 x 1 = 63

10

3 F

16

= 63

10

19

Exerccios

1 Converta o nmero 1C3

16

em decimal.

2 Converta o nmero 238

16.

3 Converta o nmero 1 FC9

16

em decimal.

1.12 Converso do Sistema Decimal para o Sistema Hexadecimal

Da mesma forma que nos casos anteriores, esta converso se faz atravs de

divises sucessivas pela base do sistema a ser convertido. Para exemplificar vamos

transformar o nmero 1000

10

em hexadecimal:

Sendo 14

10

= E

16

, temos: 3E8

16

1000

10

= 3E8

16

Exerccios

1 Converta o nmero 134

10

para o sistema hexadecimal.

2 Converta o nmero 384

10

para o sistema hexadecimal.

3 Converta o nmero 3882

10

para o sistema hexadecimal.

20

1000 16

8 62 16

14 3

ltimo quociente

1 resto

2 resto

2 FUNES E PORTAS LGICAS

2.1 Introduo

Em 1854, o matemtico ingls George Boole (1815 1864), atravs da obra

intitulada na Investigation of the Laws of Thought, apresentou um sistema

matemtico de anlise lgica conhecido como lgebra de Boole.

No incio da era da eletrnica, todos os problemas eram resolvidos por sistemas

analgicos, tambm conhecidos por sistemas lineares.

Apenas em 1938, o engenheiro americano Claude Elwood Shannon utilizou as

teorias da lgebra de Boole para a soluo de problemas de circuitos de telefonia

com rels, tendo publicado um trabalho denominado Symbolic Analysis of Relay

and Switching, praticamente introduzindo na rea tecnolgica o campo da

eletrnica digital.

Esse ramo de eletrnica emprega em seus sistemas um pequeno grupo de circuitos

bsicos padronizados conhecidos como portas lgicas.

Atravs da utilizao conveniente destas portas, podemos implementar todas as

expresses geradas pela lgebra de Boole, que constituem a base dos projetos dos

sistemas j referidos.

2.2 Funes Lgicas E, OU, NO, NE e NOU

Faremos, a seguir, o estudo das principais funes lgicas que na realidade derivam

dos postulados da lgebra de Boole, sendo as variveis e expresses envolvidas

denominadas de booleanas.

Nas funes lgicas, temos apenas dois estados distintos:

21

= O estado 0 (zero) e

= O estado 1 (um).

O estado 0 representar, Por exemplo: porto fechado, aparelho desligado,

ausncia de tenso, chave aberta, no, etc. O estado 1 representar, ento: porto

aberto, aparelho ligado, presena de tenso, chave fechada, sim, etc.

2.3 Funo E ou AND

A funo E aquela que executa a multiplicao de 2 ou mais variveis booleanas.

tambm conhecida como funo AND, nome derivado do ingls. Sua

representao algbrica para 2 variaes S = A . B, onde se l S = A e B.

Para melhor compreenso, vamos utilizar e analisar o circuito representativo da

funo E visto na figura.

Convenes: chave aberta = 0 chave fechada = 1

Lmpada apagada = 0 lmpada acesa =1

Analisando as situaes, conclumos que s teremos a lmpada acesa quando as

chaves A e B estiverem fechadas.

Tabela da Verdade de uma Funo E ou AND

22

Chamamos Tabela da Verdade um mapa onde colocamos todas as possveis

situaes com seus respectivos resultados. Na tabela, iremos encontrar o modo

como a funo se comporta. A seguir, iremos apresentar a tabela da verdade de

uma funo E ou AND para 2 variveis de entrada:

Porta E ou AND

A porta E um circuito que executa a funo E, sendo representada na prtica,

atravs do smbolo visto na figura.

Como j dissemos, a porta E executa a tabela da verdade da funo E, ou seja,

teremos a sada no estado 1 se, e somente se, as 2 entradas forem iguais a 1, e

teremos a sada igual a 0 nos demais casos.

Notamos que a tabela da verdade mostra as 4 possveis combinaes das variveis

de entrada e seus respectivos resultados na sada.

O nmero de situaes possveis a 2

N

, onde N o nmero de variveis de entrada.

Exemplo: N = 3 2

3

= 8.

23

A B S

0 0

0 1

1 0

1 1

0

0

0

1

2.4 Funo OU ou OR

A funo OU aquela que assume valor 1 quando uma ou mais variveis da entrada

forem iguais a 1 e assume valor 0 se, e somente se, todas as variveis de entrada

forem iguais a 0. Sua representao algbrica para 2 variveis de entrada S = A +

B, onde se l S = A ou B.

O termo OR, tambm utilizado, derivado do ingls.

Para entendermos melhor a funo OU, vamos representa-la atravs do circuito da

figura.

Usaremos as mesmas convenes do circuito representativo da funo E, visto

anteriormente.

Notamos pelas situaes que teremos a lmpada ligada quando chA ou chB ou

ambas as chaves estiverem ligadas.

Tabela da Verdade da Funo OU ou OR

Nesta tabela da verdade, teremos todas as situaes possveis com os respectivos

valores que a funo OU assume. A tabela apresenta a tabela da verdade da funo

OU ou OR para 2 variveis de entrada.

24

A B S

0 0

0 1

1 0

1 1

0

1

1

1

Porta OU ou OR

a porta que executa a funo OU. Representaremos a porta OU atravs do

smbolo visto na figura.

A porta OU executa a tabela da verdade de funo OU, ou seja, teremos a sada

igual a 1 quando uma ou mais variveis de entrada forem iguais a 1 e 0 se, e

somente se, todas as variveis de entrada forem iguais a 0.

2.5 Funo NO ou NOT

A funo NO aquela que inverte ou complementa o estado da varivel, ou seja,

se a varivel estiver em 0, sada vai para 1, e se estiver em 1, sada vai para 0.

representada algebricamente da seguinte forma: S = A ou S = A, onde se l A

barra ou NO A.

Esta barra ou apstrofo sobre a letra que representa a varivel significa que esta

sofre uma inverso. Tambm, podemos dizer que A significa a negao de A.

Para entendermos melhor a funo NO vamos represent-la pelo circuito da figura.

Analisaremos utilizando as mesmas convenes dos casos anteriores.

25

Tabela da Verdade da Funo NO ou NOT

A tabela apresenta casos possveis da funo NO.

A S

0

1

1

0

Inversor

O inversor o bloco lgico que executa a funo NO.

Suas representaes simblicas so vistas na figura.

2.6 Funo NO E, NE ou NAND.

Como o prprio nome NO E diz: essa funo uma composio da funo E com

a funo NO, ou seja, teremos a funo E invertida. representada

algebricamente da seguinte forma:

S = ( A . B ), onde o trao indica que temos a inverso do produto A.B.

26

A S

(antes de um outro bloco lgico)

Tabela da Verdade da Funo NE ou NAND

A tabela apresenta a funo NE para 2 variveis de entrada.

A B S

0 0

0 1

1 0

1 1

1

1

1

0

Pela tabela da verdade, podemos notar que esta funo o inverso da funo E.

Porta NE ou NAND

A porta NE o bloco lgico que executa a funo NE.

Sua representao simblica vista na figura.

2.7 Funo NO OU, NOU ou NOR.

Analogamente funo NE, a funo NOU a composio da funo NO com a

funo OU, ou seja, a funo NOU ser o inverso da funo OU. representada da

seguinte forma:

S = ( A + B ), onde o trao indica a inverso da soma booleana A + B.

Tabela da Verdade da Funo NOU ou NOR

A tabela apresenta a funo NOU para 2 variveis de entrada.

27

A

B

S

A B S

0 0

0 1

1 0

1 1

1

0

0

0

Podemos notar pela tabela da verdade que a funo NOU representa a funo Ou

invertida.

Porta NOU ou NOR

A porta NOU o bloco lgico que executa a funo NOU. Sua representao

simblica vista na figura.

2.8 Bloco OU EXCLUSIVO

A funo que ele executa, como o prprio nome diz, consiste em fornecer 1 sada

quando as variveis de entrada forem diferentes entre si.

28

A B S

0 0

0 1

1 0

1 1

0

1

1

0

Da tabela obtemos sua expresso caracterstica:

S = A . B + A . B

A notao algbrica que representa a funo OU Exclusivo S = A B, onde se l

A OU Exclusivo B, sendo S = A B = A . B + A . B. O circuito OU Exclusivo pode ser

representado tambm pelo smbolo visto na figura.

Uma importante observao que, ao contrrio de outros blocos lgicos bsicos, o

circuito OU Exclusivo s pode ter 2 variveis de entrada, fato este devido sua

definio bsica. O circuito OU Exclusivo tambm conhecido como Exclusive OR

(EXOR), termo derivado do ingls.

2.9 Bloco COINCIDNCIA

A funo que ele executa, como seu prprio nome diz, a de fornecer 1 sada

quando houver uma coincidncia nos valores das variveis de entrada.

Vamos, agora, montar sua tabela da verdade:

A B S

0 0

0 1

1 0

1 1

1

0

0

1

A tabela gera a expresso S = A . B + A.B.

A notao algbrica que representa a funo Coincidncia S = A B, onde se l A

Coincidncia B, sendo S = A . B + A . B. O smbolo do circuito Coincidncia visto

na figura abaixo:

29

Se compararmos as tabelas da verdade dos blocos OU Exclusivo e Coincidncia,

iremos concluir que estes so complementares, ou seja, teremos a sada de um

invertido em relao sada do outro. Assim sendo, podemos escrever:

A B = A B

O bloco Coincidncia tambm denominado de NOU Exclusivo e do ingls

Exclusive NOR.

Da mesma forma que o OU Exclusivo, o bloco Coincidncia definido apenas para 2

variveis de entrada.

2.10 Quadro Resumo

30

BLOCOS LGICOS BSICOS

Porta Smbolo Usual Tabela da

verdade

Funo Lgica Expresso

E

AND

Funo E:

Assume 1 quando

todas as variveis

forem 1 e 0 nos

outros casos.

S= AB

OU

OR

Funo OU:

Assume 0 quando

todas as variveis

forem 0 e 1 nos

outros casos.

S=A+B

A B S

0 0 0

0 1 0

1 0 0

1 1 1

A B S

0 0 0

0 1 1

1 0 1

1 1 1

NO NOT

INVERSOR

Funo NO:

Inverte a varivel

aplicada sua

entrada.

S = A

NE

NAND

Funo NE:

Inverso da funo

E.

S = AB

NOU

NOR

Funo NOU:

Inverso da funo

OU.

S = A + B

OU

EXCLUSIVO

EXCLUSIVE

OR

Funo OU:

Exclusivo

assume 1

quando as

variveis

assumirem

valores

diferentes entre

si

S =A . B + A . B

S = A B

NOU

EXCLUSIVO

EXCLUSIVE

NOR

COINCIDNCIA

Funo

Coincidncia:

Assume 1

quando houver

coincidncia

entre os valores

das variveis

S = A . B + A . B

S = A B

31

A B S

0 0 1

0 1 0

1 0 0

1 1 0

A B S

0 0 1

0 1 1

1 0 1

1 1 0

A S

0 1

1 0

A B S

0 0 0

0 1 1

1 0 1

1 1 0

A B S

0 0 1

0 1 0

1 0 0

1 1 1

3 LGEBRA DE BOOLE E SIMPLIFICAO DE CIRCUITOS

LGICOS

3.1 Introduo

No captulo anterior, trabalhamos com os circuitos lgicos sem nos preocuparmos

com simplificaes. Na prtica, porm, estes circuitos obtidos admitem geralmente

simplificaes.

Para entrarmos no estudo da simplificao dos circuitos lgicos, teremos que fazer

um breve estudo da lgebra de Boole, pois atravs de seus postulados,

propriedades, teoremas fundamentais e identidades que efetuamos as mencionadas

simplificaes, e, alm disso, notamos que na lgebra de Boole que esto todos

os fundamentos da Eletrnica Digital.

3.2 Variveis e Expresses na lgebra de Boole

Como vimos anteriormente, as variveis booleanas so representadas atravs de

letras, podendo assumir apenas dois valores distintos: 0 ou 1. Denominamos

expresso booleana a sentena matemtica composta de termos cujas variveis so

booleanas, da mesma forma, podendo assumir como resultado final 0 ou 1.

3.3 Postulados

A seguir, apresentaremos os postulados da complementao, da adio e da

multiplicao da lgebra de Boole, e suas respectivas identidades resultantes.

32

33

3.4 Simplificao de Expresso Booleanas

Utilizando o conceito da lgebra de Boole, podemos simplificar expresses e

conseqentemente circuitos.

Para efetuarmos estas simplificaes, existem, basicamente, dois processos. O

primeiro deles a simplificao atravs da lgebra de Boole; o segundo a

utilizao dos mapas de Veitch Karnaugh.

Para elucidar, vamos utilizar, por exemplo, a expresso:

S = ABC + AC + AB

Vamos simplific-la, utilizando a lgebra de Boole. Primeiramente, vamos evidenciar

o termo A:

S = A ( BC + C+ B )

Agora, aplicando a propriedade associativa, temos:

S = A BC + (C + B)

Aplicando a identidade X = X, temos:

S = A BC + (C + B)

Aplicando o teorema de De Morgan, temos:

S = BC + ( BC ) A

34

Chamando BC de Y, logo (BC) = Y, temos, ento:

S = A (Y+Y)

Como Y + Y = 1, logo: S = A . 1 = A S = A

Esta expresso mostra a importncia da simplificao e a conseqente minimizao

do circuito, pois os resultados so idnticos aos valores assumidos pela varivel A,

assim sendo, todo o circuito pode ser substitudo por um nico fio ligado varivel A.

Como um outro exemplo, vamos simplificar a expresso:

S = ABC + A BC + AB C

Tirando A . C em evidncia nos dois primeiros termos, temos:

S = A . C . ( B + B) + ABC

Aplicando a identidade: B + B = 1, temos:

35

4 DIAGRAMAS DE VEITCH-KARNAUGH

4.1 Mtodo da Soma de Produtos

A figura abaixo mostra as quatro maneiras possveis de se fazer operao AND de

dois sinais de entrada que esto na forma complementada e no-complementada.

Essas sadas so chamadas produtos fundamentais.

A tabela lista cada produto fundamental ao lado das condies de entrada para a

produo de uma sada alta.

4.2 Equao da Soma de Produtos

Aqui est como obter a soluo de produtos dada uma tabela-verdade:

A B C Y

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0

0

0

1

0

1

1

1

36

A B Produto Fundamental

0 0 AB

0 1 AB

1 0 AB

1 1 AB

Tabela verdade de projeto

O que voc tem a fazer localizar cada sada na tabela-verdade e colocar por

escrito o produto fundamental. Por exemplo, a primeira sada 1 aparece para uma

entrada de A = 0, B = 1 e C = 1. O produto fundamental correspondente ABC. A

prxima sada 1 aparece para A = 1, B = 0 e C = 1. O produto fundamental

correspondente ABC. Continuando dessa forma, voc pode identificar todos os

produtos fundamentais, como mostrado na Tabela:

Para obter a equao da soma de produtos, voc tem de fazer a operao OR dos

produtos fundamentais da Tabela.

Y = ABC + ABC + ABC + ABC

4.3 Circuito Lgico

Aps ter obtido uma equao de soma de produtos, voc pode deduzir o

correspondente circuito lgico desenhando uma rede AND-OR:

37

A B C Y

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 1 ABC

1 0 0 0

1 0 1 1 ABC

1 1 0 1 ABC

1 1 1 1 ABC

Produtos fundamentais

4.4 Tabela-verdade para Mapa de Karnaugh

Um mapa de Karnaugh uma exposio visual dos produtos fundamentais

necessrios para uma soluo de soma de produtos. Por exemplo, aqui est como

converter a Tabela em um mapa de Karnaugh.

Comece desenhando a figura:

38

A B Y

0 0 0

0 1 0

1 0 1

1 1 1

B B

A

A

Observe as variveis e complementos: a coluna vertical tem A seguido por A, e a

linha horizontal tem B seguido por B. agora, procure por sadas iguais a 1 na

Tabela.

Indique esse produto fundamental no mapa da Karnaugh, como mostrado:

O passo final no desenho do mapa de Karnaugh inserir os zeros nos espaos

remanescentes:

4.5 Mapas de Trs Variveis

39

B B

A

A 1 1

B B

A 0 0

A 1 1

A B C Y

0 0 0 0

0 0 1 0

0 1 0 1

0 1 1 0

1 0 0 0

1 0 1 0

1 1 0 1

1 1 1 1

4.6 Mapas de Quatro Variveis

4.7 Pares, Quadras e Octetos.

O mapa contm um par de uns que so adjacentes.

40

C C C C C C

AB AB AB 0 0

AB AB 1 AB 1 0

AB AB 1 1 AB 1 1

AB AB AB 0 0

(a) (b) (c)

4.8 Quadras

Uma quadra um grupo de quatro uns, que so adjacentes horizontalmente ou

verticalmente. Os uns podem estar lado a lado.

4.9 O Octeto

Alm de pares e quadras, h mais um grupo de uns adjacentes para procurar: o

octeto. Este um grupo de oito uns.

4.10 Simplificaes de Karnaugh

41

Como voc sabe, um par elimina uma varivel e seu complemento, uma quadra

elimina duas variveis e seus complementos, e um octeto elimina trs variveis e

seus complementos. Por causa disso, aps desenhar um mapa de Karnaugh,

circunde primeiro os octetos, em segundo as quadras e, por ltimo, os pares. Dessa

forma consegue-se a maior simplificao.

O par representa o produto simplificado A B D, a quadra inferior representa A C e a

quadra da direita representa C D. Fazendo a operao OR desses produtos

simplificados, obtemos a equao booleana correspondente ao mapa de Karnaugh

completo:

Y = A B D + A C + C D

4.11 Sobrepondo Grupos

Voc pode usar o mesmo 1 mais de uma vez.

42

Y = A + BCD

vlido circundar os uns como mostrado na figura, mas o 1 isolado resulta em uma

equao mais complicada:

Por isto sobreponha grupos sempre que for possvel. Isto , use os uns mais de uma

vez para obter os grupos maiores que voc puder.

4.12 Enrolando o Mapa

Outra coisa, a saber, sobre o enrolamento. Olhe para a figura. Os pares resultam

nesta equao:

43

Y = A + ABCD

5 CIRCUITOS COMBINACIONAIS 1 PARTE

5.1 Introduo

Um dos captulos importantes da Eletrnica Digital o que trata dos circuitos

combinacionais. atravs do estudo destes que poderemos compreender o

funcionamento de circuitos, tais como: somadores, subtratores, circuitos que

executam prioridades, codificadores, decodificadores e outros muito utilizados na

construo de computadores e em vrios outros sistemas digitais.

O circuito combinacional aquele em que a sada depende nica e exclusivamente

das combinaes entre as variveis de entrada.

Podemos utilizar um circuito lgico combinacional para solucionar problemas em que

necessitamos de uma resposta, quando acontecerem determinadas situaes,

representadas pelas variveis de entrada. Para construirmos estes circuitos,

necessitamos de suas expresses caractersticas que como vimos no captulo

anterior, so obtidas das tabelas da verdade que representam as situaes j

mencionadas.

A figura ilustra a seqncia do processo, onde, a partir da situao, obtemos a

tabela da verdade e a partir desta, atravs das tcnicas j conhecidas, a expresso

simplificada e o circuito final.

5.2 Projetos de Circuitos Combinacionais

A figura mostra o esquema geral de um circuito combinacional composto pelas

variveis de entrada, o circuito propriamente dito e sua (s) sada (s).

44

SITUAO

TABELA

DA

VERDADE

EXPRESSO

SIMPLIFICADA

CIRCUITO

Notamos que o circuito lgico pode possuir diversas variveis de entrada e uma ou

mais sadas conforme o caso do projeto.

5.3 Circuito com 2 Variveis

A figura representa o cruzamento das ruas A e B. Neste cruzamento, queremos

instalar um sistema automtico para os semforos, com as seguintes caractersticas:

1 - Quando houver carros transitando somente na Rua B, o semforo 2 dever

permanecer verde para que estas viaturas possam trafegar livremente;

2 - Quando houver carros transitando somente na Rua A, o semforo 1 dever

permanecer verde pelo mesmo motivo;

45

3 - Quando houver carros transitando nas Ruas A e B, deveremos abrir o semforo

para a Rua A, pois preferencial.

Primeiramente, vamos estabelecer as seguintes convenes:

a) Existncia de carro na Rua A: A = 1.

b) No existncia de carro na Rua A: A = 0 ou A = 1.

c) Existncia de carro na Rua B: B = 1.

d) No existncia de carro na Rua: B = 0 ou B = 1.

e) Verde do sinal 1 acesso: V

1

= 1.

f) Verde do sinal 2 acesso: V

2

= 1.

g) Quando V

1

= 1 vermelho do semforo 1 apagando: V

m1

= 0,

verde do semforo 2 apagando: V

2

= 0

e vermelho do semforo 2 acesso: V

m2

= 1.

h) Quando V

2

= 1 V

1

= 0, V

m2

= 0 e V

m1

= 1.

5.4 Circuito com 3 Variveis

Deseja-se utilizar um amplificador para ligar trs aparelhos: um toca-fitas, um toca-

discos e um rdio FM. Vamos elaborar um circuito lgico que nos permitir ligar os

aparelhos, obedecendo s seguintes prioridades:

1 prioridade: Toca-discos

2 prioridade: Toca-fitas

3 prioridade: Rdio FM

Isto significa que quando no ligarmos nem o toca-disco, nem o toca-fitas, o rdio

FM, se ligado, ser conectado entrada do amplificador. Se ligarmos o toca-fitas,

automaticamente o circuito irar conect-lo entrada do amplificador, pois possui

prioridade sobre o rdio FM. Se, ento, ligarmos o toca-disco, este ser conectado

ao amplificador, pois representa a 1 prioridade. A partir disto, podemos montar o

diagrama de blocos com as respectivas ligaes:

46

Neste projeto, o circuito lgico receber as informaes das variveis de entrada A,B

e C, representando os aparelhos, e atravs das sadas S

A

, S

B

e S

C

comutaro as

chaves CH1, CH2 e CH3 para fazer a conexo conforme a situao requerida.

Convenes Utilizadas:

= Variveis de entrada (A,B e C): aparelho desligado = 0 e ligado = 1.

= Sadas (S

A

, S

B

e S

C

): S = 0 chave aberta e S = 1 chave fechada.

47

TOCA-DISCOS

A

TOCA-FITAS

B

RDIO FM

C

AMPLIFICADOR

S

A

CH 1 S

B

CH2 S

C

CH3

6 CIRCUITO COMBINACIONAIS - 2 PARTE

6.1 Introduo

No captulo anterior, vimos o processo de circuitos lgicos combinacionais utilizados

na soluo de problemas a partir de situaes prticas de maneira geral. Neste

captulo, estudaremos outros, destinados principalmente a aplicaes especficas,

empregadas, sobretudo na arquitetura interna de circuitos integrados e, ainda, em

sistemas digitais.

Entre os circuitos destinados a estas finalidades destacamos os codificadores,

decodificadores e os circuitos aritmticos (meio somador, somador completo, meio

subtrator e subtrator completo), que sero abordados a nvel bsico como projetos

combinacionais, para melhor entendimento, sendo, entretanto encontrados na

prtica, disponveis em circuitos integrados comerciais ou internos a sistemas mais

complexos, tais como microprocessadores e circuitos integrados dedicados.

6.2 Cdigos

So vrios os cdigos dentro do campo da Eletrnica Digital, existindo situaes em

que a utilizao de um vantajosa em relao a outro. Neste tpico, descrever os

cdigos mais conhecidos.

6.3 Cdigos BCD 8421

Vamos iniciar explicando que no nome deste cdigo, a sigla BCD representa as

inicias de Binary Coded Decimal, que significa uma codificao do sistema decimal

em binrio. Os termos seguintes (8421) significam os valores dos algarismos num

dado nmero binrio, que conforme estudado no captulo 1, representam

respectivamente: 2

3

, 2

2

, 2

1

e 2

0

.

A formao deste cdigo vista na tabela

48

DECIMAL BCD 8421

A B C D

0

1

2

3

4

5

6

7

8

9

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

O nmero de bits de um cdigo o nmero de dgitos binrios que este possui.

Notamos, ento, que o cdigo BCD 8421 um cdigo de 4 bits e, ainda, que

vlido de 0 a 9

10

.

6.4 Codificadores e Decodificadores

Vamos, agora, tratar de circuitos que efetuam a passagens de um determinado

cdigo para outro. Primeiramente, vamos fazer uma anlise do significado das

palavras codificador e decodificador.

Chamamos de codificador o circuito combinacional que torna possvel a passagem

de um cdigo conhecido para um desconhecido. Como exemplo, podemos citar o

circuito inicial de uma calculadora que transforma uma entrada decimal, atravs do

sistema de chaves de um teclado, em sada binria para que o circuito interno

processe e faa a operao.

49

Chamamos de decodificador o circuito que faz o inverso, ou seja, passa um cdigo

desconhecido para um conhecido. No exemplo citado o circuito que recebe o

resultado da operao em binrio e o transforma em sada decimal, na forma

compatvel para um mostrador digital apresentar os algarismos.

6.5 Codificador Decimal/Binrio

Vamos, neste item, elaborar um codificador para transformar um cdigo decimal em

binrio (BCD 8421). A entrada do cdigo decimal vai ser feita atravs de um

conjunto de chaves numeradas de 0 a 9 e a sada por 4 fios, para fornecer um

cdigo binrio de 4 bits, correspondente chave acionada.

A seguir, vamos construir a tabela da verdade do codificador que relaciona cada

chave de entrada decimal com a respectiva sada em binrio:

50

CHAVE A B C D

Ch0

Ch1

Ch2

Ch3

Ch4

Ch5

Ch6

Ch7

Ch8

Ch9

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

O circuito, assim constitudo, visto na figura.

6.6 Decodificador Binrio/Decimal

A estrutura geral deste decodificador vista na figura.

51

Vamos montar a tabela da verdade do circuito no qual as entradas so bits do

cdigo BCD 8421 e as sadas so os respectivos bits do cdigo decimal

98766543210.

BCD 8421 CDIGO 9876543210

A B C D S9 S8 S7 S6 S5 S4 S3 S2 S1 S0

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

0 0 0 0 0 0 0 0 0 1

0 0 0 0 0 0 0 0 1 0

0 0 0 0 0 0 0 1 0 0

0 0 0 0 0 0 1 0 0 0

0 0 0 0 0 1 0 0 0 0

0 0 0 0 1 0 0 0 0 0

0 0 0 1 0 0 0 0 0 0

0 0 1 0 0 0 0 0 0 0

0 1 0 0 0 0 0 0 0 0

1 0 0 0 0 0 0 0 0 0

A partir das expresses simplificadas, obtemos o circuito do decodificador que

visto na figura.

52

6.7 Decodificador para Display de 7 Segmentos

O display de 7 segmentos possibilita escrevermos nmeros decimais de 0 a 9 e

alguns outros smbolos que podem ser letras ou sinais. A figura representa uma

unidade do display genrica, com a nomenclatura de identificao dos segmentos

usual em manuais prticos.

53

Entre as tecnologias de fabricao das unidades de display usaremos o mais comum

que o display a led, que possui cada segmento composto por um led, existindo um

tipo denominado catodo comum e outro anodo comum.

Vamos a ttulo de exemplo, elaborar um decodificador para a partir de um cdigo

binrio (BCD 8421) escrever a seqncia de 0 a 9 em um display de 7 segmentos

catodo comum. O esquema geral deste decodificador visto na figura.

54

Characteres Display BCD 8421 Cdigo para 7

Segmentos

A B C D a b c d e f g

0

0 0 0 0

1 1 1 1 1 1 0

1

0 0 0 1

0 1 1 0 0 0 0

2

0 0 1 0

1 1 0 1 1 0 1

3

0 0 1 1

1 1 1 1 0 0 1

4

0 1 0 0

0 1 1 0 0 1 1

5

0 1 0 1

1 0 1 1 0 1 1

6

0 1 1 0

1 0 1 1 1 1 1

7

0 1 1 1

1 1 1 0 0 0 0

8

1 0 0 0

1 1 1 1 1 1 1

9

1 0 0 1

1 1 1 1 0 1 1

55

6.8 Circuitos Aritmticos

Dentro do conjunto de circuitos combinacionais aplicados para finalidades especfica

nos sistemas digitais, destacam-se os circuitos aritmticos. So utilizados,

principalmente, para construir a ULA (Unidade Lgica Aritmtica) dos

microprocessadores e, ainda, encontrados disponveis em circuitos integrados

comerciais. Neste tpico, abordamos os principais circuitos aritmticos e seus

subsistemas derivados.

6.9 Meio Somador

Antes de iniciarmos o assunto, vamos relembrar alguns tpicos importantes da soma

de 2 nmeros binrios:

0 0 1 11

+ + + +

0 1 0 1

0 1 1 10

Aps essa breve introduo, vamos montar uma tabela da verdade da soma de 2

nmeros binrios de 1 algarismo:

A B S Ts

0 0

0 1

1 0

1 1

0

1

1

0

0

0

0

1

56

Transporte

Ts transporte de sada

(0 + 0 = 0 Ts = 0)

(0 + 1 = 1 Ts = 0)

(1 + 0 = 1 Ts = 0)

(1 + 1 = 0 Ts = 1)

Representando cada nmero por 1 bit, podemos, ento, montar um circuito que

possui como entradas A e B, e como sada, a soma dos algarismos (S) e o

respectivo transporte de sada (Ts). As expresses caractersticas do circuito,

extradas da tabela, so:

S = A B

Ts = AB

O circuito a partir destas expresses visto na figura.

A representao em bloco deste circuito vista na figura.

6.10 Somador Completo

O Meio Somador possibilita efetuar a soma de nmeros binrios com 1 algarismo.

Para se fazer soma de nmeros binrios de mais algarismos, esse circuito torna-se

insuficiente, pois no possibilita a introduo do transporte de entrada proveniente

da coluna anterior. Para melhor compreenso, vamos analisar o caso da soma:

1110

2

+ 110

2

. Assim sendo, temos:

57

A S

MEIO

SOMADOR

B Ts

1 1 1

+ 1 1 1 0

0 1 1 0

1 0 1 0 0

Ts = 1Ts = 1Ts = 1

A coluna 1 tem como resultado um transporte de sada igual a 0. A coluna 2 tem

como resultado 0 e um transporte de sada igual a 1. A coluna 3 tem um transporte

de entrada igual a 1 (Ts da coluna anterior), possui resultado 1 e transporte de sada

igual a 1. A coluna 4 tem transporte de entrada igual a 1, resultado 0 e transporte de

sada 1. A coluna 5 possui apenas um transporte de entrada (Ts da coluna 4) e,

obviamente, seu resultado ser igual a 1.

Para fazermos a soma de 2 nmeros binrios de mais algarismos, basta somarmos

coluna a coluna, levando em conta o transporte de entrada que nada mais do que

o Ts da coluna anterior.

O somador Completo um circuito para efetuar a soma completa de uma coluna,

considerando o transporte de entrada. Vamos, agora, montar a tabela da verdade

deste circuito:

58

A B T

E

S T

S

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0

1

1

0

1

0

0

1

0

0

0

1

0

1

1

1

Vamos, ento, escrever as expresses caractersticas, sem simplificao, de um

Somador Completo:

Transpondo para diagramas de Veitch-Karnaugh, temos:

S = A B T

E

T

S

= BT

E

+ AT

E

+ AB

Vamos, atravs das expresses, esquematizar o circuito Somador Completo:

Da mesma forma, o circuito apresentado em bloco, visto na figura.

59

T

E

transporte de entrada

(0 + 0 + 0 = 0 Ts = 0)

(0 + 0 + 1 = 1 Ts = 0)

(0 + 1 + 0 = 1 Ts = 0)

(0 + 1 + 1 = 0 Ts = 1)

(1 + 0 + 0 = 1 Ts = 0)

(1 + 0 + 1 = 0 Ts = 1)

(1 + 1 + 0 = 0 Ts = 1)

(1 + 1 + 1 = 1 Ts = 1)

Vamos, para exemplo de aplicao, montar um sistema em blocos que efetua soma

de 2 nmeros de 4 bits, conforme o esquema a seguir:

A

3

A

2

A

1

A

0

+ B

3

B

2

B

1

B

0

S

4

S

3

S

2

S

1

S

0

Para efetuar a soma dos bits A

0

e B

0

dos nmeros (1 coluna), vamos utilizar um

Meio Somador, pois no existe transporte de entrada, mas para as outras colunas

utilizaremos Somadores Completos, pois necessitaremos considerar os transportes

provenientes das colunas anteriores. O sistema montado visto na figura.

6.11 Meio Subtrator

Antes de iniciarmos o assunto, vamos relembrar alguns tpicos importantes da

subtrao de nmeros binrios:

60

A S

B

T

E

T

S

SOMADOR

COMPLETO

0 - 0 = 0

0 - 1 = 1

1 - 0 = 1

1 - 1 = 0

Vamos montar a tabela da verdade de uma subtrao de 2 nmeros binrios de 1

algarismo:

A B S T

S

0 0

0 1

1 0

1 1

0

1

1

0

0

1

0

0

Representando cada nmero por 1 bit, podemos montar um circuito com as entradas

A e B, e como sada, a subtrao (S) e o transporte de sada (Ts).

As expresses caractersticas do circuito, extradas da tabela, so:

S = A B

Ts = AB

O circuito a partir destas, visto na figura.

61

e transporta 1 (empresta 1)

(0 0 = 0 Ts = 0)

(0 1 = 1 Ts = 1)

(1 0 = 1 Ts = 0)

(1 1 = 0 Ts = 0)

Em bloco, o circuito recebe a representao da figura.

6.12 Subtrator Completo

O Meio Subtrator possibilita-nos efetuar a subtrao de nmeros binrios de 1

algarismo. Para se fazer uma subtrao com nmeros de mais algarismos, este

circuito torna-se insuficiente, pois no possibilita a entrada do transporte (T

E

),

proveniente da coluna anterior.

Para compreendermos melhor, vamos analisar a subtrao:

1100

2

11

2

. Assim sendo, temos:

1 1 0 0

- 0 0 1 1

1 1

1 0 0 1

Ts = 0Ts = 0Ts = 1Ts = 1

Col. 4 Col. 3 Col. 2 Col. 1

A coluna 1 tem como resultado de sada 1 e apresenta um transporte de sada igual

a 1. a coluna 2 tem um transporte de entrada igual a 1 (Ts da coluna anterior), um

resultado igual a 0 e Ts = 0. A coluna 4 tem: T

E

= 0, resultado igual a 1 e Ts = 0.

62

A S

MEIO

SUBTRATOR

B T

S

Para fazermos a subtrao de nmeros binrios de mais algarismos, basta

subtrairmos coluna a coluna, levando em conta o transporte de entrada, que nada

mais do que o Ts da coluna anterior.

O Subtrator Completo um circuito que efetua a subtrao completa de uma coluna,

ou seja, considera o transporte de entrada proveniente da coluna anterior. Vamos,

agora, montar a tabela da verdade deste circuito:

A B T

E

S Ts

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0

1

1

0

1

0

0

1

0

1

1

1

0

0

0

1

As expresses caractersticas extradas da tabela so:

Vamos simplificar estas expresses:

S = A B T

E

T

S

= AB +AT

E

+ BT

E

O circuito derivado das expresses visto na figura.

63

Em bloco, recebe a representao da figura.

6.13 Somador / Subtrator Completo

Podemos esquematizar um circuito que efetue as duas operaes. Para isso, vamos

introduzir uma outra entrada que permanecendo em nvel 0, faz o circuito efetuar

uma soma completa, e permanecendo em nvel 1, faz efetuar uma subtrao

completa.

Vamos, agora, montar a tabela da verdade do circuito, sendo M a varivel de

controle (M = 0 soma e M = 1 subtrao):

64

A S

B

T

E

T

S

SUBTRATOR

COMPLETO

M A B T

E

S Ts

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1 0 1 1

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

0

1

1

0

1

0

0

1

0

1

1

0

1

0

0

1

0

0

0

1

0

1

1

1

0

1

1

1

0

0

0

1

Vamos, ento, esquematizar o circuito:

A figura mostra a representao deste circuito Somador/Subtrator Completo, em

bloco:

65

Soma

Completa

(M = 0)

Subtrao

Completa

(M = 1)

A

S

B

T

S

T

E

M

SOMADOR/

SUBTRATOR

COMPLETO

7 FLIP-FLOP. REGISTRADORES E CONTADORES

7.1 Introduo

O campo da Eletrnica Digital basicamente dividido em duas reas: lgica

combinacional e lgica seqencial.

Os circuitos combinacionais, como vimos at aqui, apresentam as sadas, nica e

exclusivamente, dependentes das variveis de entrada.

Os circuitos seqenciais tm as sadas dependentes das variveis de entrada e/ou

de seus estados anteriores que permanecem armazenados, sendo, geralmente,

sistemas pulsados, ou seja, operam sob o comando de uma seqncia de pulsos

denominada clock.

Neste captulo, trataremos do estudo dos flip-flops e de circuitos nos quais fazem o

papel de elemento principal.

7.2 Flip-Flops

De forma geral, podemos representar o flip-flop como um bloco onde temos 2

sadas: Q e Q , entradas para as variveis e uma entrada de controle (clock). A

sada Q ser a principal do bloco. A figura ilustra um flip-flop genrico.

ENTRADA 1

Q (sada principal)

ENTRADA CLOCK

ENTRADA 2

66

FLIP-FLOP

Q

Este dispositivo possui basicamente dois estados de sada. Para o flip-flop assumir

um destes estados necessrio que haja uma combinao das variveis e do pulso

de controle (clock). Aps este pulso, o flip-flop permanecer neste estado at a

chegada de um novo pulso de clock e, ento, de acordo com as variveis de

entrada, mudar ou no de estado.

Os dois estados possveis so:

1) Q = 0 Q = 1

2) Q = 1 Q = 0

Vamos, a seguir, analisar alguns circuitos de flip-flops e suas respectivas operaes.

7.3 Flip-Flop RS Bsico

Primeiramente, vamos analisar o flip-flop RS bsico, construdo a partir de portas NE

e inversores, cujo circuito visto na figura.

Notamos que estes elos de realimentao fazem com que as sadas sejam injetadas

juntamente com as variveis de entrada, ficando claro, ento, que os estados que as

sadas iro assumir dependero de ambas.

Para analisarmos o comportamento do circuito, vamos construir a tabela da verdade,

levando em considerao as 2 variveis de entrada (S e R) e a sada Q anterior (Qa)

aplicao das entradas:

67

S R Qa

Qf

Qf

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0

1

0

0

1

1

1

1

1

0

1

1

0

0

1

1

Podemos, ento, resumir a tabela da verdade de um flip-flop RS bsico:

S R Qf

0 0

0 1

1 0

1 1

Qa

0

1

A entrada S denominada Set, pois quando acionada (nvel 1), passa a sada para

1 (estabelece ou fixa 1), e a entrada R denominada Reset, pois quando acionada

(nvel 1), passa a sada para 0 (recompe ou zera o flip-flop). Estes termos so

muito usuais na rea de eletrnica digital, sendo provenientes do idioma ingls.

Este circuito ir mudar de estado apenas no instante em que mudam as variveis de

entrada. Veremos em seguida, como o circuito de um flip-flop RS que tem sua

mudana de estado controlada pela entrada de clock.

7.4 Flip-Flop RS com Entrada Clock

Para que o flip-flop RS bsico seja controlado por uma seqncia de pulsos de

clock, basta trocarmos os 2 inversores por portas NE, e s outras entradas destas

portas, injetarmos o clock. O circuito, com estas modificaes visto na figura.

68

fixa Qf = Qa

fixa Qf em 0

fixa Qf em 1

no permitido

Neste circuito, quando a entrada do clock for igual a 0, o flip-flop ir permanecer no

seu estado, mesmo que variem as entradas S e R. Isso pode ser confirmado pela

anlise do circuito, onde conclumos que para clock = 0, as sadas das portas NE de

entrada sero sempre iguais a 1, independentemente dos valores assumidos por S e

R.

Quando a entrada clock assumir valor 1, o circuito ir comportar-se como um flip-flop

RS bsico, pois as portas NE de entrada funcionaro como os inversores do circuito

anteriormente visto. A tabela resume a operao deste flip-flop em funo da

entrada clock.

CK Qf

0 QA

1 RS bsico

De maneira geral, podemos concluir que o circuito ir funcionar quando a entrada

clock assumir valor 1 e manter travada esta sada quando a entrada clock passar

para 0. O flip-flop pode ser representado pelo bloco visto na figura.

69

S

Q

Q

R

CK

7.5 Flip-Flop JK

O flip-flop JK nada mais que um flip-flop RS realimentado da maneira mostrada na

figura.

A tabela simplificada resultante ser:

J K Qf

0 0 Qa

0 1 0

1 0 1

1

1

Qa

7.6 Flip-Flop JK com Entradas Preset e Clear

O flip-flop JK poder assumir valores Q = 1 ou Q = 0 mediante a utilizao das

entradas Preset (PR) e Clear (CLR).

A tabela resume a atuao das entradas Preset e Clear.

CLR PR Qf

0 0 No permitido

0 1 0

1 0 1

1 1 Funcionamento normal

70

Podemos, para facilitar, utilizar um bloco representativo como o mostrado na figura.

Os circuitos na simbologia do bloco indicam que as entradas Prest e Clear so ativas

em 0, ou seja, funcionam respectivamente com nvel 0 aplicado.

7.7 Flip-Flop JK Mestre-Escravo

O flip-flop JK apresenta uma caracterstica indesejvel. Quando o clock for igual a 1,

teremos o circuito funcionando como sendo um circuito combinacional, pois haver a

passagem das entradas J, K e tambm da realimentao. Nessa situao, se houver

uma mudana nas entradas J e K, o circuito apresentar uma nova sada, podendo

alterar seu estado tantas vezes quantas alterarem os estados das entradas J e K.

Para resolver esse problema, foi criado o flip-flop JK Mestre-Escravo (JK Master-

Slave).

Flip-flop Mestre-Escravo.

71

PR

J Q

K Q

CLR

J Q

K Q

J Q

K Q

CLK

A tabela resume a operao do flip-flop JK Mestre-Escravo:

J K Qf

0 0 Qa

0 1 0

1 0 1

1 1

Qa

Notamos que esta tabela idntica de um flip-flop JK bsico, porm a sada Q ir

assumir valores, conforme a situao das entradas JK, somente aps a passagem

do clock para 0. Assim sendo, o circuito denominado JK Mestre-Escravo sensvel

descida de clock. Para obter um circuito sensvel subida de clock basta

colocarmos um inversor interno entrada clock.

A figura mostra o bloco JK Mestre-Escravo e a simbologia para identificar o circuito

sensvel descida de clock (a) e subida de clock (b).

CK CK

(a) (b)

7.8 Flip-Flop JK Mestre-Escravo com Entrada Preset e Clear

O controle de Preset, quando assumir valor 0, far com que a sada do circuito (Q)

assuma valor 1. O mesmo ocorre com o controle de Clear, fazendo com que a sada

assuma valor 0.

72

J Q

K Q

J Q

K Q

A figura mostra o bloco representativo do flip-flop JK Mestre-Escravo com as

entradas Preset e Clear ativas em 0.

CK

7.9 Flip-Flop Tipo T

Este flip-flop obtido de um JK Mestre-escravo com as entradas J e K curto-

circuitadas (uma ligada outra), logo quando J assumir valor 1, K tambm assumir

valor 1, e quando J assumir valor 0, K tambm assumir valor 0. Obviamente, no

caso desta ligao, no iro ocorrer nunca entradas como: J = 0 e K = 1; J = 1 e K =

0. A figura mostra a ligao e o bloco representativo do flip-flop tipo T obtido.

Eliminando os casos no existentes, obtemos a tabela da verdade do flip-flop do tipo

T:

73

PR

J Q

K Q

CLR

PR

J Q

K Q

CLR

PR

T Q

Q

CLR

T

CK

CK

T Qf

0 Qa

1

Qa

Devido ao fato de o flip-flop tipo T, com a entrada T igual a 1, complementar a sada

(Qa) a cada descida de clock, este ser utilizado como clula principal dos

contadores assncronos que sero estudados adiante. A sigla T vem de Toggle.

(comutado).

7.10 Flip-Flop Tipo D

obtido a partir de um flip-flop JK Mestre-Escravo com a entrada K invertida (por

inversor) em relao a J. Logo, neste flip-flop, teremos as seguintes entradas

possveis: J = 0 e K = 1; J = 1 e K = 0. Obviamente, no iro ocorrer os casos: J = 0

e K = 0; J = 1 e K = 1. A figura mostra como este obtido e seu bloco representativo.

CK

Eliminando os casos no existentes, obtemos a tabela do flip-flop tipo D.

D Qf

0 0

1 1

74

PR

J Q

K Q

CLR

PR

D Q

Q

CLR

D

CK

Pela capacidade de passar para a sada (Qf) e armazenar o dado aplicado na

entrada D, este flip-flop ser empregado como clula de registradores de

deslocamento e em outros sistemas de memria, a serem estudados adiante. A

sigla D vem de Data (dado), termo original em ingls.

7.11 Registradores de Deslocamento

Como vimos, o flip-flop pode armazenar durante o perodo em que sua entrada clock

for igual a 0, um bit apenas (sada Q). Porm, se necessitarmos guardar uma

informao de mais de um bit, o flip-flop ir tornar-se insuficiente. Para isso

utilizamo-nos de um sistema denominado Registrador de Deslocamento (Shift

Register). Trata-se de um certo nmero de flip-flops tipo JK Mestre-Escravo ligado

de tal forma que as sadas de cada bloco sejam aplicadas nas entradas J e K

respectivas do flip-flop tipo D. A figura representa um registrador de Deslocamento.

O funcionamento deste sistema, juntamente com suas aplicaes, ser visto nos

itens subseqente.

7.12 Conversor Srie-Paralelo

O Registrador de Deslocamento pode ser usado para converter uma informao

srie em paralela, ou seja, funcionar como Conversor Srie-Paralelo. A configurao

bsica nessa situao, para uma informao de 4 bits, vista na figura.

75

Como exemplo, vamos aplicar a informao srie = 1010 (

3

2

1

0

) entrada srie

do registrador e analisar as sadas Q

0

, Q

1

, Q

2

e Q

3

, aps os pulsos de clock. Deve-

se ressaltar que estes flip-flops atuam como mestre-escravo e tm sua comutao

no instante da descida do pulso de clock. Assim sendo, temos:

0 1 0 1 Q

3

Q

2

Q

1

Q

0

1

0

1

1

1

2

1

3

1 2 3 4

Para resumir, vamos representar toda a seqncia sob a forma da tabela da

verdade:

Informao

Descidas

de clock

Q

3

Q

2

Q

1

Q

0

0

= 0

1

= 1

2

= 0

3

= 1

1

2

3

4

0

1

0

1

0

0

1

0

0

0

0

1

0

0

0

0

76

INFORMAO

SRIE

CLOCK

REGISTRADOR DE

DESLOCAMENTO

Entrada

Srie

CK

pelo motivo de deslocar a informao a cada pulso de clock que esse dispositivo

denominada Registrador de Deslocamento.

7.13 Conversor Paralelo-Srie

Para entrarmos com uma informao paralela, necessitamos de um registrador que

apresente entradas Prest e Clear, pois atravs destas que fazemos com que o

Registrador armazene a informao paralela. O registrador com estas entradas

visto na figura.

Primeiramente, vamos estudar o funcionamento da entrada ENABLE.

Quando a entrada enable estiver em 0, as entradas preset (PR) dos flip-flops

assumiro, respectivamente, nveis 1, fazendo com que o registrador atue

normalmente.

Quando a entrada enable for igual a 1, as entradas preset dos flip-flops assumiro

os valores complementares das entradas PR

3

, PR

2

, PR

1

e PR

0

, logo, os flip-flops

iro assumir os valores que estiverem, respectivamente, em PR

3

, PR

2

, PR

1

e PR

0

.

Para entendermos melhor, vamos analisar uma clula do registrador.

77

Para zerar (clear) o flip-flop (Q

3

= 0), vamos inicialmente, aplicar nvel 0 entrada

clear.

Com enable = 0, a entrada PR do flip-flop ir assumir nvel 1 e este ir ter um

funcionamento normal como clula do registrador de deslocamento em questo,

mantendo a sada no estado em que se encontra.

Com enable = 1 e PR

3

= 0, a entrada PR do flip-flop assumir nvel 1, logo, a sada

Q

3

manter o seu estado (Q

3

= 0). Com enable = 1 e PR

3

= 1, a entrada PR do flip-

flop assumir nvel 0, forando a sada a assumir nvel 1 (Q

3

= 1).

Aps essa analise, conclumos que, se zerarmos o registrador (aplicando 0

entrada clear), e logo aps introduzirmos a informao paralela (

3

,

2

,

1

e

0

) pelas

entradas PR

3

, PR

2

, PR

1

e PR

0

, as sadas Q

3

, Q

2

, Q

1

e Q

0

assumiro

respectivamente os valores da informao.

Essa maneira de entrarmos com a informao no registrador chamada entrada

paralela de informao, sendo a entrada responsvel pela habilitao da mesma.

Para que o registrador de deslocamento funcione como Conversor Paralelo-Srie,

necessitamos zer-lo e em seguida, introduzir a informao como j descrito,

recolhendo na sada Q

0

a mesma informao de modo srie.

fcil de notar que a sada Q

0

assume primeiramente o valor

0

e a cada descida do

pulso de clock, ir assumir seqencialmente os valores

1

,

2

e

3

.

7.14 Contadores

Contadores so circuitos digitais que variam os seus estados, sob o comando de um

clock, de acordo com uma seqncia predeterminada. So utilizadas principalmente

para contagens diversas, divises de freqncia, medio de freqncia e tempo,

gerao de formas de onda e converso de analgico para digital.

78

Basicamente, estes sistemas, so divididos em duas categorias: Contadores

Assncronos e Sncronos.

Contadores Assncronos

So caracterizados por seus flip-flops funcionarem de maneira assncrona (sem

sincronismo), no tendo entradas clock em comum. Neste tipo de circuito, a entrada

clock se faz apenas no primeiro flip-flop, sendo as outras derivadas das sadas dos

blocos anteriores.

Vamos, a seguir, analisar os principais contadores assncronos:

Contador de Pulsos

A principal caracterstica de um contador de pulsos apresentar nas sadas, o

sistema binrio em seqncia.

Seu circuito bsico apresenta um grupo de 4 flip-flops do tipo T ou JK Mestre-

Escravo, os quais possuem a entrada T ou, no caso, J e K iguais a 1, originando na

sada Qf = Qa, a cada descida de clock.

A entrada dos pulsos se faz atravs da entrada clock do 1 flip-flop, sendo as

entradas clock dos flip-flops seguintes, conectadas s sadas Q dos respectivos

entecessores conforme circuito visto na figura.

79

Considerando Q

0

como bit menos significativo (LSB) e Q

3

Como mais significativo

(MSB), temos nas sadas o sistema binrio em seqncia (0000 a 1111). Notamos

ainda, que aps a 16 descida de clock, o contador ir reiniciar a contagem. A figura

apresenta toda a seqncia obtida graficamente, a partir da variao aplicada

entrada clock do sistema.

Contador de Dcada

O contador de dcada o circuito que efetua a contagem em nmeros binrios de 0

a 9

10

(10 algarismos). Isso significa acompanhar a seqncia do cdigo BCD 8421

de 0000 at 1001.

Para que o contador conte somente de 0 a 9, deve-se jogar um nvel 0 na entrada

clear assim que surgir o caso 10 (1010), ou seja, no 10 pulso. O circuito de um

contador de dcada assncrono visto na figura.

80

Temos, neste caso, a seguinte tabela da verdade:

Descidas de clock Q

3

Q

2

Q

1

Q

0

CLR

1

2

3

4

5

6

7

8

9

10

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1

1

1

1

1

1

1

1

1

1

0

Este contador poder ser utilizado como divisor de freqncia por 10 para uma onda

quadrada aplicada entrada clock, pois possui 10 estados de sada.

Contador Assncrono Crescente/Decrescente

Podemos construir um contador que execute a contagem crescente ou decrescente.

Para isso, utilizamos uma varivel de controle que quando assume 1, faz o circuito

executar contagem crescente e quando assume 0, faz a contagem decrescente.

Este circuito mostrado na figura.

81

Notamos que, no circuito, quando o controle X estiver em 1, s sadasQ

0

, Q

1

eQ

2

estaro bloqueadas, fazendo com que entrem as sadas Q

0

, Q

1

e Q

2

nas entradas

clock dos flip-flops respectivamente. Isto far com que o contador conte

crescentemente.

Quando o controle X estiver em 0, a situao investir-se- e, por conseguinte, o

contador contar decrescentemente.

Notamos, ainda, que Q

0

ser a sada bit menos significativo (LSB).

O contador crescente/decrescente tambm denominado Up/Down Counter, que

o termo designativo em ingls.

Contadores Sncronos

Estes contadores possuem entradas clock curto-circuitadas, ou seja, o clock entra

em todos os flip-flops simultaneamente, fazendo todos atuarem de forma

sincronizada.

Para que haja mudanas de estado, devemos ento estudar o comportamento das

entradas J e K dos vrios flip-flops, para que tenhamos nas sadas, as seqncias

desejadas.

Para estudarmos os contadores sncronos devemos sempre escrever a tabela da

verdade, estudando quais devem ser as entradas J e K dos vrios flip-flops, para

que estes assumam o estado seguinte. Para isso, vamos utilizar a tabela da verdade

do flip-flop JK.

82

J K Qf

0 0 Qa

0 1 0

1 0 1

1 1 Qa

A partir desta tabela, construmos outra relacionando os estados de sada e as

entradas J e K:

Qa Qf J K

0 0 0 X

0 1 1 X

1 0 X 1

1 1 X 0

Vamos, a seguir analisar cada caso:

1) Se o flip-flop estiver em 0 (Qa = 0) e quisermos que o estado a ser

assumido seja 0 (Qf = 0), podemos tanto manter o estado do flip-flop (J =

0, K = 0 = Qf = Qa), como fixar 0 (J = 0, K = 1 = Qf = 0), logo, se J = 0 e

K = X, teremos a passagem de Qa = 0 para Qf = 0.

2) Se o flip-flop estiver em 0 (Qa = 0) e quisermos que o estado a ser

assumido seja 1 (Qf = 1), podemos tanto inverter o estado (J = 1, K =1 =

Qf = Qa), como fixarmos 1 (J = 1, K = 0 = Qf = 1), logo, se J = 1 e K = X,

teremos a passagem de Qa = 0 para Qf = 1.

3) Quando o flip-flop estiver em 1 (Qa = 1) e quisermos que ele v para 0 (Qf

= 0), podemos inverter o estado (J = 1, K = 1 = Qf = Qa) ou fixar 0 (J =

0, K = 1 = Qf = 0), logo, se J = X e K = 1, teremos a passagem de Qa = 1

para Qf = 0.

83

(mantm o estado)

(fixa 0)

(fixa 1)

(inverte o estado)

1)

2)

3)

4)

4) Quando o flip-flop estiver em 1 (Qa = 1) e quisermos que ele permanea

em 1 (Qf = 1), podemos manter o estado (J = 0, K = o = Qf = Qa) ou

fixarmos 1 (J = 1, K = 0 = Qf = 1), logo, se J = X e K = 0, teremos a

passagem de Qa = 1 para Qf = 1.

De posse dos resultados das entradas J e K dos flip-flops para a seqncia

desejada, obtida da tabela, efetuamos as simplificaes e montamos um circuito

combinacional que em funo das sadas dos flip-flops ir atuar nestas entradas

para processar as mudanas de estado.

Genericamente, um contador sncrono possui o esquema visto na figura.

Contador Gerador de uma Seqncia Qualquer

Podemos construir um contador que gere uma seqncia qualquer. Para isso, basta

estabelecermos a seqncia e seguirmos o mtodo j conhecido, ou seja, o da

determinao das entradas J e K. os estados que no fizerem parte da seqncia

devero ser considerados como condies irrelevantes, ou ser encadeados

objetivando atingir o estado inicial.

Para exemplificarmos, vamos construir um contador que gere a seguinte seqncia:

0 = 1 = 2= 3 = 10 = 13 = 0.

84

O loop que o contador deve efetuar para acompanhar a seqncia visto no

diagrama de estados visto na figura.

Notamos que os estados que no pertencem seqncia so: 4, 5, 6, 7, 8, 9, 11,

12, 14 e 15. Vamos fazer, ento, com que o contador, estando no estado 4, aps o

pulso de clock, v para o estado 5, deste para o 6 e assim sucessivamente, at que

o estado 15 v para 0 que inicia a seqncia. Esquematicamente, temos:

7.15 Contadores Utilizados em Circuitos Temporizadores

Os contadores podem ser usados em vrias aplicaes nos sistemas digitais. Nos