Professional Documents

Culture Documents

μP Compatible A/D Converters with 8-Channel: ADC0808/ADC0809 8-Bit Multiplexer

Uploaded by

Kasi ChinnaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

μP Compatible A/D Converters with 8-Channel: ADC0808/ADC0809 8-Bit Multiplexer

Uploaded by

Kasi ChinnaCopyright:

Available Formats

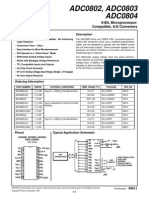

ADC0808/ADC0809 8-Bit P Compatible A/D Converters with 8-Channel Multiplexer

March 2007

ADC0808/ADC0809 8-Bit P Compatible A/D Converters with 8-Channel Multiplexer

General Description

The ADC0808, ADC0809 data acquisition component is a monolithic CMOS device with an 8-bit analog-to-digital converter, 8-channel multiplexer and microprocessor compatible control logic. The 8-bit A/D converter uses successive approximation as the conversion technique. The converter features a high impedance chopper stabilized comparator, a 256R voltage divider with analog switch tree and a successive approximation register. The 8-channel multiplexer can directly access any of 8-single-ended analog signals. The device eliminates the need for external zero and full-scale adjustments. Easy interfacing to microprocessors is provided by the latched and decoded multiplexer address inputs and latched TTL TRI-STATE outputs. The design of the ADC0808, ADC0809 has been optimized by incorporating the most desirable aspects of several A/D conversion techniques. The ADC0808, ADC0809 offers high speed, high accuracy, minimal temperature dependence, excellent long-term accuracy and repeatability, and consumes minimal power. These features make this device ideally suited to applications from process and machine control to consumer and automotive applications. For 16-channel multiplexer with common output (sample/hold port) see ADC0816 data sheet. (See AN-247 for more information.)

Features

Easy interface to all microprocessors Operates ratiometrically or with 5 VDC or analog span

adjusted voltage reference No zero or full-scale adjust required 8-channel multiplexer with address logic 0V to VCC input range Outputs meet TTL voltage level specifications ADC0808 equivalent to MM74C949 ADC0809 equivalent to MM74C949-1

Key Specifications

Resolution Total Unadjusted Error Single Supply Low Power Conversion Time 8 Bits LSB and 1 LSB 5 VDC 15 mW 100 s

Block Diagram

567201

See Ordering Information

2007 National Semiconductor Corporation

5672

www.national.com

ADC0808/ADC0809

Connection Diagrams

Dual-In-Line Package Molded Chip Carrier Package

567211

567212

Order Number ADC0808CCN or ADC0809CCN See NS Package J28A or N28A

Order Number ADC0808CCV or ADC0809CCV See NS Package V28A

Ordering Information

Temperature Range Package Outline Error LSB Unadjusted 1 LSB Unadjusted N28A Molded DIP ADC0808CCN ADC0809CCN 40C to +85C V28A Molded Chip Carrier ADC0808CCV ADC0809CCV V28A Molded Chip Carrier (Tape and Reel) ADC0808CCVX ADC0809CCVX

www.national.com

ADC0808/ADC0809

Absolute Maximum Ratings

(Notes 2, 1) If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications. Supply Voltage (VCC) (Note 3) Voltage at Any Pin 6.5V 0.3V to (VCC +0.3V)

Operating Conditions

(Notes 1, 2) Temperature Range Range of VCC 40CTA+85C 4.5 VDC to 6.0 VDC TMINTATMAX

Except Control Inputs Voltage at Control Inputs 0.3V to +15V (START, OE, CLOCK, ALE, ADD A, ADD B, ADD C) Storage Temperature Range 65C to +150C Package Dissipation at TA=25C 875 mW Lead Temp. (Soldering, 10 seconds) Dual-In-Line Package (plastic) 260C Molded Chip Carrier Package Vapor Phase (60 seconds) 215C Infrared (15 seconds) 220C ESD Susceptibility (Note 8) 400V

Electrical Characteristics Converter Specifications

Converter Specifications: VCC=5 VDC=VREF+, VREF()=GND, TMINTATMAX and fCLK=640 kHz unless otherwise stated. Symbol Parameter ADC0808 Total Unadjusted Error (Note 5) ADC0809 Total Unadjusted Error (Note 5) Input Resistance Analog Input Voltage Range VREF(+) Voltage, Top of Ladder Voltage, Center of Ladder VREF() IIN Voltage, Bottom of Ladder Comparator Input Current Measured at Ref() fc=640 kHz, (Note 6) 25C TMIN to TMAX 0C to 70C TMIN to TMAX From Ref(+) to Ref() (Note 4) V(+) or V() Measured at Ref(+) (VCC/2) 0.1 0.1 2 1.0 GND 0.1 VCC VCC/2 0 0.5 2 2.5 VCC + 0.1 VCC + 0.1 (VCC/2) + 0.1 Conditions Min Typ Max 1 1 Units LSB LSB LSB LSB k VDC V V V A

Electrical Characteristics Digital Levels and DC Specifications

Digital Levels and DC Specifications: ADC0808CCN, ADC0808CCV, ADC0809CCN and ADC0809CCV, 4.75VCC5.25V, 40CTA+85C unless otherwise noted Symbol ANALOG MULTIPLEXER VCC=5V, VIN=5V, IOFF(+) OFF Channel Leakage Current TA=25C TMIN to TMAX VCC=5V, VIN=0, IOFF() OFF Channel Leakage Current TA=25C TMIN to TMAX CONTROL INPUTS VIN(1) VIN(0) Logical 1 Input Voltage Logical 0 Input Voltage (VCC 1.5) 1.5 V V 200 1.0 10 nA A 10 200 1.0 nA A Parameter Conditions Min Typ Max Units

www.national.com

ADC0808/ADC0809

Symbol IIN(1) IIN(0) ICC

Parameter

Conditions

Min

Typ

Max 1.0

Units A A

Logical 1 Input Current (The Control VIN=15V Inputs) Logical 0 Input Current (The Control VIN=0 Inputs) Supply Current fCLK=640 kHz VCC = 4.75V IOUT = 360A IOUT = 10A IO=1.6 mA IO=1.2 mA VO=5V VO=0 3 1.0 0.3

3.0

mA

DATA OUTPUTS AND EOC (INTERRUPT) VOUT(1) VOUT(0) VOUT(0) IOUT Logical 1 Output Voltage Logical 0 Output Voltage Logical 0 Output Voltage EOC TRI-STATE Output Current 2.4 4.5 0.45 0.45 3 V V V V A A

Electrical Characteristics Timing Specifications

Timing Specifications VCC=VREF(+)=5V, VREF()=GND, tr=tf=20 ns and TA=25C unless otherwise noted. Symbol tWS tWALE ts tH tD tH1, tH0 t1H, t0H tc fc tEOC CIN COUT Parameter Minimum Start Pulse Width Minimum ALE Pulse Width Minimum Address Set-Up Time Minimum Address Hold Time (Figure 5) (Figure 5) (Figure 5) (Figure 5) CL=50 pF, RL=10k (Figure 8) CL=10 pF, RL=10k (Figure 8) fc=640 kHz, (Figure 5) (Note 7) 90 10 (Figure 5) At Control Inputs At TRI-STATE Outputs 0 10 10 Conditions MIn Typ 100 100 25 25 1 125 125 100 640 Max 200 200 50 50 2.5 250 250 116 1280 8 + 2 S 15 15 Units ns ns ns ns s ns ns s kHz Clock Periods pF pF

Analog MUX Delay Time From ALE RS=0 (Figure 5) OE Control to Q Logic State OE Control to Hi-Z Conversion Time Clock Frequency EOC Delay Time Input Capacitance TRI-STATE Output Capacitance

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its specified operating conditions. Note 2: All voltages are measured with respect to GND, unless otherwise specified. Note 3: A Zener diode exists, internally, from VCC to GND and has a typical breakdown voltage of 7 VDC. Note 4: Two on-chip diodes are tied to each analog input which will forward conduct for analog input voltages one diode drop below ground or one diode drop greater than the VCCn supply. The spec allows 100 mV forward bias of either diode. This means that as long as the analog VIN does not exceed the supply voltage by more than 100 mV, the output code will be correct. To achieve an absolute 0VDC to 5VDC input voltage range will therefore require a minimum supply voltage of 4.900 VDC over temperature variations, initial tolerance and loading. Note 5: Total unadjusted error includes offset, full-scale, linearity, and multiplexer errors. See Figure 3. None of these A/Ds requires a zero or full-scale adjust. However, if an all zero code is desired for an analog input other than 0.0V, or if a narrow full-scale span exists (for example: 0.5V to 4.5V full-scale) the reference voltages can be adjusted to achieve this. See Figure 13. Note 6: Comparator input current is a bias current into or out of the chopper stabilized comparator. The bias current varies directly with clock frequency and has little temperature dependence (Figure 6). See paragraph 4.0. Note 7: The outputs of the data register are updated one clock cycle before the rising edge of EOC. Note 8: Human body model, 100 pF discharged through a 1.5 k resistor.

www.national.com

ADC0808/ADC0809

Functional Description

MULTIPLEXER The device contains an 8-channel single-ended analog signal multiplexer. A particular input channel is selected by using the address decoder. Table 1 shows the input states for the address lines to select any channel. The address is latched into the decoder on the low-to-high transition of the address latch enable signal. TABLE 1. Analog Channel Selection SELECTED ANALOG CHANNEL IN0 IN1 IN2 IN3 IN4 IN5 IN6 IN7 ADDRESS LINE C L L L L H H H H B L L H H L L H H A L H L H L H L H

CONVERTER CHARACTERISTICS The Converter The heart of this single chip data acquisition system is its 8bit analog-to-digital converter. The converter is designed to give fast, accurate, and repeatable conversions over a wide range of temperatures. The converter is partitioned into 3 major sections: the 256R ladder network, the successive approximation register, and the comparator. The converter's digital outputs are positive true. The 256R ladder network approach (Figure 1) was chosen over the conventional R/2R ladder because of its inherent monotonicity, which guarantees no missing digital codes. Monotonicity is particularly important in closed loop feedback control systems. A non-monotonic relationship can cause oscillations that will be catastrophic for the system. Additionally, the 256R network does not cause load variations on the reference voltage.

The bottom resistor and the top resistor of the ladder network in Figure 1 are not the same value as the remainder of the network. The difference in these resistors causes the output characteristic to be symmetrical with the zero and full-scale points of the transfer curve. The first output transition occurs when the analog signal has reached + LSB and succeeding output transitions occur every 1 LSB later up to full-scale. The successive approximation register (SAR) performs 8 iterations to approximate the input voltage. For any SAR type converter, n-iterations are required for an n-bit converter. Figure 2 shows a typical example of a 3-bit converter. In the ADC0808, ADC0809, the approximation technique is extended to 8 bits using the 256R network. The A/D converter's successive approximation register (SAR) is reset on the positive edge of the start conversion start pulse. The conversion is begun on the falling edge of the start conversion pulse. A conversion in process will be interrupted by receipt of a new start conversion pulse. Continuous conversion may be accomplished by tying the end-of-conversion (EOC) output to the SC input. If used in this mode, an external start conversion pulse should be applied after power up. Endof-conversion will go low between 0 and 8 clock pulses after the rising edge of start conversion. The most important section of the A/D converter is the comparator. It is this section which is responsible for the ultimate accuracy of the entire converter. It is also the comparator drift which has the greatest influence on the repeatability of the device. A chopper-stabilized comparator provides the most effective method of satisfying all the converter requirements. The chopper-stabilized comparator converts the DC input signal into an AC signal. This signal is then fed through a high gain AC amplifier and has the DC level restored. This technique limits the drift component of the amplifier since the drift is a DC component which is not passed by the AC amplifier. This makes the entire A/D converter extremely insensitive to temperature, long term drift and input offset errors. Figure 4 shows a typical error curve for the ADC0808 as measured using the procedures outlined in AN-179.

www.national.com

ADC0808/ADC0809

567202

FIGURE 1. Resistor Ladder and Switch Tree

567213 567214

FIGURE 2. 3-Bit A/D Transfer Curve

FIGURE 3. 3-Bit A/D Absolute Accuracy Curve

567215

FIGURE 4. Typical Error Curve

www.national.com

ADC0808/ADC0809

Timing Diagram

567204

FIGURE 5.

www.national.com

ADC0808/ADC0809

Typical Performance Characteristics

567216

FIGURE 6. Comparator IIN vs. VIN (VCC=VREF=5V)

567217

FIGURE 7. Multiplexer RON vs. VIN (VCC=VREF=5V)

www.national.com

ADC0808/ADC0809

TRI-STATE Test Circuits and Timing Diagrams

t1H, tH1 t0H, tH0

567218

567221

t1H, CL = 10 pF

t0H, CL = 10 pF

567219

567222

tH1, CL = 50 pF

tH0, CL = 50 pF

567220

567223

FIGURE 8.

Applications Information

OPERATION 1.0 RATIOMETRIC CONVERSION The ADC0808, ADC0809 is designed as a complete Data Acquisition System (DAS) for ratiometric conversion systems. In ratiometric systems, the physical variable being measured is expressed as a percentage of full-scale which is not necessarily related to an absolute standard. The voltage input to the ADC0808 is expressed by the equation

the transducers can be connected directly across the supply and their outputs connected directly into the multiplexer inputs, (Figure 9). Ratiometric transducers such as potentiometers, strain gauges, thermistor bridges, pressure transducers, etc., are suitable for measuring proportional relationships; however, many types of measurements must be referred to an absolute standard such as voltage or current. This means a system reference must be used which relates the full-scale voltage to the standard volt. For example, if VCC=VREF=5.12V, then the full-scale range is divided into 256 standard steps. The smallest standard step is 1 LSB which is then 20 mV. 2.0 RESISTOR LADDER LIMITATIONS The voltages from the resistor ladder are compared to the selected into 8 times in a conversion. These voltages are coupled to the comparator via an analog switch tree which is referenced to the supply. The voltages at the top, center and bottom of the ladder must be controlled to maintain proper operation. The top of the ladder, Ref(+), should not be more positive than the supply, and the bottom of the ladder, Ref(), should not be more negative than ground. The center of the ladder voltage must also be near the center of the supply because the analog switch tree changes from N-channel switches to Pchannel switches. These limitations are automatically satisfied in ratiometric systems and can be easily met in ground referenced systems.

(1) VIN= Input voltage into the ADC0808 Vfs= Full-scale voltage VZ= Zero voltage DX= Data point being measured DMAX= Maximum data limit DMIN= Minimum data limit A good example of a ratiometric transducer is a potentiometer used as a position sensor. The position of the wiper is directly proportional to the output voltage which is a ratio of the fullscale voltage across it. Since the data is represented as a proportion of full-scale, reference requirements are greatly reduced, eliminating a large source of error and cost for many applications. A major advantage of the ADC0808, ADC0809 is that the input voltage range is equal to the supply range so

9

www.national.com

ADC0808/ADC0809

Figure 10 shows a ground referenced system with a separate supply and reference. In this system, the supply must be trimmed to match the reference voltage. For instance, if a

5.12V is used, the supply should be adjusted to the same voltage within 0.1V.

567207

FIGURE 9. Ratiometric Conversion System The ADC0808 needs less than a milliamp of supply current so developing the supply from the reference is readily accomplished. In Figure 11 a ground referenced system is shown which generates the supply from the reference. The buffer shown can be an op amp of sufficient drive to supply the milliamp of supply current and the desired bus drive, or if a capacitive bus is driven by the outputs a large capacitor will supply the transient supply current as seen in Figure 12. The LM301 is overcompensated to insure stability when loaded by the 10 F output capacitor. The top and bottom ladder voltages cannot exceed VCC and ground, respectively, but they can be symmetrically less than VCC and greater than ground. The center of the ladder voltage should always be near the center of the supply. The sensitivity of the converter can be increased, (i.e., size of the LSB steps decreased) by using a symmetrical reference system. In Figure 13, a 2.5V reference is symmetrically centered about VCC/2 since the same current flows in identical resistors. This system with a 2.5V reference allows the LSB bit to be half the size of a 5V reference system.

567224

FIGURE 10. Ground Referenced Conversion System Using Trimmed Supply

www.national.com

10

ADC0808/ADC0809

567225

FIGURE 11. Ground Referenced Conversion System with Reference Generating VCC Supply

567226

FIGURE 12. Typical Reference and Supply Circuit

11

www.national.com

ADC0808/ADC0809

567227

RA=RB *Ratiometric transducers FIGURE 13. Symmetrically Centered Reference 3.0 CONVERTER EQUATIONS The transition between adjacent codes N and N+1 is given by: VREF(+)512) 4.0 ANALOG COMPARATOR INPUTS The dynamic comparator input current is caused by the periodic switching of on-chip stray capacitances. These are connected alternately to the output of the resistor ladder/switch tree network and to the comparator input as part of the operation of the chopper stabilized comparator. The average value of the comparator input current varies directly with clock frequency and with VIN as shown in Figure 6. If no filter capacitors are used at the analog inputs and the signal source impedances are low, the comparator input current should not introduce converter errors, as the transient created by the capacitance discharge will die out before the comparator output is strobed. If input filter capacitors are desired for noise reduction and signal conditioning they will tend to average out the dynamic comparator input current. It will then take on the characteristics of a DC bias current whose effect can be predicted conventionally.

(2) The center of an output code N is given by:

(3) The output code N for an arbitrary input are the integers within the range:

(4) Where: VIN=Voltage at comparator input VREF(+)=Voltage at Ref(+) VREF()=Voltage at Ref() VTUE=Total unadjusted error voltage (typically

www.national.com

12

ADC0808/ADC0809

Typical Application

567210

*Address latches needed for 8085 and SC/MP interfacing the ADC0808 to a microprocessor

TABLE 2. Microprocessor Interface Table PROCESSOR 8080 8085 Z-80 SC/MP 6800 READ MEMR RD RD NRDS VMA2R/W WRITE MEMW WR WR NWDS VMAR/W INTERRUPT (COMMENT) INTR (Thru RST Circuit) INTR (Thru RST Circuit) INT (Thru RST Circuit, Mode 0) SA (Thru Sense A) IRQA or IRQB (Thru PIA)

13

www.national.com

ADC0808/ADC0809

Physical Dimensions inches (millimeters) unless otherwise noted

Molded Dual-In-Line Package (N) Order Number ADC0808CCN or ADC0809CCN NS Package Number N28B

Molded Chip Carrier (V) Order Number ADC0808CCV or ADC0809CCV NS Package Number V28A

www.national.com 14

ADC0808/ADC0809

15

www.national.com

ADC0808/ADC0809 8-Bit P Compatible A/D Converters with 8-Channel Multiplexer

Notes

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION (NATIONAL) PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONALS PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS. EXCEPT AS PROVIDED IN NATIONALS TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. LIFE SUPPORT POLICY NATIONALS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein: Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness. National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright 2007 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530-85-86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +49 (0) 870 24 0 2171 Franais Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560

www.national.com

You might also like

- μP Compatible A/D Converters with 8-Channel: ADC0808/ADC0809 8-Bit MultiplexerDocument16 pagesμP Compatible A/D Converters with 8-Channel: ADC0808/ADC0809 8-Bit MultiplexerKudo ShinichiNo ratings yet

- Adc 0808Document14 pagesAdc 0808Vikas PatelNo ratings yet

- ADC0809CCNDocument16 pagesADC0809CCNFrancesca Castelar BenalcazarNo ratings yet

- Adc 0809Document12 pagesAdc 0809Carbon Nano TubeNo ratings yet

- ADC0808Document15 pagesADC0808Ketan SalviNo ratings yet

- Adc 0804Document41 pagesAdc 0804AndySilvandNo ratings yet

- Distributed byDocument42 pagesDistributed bydennyjoelNo ratings yet

- ADC0844/ADC0848 8-Bit P Compatible A/D Converters With Multiplexer OptionsDocument20 pagesADC0844/ADC0848 8-Bit P Compatible A/D Converters With Multiplexer Optionsrazali1982No ratings yet

- ADC0801, ADC0802, ADC0803, ADC0804, ADC0805: ADC0801/ADC0802/ADC0803/ADC0804/ADC0805 8-Bit P Compatible A/D ConvertersDocument43 pagesADC0801, ADC0802, ADC0803, ADC0804, ADC0805: ADC0801/ADC0802/ADC0803/ADC0804/ADC0805 8-Bit P Compatible A/D ConvertersPiyush JainNo ratings yet

- Adc0801 PDFDocument36 pagesAdc0801 PDFroi_sihombingNo ratings yet

- 0804Document41 pages0804Mehanathan Maggie MikeyNo ratings yet

- Adc 0804 PDFDocument18 pagesAdc 0804 PDFCinthya VillenaNo ratings yet

- ADC0804 DatasheetDocument48 pagesADC0804 DatasheetSaurabh AnmadwarNo ratings yet

- Adc0803, Adc0804Document24 pagesAdc0803, Adc0804j.wNo ratings yet

- DAC08Document20 pagesDAC08Severiano Jaramillo QuintanarNo ratings yet

- ADC0800 8-Bit Analog-to-Digital Converter Technical DocumentDocument10 pagesADC0800 8-Bit Analog-to-Digital Converter Technical Documentskiziltoprak100% (1)

- 8051 SchematicDocument37 pages8051 SchematicShabeeb Ali OruvangaraNo ratings yet

- AutoRanging DMMDocument8 pagesAutoRanging DMMPankaj VermaNo ratings yet

- Adc0804 PDFDocument16 pagesAdc0804 PDFbudicw0% (1)

- ADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesDocument17 pagesADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesJorge Luis Castillo GuarachiNo ratings yet

- ADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesDocument18 pagesADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesMarco MenezesNo ratings yet

- DAC0800/DAC0802 8-Bit Digital-to-Analog Converters: General DescriptionDocument11 pagesDAC0800/DAC0802 8-Bit Digital-to-Analog Converters: General DescriptionFernando FortunaNo ratings yet

- ADC0802, ADC0803 ADC0804: Features DescriptionDocument17 pagesADC0802, ADC0803 ADC0804: Features DescriptionSuryananda PadmadinataNo ratings yet

- DAC0830/DAC0832 8-Bit P Compatible, Double-Buffered D To A ConvertersDocument24 pagesDAC0830/DAC0832 8-Bit P Compatible, Double-Buffered D To A Convertersbhuvi2312No ratings yet

- Dac0800 PDFDocument9 pagesDac0800 PDFCarbon Nano TubeNo ratings yet

- 10-Bit and 12-Bit Binary Multiplying DACs from National SemiconductorDocument14 pages10-Bit and 12-Bit Binary Multiplying DACs from National SemiconductormicochangoNo ratings yet

- Dac 0800Document16 pagesDac 0800Ali A-cNo ratings yet

- ADC0808M: Total Unadjusted Error - . - 0.75 LSB Max Resolution of 8 Bits 100-s Conversion TimeDocument8 pagesADC0808M: Total Unadjusted Error - . - 0.75 LSB Max Resolution of 8 Bits 100-s Conversion TimeSushant MishraNo ratings yet

- ADC08831/ADC08832 8-Bit Serial I/O CMOS A/D Converters With Multiplexer and Sample/Hold FunctionDocument24 pagesADC08831/ADC08832 8-Bit Serial I/O CMOS A/D Converters With Multiplexer and Sample/Hold Functionrudra_1No ratings yet

- LTC 1661Document14 pagesLTC 1661mneagu123No ratings yet

- ADC0831/ADC0832/ADC0834 and ADC0838 8-Bit Serial I/O A/D Converters With Multiplexer OptionsDocument33 pagesADC0831/ADC0832/ADC0834 and ADC0838 8-Bit Serial I/O A/D Converters With Multiplexer OptionsRoy Muy GolfoNo ratings yet

- DAC800Document14 pagesDAC800JaimeAugustoPrietoNo ratings yet

- ANALOG TO DIGITAL AND DIGITAL TO ANALOG INTERFACINGDocument28 pagesANALOG TO DIGITAL AND DIGITAL TO ANALOG INTERFACINGsatyanarayana12No ratings yet

- DAC0808 8-Bit D/A Converter: Literature Number: SNAS539ADocument15 pagesDAC0808 8-Bit D/A Converter: Literature Number: SNAS539AYasser Mauricio Flores RamonNo ratings yet

- DS1307 64 X 8, Serial, I C Real-Time Clock: General Description FeaturesDocument14 pagesDS1307 64 X 8, Serial, I C Real-Time Clock: General Description FeaturesAn TrìnhNo ratings yet

- ADC0831/ADC0832/ADC0834/ADC0838 8-Bit Serial I/O A/D Converters With Multiplexer OptionsDocument41 pagesADC0831/ADC0832/ADC0834/ADC0838 8-Bit Serial I/O A/D Converters With Multiplexer OptionsSathiya KumarNo ratings yet

- ADC0808/ADC0809 8-Bit P Compatible A/D Converters With 8-Channel MultiplexerDocument14 pagesADC0808/ADC0809 8-Bit P Compatible A/D Converters With 8-Channel MultiplexerYenny RozaNo ratings yet

- Complete 8-Bit A-to-D Converter AD570 : Ms 8C To +708C: AD570J 8C To +1258C: AD570SDocument8 pagesComplete 8-Bit A-to-D Converter AD570 : Ms 8C To +708C: AD570J 8C To +1258C: AD570SFida PyrtuhNo ratings yet

- Features Description: 12-Bit, Multiplying D/A ConverterDocument9 pagesFeatures Description: 12-Bit, Multiplying D/A Convertershobhitmittal7No ratings yet

- DAC0808 8-Bit D/A Converter: Literature Number: SNAS539ADocument14 pagesDAC0808 8-Bit D/A Converter: Literature Number: SNAS539AomNo ratings yet

- LC MOS Octal 8-Bit DAC AD7228A: Functional Block DiagramDocument9 pagesLC MOS Octal 8-Bit DAC AD7228A: Functional Block DiagramnandobnuNo ratings yet

- Lm75 Sensor TemperatureDocument18 pagesLm75 Sensor TemperatureJeziel Vazquez NavaNo ratings yet

- MCP3040 DatasheetDocument40 pagesMCP3040 Datasheetjiajun898No ratings yet

- AA AA AA AA A A A A A A A: 12-Bit 100 KSPS A/D Converter AD1674Document13 pagesAA AA AA AA A A A A A A A: 12-Bit 100 KSPS A/D Converter AD1674Iancu CiocioiNo ratings yet

- 74 Ls 390Document6 pages74 Ls 390Yoga AdiNo ratings yet

- EELab2 Exp8 AD ConverterDocument4 pagesEELab2 Exp8 AD ConverterAhmed Abdel AzizNo ratings yet

- Ad 421Document14 pagesAd 421Vishal Devrao JadhavNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- Analog Circuit Design Volume Three: Design Note CollectionFrom EverandAnalog Circuit Design Volume Three: Design Note CollectionRating: 3 out of 5 stars3/5 (2)

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Digital Power Electronics and ApplicationsFrom EverandDigital Power Electronics and ApplicationsRating: 3.5 out of 5 stars3.5/5 (3)

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsFrom EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsNo ratings yet

- Quine-McCluskey Tabular MinimizationDocument17 pagesQuine-McCluskey Tabular MinimizationMohammedali_Kh_1552No ratings yet

- Chapter 4: Programmable Logic DevicesDocument63 pagesChapter 4: Programmable Logic DevicesKasi ChinnaNo ratings yet

- Chapter 4: Programmable Logic DevicesDocument63 pagesChapter 4: Programmable Logic DevicesKasi ChinnaNo ratings yet

- Fatgen 103Document34 pagesFatgen 103Kasi ChinnaNo ratings yet

- Examining The Fat File SystemDocument22 pagesExamining The Fat File SystemKasi ChinnaNo ratings yet

- Frank Vahid PDFDocument11 pagesFrank Vahid PDFKasi ChinnaNo ratings yet

- Hydraulics LectureDocument20 pagesHydraulics Lecturee_manpreetNo ratings yet

- Flash Me M GuideDocument13 pagesFlash Me M GuideTerence LeungNo ratings yet

- ASP.Net.docxDocument74 pagesASP.Net.docxKasi ChinnaNo ratings yet

- Digital StorageDocument3 pagesDigital StoragegadunNo ratings yet

- B 01Document27 pagesB 01Kasi ChinnaNo ratings yet

- Flash FileDocument39 pagesFlash Fileletanbaospkt06No ratings yet

- UR24A Multi-Channel UART Wireless ModuleDocument6 pagesUR24A Multi-Channel UART Wireless ModuleKasi ChinnaNo ratings yet

- Max3070e Max3079e PDFDocument24 pagesMax3070e Max3079e PDFKasi ChinnaNo ratings yet

- Spraa 33Document12 pagesSpraa 33Ayesha KamalNo ratings yet

- 312 PPTDocument37 pages312 PPTHcv Prasad KacharlaNo ratings yet

- Selection of Candidates For Lynux BELDocument1 pageSelection of Candidates For Lynux BELKasi ChinnaNo ratings yet

- 200 Motivational Quotes An Inspirational ReferenceDocument42 pages200 Motivational Quotes An Inspirational ReferencevinaykumarjainNo ratings yet

- K.H.V.Sreenivasa Varma (06-469) K.Srimala (06-470) B.Sindhu (06-471) A.Sreenivas (06-472) Presented byDocument16 pagesK.H.V.Sreenivasa Varma (06-469) K.Srimala (06-470) B.Sindhu (06-471) A.Sreenivas (06-472) Presented byKrishna Gowri DasariNo ratings yet

- LM35 Temperature SensorDocument13 pagesLM35 Temperature Sensorapi-3799604100% (1)

- Wireless Transformer MonitoringDocument18 pagesWireless Transformer MonitoringKamlesh MotghareNo ratings yet

- At 89 C 52Document24 pagesAt 89 C 52Rohit MehtaNo ratings yet

- Transformer Fault Detection Using Zigbee and GSMDocument46 pagesTransformer Fault Detection Using Zigbee and GSMIrfan Baig100% (1)

- Automatic Railwa Gate ControlDocument57 pagesAutomatic Railwa Gate ControlmgitecetechNo ratings yet

- Fantasyelectronics - Automatic Railway Gate Control System Using AVR ATmega8 With Complete Project Report, Code and Circuit DiagramDocument7 pagesFantasyelectronics - Automatic Railway Gate Control System Using AVR ATmega8 With Complete Project Report, Code and Circuit DiagramKasi ChinnaNo ratings yet

- 312 DocDocument87 pages312 DocHcv Prasad KacharlaNo ratings yet

- Intelligent Railway Level Crossing SystemDocument2 pagesIntelligent Railway Level Crossing SystemKasi ChinnaNo ratings yet

- XBEE Based Remote Monitoring of 3 Parameters On Transformer / Generator HealthDocument2 pagesXBEE Based Remote Monitoring of 3 Parameters On Transformer / Generator HealthKasi ChinnaNo ratings yet

- Learn. Explore. Excel.: 20135127 Hall Ticket For MS in VLSI Engg. Entrance Test - 2013' Hall Ticket No MS13 - 1095Document2 pagesLearn. Explore. Excel.: 20135127 Hall Ticket For MS in VLSI Engg. Entrance Test - 2013' Hall Ticket No MS13 - 1095Kasi ChinnaNo ratings yet

- VLSIGURU DFT SCAN INSERTION LABDocument5 pagesVLSIGURU DFT SCAN INSERTION LABsenthilkumarNo ratings yet

- PS Basics of A DC DriveDocument37 pagesPS Basics of A DC Drivesopan saNo ratings yet

- Data Representation and Memory StorageDocument28 pagesData Representation and Memory StoragesubaNo ratings yet

- Commsim UserGuideDocument580 pagesCommsim UserGuideSanjay SinhaNo ratings yet

- Traffic Light Controller Using VHDLDocument6 pagesTraffic Light Controller Using VHDLAbdoulrazakNo ratings yet

- Opamp PDFDocument15 pagesOpamp PDFBhumika PoriyaNo ratings yet

- Phys201 RQ Ch31Document45 pagesPhys201 RQ Ch31Daniel Zahn100% (1)

- Skyline PDFDocument4 pagesSkyline PDFJoão Felipe da FragaNo ratings yet

- Thermal Simulation Techniques For Nano Transistors: Ken GoodsonDocument41 pagesThermal Simulation Techniques For Nano Transistors: Ken GoodsonSwapnil BhuratNo ratings yet

- ICT - PPTX (Repaired)Document290 pagesICT - PPTX (Repaired)Samuel Benson SesayNo ratings yet

- 1 Heat in Integrated Circuits and Systems 1: Acknowledgments XDocument3 pages1 Heat in Integrated Circuits and Systems 1: Acknowledgments XRamachandra ReddyNo ratings yet

- BLDC Motor Controller: V - SupplyDocument7 pagesBLDC Motor Controller: V - SupplyFatihNo ratings yet

- Katalog Bezbednosni Resenija Aleks SistemiDocument4 pagesKatalog Bezbednosni Resenija Aleks SistemiKirilNo ratings yet

- CST Application Note Ultra Wideband High Power Microwave Traveling Wave AntennaDocument8 pagesCST Application Note Ultra Wideband High Power Microwave Traveling Wave AntennaSumindak GultomNo ratings yet

- LG and MSI Are Taking On Samsung's Odyssey G9 With Giant Curved OLED Gaming MonitorsDocument5 pagesLG and MSI Are Taking On Samsung's Odyssey G9 With Giant Curved OLED Gaming Monitorsremo meinNo ratings yet

- Diodes Spice ModelsDocument1,063 pagesDiodes Spice ModelsAnonymous zyF9pyxtBNo ratings yet

- Information Sheet Lsim SeriesDocument4 pagesInformation Sheet Lsim SeriesjimmymacbootNo ratings yet

- Sirio SY 27-4 PDFDocument4 pagesSirio SY 27-4 PDFAriel BecerraNo ratings yet

- Lakshya User ManualDocument27 pagesLakshya User ManualPrajakta WahurwaghNo ratings yet

- Wiring DiagramDocument12 pagesWiring DiagramÁlvaro TorrellasNo ratings yet

- Combox Installation Instruction For Exx Series BMW PDFDocument14 pagesCombox Installation Instruction For Exx Series BMW PDFsucrooNo ratings yet

- PrimeTrex One DescriptionDocument2 pagesPrimeTrex One DescriptionCarlos AparicioNo ratings yet

- TK-2402 (V) /2402 TK-2406/2407: Service ManualDocument46 pagesTK-2402 (V) /2402 TK-2406/2407: Service Manualfelix FloresNo ratings yet

- IPnest: Interface Ip Survey USB PCIe HDMI DDR MIPIDocument15 pagesIPnest: Interface Ip Survey USB PCIe HDMI DDR MIPIEricIPNo ratings yet

- 01696260Document10 pages01696260arthura75075No ratings yet

- divIDE Plus ManualDocument140 pagesdivIDE Plus ManualOscar Arthur KoepkeNo ratings yet

- Storage Calculator ValerusDocument14 pagesStorage Calculator Valeruspeugeniu_1No ratings yet

- Railway (EC)Document41 pagesRailway (EC)luckyNo ratings yet

- Eee 523 ProjDocument12 pagesEee 523 ProjBodhayan PrasadNo ratings yet