Professional Documents

Culture Documents

Amba

Uploaded by

Atish BardeCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Amba

Uploaded by

Atish BardeCopyright:

Available Formats

9

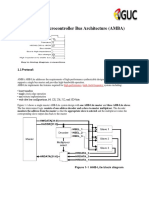

Chapter 3

AMBA Specification

In this chapter, we introduce an on-chip communication standard, called

Advanced Microcontroller Bus Architecture (AMBA) [15] . AMBA specification

defines three distinct bus architectures. Advanced high-performance bus (AHB) and

advanced-system bus (ASB) are both for high clock frequency module. But ASB is

hardly used in peripheral module in popular SOC system recently. The last bus

architecture is advanced peripheral bus (APB), which is mainly used for low-power

peripheral modules. Section 2.1 talks about the usage and functionalities of three

distinct bus architectures. The signal declaration and all kinds of transfer type are

discussed in section 2.2. The last section of this chapter shows the architecture of

AHB component, including master wrapper, slave wrapper and direct-memory-

access (DMA) controller.

3.1 Introduction of AMBA

Well compare the three distinct bus architectures defined in AMBA

specification in aspect of usage and functionality.

The AHB is used as the backbone bus for high-performance system and

supports connection between embedded processor, on-chip and off-chip memory

interface or bridges to low-performance system where most of the peripheral

devices located. AHB is more complex and has more transfer functionalities than

ASB, which is the alternative choice for system bus. APB is optimized for minimal

power consumption and reduces complexity to peripheral devices integration. APB

10

is usually used for interfacing peripheral devices with low bandwidth and do not

require high performance like pipeline architecture.

Table 1 shows the features that each bus architecture support. We choose AHB

as our system bus. All the IP integrated in this system must be AHB-compliant.

AHB data transfer will be detailed in next section.

AHB ASB APB

High performance High performance Low power

Pipelined operation Pipelined operation Latched address and control

Multiple bus masters Multiple bus masters Simple interface

Burst transfers Burst transfer Suitable for many peripherals

Split transactions

Wider data bus configuration

(64 and 128 bit)

Table 1. AMBA Features

Figure 5 illustrates a typical AMBA system. Several master or slave devices

are connected via AHB or ASB which are often used as system bus. The high-

performance ARM processor which acts as system controller is the typical master

device in this system. The processor can load instructions from program memory

and execute them. The data transfer between each memory module and peripheral

devices also can be done by it. The processor can send control data via the method

to control the devices implemented in high-performance system like DMA bus

master.

11

Expansion Memory

Interface

High-bandwidth

On-chip RAM

High-performance

ARM Processor

DMA

Bridge

Uart Timer

AHB or ASB

APB

AHB to APB Bridge

or

ASB to APB Bridge

PIO KeyPad

Figure 5. AMBA system

The bridge locates between system bus and peripheral bus. While transferring

data from processor to peripheral devices like UART, timer, peripheral I/O and

keyboard, the bridge convert the transferred signals from one type to another for

satisfying different performance and protocol.

3.2 AMBA AHB

The AMBA AHB bus protocol is designed to be used with a central

multiplexer interconnection scheme. All the master devices drive out the address

and control signals indicating the transfer they with to perform. The arbiter

determines which master devices has its address and control signals sending to all of

slave devices. A central decoder is required to control the read data and response

signal multiplexer, which selects appropriate signal from the slave involved in the

transfer. The slave devices passively wait for address and control signals from one

of the master devices. When the slave device is selected, it has to provide the

response signals indicating the transfer status to central decoder.

Figure 6 illustrates the structure required to be implemented in AHB system

with two master and three slave devices.

12

Write Data Mux

Read Data Mux

Address and

Control Mux

HADDR

Master #1

Master #2

Slave #1

Slave #2

Slave #3

Arbiter

Decoder

HADDR

HWDATA

HWDATA

HRDATA

HRDATA

HADDR

HWDATA

HRDATA

HADDR

HWDATA

HRDATA

HADDR

HWDATA

HRDATA

Figure 6. AMBA AHB Structure

3.2.1 AMBA AHB Signal List

In order to design the wrapper, we must figure out the signal declarations for

AHB. Table 2 describes the signal declarations used in common AHB system.

3.2.2 AHB Transfer Type

The AHB transfer types consist of basic transfer and burst transfer.

Figure 7 shows the basic transfer on AHB. One data transfer can be separated

into two phases, one is address and the other is data. The master devices drive out

control and address signal at address phase. Data and appropriate response driven by

selected slave device are transferred at data phase. Address phase lasts only one

clock cycle, but data phase may require several clock cycles.

13

Name Width Source Destination Description

HCLK 1 Global All devices System clock signal

HRESETn 1 Global All devices Negative reset signal

HBUSREQx 1 Masters Arbiter Master bus request signal

AHB supports at most 16 masters on a bus. There are at most 16 bus request lines in the system.

Arbiter will sample these requests to determine which master would be granted.

HLOCKx 1 Masters Arbiter Master transfer lock signal

There are 16 signal lines came from 16 masters in AHB. If the signal is high, it means that this

transfer should lock bus until transfer complete.

HADDR 32 Masters Slaves and Arbiter Address signal from one of

masters.

HTRANS 2 Master Slave Transfer type signal

AHB master transfer type, which can be IDLE, BUSY, NONSEQ or SEQ. This signal comes from

the granted master.

HBURST 3 Master Slave Burst type signal

This signal comes from the granted master. It indicates the type of burst transfer like SINGLE,

INCR, and WRAP.

HRESP 2 Slave Master Slave response signal

This signal which comes from the selected slave can be OKAY, ERROR, RETRY or SPLIT.

HREADY 1 Slave Master Slave response signal

This signal comes from the selected slave. When HREADY is equal to HIGH, it indicates that the

transfer has finished on the bus. Otherwise, it means the transfer should be extended or the

ERROR, RETRY and SPLIT may happen.

HGRANTx 1 Arbiter Master Master bus granted signal

These signals would connect to each relative master. When one of the HGRANT signal is HIGH, it

means that one of master has the bus ownership and the master can perform the transfer operation.

HMASTER 4 Arbiter Split-capable slave Master bus granted signal

This signal would show which master is granted on the bus. When a slave starts to do SPLIT

transaction, the slave needs to record the split master by storing this signal.

HMASTLOCK 1 Arbiter Split-capable slave Master bus granted signal

This signal shows that which master is granted for doing lock transfer. If the transaction are lock

transfer, the slave could not do SPLIT transaction.

HSELx 1 Decoder Slaves Slave selected signal

This signal would connect to each slave. When this signal to one slave is HIGH, it means that the

slave has been selected.

Table 2. AHB Signal List

14

Data A

Control

A

Address phase Data phase

HADDR[31:0

HCLK

Control

HREADY

HWDATA[31:0

HRDATA[31:0]

Data A

Figure 7. Basic Transfer

Slave device can insert wait cycles into transfer to have more time for

preparing valid data. When performing read operation, the slave device de-asserts

the HREADY signal until the read data is valid. When performing write operation,

the master device holds write data until the slave device asserts HREADY signal.

Figure 8 illustrates the waveform of basic transfer with wait cycle.

Data A

Control A

A

Address phase Data phase

HADDR[31:0

HCLK

Control

HREADY

HWDATA[31:0

HRDATA[31:0]

Data A

Wait cycle

Figure 8. Basic Transfer with wait cycle

15

AHB can support pipeline operation. The data phase of first transfer and the

address phase of second transfer can overlap to get better performance. The

waveform is illustrated in Figure 9. Transfer A and transfer C have no wait cycles,

but transfer B has one. The wait cycle extends the data phase of transfer B and the

master device holds the control signals of transfer C one more clock cycle.

Control A

A

Data C Data A

Data A Data B Data C

Control B Control C

B C

Data B HRDATA[31:0]

HADDR[31:0

HCLK

Control

HREADY

HWDATA[31:0

Figure 9. Pipelined Transfer

Burst transfer is sequential transfer. Before we talk about the burst transfer, we

must detail the transfer type encoding signal, HTRANS first. There are four

different types of HTRANS includes IDLE, BUSY, NONSEQ (non-sequential), and

SEQ (sequential).

IDLE indicates that no data transfer is required. In this state, its not going to

perform any data transfer. BUSY allows the master device inserting idle cycles

during burst transfer. This transfer type indicates that the master device wants to

continue the burst transfer, but the next transfer cant take place immediately. The

address and control signals be held during BUSY transfer type.

16

NONSEQ indicates the first transfer of burst transfer or just a single transfer.

The address and control signals in this transfer type are not related to the previous

transfer. The followed transfer type in burst transfer is SEQ and the address and

control signals are related to the previous transfer. For incremental burst, the

followed address is equal to the address of the previous transfer plus the size of

transfer in byte. For wrapping burst, the address of the transfer wraps at the address

boundary equal to the size in bytes multiplied by the number of beats in the transfer.

Burst transfer must not exceed a 1KByte address boundary. Therefore it is

important that master device does not attempt to perform incremental or wrapping

burst transfer which crosses the address boundary. An incremental burst transfer can

be any length, but under the 1KByte address boundary constraint. Figure 10 shows

the waveform of burst transfer.

Data

0x28

Data

0x24

INCR

0x2C 0x28 0x24

SEQ

Data A

Data

0x20

0x24

BUSY

0x20

NONSEQ

HRDATA[31:0]

HTRANS[1:0]

HCLK

HADDR[31:0]

HREADY

HWDATA[31:0

HBURST[2:0]

SEQ SEQ

Data

0x2C

Data

0x24

Data

0x2C

Data

0x2C

Figure 10. Burst Transfer

3.3 AHB Device Implementation

We only implement AHB master device, slave device and DMA controller

because of the arbiter and decoder has been in our platform. In this section, we

introduce the I/O interface and finite state machine of each device.

17

3.3.1 AHB Slave Interface and FSM

After the master device has started the transfer, the slave device then

determines how the transfer should progress. The slave device receives HSEL signal

which comes from decoder to recognize it is chosen or not. Whenever a slave device

is chosen, it must provide the response which indicates the status of the transfer like

complete or error.

Figure 11 displays the I/O for an AHB slave device. If the slave device

supports SPLIT transfer, it must have additional ports include HMASTER,

HMASLOCK, and HSPLIT. We do not mention about this issue in this thesis.

HSELx

HBURST

HSIZE

HTRANS

HMASTLOCK

HWRITE

RESET

HRESETn

CLOCK

HCLK

AHB

Slave

Device

HMASTER

HADDR

HWDATA HRDATA

HSPLITx

HRESP

HREADY

Split-capable

Slave

Transfer

Response

Data Data

Select

Address

and

Control

Figure 11. AHB Slave I/O

Lets consider the finite state machine of AHB slave device. It starts from idle

state. If the device is chosen, the state can move to address state then data state. The

two states map to the address phase and data phase of the transfer on AHB. We can

also define the error condition that leads the state to error state. In error state, the

response signal will be set to ERROR, RETRY, or SPLIT. Retry and split state

handle these two different conditions. Figure 12 illustrates the FSM of AHB slave

device. Wait state is to handle the wait cycle insertion.

18

ADDRESS IDLE DATA WAIT

ERROR RETRY SPLIT

Figure 12. AHB Slave FSM

3.3.2 AHB Master Interface and FSM

AHB master device has the most complex bus interface in AMBA system and

can perform data transfer. When performing transfer, the master device provides the

address and control signals and monitors the transfer response from slave device.

Only one master device gets bus ownership on AHB. Figure 13 displays the I/O for

an AHB master device.

HGRANT

RESET

HRESETn

CLOCK

HCLK

AHB

Master

Device

HRDATA

HRESP

HREADY Transfer

Response

Data

Arbiter

HBURST

HSIZE

HPRONT

HWRITE

HADDR

HWDATA Data

Address

and

Control

HTRANS

HBUSREQ

HLOCKx Arbiter

Transfer type

Figure 13. AHB Master I/O

19

The FSM of AHB master device also starts from the IDLE state. When the

master device attempts to perform data transfer, BUSREQ is asserted to arbiter for

bus ownership. After granting the bus, the master device can perform single or burst

transfer. The behavior maps to the NONSEQ and SEQ states. The device can also

insert wait cycles during transfer. It map to BUSY state. WAIT state reflects the

wait cycles inserted by slave device. Figure 14 illustrates the FSM of AHB master

device.

IDLE SEQ NONSEQ

BUSY

BUSREQ

WAIT ERROR

Figure 14. AHB Master FSM

3.3.3 AHB DMA and FSM

DMA (Direct Memory Access) controller can transfer a mount of data between

every memory modules and peripherals. The processor doesnt have to waste clock

cycles to handle data transfer if there is a DMA controller in the system. In this

section, we introduce the control method and architecture of typical DMA controller

with AHB interface.

The DMA controller consist both AHB master and slave interface. The slave

interface receives the control information like source address, destination address or

the number of beats from processor. The master interface uses the information to

20

perform data transfer from source address to destination address. The mechanism is

memory-mapped I/O. Table 3 lists the memory-mapped register description. Figure

15 shows the architecture of DMA controller.

Address offset Name Type Width Description

0x00 [0] DMA_Enable r/w 1 If the DMA enable signal is

asserted, the DMA controller is

ready to be used.

0x00 [10:1] DMA_Beat_Count r/w 10 The number of beat count in

transfer. 1023 at most.

0x04 DMA_Source r/w 32 DMA source address register

0x08 DMA_Destination r/w 32 DMA destination address register

0x0C DMA_Interrupt_Mask r/w 8 When DMA complete transfer, the

interrupt signal is assert. Software

driver should close the interrupt and

run the sub-routine

Table 3. Register Description for DMA Controller

This is the DMA operation flow:

1. If the processor wants to use DMA controller, it has to check the

DMA_Enable register through AHB slave interface. If the signal is de-assert,

it means the DMA controller is working. Otherwise the device is ready to

use.

2. If the module is ready to use, processor transfer configuration data like

number of beat count, source and destination address to the registers of

DMA controller. The content of DMA_Enable must be de-asserted.

21

3. The DMA controller starts to transfer data from source to destination address.

The performance is related to the number of buffer in controller.

4. If the transfer is complete, the DMA controller asserts the interrupt signal to

interrupt controller. Processor uses the DMA_Interrupt_Mask register to

disable the interrupt signal and then run interrupt subroutine.

Response

Address and control

Read and write data

Read and write data

Response

Address and control

Slave

Interface

Master

Interface

Register

File

Central Controller

of DMA

FIFO Buffer

Figure 15. Architecture of DMA Controller

You might also like

- RTL Design of AHB ProtocolDocument10 pagesRTL Design of AHB ProtocolAnji medidiNo ratings yet

- Calculator With Keypad and LCDDocument30 pagesCalculator With Keypad and LCDSyed Ariful Islam Emon67% (3)

- Abreviacoes Siglas Usadas EletronicaDocument6 pagesAbreviacoes Siglas Usadas EletronicaDiegoNo ratings yet

- Brevet - Contre Mesure Technologie V2KDocument42 pagesBrevet - Contre Mesure Technologie V2KFabrice Bresil0% (1)

- Design of An Efficient FSM For An Implementation of AMBA AHB MasterDocument5 pagesDesign of An Efficient FSM For An Implementation of AMBA AHB Masterrahul shiv shankarNo ratings yet

- Implementation of AMBA AHB Protocol Using Verilog HDLDocument4 pagesImplementation of AMBA AHB Protocol Using Verilog HDLEditor IJRITCCNo ratings yet

- Seminar ReportDocument17 pagesSeminar ReportG-1076-Sudhansu AwasthiNo ratings yet

- Ahb 5Document8 pagesAhb 5ShaikAzharNo ratings yet

- Amba AhbDocument4 pagesAmba AhbArun BaskaranNo ratings yet

- Design and Verification of AMBA AHBDocument6 pagesDesign and Verification of AMBA AHBrishi tejuNo ratings yet

- AHB SignalsDocument2 pagesAHB Signalsavdhesh7No ratings yet

- AHB FeaturesDocument12 pagesAHB Featuresrahulnivak2333No ratings yet

- Arm Ahb For McusDocument7 pagesArm Ahb For McusBharathwajan ParthasarathyNo ratings yet

- On-Chip Bus Protocols: National Chiao Tung University Chun-Jen Tsai 05/3/2011Document63 pagesOn-Chip Bus Protocols: National Chiao Tung University Chun-Jen Tsai 05/3/2011madhukirNo ratings yet

- Amba 454Document27 pagesAmba 454HemanthNo ratings yet

- AMBA ProtocolDocument11 pagesAMBA Protocolsachin palNo ratings yet

- AMBA APB v2Document20 pagesAMBA APB v2Aditya RajaNo ratings yet

- Design and Verification of AMBA AHB-Lite protocol using Verilog HDLDocument8 pagesDesign and Verification of AMBA AHB-Lite protocol using Verilog HDLHeekwan SonNo ratings yet

- Vlsi Design of Amba Based Ahb2apb BridgeDocument12 pagesVlsi Design of Amba Based Ahb2apb BridgeAnonymous e4UpOQEPNo ratings yet

- Session 10 - AMBA-busDocument35 pagesSession 10 - AMBA-busSai Mohnish MuralidharanNo ratings yet

- Amba Protocols OverviewDocument25 pagesAmba Protocols OverviewVidya kpNo ratings yet

- USARTDocument17 pagesUSARTtharunvenkataNo ratings yet

- Technical Seminar ReportDocument22 pagesTechnical Seminar Reportsai sandeep kumarNo ratings yet

- Technical Seminar ReportDocument22 pagesTechnical Seminar Reportsai sandeep kumarNo ratings yet

- Technical Seminar ReportDocument22 pagesTechnical Seminar Reportsai sandeep kumarNo ratings yet

- AMBA Interface Design RNSITDocument5 pagesAMBA Interface Design RNSITShailendra RajputNo ratings yet

- Design Amba Based Ahb To Apb Bridge Using Verilog HDL: Prarthi Bhatt, Prof..Devang ShahDocument5 pagesDesign Amba Based Ahb To Apb Bridge Using Verilog HDL: Prarthi Bhatt, Prof..Devang ShahPotnuru KarishmaNo ratings yet

- Ambabus 120718061800 Phpapp02 PDFDocument18 pagesAmbabus 120718061800 Phpapp02 PDFAashishNo ratings yet

- Direct Memory Access (DMA) : Burst ModeDocument7 pagesDirect Memory Access (DMA) : Burst ModeAnand ReddyNo ratings yet

- 8086 SignalsDocument11 pages8086 SignalssushalworkNo ratings yet

- Labview Serial CommunicationDocument0 pagesLabview Serial Communicationmajidkhan04No ratings yet

- AMBA Peripheral Bus Controller: Data SheetDocument14 pagesAMBA Peripheral Bus Controller: Data SheetggmaneNo ratings yet

- Implementation Methodology of High Performance Multi Byte Data Access Control of AMBA BusDocument5 pagesImplementation Methodology of High Performance Multi Byte Data Access Control of AMBA BusKumar Goud.KNo ratings yet

- 07a Section7 Notes CPD sdds1 AXIDocument18 pages07a Section7 Notes CPD sdds1 AXIRohit BanerjeeNo ratings yet

- Design & Verification of AMBA APB ProtocolDocument4 pagesDesign & Verification of AMBA APB ProtocolKrishnajithKjNo ratings yet

- Design of AMBA Based AHB2APB BridgeDocument12 pagesDesign of AMBA Based AHB2APB BridgeSai Kiirran CH100% (2)

- Amba Bus: Advanced Micro Controller Bus ArchitectureDocument15 pagesAmba Bus: Advanced Micro Controller Bus ArchitecturemukulNo ratings yet

- Design AMBA-AXI Protocol VHDL SoCDocument4 pagesDesign AMBA-AXI Protocol VHDL SoCBethuna Sayed100% (1)

- AHB-APB Bridge Architecture and Protocol OverviewDocument15 pagesAHB-APB Bridge Architecture and Protocol OverviewDebabrato BanikNo ratings yet

- 02 TopologyDocument19 pages02 TopologyVarunNo ratings yet

- MBSD NOTES (PDF 2)Document25 pagesMBSD NOTES (PDF 2)Syed Ali Raza NaqviNo ratings yet

- AMBA Advanced Peripheral BusDocument8 pagesAMBA Advanced Peripheral BusbalamuraliNo ratings yet

- AMBA PDFDocument14 pagesAMBA PDFSHUKLA NISHANTNo ratings yet

- NewAMBA PDFDocument14 pagesNewAMBA PDFPralhadrao sNo ratings yet

- Arm Amba AhbDocument18 pagesArm Amba AhbgeethaNo ratings yet

- Optimize DMA Controller Data TransferDocument25 pagesOptimize DMA Controller Data Transfersatyanarayana12No ratings yet

- Configure Serial Communication InterfaceDocument31 pagesConfigure Serial Communication InterfaceskarthikpriyaNo ratings yet

- Pin Diagram of 8086Document21 pagesPin Diagram of 8086adithya123456100% (5)

- Workbook Workbook Workbook Workbook Workbook: Try Yourself QuestionsDocument7 pagesWorkbook Workbook Workbook Workbook Workbook: Try Yourself QuestionsarunNo ratings yet

- Presentation Microprocessors: 8237 DMA ControllerDocument13 pagesPresentation Microprocessors: 8237 DMA ControllerMimansha SharmaNo ratings yet

- Micro Channel ArchitectureDocument67 pagesMicro Channel ArchitectureMuhammad Riski SaputraNo ratings yet

- Unit IIIDocument42 pagesUnit IIISoundarrajan RajanNo ratings yet

- On-Chip Bus: Speaker: Tian-Sheuan Chang July, 2004Document40 pagesOn-Chip Bus: Speaker: Tian-Sheuan Chang July, 2004Tarun GhoshNo ratings yet

- Serial Data Transmission Vs Parallel Data Transmission: Unit 5Document16 pagesSerial Data Transmission Vs Parallel Data Transmission: Unit 5achuu1987No ratings yet

- Unit 6Document16 pagesUnit 6sung hooNo ratings yet

- One Bit at A Time, Slower and Less No of Cables RequiredDocument23 pagesOne Bit at A Time, Slower and Less No of Cables RequiredKiran KumarNo ratings yet

- Register Transfer Logic: This ChapterDocument25 pagesRegister Transfer Logic: This ChapterSai lakshmi SindhuraNo ratings yet

- Input-Output Interfaces and Communication ProtocolsDocument21 pagesInput-Output Interfaces and Communication ProtocolsBlackk SpydoNo ratings yet

- Programmable Interval Timer 8253: Architecture of 8253Document13 pagesProgrammable Interval Timer 8253: Architecture of 8253Srikanth KodothNo ratings yet

- Presented by B. Koteswar Rao 08G71D7005 Under The Guidence of Mr.B. Naresh Reddy M.TechDocument14 pagesPresented by B. Koteswar Rao 08G71D7005 Under The Guidence of Mr.B. Naresh Reddy M.TechSrinivas KumarNo ratings yet

- SATA Device Controller with Optional DMADocument2 pagesSATA Device Controller with Optional DMAsibridgeNo ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- OSDS-Multiple Choice QuestionsDocument39 pagesOSDS-Multiple Choice QuestionsNuhu Magwai100% (1)

- Ring Main Protection: January 2015Document6 pagesRing Main Protection: January 2015Vaibhav kumbharNo ratings yet

- Doc6175 PDFDocument775 pagesDoc6175 PDFNani2220No ratings yet

- s71200 Easy Book en-US en-USDocument304 pagess71200 Easy Book en-US en-USAli Özkan KayaNo ratings yet

- Bojuxing Industry BJ8P509FGA - C84125Document39 pagesBojuxing Industry BJ8P509FGA - C84125spotNo ratings yet

- MSP430 5xx ODWDocument84 pagesMSP430 5xx ODWHung PhamNo ratings yet

- Using External Interrupts For MegaAVR DevicesDocument12 pagesUsing External Interrupts For MegaAVR DevicesJhon ZumaetaNo ratings yet

- ErtosDocument16 pagesErtosМахеш Бабу100% (1)

- Embedded RTOS Automotive Material 2020Document277 pagesEmbedded RTOS Automotive Material 2020Mohankumarglmanu MohankumarglmanuNo ratings yet

- PLC - s7300 - sm331 - Ai - 8x12 - Bit - Getting - Started - En-Us - En-Us - (Cuuduongthancong - Com)Document76 pagesPLC - s7300 - sm331 - Ai - 8x12 - Bit - Getting - Started - En-Us - En-Us - (Cuuduongthancong - Com)Cường TrầnNo ratings yet

- SIRTOS A Simple Real Time Operating SystemDocument6 pagesSIRTOS A Simple Real Time Operating Systemmiguel angelNo ratings yet

- 8-Bit Microcontroller With 8K Bytes of In-System Programmable Flash AT90S8515 Rev. C Errata SheetDocument4 pages8-Bit Microcontroller With 8K Bytes of In-System Programmable Flash AT90S8515 Rev. C Errata Sheetcarlos augusto do carmo braiaNo ratings yet

- Universal Verification Methodology Based Verification Environment For PCIE Data Link LayerDocument5 pagesUniversal Verification Methodology Based Verification Environment For PCIE Data Link LayerAnonymous kw8Yrp0R5rNo ratings yet

- Lec1 Operating SystemDocument33 pagesLec1 Operating SystemMirna AttallahNo ratings yet

- Infineon TC1766 DS v01 00 enDocument117 pagesInfineon TC1766 DS v01 00 enFiliberto Conde MayoNo ratings yet

- Et200sp TM Count 1x24v Manual en-US en-USDocument106 pagesEt200sp TM Count 1x24v Manual en-US en-USrafaelotreNo ratings yet

- Master Memory MapDocument308 pagesMaster Memory MapgamerhobbistaNo ratings yet

- Design and Implementation of Digital Trigger Circuit For Converter IJERTV1IS3229 PDFDocument6 pagesDesign and Implementation of Digital Trigger Circuit For Converter IJERTV1IS3229 PDFShakir HussainNo ratings yet

- VLT Automationdrive FC 300: Safe PLC Interface Option MCB 108Document2 pagesVLT Automationdrive FC 300: Safe PLC Interface Option MCB 108Jorge LoeraNo ratings yet

- Confidential: Preliminary Datasheet-Please See The Known Issues ListDocument33 pagesConfidential: Preliminary Datasheet-Please See The Known Issues Listmsc51No ratings yet

- 08 Grp11 Hybrid EbcmDocument31 pages08 Grp11 Hybrid Ebcmeurospeed2No ratings yet

- INTERRUPT PROGRAMMING IN CDocument4 pagesINTERRUPT PROGRAMMING IN CNova Hani50% (2)

- Ds 11031Document6 pagesDs 11031Nch NMNo ratings yet

- Embedded System Lab - Blinking LED, Seven Segment Display and LCD Interfacing Projects Using PIC MicrocontrollerDocument62 pagesEmbedded System Lab - Blinking LED, Seven Segment Display and LCD Interfacing Projects Using PIC Microcontrollerfatima100% (1)

- SWRZ 127 ADocument15 pagesSWRZ 127 ASarah Joy ManimtimNo ratings yet

- Cortex-M3 Reference ManualDocument410 pagesCortex-M3 Reference ManualAgabier12No ratings yet

- CSC203 - Operating System ConceptsDocument55 pagesCSC203 - Operating System ConceptsMohd KhairiNo ratings yet