Professional Documents

Culture Documents

IEEE Paper Word Template A4 V3

Uploaded by

Mudit GuptaCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

IEEE Paper Word Template A4 V3

Uploaded by

Mudit GuptaCopyright:

Available Formats

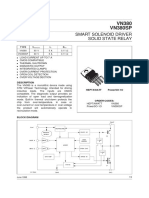

Performance Analysis of 180nm CMOS Digital

Circuit Technologies

Bhawana Panwar, Shruti Kalra(Member IEEE)

Department of Electronics and Communication

J aypee Institute of Information Technology, Noida, India

bhawanapanwar@gmail.com, shruti.sabharwal@jiit.ac.in

AbstractFor your paper to be published in the conference

proceedings, you must use this document as both an instruction

set and as a template into which you can type your own text. If

your paper does not conform to the required format, you will be

asked to fix it.

I. INTRODUCTION

Well-designed and properly functioned digital circuits are

accomplished by selecting right technology node and

considering all issues related to performance parameters. The

technology node for any digital circuit is selected according to

the application. This paper presents a detailed approach for

the design and performance analysis for 180nm CMOS digital

circuit technology. These performance analysis are based on

relatively simple sets of fundamental device parametric and

circuit equations.

As device gets smaller many aspects of their

performance deteriorate: leakage increases, gain decreases,

and sensitivity to unavoidable small fluctuations in

manufacturing process rises dramatically. Power and energy

have become the key limiters on many new designs. we look

at recent computer-aided design efforts in modeling, analysis,

and according to that optimize for nanoscale designs. Our

goal in this paper is to gather all the performance parameters

related to any digital circuit. Also, perform the H-SPICE

simulation for 180nm technology node in order to match the

experimental results with BSIM3v3 model equations. To see

improvement of technology node at 180nm, we compare

these results by computing available first order modal

equations.

The performance parameter of any digital circuit can be

listed as: Switching point, Noise margin, Total capacitance,

Power dissipation, Fan-in, Fan-out, leakage and Propogation

delay.

The base of our analysis is based on CMOS inverter

circuit as its truly the nucleus of all digital designs. Once its

operation and properties are clearly understood, designing

more intricate structures such as NAND gates, adders,

multipliers, and microprocessors is greatly simplified. The

electrical behavior of these complex circuits can be almost

completely derived by extrapolating the results obtained from

inverter circuit.

The paper is organized as follows. Switching Point

for CMOS inverter is analyzed in Section II, Noise margin in

Section III, Total Capacitance in Section IV, Power

dissipation in Section V and Effects of

on proppgation

delay in Section VI. Finally, conclusions are provided in

Section VII.

II. SWITCHING POINT

The switching threshold,

is defined as the point where

. Its value can be obtained graphically from the

intersection of the VTC with the line given by

(see

in Figure 1). We analyze that the width of PMOS and NMOS

transistors should be in 3:1 ratio such that the switching

threshold of a CMOS inverter, implemented in our generic

0.18 um CMOS process, should be located in the middle

between the supply rails i.e. at .75V (taking

=1.5V). We

get the value of switching threshold

=.743V by H-SPICE

simulation for

=1.62um and

=.54um at 180nm

technology node. In this region, both PMOS and NMOS are

always saturated, since

. An analytical expression

for

is obtained by equating the currents through

Fig. 1. Shows the DC or transfer characteristic of CMOS inverter. Fromthis

graph we measure the Switching Point (

M

V )

the transistors. We ignore the channel length modulation

effects. By solving for

yields

2

+

2

1+

(1.1)

with =

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1 1.1 1.2 1.3 1.4 1.5

0

0.3

0.6

0.9

1.2

1.5

X: 0.7429

Y: 0.7429

V

in

V

o

u

t

Switching Point

For large values of

(compared to threshold and saturation

voltages), Equation(1.1) can be simplified as:

1+

(1.2)

From equation(1.2)

=1.234V. This shows that the result

obtained by equation(1.2) is not true. So, we have to modify

first order equation in order to match our results for 180nm

technology by using available mathematical approach. The

method we our using in this paper named as least square curve

fitting method. The modified equation by using this

approach is given as

+

(1.3)

Where

=

1

0

and =

1

.

Values of fitting parameter (A and B) is calculated by least

square curve fitting method as,

0

=1.125 and

1

=1.259.

Value of

form equation (1.3) is calculated as

=.765V.

The simulated value of switching threshold confirms the

calculated value with 2.87% error.

III. NOISE MARGIN

For a gate to be robust and insensitive to noise disturbances, it

is essential that the 0 and 1 intervals be as large as

possible. A measure of the sensitivity of a gate to noise is

given by the noise margins

(noise margin low) and

(noise margin high), which quantize the size of the legal 0

and 1, respectively, and set a fixed maximum threshold on

the noise value:

OL

V

IL

V

L

NM =

(1.4)

IH

V

OH

V

H

NM =

(1.5)

The equation used for calculation are

=

2

+

0,

0,

1+

(1.6)

+

0,

+

+

0,

1+

(1.7)

where,

By using Equation (1.6) and (1.8), we get value of

=0.673V and

=0.813 V. Using calculated value of

and

,we get value of

=0.673V and

=0.687V

from equation (1.4) and (1.5). To match our results for 180nm

technology, we extract the value of

and

by circuit

simulation in H-SPICE. Using Matlab we got

(gain) verses

plot (as shown in Fig. 2).

and

are the

operational points of the CMOS inverter circuit where gain=-

1. We got value of

=0.796 and

=0.536 from the plot at

gain= -1. Using Equation 1.4 and 1.5, we got value of

=0.536 and

=0.704 . The simulated value and

calculated value of Noise margin confirms the value with 2.35%

error.

Fig. 2. Noise margin

IV. TOTAL CAPACITANCE

Manual analysis of MOS circuits where each capacitor is

considered individually is virtually impossible and is

exacerbated by the many nonlinear capacitances in the MOS

transistor model. To make the analysis tractable, we assume

that all capacitances are lumped together into one single

capacitor

, located between

and GND.

Fig. 3. Parasitic capacitances, influencing the transient behavior of the

cascaded inverter pair

Fig. 3 shows the schematic of a cascaded inverter pair. It

includes all the capacitances influencing the transient response

of node

. Accounting only for capacitances connected to

the output node, we proceed our analysis.

The results of bringing all the components together are

summarized in Table I. Notice that the load capacitance is

almost evenly split between its two major components: the

intrinsic capacitance, composed of diffusion and overlap

capacitances, and the extrinsic load capacitance, contributed

by wire and connecting gate.

.2 .25 .3 .35 .4 .45 .5 .55 .6 .65 .7 .75 .8 .85 .9 .95 1.0 1.1 1.2

-12

-11

-10

-9

-8

-7

-6

-5

-4

-3

-2

-1

0

V

I L

V

I H

V

in

(V)

G

a

i

n

V

M

Capacitor Expression Value (fF)

( )

Value (fF)

( )

Cgd1 2 CGD0n Wn 0.395 0.395

Cgd2 2 CGD0p Wp 1.062 1.062

Cdb1 Keqn ADn CJ +

Keqswn PDn CJ SW

0.414 0.463

Cdb2 Keqp ADp CJ +

Keqswp PDp CJ SW

1.059 0.874

Cg3 (CGD0n+CGSOn)

Wn +Cox Wn Ln

1.232 1.232

Cg4 (CGD0p+CGSOp)

Wp +Cox Wp Lp

3.573 3.573

7.735 7.599

Table I. Components of C

L

(for high-to-low and low-to-high transitions)

Analysis of

by SPICE simulation is as follows:

We can obtain propagation delay for the high-to-low

transition by using this equation:

= ln(2)

= 0.69

(1.8)

1) Firstly connect a capacitor (

) between

and

Ground, Assume

=12pf, and do circuit simulation

so that we get triangular wave at output node, note

down value of

at 50% i.e.,

=35.9nsec (Fig.

4).

2) From circuit simulation Reqn value after calculation

obtained as Reqn=4.335 k (by Eq 1.8).

3) Remove

from the circuit and again do circuit

simulation, note down value of

at 50% i.e.,

=17.2psec (Fig. 5).

4) by using above calculated value of

and Reqn ,

we get value of

( )=5.749fF.

Fig. 4: SPICE simulation for tphl(with capacitor cl=12pf)

Figure 8: SPICE simulation for tphl(without capacitor)

Similarly, propagation delay for the low-to-high transition

given as

= 0.69

(1.9)

by using Equation(1.9) value of

=13.7psec and we get

value of

( )=4.6FfF.

Analysis of

by calculation:

In a CMOS inverter, the charge-up event of the output load

capacitance for falling input transition is completely

analogous to the charge-down event for rising input. When the

input voltage switches from high (

) to low (

) the

nMOS transistor is cut off, and the load capacitance is being

charged up through the pMOS transistor. The propagation

delay time

can be found as:

2

,

+

4

1

(1.10)

In above equation put the calculated value of

( ) i.e. 7.59fF.

After calculation we get

=13.76psec, which is

same as simulated value with .004% error.

V. POWER CONSUMPTION

Static Consumption: The static (or steady-state) power

dissipation of a circuit is expressed by Eq. (1.11), where

is the current that flows between the supply rails in the

absence of switching activity

(1.11)

Ideally, the static current of the CMOS inverter is equal to

zero, as the PMOS and NMOS devices are never on

simultaneously in steady-state operation. This makes CMOS

technology useable in low power and high-density

applications. There is, unfortunately, a leakage current

flowing through the reverse-biased diode junctions (as shown

0 0.2 0.4 0.6 0.8 1 1.2 1.4 1.6 1.8 2 2.2 2.4 2.6 2.8 3

x10

-7

0

0.25

0.5

0.75

1

1.25

1.5 1.5

Time (sec)

V

o

u

t

(

V

)

t

pLH

t

pHL

0 0.5 1 1.5 2

x10

-10

-0.5

-0.25

0

0.25

0.5

0.75

1

1.25

1.5

1.75

2

Time (V)

V

o

u

t

(

V

)

t

pLH

t

pHL

in figure 10) of the transistors, located between the source or

drain and the substrate. This contribution is, in general, very

small and can be ignored. CMOS inverter dissipates a

negligible amount of power during steady state operation. The

maximum current dissipation for CMOS inverter is less than

29uA obtained by H-SPICE simulation for 180nm

technology.

Fig. 9. Variation in

verses static power

Vsb (V) Vm(V) Drain Current

(pA)

Static

Power(pW)

.1 .553 4.4 6.60

.15 .566 4.35 6.525

.2 .573 4.3 6.45

.25 .623 4.25 6.375

.3 .646 4.2 6.30

.35 .648 4.15 6.225

.4 .648 4.1 6.15

.45 .649 4.05 6.075

.5 .649 4.0 6.00

.55 .649 3.95 5.925

Table II. SPICE simulation results by varying

, variation in switching point,

drain current and static power.

Table (2) shows as we increases the

voltage of CMOS

inverter, drain current decreases and it cause to decrease

static power.

Figure 10: shows supply voltage verses drain leakage current.

Dynamic Power Consumption: (Dynamic Dissipation due to

Charging and Discharging Capacitances) In order to compute

the power consumption, we have to take into account how

often the device is switched. If the gate is switched on and off

01

times per second, the power consumption equals

01

(1.12)

01

represents the frequency of energy-consuming transitions,

this is 01 transitions for static CMOS.

Figure 11: Variations in Vdd Verses Dynamic Power

The dynamic power is independent of the typical device

parameters, but is simply a function of power supply, load

capacitance and frequency of the switching.

VDD 1 .3 .5 .7 .9 1.1 1.3 1.5

Dynamic

Power(W)

1 9 26 51 84 126 176 236

TABLE (): Dynamic Power of CMOS Inverter varying with

Supply Voltage

REFERENCES

0.1 0.15 0.2 0.25 0.3 0.35 0.4 0.45 0.5 0.55 0.6

5.9

6

6.1

6.2

6.3

6.4

6.5

6.6

x10

-12

V

SB

(V)

S

t

a

t

i

c

P

o

w

e

r

(

W

)

0.2 0.4 0.6 0.8 1 1.2 1.4

1

2

x10

-4

V

DD

(V)

D

y

n

a

m

i

c

P

o

w

e

r

(

W

)

Arora, N. (2006). MOSFET Modeling for VLSI Simulation: Theory And

Practice (International Series on Advances in Solid State Electronics). World

Scientific Publishing Co., Inc.

You might also like

- Electronic Concepts - An Introduction - Jerrold KrenzDocument468 pagesElectronic Concepts - An Introduction - Jerrold KrenzAsdf FdsaNo ratings yet

- Recitation 2Document17 pagesRecitation 2Ahmed HassanNo ratings yet

- FinFET History and FundamentalsDocument55 pagesFinFET History and FundamentalsMurali Shanmuga Sundaram100% (2)

- Two Novel Fully Complementary Self-Biased CMOS Differential AmplifiersDocument4 pagesTwo Novel Fully Complementary Self-Biased CMOS Differential Amplifiersmanikanta11No ratings yet

- Design of Traffic Light Controller Using Timer CircuitDocument3 pagesDesign of Traffic Light Controller Using Timer CircuitVinooja cNo ratings yet

- r7100406 Network AnalysisDocument4 pagesr7100406 Network AnalysissivabharathamurthyNo ratings yet

- VLSI Implementation of A Low-Cost High-Quality Image Scaling ProcessorDocument5 pagesVLSI Implementation of A Low-Cost High-Quality Image Scaling ProcessorManish BansalNo ratings yet

- Assignment 2Document5 pagesAssignment 2Jemosha JeNo ratings yet

- Enhanced Speech Recognition Using ADAG SVM ApproachDocument5 pagesEnhanced Speech Recognition Using ADAG SVM ApproachInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- EC8093 Unit 2Document136 pagesEC8093 Unit 2Santhosh PaNo ratings yet

- Experiment-3: %linear Convolution Using Circular ConvolutionDocument4 pagesExperiment-3: %linear Convolution Using Circular ConvolutionFAIZNo ratings yet

- Internship PPT FormatDocument11 pagesInternship PPT FormatDhanush V NNo ratings yet

- ECD Lab EEC 752Document17 pagesECD Lab EEC 752juhi99360% (5)

- Electronic Circuits Lab Manual Clippers and AmplifiersDocument29 pagesElectronic Circuits Lab Manual Clippers and AmplifiersAshwath NadahalliNo ratings yet

- Finite Word Length EffectsDocument9 pagesFinite Word Length Effectsohmshankar100% (2)

- Energy Band Theory and Classification of SolidsDocument128 pagesEnergy Band Theory and Classification of SolidsDiah Ayu KinasihNo ratings yet

- Electrical Circuits LabDocument64 pagesElectrical Circuits LabraveendrababupNo ratings yet

- VLSI Lab Part B SolutionsDocument40 pagesVLSI Lab Part B SolutionsNandiniManinarayanaNo ratings yet

- Astable and Monostable Multivibrator Trainer NV6507Document10 pagesAstable and Monostable Multivibrator Trainer NV6507Himadri MandalNo ratings yet

- 47-Wavelet Based Power Quality Disturbances Analysis of BLDC Motor Drive PDFDocument10 pages47-Wavelet Based Power Quality Disturbances Analysis of BLDC Motor Drive PDFveerannaNo ratings yet

- Atal FDP On Sensor Technology - 2Document3 pagesAtal FDP On Sensor Technology - 2Rameshkumar JayaramanNo ratings yet

- HackerRank Algorithm Problem SolvingDocument4 pagesHackerRank Algorithm Problem SolvingSasukedevil SnakemaniaNo ratings yet

- Assignment PS4 StudentRecord-1Document4 pagesAssignment PS4 StudentRecord-1anon_368873566No ratings yet

- Ec 2252 Communication Theory Lecture NotesDocument120 pagesEc 2252 Communication Theory Lecture NotesChoco BoxNo ratings yet

- Microwave Periodic Structures and Filter Design Using Image Parameter MethodDocument63 pagesMicrowave Periodic Structures and Filter Design Using Image Parameter MethodmuhzinamoideenNo ratings yet

- Design and Verify a Single Stage FET AmplifierDocument9 pagesDesign and Verify a Single Stage FET Amplifierswapnajeet shendkarNo ratings yet

- Chapter 7-AC STEADY STATE ANALYSIS. Cruicial TopicDocument55 pagesChapter 7-AC STEADY STATE ANALYSIS. Cruicial TopicDouglas OngomNo ratings yet

- UNIT-IV: Locus Diagrams and ResonanceDocument34 pagesUNIT-IV: Locus Diagrams and ResonanceRagha RamojuNo ratings yet

- Class 7Document24 pagesClass 7karthikNo ratings yet

- Software Design For Low PowerDocument20 pagesSoftware Design For Low PowerGokul B S MandyaNo ratings yet

- B e BmeDocument42 pagesB e BmeRAMESHKUMAR.S MCE-LECT/MECHNo ratings yet

- Torque - Slip Characteristic of A Three - Phase Induction MachineDocument28 pagesTorque - Slip Characteristic of A Three - Phase Induction MachineAli AltahirNo ratings yet

- TRB Circuit Theory Test 1Document6 pagesTRB Circuit Theory Test 1Ragunathan NarayananNo ratings yet

- Lesson Plan - Signals & Systems 2012Document3 pagesLesson Plan - Signals & Systems 2012KALAIMATHINo ratings yet

- 1.adc DacDocument35 pages1.adc DacGopinathan MNo ratings yet

- Considering: Rec. ITU-R P.530-8 1Document34 pagesConsidering: Rec. ITU-R P.530-8 1Vladan BozicNo ratings yet

- Exam MEP1553 Apr2010Document7 pagesExam MEP1553 Apr2010Abid JamaliNo ratings yet

- Image EnhancementDocument89 pagesImage EnhancementFarzana NazimNo ratings yet

- Lica Lab ManualDocument83 pagesLica Lab ManualDinesh DoddiNo ratings yet

- Wavelets and Multiresolution: by Dr. Mahua BhattacharyaDocument39 pagesWavelets and Multiresolution: by Dr. Mahua BhattacharyashubhamNo ratings yet

- TMS320C50 ArchitectureDocument2 pagesTMS320C50 ArchitectureParvatham Vijay100% (5)

- Multi Resolution Based Fusion Using Discrete Wavelet Transform.Document27 pagesMulti Resolution Based Fusion Using Discrete Wavelet Transform.saranrajNo ratings yet

- Lab Manual for Industrial Automation Diploma Electronics EngineeringDocument56 pagesLab Manual for Industrial Automation Diploma Electronics EngineeringEr Amarsinh RNo ratings yet

- Write A Mat Lab Program To Perform Linear and Circular Convolution of The Discrete Time Sequences XDocument26 pagesWrite A Mat Lab Program To Perform Linear and Circular Convolution of The Discrete Time Sequences XD Geetha Durai50% (2)

- ET7014-Application of MEMS Technology PDFDocument4 pagesET7014-Application of MEMS Technology PDFSaran ArunNo ratings yet

- Midterm Solution - COSC 3213 - Computer Networks 1Document13 pagesMidterm Solution - COSC 3213 - Computer Networks 1faesalhasanNo ratings yet

- DSP MCQDocument2 pagesDSP MCQBala MuruganNo ratings yet

- CE Amplifier - Record PartDocument10 pagesCE Amplifier - Record PartAlfred D'SouzaNo ratings yet

- Sample Delphi TVS Placement Test PaperDocument8 pagesSample Delphi TVS Placement Test PaperMuthu Palaniappan ANo ratings yet

- Lab # 01 To Study The Transient Response of RL Series Circuit MaterialsDocument4 pagesLab # 01 To Study The Transient Response of RL Series Circuit MaterialsYasir100% (1)

- CIRCUIT Analysis QB 20 21Document44 pagesCIRCUIT Analysis QB 20 216112 Shanmuga priyanNo ratings yet

- IEEE 13 Node Test FeederDocument11 pagesIEEE 13 Node Test FeederSebastián HernandezNo ratings yet

- CPU Scheduling Algorithm AssignmentDocument29 pagesCPU Scheduling Algorithm Assignmentsadman rahmanNo ratings yet

- Chapter4-Loading EffectsDocument41 pagesChapter4-Loading Effectshumervat100% (1)

- Cs2403 Digital Signal Processing NotesDocument106 pagesCs2403 Digital Signal Processing NotesRaja SekarNo ratings yet

- Antennas and Microwave Engineering LaboratoryDocument190 pagesAntennas and Microwave Engineering LaboratorySRNo ratings yet

- Chapter 2: Mathematical Modelling of Translational Mechanical SystemDocument8 pagesChapter 2: Mathematical Modelling of Translational Mechanical SystemNoor Nadiah Mohd Azali100% (1)

- Design of CMOS OpAmp For A D/A Converter Buffer by Manraj Singh GujralDocument22 pagesDesign of CMOS OpAmp For A D/A Converter Buffer by Manraj Singh GujralManraj GujralNo ratings yet

- Optimizing The Design of A Switched-Capacitor Dynamic-Element-Matching AmplifierDocument6 pagesOptimizing The Design of A Switched-Capacitor Dynamic-Element-Matching Amplifierreza12368No ratings yet

- A High Performance CMOS Band - Gap Reference Circuit DesignDocument6 pagesA High Performance CMOS Band - Gap Reference Circuit DesignKhaja Mujeebuddin QuadryNo ratings yet

- Design Procedures for a Fully Differential Folded-Cascode CMOS Op AmpDocument4 pagesDesign Procedures for a Fully Differential Folded-Cascode CMOS Op AmpwleaderheeNo ratings yet

- Floor PlanningDocument7 pagesFloor PlanningMudit GuptaNo ratings yet

- Mikrosensorer: Handbook of Silicon Based MEMS Materials & TechnologiesDocument10 pagesMikrosensorer: Handbook of Silicon Based MEMS Materials & TechnologiesMudit GuptaNo ratings yet

- Reliability in MEMS Packaging 1Document5 pagesReliability in MEMS Packaging 1satishkumar8421No ratings yet

- Packaging IssuesDocument26 pagesPackaging IssuesMudit GuptaNo ratings yet

- MEMS AssignmentDocument2 pagesMEMS AssignmentMudit GuptaNo ratings yet

- Master SetDocument624 pagesMaster SetEr Lokesh MahorNo ratings yet

- Limits of CMOS Technology ScalingDocument5 pagesLimits of CMOS Technology ScalingIzzat MustafaNo ratings yet

- Circuit Note: Fully Isolated Conductivity Measurement Data Acquisition SystemDocument10 pagesCircuit Note: Fully Isolated Conductivity Measurement Data Acquisition Systemnguyen thuanNo ratings yet

- VEC Question Bank on CMOS VLSI DesignDocument10 pagesVEC Question Bank on CMOS VLSI Designmaheshwarivikas1982No ratings yet

- Instruction Manual: Varispeed-656Dc5Document71 pagesInstruction Manual: Varispeed-656Dc5Lee LeeNo ratings yet

- CHAPTER 1: Semiconductor Materials & PhysicsDocument25 pagesCHAPTER 1: Semiconductor Materials & PhysicsUma MaheswariNo ratings yet

- VLSI Exam Questions on Crystal Growth, Photolithography and Oxidation ProcessesDocument2 pagesVLSI Exam Questions on Crystal Growth, Photolithography and Oxidation ProcessesAnjanaNo ratings yet

- AEC Notes 1Document40 pagesAEC Notes 1Nooman ShaikhNo ratings yet

- Research Article: 9T Full Adder Design in Subthreshold RegionDocument5 pagesResearch Article: 9T Full Adder Design in Subthreshold Regiondeepa_sinha_3No ratings yet

- VN380 Smart Solenoid Driver SpecificationsDocument10 pagesVN380 Smart Solenoid Driver SpecificationsAdan Pérez EchevarríaNo ratings yet

- Mips Processor ExampleDocument40 pagesMips Processor ExampleepNo ratings yet

- Improved Effective Switching Current IEFF and Capacitance Methodology For CMOS Circuit Performance Prediction and Model-To-Hardware CorrelationDocument4 pagesImproved Effective Switching Current IEFF and Capacitance Methodology For CMOS Circuit Performance Prediction and Model-To-Hardware CorrelationLohith DharavathNo ratings yet

- 01 EE6306 - MOS Transistor TheoryDocument74 pages01 EE6306 - MOS Transistor TheoryononahjNo ratings yet

- Literature Review On Mobile Phone DetectorDocument4 pagesLiterature Review On Mobile Phone Detectorzyfepyfej0p2100% (1)

- Lab-05 Layout: "Layout of Basic Gates Using 0.25 Micron Technology in Microwind" 1. ObjectiveDocument3 pagesLab-05 Layout: "Layout of Basic Gates Using 0.25 Micron Technology in Microwind" 1. ObjectiveSheikh Abdullah Al SalmanNo ratings yet

- Chapter 10 Field Effect TransistorsDocument48 pagesChapter 10 Field Effect TransistorsanjugaduNo ratings yet

- VLC-853C3 VLC-853C3 VLC-853C3 VLC-853C3 VLC-853C3Document2 pagesVLC-853C3 VLC-853C3 VLC-853C3 VLC-853C3 VLC-853C3IREX TECHNOLOGIESNo ratings yet

- Basic Fabrication Steps and LayoutDocument35 pagesBasic Fabrication Steps and Layoutgokul viratNo ratings yet

- Adamson University College of Engineering Computer Engineering Department Microelectronics LaboratoryDocument9 pagesAdamson University College of Engineering Computer Engineering Department Microelectronics Laboratoryroxy8marie8chanNo ratings yet

- Analog and Digital Electronics (Subject Code: 17CS32) Lecturer NotesDocument59 pagesAnalog and Digital Electronics (Subject Code: 17CS32) Lecturer NotesKarthik v BhatNo ratings yet

- CD4001BC/CD4011BC Quad 2-Input NOR Buffered B Series Gate - Quad 2-Input NAND Buffered B Series GateDocument9 pagesCD4001BC/CD4011BC Quad 2-Input NOR Buffered B Series Gate - Quad 2-Input NAND Buffered B Series GateJexel GomezNo ratings yet

- Be Summer 2021Document2 pagesBe Summer 2021Sandip SolankiNo ratings yet

- M.Tech DECS R17 Course Structure & SyllabusDocument45 pagesM.Tech DECS R17 Course Structure & SyllabusVijay KumarNo ratings yet

- All Structures of DYNAMIC COMPARATOR2019 PDFDocument4 pagesAll Structures of DYNAMIC COMPARATOR2019 PDFPratibha SinghNo ratings yet

- Using 90nm Technology Node For Low Power Application: Performance Investigation of 2:1 MultiplexerDocument4 pagesUsing 90nm Technology Node For Low Power Application: Performance Investigation of 2:1 Multiplexerkanha gargNo ratings yet

- Low Noise Amplifier Design and OptimizationDocument57 pagesLow Noise Amplifier Design and OptimizationPranjal JalanNo ratings yet

- A 2.45-Ghz Near-Field Rfid System With Passive On-Chip Antenna TagsDocument8 pagesA 2.45-Ghz Near-Field Rfid System With Passive On-Chip Antenna TagsVARSHALI SHARMANo ratings yet