Professional Documents

Culture Documents

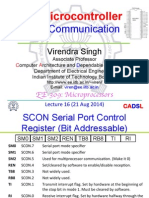

11 Serial 0515

Uploaded by

Govinda Prasad AcharyaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

11 Serial 0515

Uploaded by

Govinda Prasad AcharyaCopyright:

Available Formats

CMPE328 Microprocessors

(Spring 2007-08)

Serial Interfacing

By Dr. Mehmet Bodur

Dr.Mehmet Bodur, EMU-CMPE 2 CMPE328 Spring 2007-08

Objectives

Upon completion of this chapter, you will be able to:

List the advantages of serial communication over parallel

communication

Explain the difference between synchronous and

asynchronous communication

Define the terms simplex, half duplex, and full duplex and

diagram their implementation in serial communication

Describe how start and stop bits frame data for serial

communication

Compare the measures baud rate and bps (bits per second)

Describe the RS232 standard

Compare DTE (data terminal) versus DCE (data

communication) equipment

Describe the purpose of handshaking signals such as DTR,

RTS, and CTS

Describe the operation of a USART and use and 8251 IC

Section 17.1

Dr.Mehmet Bodur, EMU-CMPE 3 CMPE328 Spring 2007-08

Basics of Serial Communication

Microprocessors are based mostly on 8-bit

registers. Thus, their fastest I/O is 8-bit

parallel ports.

But, wiring cost of a long distance

communication is very expensive if you

carry 8-wires.

Remedy is to transfer data serially in bits

instead of in bytes or words.

Section 17.1

Dr.Mehmet Bodur, EMU-CMPE 4 CMPE328 Spring 2007-08

Simplex vs Duplex

In Simplex Mode data flow

is in one direction only.

In Half Duplex Mode data

flows in one direction, at a

given time,

A protocol and switches

connect the devices both to

receive and also to transmit.

In Full Duplex mode,

transmitted data and

received data goes

simultaneously through two

channels.

Transmitter Receiver

Transmitter

Receiver

Transmitter

Receiver

0

0

1

1

Transmitter

Receiver

Transmitter

Receiver

Section 17.1

Dr.Mehmet Bodur, EMU-CMPE 5 CMPE328 Spring 2007-08

Asynchronous vs Synchronous

How can the receiver get each data bit when it is

delivered by the transmitter?

In synchronous transmission an explicit clock

signal describes the instants of valid data.

A single data bit is sent at each clock.

Minimum three signal lines required for full duplex,

Receive-DATA,Transmit-DATA, and CLOCK.

In asynchronous transmission clock is derived

using a-priory parameters and a start bit.

Transfer rate known, internal clock starts to pulse with

the start bit, at the known transfer rate.

Ony two signal lines required for full duplex

Receive-DATAand Transmit-DATA

Section 17.1

Dr.Mehmet Bodur, EMU-CMPE 6 CMPE328 Spring 2007-08

Asynchronous Transmission

Start and Stop Bits

Start bit is required to synchronize the internal

clock of receiver.

Stop bit is required to test the clock frequency.

Only DATA is transmitted, internal clock is

generated locally.

time

Start

0

D0

1

D1

0

D2

1

D3

0

D4

0

D5

1

D6

1

D7

0

Stop

1

Internal clock starts

with thestart bit.

Bits aresampled at

therising edgeof

theinternal clock

Internal clock stops with the

stop bit. If Stop bit is not

high, it gives framing error.

bit#: 76543210

Data is 01100101b =65h. It is ASCII e

Section 17.1

TTL DATA

internal

clock

Voltagelevels are0and 5V(TTL signal)

Dr.Mehmet Bodur, EMU-CMPE 7 CMPE328 Spring 2007-08

Asynchronous

Communication System

Computers may be

connected to

eachother at COM

port or TTL signal

levels as well.

CPU

System

Bus

UART

TTL

Level Signals

Transmit

Receive

BUS

DRIVER

RS232

Level Signals

Transmit

Receive

MODEM

CPU

System

Bus

UART

TTL

Level

Signals

Transmit

Receive

BUS

DRIVER

RS232

Level

Signals

Transmit

Receive

MODEM

Phone

Telecommunication

Media

PhoneLine

COMport 1488and 1489

Section 17.1

Dr.Mehmet Bodur, EMU-CMPE 8 CMPE328 Spring 2007-08

Data Transfer Rate

Both devices shall know the data transfer

rate of the communication to synchronize

the internal clocks correctly.

Data transfer rate is measured in BAUD

Baud =bit/second number of bits TX or RX per second

(including start, stop, data, parity etc.)

kilo Baud =1000 Baud. (not 1024 Baud)

Mega Baud =1000 000 Baud

Section 17.1

Dr.Mehmet Bodur, EMU-CMPE 9 CMPE328 Spring 2007-08

Baud Rate Calculations

If each bit takes T seconds,

the baud rate is B=1/T.

Standard Baudrates are

150, 300, 600, 1200, 2400, 4800, 9600, 19200, etc.

Baudrate tolerance for a10-bit frame is 5%.

Example: T=209s B=1/T =4785 Baud

it is 4800 Baud within 5% tolerance.

time

Start

0

D0

1

D1

0

D2

1

D3

0

D4

0

D5

1

D6

1

D7

0

Stop

1

T

oneframeperiod

thetransmitted datavalueis 01100101 b=65h =e

bits 76 5 4 3 210

Dr.Mehmet Bodur, EMU-CMPE 10 CMPE328 Spring 2007-08

Packet transmission time

If a system sends a packet of 50 bytes at

1200 Baud, using 8-data, no-parity, one

stop bits, what is the transmission time of

the whole packet:

1-byte frame is 1-start +8-data +1-stop bit

=10 bits/byte.

packet is transferred by 50 x 10 bits =500 bits

on the serial communication line.

T

packet

=500 bits / 1200 Baud =0.417sec.

=417 milliseconds.

Section 17.1

Dr.Mehmet Bodur, EMU-CMPE 11 CMPE328 Spring 2007-08

RS232 Socket Pins

Recommended standard

describe two kind of sockets.

DTE: Device Terminal Equipment.

Computers, Terminals, etc.

DCE: Device Communication Equipment

Modem (modulator-demodulator).

Equipment connections:

DTE is connected to DCE

without crossing.

DTE is connected to DTE

cross-wired.

TxD2

RxD3

GND7

DTE

TxD2

RxD3

GND7

DCE

TxD2

RxD3

GND7

DTE

TxD2

RxD3

GND7

DTE

Section 17.1

Dr.Mehmet Bodur, EMU-CMPE 12 CMPE328 Spring 2007-08

Handshaking Signals

Modem-Terminal handshaking signals:

Device status signals

DTR: Data terminal ready (DTE is ok.).

DSR: Data Set ready (DCE is ok.)

Flow control signals

RTS: Request to Send (DTE sends char.)

CTS: Clear to Send (DCE accepts RTS)

Section 17.1

Dr.Mehmet Bodur, EMU-CMPE 13 CMPE328 Spring 2007-08

UART 8251

A processor may transmit/receive data in

serial format without any extra hardware.

But it costs to the processing time of the

processor.

A UART (Universal Asynchronous Receiver Transmitter) is

a hardware device that shifts out data bits

to transmit a data byte, and also shifts-in

data bits to receive a data byte.

Section 17.4

Dr.Mehmet Bodur, EMU-CMPE 14 CMPE328 Spring 2007-08

8251 UART Device

Register addressing

~CS C/~D=00 (data)

writes to the transmit buffer

reads from the receive buffer

~CS C/~D=01 (control)

writes to the

mode register right after a reset.

command register after mode is

written.

reads from the status register.

Section 17.4

D[0..7]

TXRDY

TXE

~TXC

TXD

RXD

RXRDY

~RXC

SY/BR

~DSR

~DTR

~CTS

~RTS

RESET

CLK

C/~D

~RD

~WR

~CS

8251 USART

Dr.Mehmet Bodur, EMU-CMPE 15 CMPE328 Spring 2007-08

8251 system bus connection

Data buffer

address is 308h

Control/Status

address is 309h,

TXRDY and

RXRDY are for

interrupted

operation.

D[0..7]

TXRDY

TXE

~TXC

TXD

RXD

RXRDY

~RXC

SY/BR

~DSR

~DTR

~CTS

~RTS

RESET

CLK

C/~D

~RD

~WR

~CS

8251 USART

Address

Decoder ~308h ~309h

A0

~IOR

~IOW

RESET

CLK

D[0..7]

serial

data

modem

handshaking

Receive

Clock

Clock

Generator

Transmit

Clock

Section 17.4

Dr.Mehmet Bodur, EMU-CMPE 16 CMPE328 Spring 2007-08

8251 Clock Signals

CLK is system clock input

TXC and RXC are transmit-receive

clock inputs.

There are three baudrate factors

divide by 1, 16 and 64.

Example. Find RXC oscillator frequency

for 1200 Baud operation with baudrate

factor 1/64.

Solution: f

RXC

=1200*64 Hz =76.8 kHz.

Example: What shall be the baudrate

factor for 4800 Baud operation if RXC is

connected to 19.2 kHz ?

Solution: 19.2kHz/4.8kHz =4, 1/4

D[0..7]

TXRDY

TXE

~TXC

TXD

RXD

RXRDY

~RXC

SY/BR

~DSR

~DTR

~CTS

~RTS

RESET

CLK

C/~D

~RD

~WR

~CS

8251 USART

Section 17.4

Dr.Mehmet Bodur, EMU-CMPE 17 CMPE328 Spring 2007-08

8251 Reset Sequence

8251 reset sequence is

write three successive zeros to control address to

assure writing a reset to the command register.

write command 40h to reset (reset chip)

After the reset, 8251 expects mode settings.

write the mode settings to control address

There after 8251 needs command settings.

write command for command settings.

Now the device is ready for transmit and receive

operations

Section 17.4

Dr.Mehmet Bodur, EMU-CMPE 18 CMPE328 Spring 2007-08

8251 mode/control settings

and status bits 8251 USART

Mode Register format for asynchronous mode:

b7 b6 ={S2S1: nr.of stop bits 00: invalid / 01:1stop / 10: 1.5stop / 11: 2stop },

b5 ={EP: parity type 0: odd / 1: even },

b4 ={PEN: parity enable 0: no-parity-bits / 1: parity-bits-present },

b3 b2 ={L2L1: nr.of data bits 00: 5-bit / 01: 6-bit / 10: 7-bit / 11: 8-bit },

b1 b0 ={B2B1: baud rate factor 00: sync-mode / 01: /1 / 10: /16 / 11: /64 }

Control Register format for asynchronous mode:

b7 ={EH: Enter hunt mode to search sync char 1: enable / 0: disable }

b6 ={IR: Internal reset 1: resets the 8251A }

b5 ={RTS: Request to send, 1: RTS-output-forced-to-low }

b4 ={ER: Error Reset 1: reset error flags PE,OE,FE }

b3 ={SBRK: Send break char 1: forces TxDlow }

b2 ={RxE: Receiver enable 1: enable, 0: disable }

b1 ={DTR: Data terminal ready 1: DTR-output-forced-to-low }

b0 ={TxE: Transmitter enable 1: enable, 0: disable }

Status Register format for asynchronous mode:

b7 ={DSR 1: DSR pin is active (low)}

b6 ={SY/BD 1: sync-or-break char detected}

b5 ={FE 1: Framing error occurs}

b4 ={OE 1: Overrun error occurs}

b3 ={PE 1: Parity error occurs}

b2 ={TxE 1: Tx finished transmitting all data}

b1 ={RxRDY 1: Data-in buffer is full}

b0 ={TxRDY 1: Data-out buffer is empty}

Section 17.4

Dr.Mehmet Bodur, EMU-CMPE 19 CMPE328 Spring 2007-08

8251 initialization

For the circuit

with ports 308h,

309h enabling

8251, write a

code

a) to initialize it for

1200 baud when

TXC connected to

19.2kHz, to

transmit

characters to a

DCE with 8-bit

data, no parity,

one stop bit

configuration.

b) to read port

300h, and

transmit the value

in serial format

Mode Register

b7b6 ={S2S1: nr.ofstop bits 00: inval./ 01:1stop / 10: 1.5stop / 11: 2stop },

b5 ={EP: parity type0: odd / 1: even },

b4 ={PEN: parity enable 0: no-parity-bits / 1: parity-bits-present },

b3b2 ={L2L1: nr.ofdatabits 00: 5-bit / 01: 6-bit / 10: 7-bit / 11: 8-bit },

b1b0 ={B2B1: baud ratefactor 00: sync-mode/ 01: 1 / 10: 16 / 11: 64}

Control Register

b7 ={EH: Enter hunt modeto search sync char 1: enable/ 0: disable}

b6 ={IR: Internal reset 1: resets the8251A }

b5 ={RTS: Request to send, 1: RTS-output-forced-to-low}

b4 ={ER: Error Reset 1: reset error flags PE,OE,FE }

b3 ={SBRK: Send break char 1: forces TxDlow}

b2 ={RxE: Receiver enable 1: enable, 0: disable}

b1 ={DTR: Dataterminal ready 1: DTR-output-forced-to-low}

b0 ={TxE: Transmitter enable 1: enable, 0: disable}

Mode register shall be 01001110b =4Eh

Control register shall be 00110011b =33h

receiver is disabled.

only transmitter enabled.

handshaking

to modemis

enabled.

Section 17.4

Dr.Mehmet Bodur, EMU-CMPE 20 CMPE328 Spring 2007-08

8251 coding

For the circuit with ports

308h, 309h enabling

8251, write a code

a) to initialize it for 1200

baud when TXC

connected to 19.2kHz, to

transmit characters to a

DCE with 8-bit data, no

parity, one stop bit

configuration.

b) to read port 300h, and

transmit the value in

serial format

.model small

.code

; reset 8251

movdx,309h

moval,0

out dx,al

out dx,al

out dx,al

moval,40h

out dx,al

; set mode

moval, 4Eh

out dx,al

; set command

moval, 33h

out dx,al

mainloop

.

; read the port

movdx,300h

in al,dx

movah,al ; save it

; send the char,

; wait if buffer is full

movdx,309h

wdataout:

in al,dx; status byte

and al,01h

jzwdataout

; nowsend character

moval,ah

movdx,308h

out dx,al

; continue looping

jmpmainloop

end

StatusRegister format for asynchronous mode:

b7 = {DSR 1: DSR pin is active (low)}

b6 = {SY/BD 1: sync-or-break char detected}

b5 = {FE 1: Framing error occurs}

b4 = {OE 1: Overrun error occurs}

b3 = {PE 1: Parity error occurs}

b2 = {TxE 1: Txfinished transmitting all data}

b1 = {RxRDY 1: Data-in buffer is full}

b0 = {TxRDY 1: Data-out buffer is empty}

Dr.Mehmet Bodur, EMU-CMPE 21 CMPE328 Spring 2007-08

Exercise

Solve the following two Final Exam

questions.

Final Fall 06

Final Fall 07

You might also like

- 8051 2 Rs 232 InterfacingDocument45 pages8051 2 Rs 232 InterfacingPavankumar KalliNo ratings yet

- Modbus RTU VLT Micro DriveDocument17 pagesModbus RTU VLT Micro DriveIvan Cordero ValerianoNo ratings yet

- 8051 Microcontroller Serial Communication: Doubling the Baud RateDocument15 pages8051 Microcontroller Serial Communication: Doubling the Baud RateRohan JainNo ratings yet

- 8051 Serial Port Programming GuideDocument110 pages8051 Serial Port Programming GuideshivaspyNo ratings yet

- 8051 Serial Communication ProgrammingDocument93 pages8051 Serial Communication ProgrammingjaigodaraNo ratings yet

- PCF8582C-2: 1. DescriptionDocument21 pagesPCF8582C-2: 1. DescriptionroozbehxoxNo ratings yet

- Lithium-Ion Battery ChargerDocument10 pagesLithium-Ion Battery ChargerMohsen MollaaliNo ratings yet

- Serial Data Transmission Vs Parallel Data Transmission: Unit 5Document16 pagesSerial Data Transmission Vs Parallel Data Transmission: Unit 5achuu1987No ratings yet

- DPX 1Document12 pagesDPX 1anon_624220363No ratings yet

- Microcontroller Basics and ProgrammingDocument92 pagesMicrocontroller Basics and ProgrammingVishal Gudla NagrajNo ratings yet

- Mpmcnotesunit IIIDocument34 pagesMpmcnotesunit IIIAmy OliverNo ratings yet

- PLC-VFD Communications for RS-485 RTU NetworksDocument5 pagesPLC-VFD Communications for RS-485 RTU NetworksdaocongdablNo ratings yet

- Serial Communication Using AVR Lab 8 PDFDocument5 pagesSerial Communication Using AVR Lab 8 PDFlovelyosmile253100% (1)

- Lecture 08Document12 pagesLecture 08MuhammadHafizhNo ratings yet

- 8255Document34 pages8255Manjula Bn100% (1)

- Mastering The PIC16C7X A/D ConverterDocument8 pagesMastering The PIC16C7X A/D ConverterGuillermo Hernandez100% (1)

- Abstract 2. Circuit Diagram 3. Explanation 4. Working 5. Program Code 6. PCB Layout Fabrication and Assembly 8. Conclusion 9. Reference 10. DatasheetDocument22 pagesAbstract 2. Circuit Diagram 3. Explanation 4. Working 5. Program Code 6. PCB Layout Fabrication and Assembly 8. Conclusion 9. Reference 10. Datasheetaditya_pundirNo ratings yet

- 8051 CH10Document93 pages8051 CH10Murali KrishnaNo ratings yet

- Analog To Digital Converter: Vitrax Plus ControllerDocument13 pagesAnalog To Digital Converter: Vitrax Plus Controlleries837No ratings yet

- Lab Serial Communication 8051Document3 pagesLab Serial Communication 8051khawar iqbalNo ratings yet

- Modbus RTU Quick GuideDocument8 pagesModbus RTU Quick Guidehernangyc100% (1)

- Z3 2 4Document104 pagesZ3 2 4Vu Duc Hoan100% (1)

- ST24 25C04, ST24 25W04Document16 pagesST24 25C04, ST24 25W04Zoran KovacevicNo ratings yet

- MODBUS & BACNET protocols guide for ElNET power metersDocument81 pagesMODBUS & BACNET protocols guide for ElNET power metersTomas Fazzio100% (1)

- Programmable Peripheral Interface 8255: Microprocessor Unit 4 1Document32 pagesProgrammable Peripheral Interface 8255: Microprocessor Unit 4 1veeramaniks408No ratings yet

- Data Communication and Networking (Lab Manual)Document62 pagesData Communication and Networking (Lab Manual)Abhishek Pattanaik100% (1)

- 8282,8286,8284Document23 pages8282,8286,8284Relan Soniia100% (1)

- SPI & DPI Commands Slave Mode Notes: MV SetpointsDocument4 pagesSPI & DPI Commands Slave Mode Notes: MV SetpointsArun KumarNo ratings yet

- Unit 6 2Document25 pagesUnit 6 2Venkatesh RachaNo ratings yet

- Power Quality MeterDocument12 pagesPower Quality MeterSarmadRSNo ratings yet

- Data Sheet: 2048 8-Bit CMOS EEPROM With I C-Bus InterfaceDocument21 pagesData Sheet: 2048 8-Bit CMOS EEPROM With I C-Bus InterfacejuniormalitNo ratings yet

- Infrared Data Transmission With The PIC Microcontroller: Matthew Beckler Beck0778@umn - Edu EE2361 Lab 007 May 5, 2006Document8 pagesInfrared Data Transmission With The PIC Microcontroller: Matthew Beckler Beck0778@umn - Edu EE2361 Lab 007 May 5, 2006anujchopra007No ratings yet

- AD9850 DDS Signal Generator Module GuideDocument4 pagesAD9850 DDS Signal Generator Module GuideJesus HuitronNo ratings yet

- Microprocessor & Microcontrollers: Serial CommunicationDocument36 pagesMicroprocessor & Microcontrollers: Serial CommunicationAbdul Rehman AfzalNo ratings yet

- NEC 022 External Paper SolutionDocument13 pagesNEC 022 External Paper SolutionSachin PalNo ratings yet

- Bluetooth RS232 Serial Adapter Manual Document Version: 1.3 Firmware Version: 6.5xDocument23 pagesBluetooth RS232 Serial Adapter Manual Document Version: 1.3 Firmware Version: 6.5xMauricio Palacios BazaNo ratings yet

- ADC Data Acquisition and AnalysisDocument8 pagesADC Data Acquisition and AnalysisAnonymous kT0ONWNo ratings yet

- Design and Implementation of UART Based On VerilogDocument7 pagesDesign and Implementation of UART Based On VeriloglabibatariqueNo ratings yet

- M 3425a Beco2200 ModbusDocument103 pagesM 3425a Beco2200 ModbusNurdin MubarokNo ratings yet

- 2CSG445012D0201 - Modbus Communication Protocol - M2M BasicDocument13 pages2CSG445012D0201 - Modbus Communication Protocol - M2M BasicJoako FilipovichNo ratings yet

- 5.serial Communication - 1Document28 pages5.serial Communication - 1Dr-Samson ChepuriNo ratings yet

- TRISC 0 // Set Direction To Be Output 0 Output 1 InputDocument7 pagesTRISC 0 // Set Direction To Be Output 0 Output 1 Inputiri_scribdNo ratings yet

- ECE 2211 Microprocessor and Interfacing Chapter 8 Comparison of 8088 and 8086 Memory InterfacesDocument37 pagesECE 2211 Microprocessor and Interfacing Chapter 8 Comparison of 8088 and 8086 Memory InterfacesZahid Ali ArainNo ratings yet

- Peripheral Interfacing + Coding: Lets Learn How To Do It in 8051 !!Document44 pagesPeripheral Interfacing + Coding: Lets Learn How To Do It in 8051 !!malhiavtarsinghNo ratings yet

- Intelligent Water Control System Using 8051 (AT89C51) : Project ReportDocument12 pagesIntelligent Water Control System Using 8051 (AT89C51) : Project ReportNadeem AnjumNo ratings yet

- Chapter 13 - EUARTDocument33 pagesChapter 13 - EUARTPhương NguyễnNo ratings yet

- CAN Bus in PSoC Report210Document16 pagesCAN Bus in PSoC Report210Marcos Antonio EstremoteNo ratings yet

- Serial Communication With 8051Document25 pagesSerial Communication With 8051prakriti sankhlaNo ratings yet

- How to Get a Second Asynchronous Interface on a 80C51 MicrocontrollerDocument8 pagesHow to Get a Second Asynchronous Interface on a 80C51 Microcontrollerscribduser100% (1)

- PIM-PB-01 - Profibus Interface: 1. InstallationDocument10 pagesPIM-PB-01 - Profibus Interface: 1. InstallationweiyaNo ratings yet

- Sle4418, Sle4428Document17 pagesSle4418, Sle4428Badrulshahputra BashaNo ratings yet

- Spot ProtocolDocument12 pagesSpot Protocolj_pozo_c209No ratings yet

- Elnet CommDocument82 pagesElnet CommNicolas A. RomanNo ratings yet

- USB Bus Interface Chip CH375Document18 pagesUSB Bus Interface Chip CH375Mario Esteban100% (1)

- AVR J1850 VPW Interface DocumentationDocument15 pagesAVR J1850 VPW Interface DocumentationAjish AlfredNo ratings yet

- Protocolo I2CDocument12 pagesProtocolo I2Cディエゴ水上100% (2)

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Digital Signal Processing: Instant AccessFrom EverandDigital Signal Processing: Instant AccessRating: 3.5 out of 5 stars3.5/5 (2)

- From GSM to LTE-Advanced Pro and 5G: An Introduction to Mobile Networks and Mobile BroadbandFrom EverandFrom GSM to LTE-Advanced Pro and 5G: An Introduction to Mobile Networks and Mobile BroadbandNo ratings yet

- IEEE Author Ethics GuidelinesDocument1 pageIEEE Author Ethics GuidelinesTole SutiknoNo ratings yet

- LDICA ApplicationsDocument4 pagesLDICA ApplicationsGovinda Prasad AcharyaNo ratings yet

- Graphical Abstract InstructionsDocument1 pageGraphical Abstract InstructionsGovinda Prasad AcharyaNo ratings yet

- Fault Clustering Technique For 3D Memory BISR: Tianjian Li, Yan Han, Xiaoyao Liang, Hsien-Hsin S. Lee and Li JiangDocument6 pagesFault Clustering Technique For 3D Memory BISR: Tianjian Li, Yan Han, Xiaoyao Liang, Hsien-Hsin S. Lee and Li JiangGovinda Prasad AcharyaNo ratings yet

- Centronics and Ieee 488 (Parallel Interfaces)Document139 pagesCentronics and Ieee 488 (Parallel Interfaces)Govinda Prasad Acharya100% (1)

- Cadence ManualDocument51 pagesCadence Manualapi-27099960100% (4)

- Fault Clustering Technique For 3D Memory BISR: Tianjian Li, Yan Han, Xiaoyao Liang, Hsien-Hsin S. Lee and Li JiangDocument6 pagesFault Clustering Technique For 3D Memory BISR: Tianjian Li, Yan Han, Xiaoyao Liang, Hsien-Hsin S. Lee and Li JiangGovinda Prasad AcharyaNo ratings yet

- A Novel Built-In Self-Repair Scheme For 3D MemoryDocument8 pagesA Novel Built-In Self-Repair Scheme For 3D MemoryGovinda Prasad AcharyaNo ratings yet

- Cabinet - Secretariat.lower .Division - Clerk .Recruitment.2014Document5 pagesCabinet - Secretariat.lower .Division - Clerk .Recruitment.2014g24uallNo ratings yet

- Scaling, Power, and The Future of CMOSDocument7 pagesScaling, Power, and The Future of CMOSGovinda Prasad AcharyaNo ratings yet

- Quality Control Quality ControlDocument44 pagesQuality Control Quality ControlMuza SheruNo ratings yet

- Eula Microsoft Visual StudioDocument3 pagesEula Microsoft Visual StudioqwwerttyyNo ratings yet

- 438 Final Exam F13Document4 pages438 Final Exam F13Kathan ShuklaNo ratings yet

- Embedded Systems For ECEDocument92 pagesEmbedded Systems For ECESurudhi AsokrajNo ratings yet

- Ds30 Loader - Firmware ManualDocument20 pagesDs30 Loader - Firmware ManualSamPolancos100% (1)

- Merlin-V3.6.1 Customer Release Notes - 83-000091-01!01!07Document10 pagesMerlin-V3.6.1 Customer Release Notes - 83-000091-01!01!07FranciscoXavierGonzalezMenaNo ratings yet

- ABB REM Relay Unit Software Manual CAP 505Document102 pagesABB REM Relay Unit Software Manual CAP 505mitch1973100% (1)

- Maharishi University of Information Technology LUCKNOW (UP) - 226013Document77 pagesMaharishi University of Information Technology LUCKNOW (UP) - 226013Suraj DubeyNo ratings yet

- CC Unit 1 NotesDocument5 pagesCC Unit 1 NotesArif KhanNo ratings yet

- Network Engineer Nomanejaz Seeks New OpportunityDocument1 pageNetwork Engineer Nomanejaz Seeks New OpportunityNoman EjazNo ratings yet

- MiraScreen 5G V1.20Document10 pagesMiraScreen 5G V1.20Irfandi Al WhbNo ratings yet

- Chapter 2: Database Environment TransparenciesDocument38 pagesChapter 2: Database Environment TransparenciesRifat_mmuNo ratings yet

- Guia Configuracion 9500MPR MSS4 MSS8 Orange PDFDocument15 pagesGuia Configuracion 9500MPR MSS4 MSS8 Orange PDFalcides quijadaNo ratings yet

- Pre Emphasis de EmphasisDocument2 pagesPre Emphasis de EmphasisgodierobertNo ratings yet

- IBM DataPower Operations Dashboard Provides Real-Time VisibilityDocument8 pagesIBM DataPower Operations Dashboard Provides Real-Time VisibilityRohit ChaubeyNo ratings yet

- 03 Delta Controls - PPT PDFDocument73 pages03 Delta Controls - PPT PDFsureshkanuboyinaNo ratings yet

- Instruction Manual: HD/SD 12-Channel Digital Video SwitcherDocument73 pagesInstruction Manual: HD/SD 12-Channel Digital Video SwitcherOscar Alberto Carcassés BorgesNo ratings yet

- AWS T&C Cert AllUp Ebook FINAL PDFDocument48 pagesAWS T&C Cert AllUp Ebook FINAL PDFPrabhugurudarshan SinghNo ratings yet

- Digital Audio Technology WordclockDocument2 pagesDigital Audio Technology WordclockSusana BrochadoNo ratings yet

- Scan ClasaDocument27 pagesScan ClasaMarius BleauNo ratings yet

- MCQ - MPMCDocument9 pagesMCQ - MPMCRanganayaki RamkumarNo ratings yet

- 68 HC11 ManualDocument36 pages68 HC11 ManualГеорги МончевNo ratings yet

- Venkataraman RDocument2 pagesVenkataraman RVenkat RamanNo ratings yet

- Sending and Receiving Data Via Bluetooth With Android DeviceDocument7 pagesSending and Receiving Data Via Bluetooth With Android DeviceManuel Gómez EnríquezNo ratings yet

- Collaborative Whiteboard Using RMI: I I of T, KDocument11 pagesCollaborative Whiteboard Using RMI: I I of T, Kmadhusudan chunletiaNo ratings yet

- T3TAFJ-T24 and TAFJ Upgrade-R16Document21 pagesT3TAFJ-T24 and TAFJ Upgrade-R16adyani_0997No ratings yet

- m160 PDFDocument836 pagesm160 PDFMery Helen Barraza Delgado100% (1)

- Step by Step Guide To Become Big Data DeveloperDocument15 pagesStep by Step Guide To Become Big Data DeveloperSaggam Bharath75% (4)

- Log Cat 1660442629854Document154 pagesLog Cat 1660442629854穆楓No ratings yet

- Veeam On Nutanix With Hyper-V BPDocument24 pagesVeeam On Nutanix With Hyper-V BPqabbasNo ratings yet

- Https Support - Honeywellaidc.com S Article Best-Practices-On-tDocument3 pagesHttps Support - Honeywellaidc.com S Article Best-Practices-On-tcocibolca61No ratings yet

- IEC 61850 Standard ExplainedDocument4 pagesIEC 61850 Standard ExplainedbansalrNo ratings yet