Professional Documents

Culture Documents

Frequency Measurement Using FLL

Uploaded by

phieuxuatkhoCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Frequency Measurement Using FLL

Uploaded by

phieuxuatkhoCopyright:

Available Formats

Frequency Measurement using a Frequency Locked

Loop

Zijun Luo, Mary Kaye, Chris Diduch and Liuchen Chang

Department of Electrical and Computer Engineering

University of New Brunswick

Fredericton, Canada

AbstractA phase locked loop method is proposed for fast

estimation of utility grid frequency, for control and protection

purposes in grid-connected power converters. Using a second order

generalized integrator (SOGI) and a novel frequency locked loop

(nFLL), which makes the SOGI frequency adaptive, the proposed

SOGI-nFLL detects small and large step changes in frequency with

fast response and without large overshoot. In this paper, the SOGI-

nFLL method is analyzed, simulated and implemented in a Field

Programmable Gate Array (FPGA). Its performance is compared

with the original SOGI-FLL using simulations and experimental

data. The experimental results verify that the proposed method

results in smoother transients for frequency detection that may be

used to reliably activate over-frequency protection within a half

cycle.

I. INTRODUCTION

In distributed generation (DG) systems the phase locked

loop (PLL) method has been frequently used for phase,

magnitude and frequency detection of sinusoidal voltages

for the purpose of grid synchronization, control and

protection. However, existing single-phase PLL strategies

are unsatisfactory for frequency estimation when the input

frequency has small step changes. Most existing single-

phase PLL methods tend to focus on phase and magnitude

detection under harmonics or distorted conditions. Of the

few PLL approaches aimed at frequency tracking, these tend

to generate excessive overshoot for small step changes in

frequency. Such transients may trigger under-frequency or

over-frequency faults in a distributed generation system. In

practical applications, the grid frequency varies within a

small range, typically _0.2Hz. According to the IEEE 1547

standard, it is recommended that a DG must not

unnecessarily disconnect due to small frequency variations

[1]. As a result, the existing PLL based methods fail to

satisfy the IEEE 1547 standard.

To feed high quality electricity to the utility grid, grid-

connected inverters require precise and real-time grid phase

and frequency information for system control with

robustness and reliability. Rapid frequency detection is also

needed for the under-frequency, over-frequency and anti-

islanding protection to ensure DG integrity and timely

activation of protection schemes. When the inverters of

distributed generators connected to the utility grid use poor

measurements of frequency and phase, voltage unbalance,

line dip, harmonics, phase loss, and frequency deviation will

occur.

Among the PLL techniques, a second order generalized

integrator (SOGI) with frequency locked loop (FLL) is a

meaningful option. A number of different SOGI structures

are proposed in [2]-[5]. For instance, M. Ciobotaru et al [2]

combined the SOGI and the synchronous reference frame

(SRF) to extract phase and frequency information. Since the

SOGI is resonant with the fundamental frequency, it is

capable of duplicating the sinusoidal wave and filtering out

the harmonics and noise without a time delay. M. Ciobotaru

et al [3] provided a voltage offset rejection method to

improve the performance of the SOGI method [2]. With a PI

controller in SRF, the frequency estimation experiences

oscillation. By adjusting the PI parameters, the transients

can be reduced at the cost of a longer settling time. Another

method named SOGI-FLL was presented by P. Rodriguez et

al [5]. It replaces the SRF with a FLL for frequency

detection. The SOGI-FLL method provides fast and accurate

tracking of frequency even under harmonic, distortion,

phase jump, and frequency jump conditions. However, small

step variations in frequency of the order of 0.2Hz result in

large overshoot which leads to false detection of an over-

frequency fault.

In an attempt to eliminate the drawbacks in existing

PLLs, this paper develops a PLL based method for fast and

accurate frequency detection without large overshoot for

small step variations in frequency. The paper is organized as

follows. The principles of SOGI are described in Section 2,

the idea of the proposed novel FLL (nFLL) is explained in

Section 3, and simulation results are shown in Section 4,

followed by the hardware implementation, experimental

results and conclusion in Section 5, Section 6 and Section 7

respectively.

II. SECOND ORDER GRENERALIZED

INTEGRATOR

The second order generalized integrator (SOGI) for

sinusoidal signals, which was proposed in [2], was derived

from a generalized integrator (GI) and is represented by the

block diagram of Fig. 1. The transfer function is given by

(1).

The research has been supported by Atlantic Innovation Fund (AIF)

and Natural Sciences and Research Council (NSERC) of Canada.

978-1-4577-0541-0/11/$26.00 2011 IEEE 917

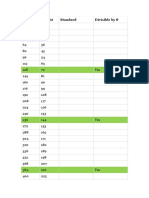

Figure 3. Frequency detection by the original SOGI-FLL

0 0.1 0.2 0.3 0.4 0.5 0.

59

60

61

62

63

64

Input Frequency

(a)

F

r

e

q

u

e

n

c

y

(

H

z

)

0 0.1 0.2 0.3 0.4 0.5 0.

50

53

56

59

62

65

Estimated Frequency

Time (s)

(b)

F

r

e

q

u

e

n

c

y

(

H

z

)

Figure 2. The proposed SOGI-nFLL method Figure 1. The SOGI-FLL method

S00I(s) =

i

s

s

2

+

i

2

(1)

According to the internal model principle, when the

resonant frequency

is constant and identical to the input

frequency , the SOGI output, :

i

, tracks the input sinewave

with zero steady state error. In steady state, the SOGI also

generates the quadrature phase signal, q:

i

.

Furthermore, the output signals :

i

and q:

i

are

characterized by the following transfer functions [2].

I(s) =

:

i

:

(s) =

k

i

s

s

2

+ k

i

s +

i

2

(2)

(s) =

q:

:

(s) =

k

2

s

2

+ k

s +

2

(3)

The Bode plot for (2) and (3) infers them acting as a

band-pass filter and low-pass filter, whose bandwidth is

governed by the gain k [2].

III. PROPOSED FREQUENCY LOCKED LOOP

To adapt the center frequency,

i

, a frequency locked

loop (FLL) was proposed in [4]. If

i

, is constant then the

transfer function relating the error signal, e

, to v is given by

E(s) =

e

:

(s) =

s

2

+

2

s

2

+k

s +

2

(4)

Due to the infinite gain between the SOGI output :

and

the error e

at the resonant frequency

, the steady-state

error is zero. However, the infinite gain makes the system

very sensitive to small frequency deviations, tending to

produce large overshoots that may result in false activation

of under and over-frequency protection [6]. In the FLL, the

error in frequency, e

]

= e

q:

i

, is used to adjust the

estimated frequency,

, by the update law, = k

e

]

.

In the proposed SOGI-nFLL a nonlinear gain, K

g

, is

cascaded with the error e

]

. The gain is chosen to transform

the error, e

]

, so as to compress its dynamic range. To

simplify and save computation resources for hardware

implementation, the arctangent function was chosen. The

transformed error in frequency is cascaded with a linear gain,

K

a

, which is used to accelerate and shape the frequency

tracking response. The structure of the proposed second

order generalized integrator - novel frequency locked loop

(SOGI-nFLL) is shown in Fig. 2.

IV. SIMULATION RESULTS

The system input is given as a sinusoidal voltage v =

S4usin2nt. As shown in Fig. 3(a), the input frequency, f,

steps from 60Hz to 60.2Hz at 0.2s resulting in an overshoot

up to approximately 63Hz with the original SOGI-FLL

method as shown in Fig. 3(b). The excessive overshoot at

0.2s leads to a false activation of the over-frequency

protection. In comparison, the results in Fig. 4(b) as obtained

with the proposed PLL method show a much smoother

frequency estimation with settling time of 0.024s and an

overshoot of 0.24Hz which will not cause false over and

under-frequency alarms. When it encounters a large

frequency jump at 0.32s, the SOGI-nFLL reaches the

protection threshold of 60.5Hz within 0.0363s. Fig. 5(b)

shows that e

]

is orders of magnitude smaller than that of the

existing method in Fig. 5(a). Therefore, the proposed PLL

method eliminates the overshoot without loss of accuracy for

small frequency changes, and for large frequency jumps it

can activate the over-frequency protection in less than three

cycles, leading to a fast activation of frequency protection.

918

Figure 5. Error in Frequency Comparison

0 0.1 0.2 0.3 0.4 0.5 0.6

-2

-1.2

-0.4

0.4

1.2

2

x 10

4

Error in Frequency from the existing SOGI-FLL

(a)

0 0.1 0.2 0.3 0.4 0.5 0.6

-2

-1.2

-0.4

0.4

1.2

2

Error in Frequency from the proposed SOGI-nFLL

Time (s)

(b)

Figure 4. Frequency detection by the proposed SOGI-nFLL

0 0.1 0.2 0.3 0.4 0.5 0.6

59

60

61

62

63

64

Input Frequency

(a)

F

r

e

q

u

e

n

c

y

(

H

z

)

0 0.1 0.2 0.3 0.4 0.5 0.6

59

60

61

62

63

64

Estimated Frequency

Time (s)

(b)

F

r

e

q

u

e

n

c

y

(

H

z

)

Figure 6. The S0uI-nFLL FPuA Besign in SIN0LINK

V. HARDWARE IMPLEMENTATION

An FPGA realization was considered because such a

platform facilitates rapid prototyping and system-on-chip

design that augments high speed protection schemes with

the measurements provided by nFLL-SOGI. To convert the

design from the analog domain to the digital domain, the

integration operation was transformed using the Euler

backward difference operation, s =

1-z

-1

1

s

[7], where I

s

is

the sampling period. The Xilinx System Generator tool was

used in MATLAB to model, simulate, and implement the

design. A SIMULINK model appears in Fig. 6. Xilinx

System Generator creates a high-level specification using

standard SIMULINK Blocksets for system modeling, and

then generates the hardware description language (HDL)

code for realization.

There are additional design considerations in translating

the design from the s-domain into the z-domain. Firstly, the

z-domain specification is of fixed-point precision compared

to the double floating point precision in the s-domain. The

selection of the word-length, binary point and rounding are

governed by the finite logic resources in the FPGA [8].

Generally, more accurate performance requires the longer

word-length which means higher hardware-cost. Proper

scaling is also needed to avoid overflow. In the SOGI-nFLL

method the precise value of the sampling time, I

s

, affects

frequency tracking performance. So there is a tradeoff

between performance and resources. Secondly, by default,

the Xilinx blocksets for modeling the proposed method are

driven by the global clock which is 50MHz in the Xilinx

Spartan 3E FPGA. The sampling rate of the input signal is

determined by the analog to digital converter (ADC) and is

selected as 2MHz. So crossing two different clock domains

919

Figure 7. Frequency detection by Xilinx Blocksets

0 0.1 0.2 0.3 0.4 0.5 0.6

59

60

61

62

63

64

Input Frequency

(a)

F

r

e

q

u

e

n

c

y

(

H

z

)

0 0.1 0.2 0.3 0.4 0.5 0.6

59

60

61

62

63

64

Estimated Frequency

Time (s)

(b)

F

r

e

q

u

e

n

c

y

(

H

z

)

requires a data buffer such as an asynchronous FIFO (First

In First Out) or a handshaking signaling method. Since it

takes more than 20ns to execute the algorithm because of

the large number of logic blocks required, the SOGI-nFLL

blocksets were driven by the 2MHz clock to match the input

signals. The operation of the SOGI-nFLL is verified using

the pre-synthesis SIMULINK model, and appears in Fig. 7.

For the sake of observation, Fig. 8 is the zoomed in version

at 0.2s. It is proved that the proposed method presented in

Fig. 8(b) provides faster and more precise frequency

tracking than the SOGI-FLL method as shown in Fig. 8(a).

The FPGA design is then translated into a Verilog HDL

characterization by Xilinx System Generator, and then

synthesized and implemented by the Xilinx ISE software.

VI. EXPERIMENTAL RESULTS

The proposed PLL method has been successfully

implemented and verified on the Xilinx Spartan 3E

XC3S500E FPGA (500,000 logic gates). The step changes

in frequency were generated by an Agilent 33120A arbitrary

waveform generator, and then sampled by a 12-bit 2MHz

ADS7883 ADC from Texas Instrument. Table I compares

the resources consumed in the FPGA by the SOGI-nFLL

and SOGI-FLL methods. The SOGI-nFLL consumes less

than 10% more slices and LUTs compared to the SOGI-FLL

method.

TABLE II. DEVICE UTILIZATION SUMMARY

SOGI-nFLL SOGI-FLL

Logic Utilization Used/ Available Used /Available

Number of Slice Flip Flop 995/9,312 166/9,312

Number of 4 input LUTs 3,893/9,312 3084/9,312

Number of

MULT18X18SIO

17/20 17/20

To compare the performance in the test bed, a 0.2Hz

step change in frequency was generated at 0s, as shown in

Fig. 9. It is observed that the original SOGI method takes

0.066s to settle while the proposed SOGI-nFLL method

only takes 0.033s. Also, compared with the fluctuation of

_u.u7Bz in Fig. 9(a), the results from the proposed method

fluctuate between _u.uSBz as shown in Fig. 9(b).

In terms of the large frequency jump, Fig.10 presents the

frequency tracking performance for the SOGI-nFLL method

when the input frequency steps from 60Hz to 63Hz. Fig.

10(a) shows it takes 0.003s to reach the over-frequency

threshold (60.5Hz), and 0.12s to reach the steady state for

the original method which is more than seven cycles. Fig.

10(b) shows it takes 0.006s to reach the over-frequency

threshold, which is less than a half cycle, and 0.1s to settle

down which is six cycles.

Due to the slow sampling rate of the embedded ADC on

the Spartan 3E development board, an external 2MHz

ADS7883 ADC was used instead. The benefit of a fast

external ADC is faster and finer frequency detection. But

the drawback is a certain amount of noise contained in the

input signal. Because the original SOGI method is very

sensitive to small deviations and tends to fluctuate

dramatically in the frequency tracking, the gain k

in Fig. 1

needs to be decreased to get a stable estimation in the

experiments. Without adjusting the gain k

, the frequency

Figure 8. Zoomed in at 0.2s

0.15 0.2 0.25 0.3

59.8

60

60.2

60.4

60.6

60.8

Original SOGI

(a)

F

r

e

q

u

e

n

c

y

(

H

z

)

0.15 0.2 0.25 0.3

59.8

60

60.2

60.4

60.6

60.8

Proposed SOGI-nFLL

Time (s)

(b)

F

r

e

q

u

e

n

c

y

(

H

z

)

Figure 9. Experimental results for small jump

-0.1 -0.05 0 0.05 0.1 0.15 0.2 0.25 0.3 0.35

59.9

60

60.1

60.2

60.3

Original SOGI

(a)

F

r

e

q

u

e

n

c

y

(

H

z

)

-0.1 -0.05 0 0.05 0.1 0.15 0.2 0.25 0.3 0.35

59.9

60

60.1

60.2

60.3

Proposed SOGI-nFLL

Time (s)

(b)

F

r

e

q

u

e

n

c

y

(

H

z

)

920

tracking by the SOGI method will oscillate between _1 Hz

even when there is no frequency change as shown in Fig.

11. Therefore, there is always a trade-off between fast

tracking and accuracy for the original SOGI method.

On the contrary, even when the input signal is corrupted

by digital noise, both experimental results in Fig. 9 and Fig.

10 prove that the proposed PLL method provides faster and

finer frequency detection for small and large step changes in

frequency. Hence, better frequency detection can be

captured for the grid synchronization by the proposed

method.

VII. CONCLUSION

A novel PLL method for frequency measurement is

proposed. The method is mainly for control and protection

purposes for grid-connected power converters in distributed

generation applications. Higher immunity against noise,

faster and finer frequency estimate is achieved when a

nonlinear gain is incorporated in the frequency adaptive

loop. The feasibility of the methodology is proved by the

simulated and experimental results. Taking advantage of the

Xilinx System Generator, the FPGA implementation of the

proposed SOGI-nFLL is simple and efficient.

REFERENCES

[1] IEEE, IEEE Std 1547 -standard for interconnecting distributed

resources with electric power systems, June 2003.

[2] M. Ciobotaru, R. Teodorescu and F. Blaabjerg, A new single-phase

PLL structure based on second order generalized integrator, Power

Electronics Specialists Conference, pp. 1-6, 2006.

[3] M. Ciobotaru, R. Teodorescu and V. G. Agelidis, Offset rejection for

PLL based synchronization in grid-connected converters, Applied

Power Electronics Conference and Exposition, pp. 1611-1617, 2008.

[4] P. Rodriguez, A. Luna, M. Ciobotaru, R. Teodorescu and F.

Blaabjerg, Advanced grid synchronization system for power

converters under unbalanced and distorted operating conditions, 32

nd

Annual Conference of IEEE on Industrial Electronics, pp. 5173-5178,

2006.

[5] P. Rodriguez, A. Luna, I. Etxeberria, J. R. Hermoso and R.

Teodorescu, Multiple second order generalized integrators for

harmonic synchronization of power converters, IEEE Energy

Conversion Congress and Exposition, pp. 2293-2246, 2009.

[6] R. Teodorescu, F. Blaabjerg, M. Liserre and P. C. Loh, Proportional-

resonant controllers and filters for grid-connected voltage-source

converters, Electric Power Applications, IEE Proceedings, Vol.153,

Issue 5, pp. 750-762, 2006.

[7] F. J. Rodriguez, E. Bueno, M. Aredes, L. G. B. Rolim, F. A. S. Neves

and M. C. Cavalcanti, Discrete-time implementation of second order

generalized integrators for grid converters, 34

th

Annual Conference

of IEEE, pp. 176-187, 2008.

[8] P. Martin, E. Bueno, F. J. Rodriguez and V. Saez, A methodology

for optimizing the FPGA implementation of industrial control

systems, 35

th

Annual Conference of IEEE, pp. 2811-2816, 2009.

Figure 10. Experimental results for large jump

-0.1 0 0.1 0.2 0.3 0.4

59

60

61

62

63

64

Original SOGI

(a)

F

r

e

q

u

e

n

c

y

(

H

z

)

-0.1 0 0.1 0.2 0.3 0.4

59

60

61

62

63

64

Proposed SOGI-nFLL

Time (s)

(b)

F

r

e

q

u

e

n

c

y

(

H

z

)

Figure 11. Experimental detection by the original SOGI at 60Hz

0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5

x 10

4

58.5

59

59.5

60

60.5

61

SOGI frequency tracking at 60Hz

921

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- PSCAD X4 Software Setup - Quick Start (Certificate Licensing)Document3 pagesPSCAD X4 Software Setup - Quick Start (Certificate Licensing)phieuxuatkhoNo ratings yet

- Setting Up PSCAD v4.6.3 Update 5: Release NotesDocument1 pageSetting Up PSCAD v4.6.3 Update 5: Release NotesphieuxuatkhoNo ratings yet

- 13.3 2023 ERCOT Methodologies For Determining Minimum Ancillary Service RequirementsDocument24 pages13.3 2023 ERCOT Methodologies For Determining Minimum Ancillary Service RequirementsphieuxuatkhoNo ratings yet

- Julia ProgrammingDocument115 pagesJulia ProgrammingphieuxuatkhoNo ratings yet

- How To DesignDocument6 pagesHow To DesignphieuxuatkhoNo ratings yet

- Are You Still Using Pandas For Big Data - by Roman Orac - Towards Data ScienceDocument10 pagesAre You Still Using Pandas For Big Data - by Roman Orac - Towards Data SciencephieuxuatkhoNo ratings yet

- A World-Class Research University On The Periphery: The Pohang University of Science and Technology, The Republic of KoreaDocument27 pagesA World-Class Research University On The Periphery: The Pohang University of Science and Technology, The Republic of KoreaphieuxuatkhoNo ratings yet

- A Comprehensive Computer Program For Small Signal Stability Analysis of Power SystemsDocument8 pagesA Comprehensive Computer Program For Small Signal Stability Analysis of Power SystemsphieuxuatkhoNo ratings yet

- PSCAD Resolving IssuesDocument227 pagesPSCAD Resolving IssuesphieuxuatkhoNo ratings yet

- Julia TutorialDocument75 pagesJulia TutorialphieuxuatkhoNo ratings yet

- Fast Calculation of A Voltage Stability IndexDocument11 pagesFast Calculation of A Voltage Stability IndexphieuxuatkhoNo ratings yet

- Parallel Computing With JuliaDocument87 pagesParallel Computing With JuliaphieuxuatkhoNo ratings yet

- The Nordic Test System For Voltage Stability Assessment: Thierry Van CutsemDocument28 pagesThe Nordic Test System For Voltage Stability Assessment: Thierry Van CutsemphieuxuatkhoNo ratings yet

- ZCMW 6000-1Document1 pageZCMW 6000-1phieuxuatkhoNo ratings yet

- HW1 2Document2 pagesHW1 2phieuxuatkhoNo ratings yet

- PSCAD TutorialDocument42 pagesPSCAD Tutorialchenukap100% (1)

- Irs 2184 DatasheetDocument30 pagesIrs 2184 DatasheetphieuxuatkhoNo ratings yet

- Maxwell 3D Transient: Ansoft Corporation Pittsburgh, Sept. 2001Document16 pagesMaxwell 3D Transient: Ansoft Corporation Pittsburgh, Sept. 2001phieuxuatkhoNo ratings yet

- Bi-Dirctional Acdc Converter Based On Neutral Point ClampedDocument6 pagesBi-Dirctional Acdc Converter Based On Neutral Point ClampedphieuxuatkhoNo ratings yet

- Motor Design Suite V12Document60 pagesMotor Design Suite V12Trần Trung HiếuNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Toshiba e Studio163 203 165 205 Printer Brochure PDFDocument2 pagesToshiba e Studio163 203 165 205 Printer Brochure PDFMohamed ZayedNo ratings yet

- Power System Studies For Steel Plant - Case StudyDocument5 pagesPower System Studies For Steel Plant - Case StudyGervasio SimaoNo ratings yet

- Claud D.: CationDocument3 pagesClaud D.: CationSathvik S PrabhuNo ratings yet

- Abb Ag: RTU560 / RTU211Document2 pagesAbb Ag: RTU560 / RTU211Cosmic Garash 2No ratings yet

- Robox User Manual RBX 1Document120 pagesRobox User Manual RBX 1JoezifNo ratings yet

- Ads 1298Document87 pagesAds 1298Rui AllesNo ratings yet

- 11Document25 pages11Suraj KumarNo ratings yet

- mcp3911 3.3v Two Channel Analog Front End ds20002286dDocument74 pagesmcp3911 3.3v Two Channel Analog Front End ds20002286dJosueEspinozaNo ratings yet

- Beetel Blitz - Apr 28'ver11Document32 pagesBeetel Blitz - Apr 28'ver11sums_devNo ratings yet

- PLLDP BSCDocument6 pagesPLLDP BSCmounhacNo ratings yet

- USB-A To Serial Cable: What's IncludedDocument1 pageUSB-A To Serial Cable: What's Includedabarboza4574No ratings yet

- DCD 435Document1 pageDCD 435ojhabreNo ratings yet

- HDS 5/11 U/UX Service Manual: English 5.906-487.0 Rev. 00 (04/10)Document50 pagesHDS 5/11 U/UX Service Manual: English 5.906-487.0 Rev. 00 (04/10)Jose Maria Castro PazosNo ratings yet

- Oversizing of Solaredge Inverters, Technical NoteDocument1 pageOversizing of Solaredge Inverters, Technical NoteMohammad HamamdNo ratings yet

- Pengenalan Kepada AutocadDocument28 pagesPengenalan Kepada AutocadHanapi Ahamd AwatNo ratings yet

- Catalogue SGF Eng PDFDocument8 pagesCatalogue SGF Eng PDFrimce77No ratings yet

- 2 Mark (ED Questions)Document26 pages2 Mark (ED Questions)Pradeep ravichanderNo ratings yet

- Basic Electrical Engineering Questions & AnswersDocument9 pagesBasic Electrical Engineering Questions & AnswersRajuNo ratings yet

- D74942GC40 15947 UsDocument4 pagesD74942GC40 15947 UsWilliam LeeNo ratings yet

- Initial Start Up Procedure g3516bDocument16 pagesInitial Start Up Procedure g3516bmuhammad arifNo ratings yet

- Silo Weight & Volume CalculationDocument18 pagesSilo Weight & Volume CalculationYogesh PatilNo ratings yet

- Bei Drawworks Encoder Hs35Document2 pagesBei Drawworks Encoder Hs35pr_oilNo ratings yet

- List of True 16 9 ResolutionsDocument19 pagesList of True 16 9 ResolutionsryuNo ratings yet

- DGT Quick Setup 07.03 13.03 ENDocument1 pageDGT Quick Setup 07.03 13.03 ENseabellNo ratings yet

- Quartz Crystal Filter GuideDocument10 pagesQuartz Crystal Filter Guidedenkins2020No ratings yet

- Kreatryx Analog Circuits PDFDocument43 pagesKreatryx Analog Circuits PDFshubhamNo ratings yet

- Pizzato - Elettrica FS2996D024 F3 Datasheet PDFDocument35 pagesPizzato - Elettrica FS2996D024 F3 Datasheet PDFEwerton SoaresNo ratings yet

- Ultimate Midi Guide From PDFDocument4 pagesUltimate Midi Guide From PDFnetzah2padre100% (1)

- Survey & Mitigation: Who We Are & What We DoDocument5 pagesSurvey & Mitigation: Who We Are & What We DorustyNo ratings yet

- Lourve: Product InformationDocument8 pagesLourve: Product Informationntt_121987No ratings yet