Professional Documents

Culture Documents

Lista de Exercícios de Eletrônica Digital sobre Flip Flops e Contadores

Uploaded by

grtt900%(1)0% found this document useful (1 vote)

182 views6 pagesOriginal Title

FF USF

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0%(1)0% found this document useful (1 vote)

182 views6 pagesLista de Exercícios de Eletrônica Digital sobre Flip Flops e Contadores

Uploaded by

grtt90Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 6

1

UNIVESIDADE SO FRANCISCO - USF

Lista Exerccios de Eletrnica Digital Flip Flop

1. As formas de onda mostradas abaixo so aplicadas nas entradas do

latch de portas NOR. Considere inicialmente que Q = 0 e determine a

forma de onda de Q.

2. a) Inicialmente, faa uma anlise e descreva a operao do circuito

abaixo e b) um estudante realiza alguns testes no circuito, e observa

que quando a chave esta na posio B, o circuito funciona

corretamente; entretanto, quando a chave passa para a posio A, o

latch no vai para o estado onde Q = 1. Quais so as possveis causas

deste mau funcionamento.

3. Como um flip-flop J-K pode ser modificado para operar como um flip-

flop D.

4. Na figura abaixo mostra dois registradores de deslocamento de trs

bits, X e Y, com sadas iguais a X2, X1, X0, Y2, Y1 e Y0, respectivamente.

Os registradores so conectados de tal forma que o contedo do

registrador X deslocado (transferido serialmente) para o registrador Y.

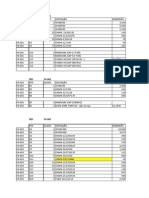

A partir dos valores iniciais para os registradores X e Y da tabela,

determine o contedo de cada flip-flop aps a ocorrncia do sexto pulso

de deslocamento.

2

registrador X registrador Y

X2 X1 X0 Y2 Y1 Y0

1 0 1 0 0 0 Antes dos pulsos serem aplicados

0 1 0 1 0 0 Depois do primeiro pulso

0 0 1 0 1 0 Depois do segundo pulso

0 0 0 1 0 1 Depois do terceiro pulso

5. Considere que o contador de mdulo 8 da figura abaixo. a) se ele estiver

no estado 101, qual ser seu estado aps 13 pulsos terem sido

aplicados. Se outros trs flip-flops foram ligados ao contador de forma

que suas sadas, determine: b) o mdulo do contador, c) a freqncia na

sada do ltimo flip-flop (MSB) quando a freqncia de entrada igual a

1,0 MHz, d) qual a faixa de contagem para este contador e e) suponha o

estado inicial 000000, qual ser o estado deste contador aps 129

pulsos.

6. Suponha que as formas de onda mostradas abaixo estejam conectadas

ao circuito. Se inicialmente Q = 0, determine a forma de onda da sada

Q.

3

7. a) mostre como um flip-flop J-K pode funcionar como um flip-flop T.

Aplique uma onda quadrada de 10 kHz na sua entrada e determine sua

forma de onda de sada e b) conecte a sada deste flip-flop na entrada

clock de um outro flip-flop J-K e determine a freqncia da forma de

onda da sada do segundo flip-flop.

8. Um flip-flop D disparado pela borda pode ser operado no modo de

comutao conectando-o como mostra a figura abaixo. Considere

inicialmente Q = 0 e determine: a) a forma de onda de Q; b) altere o

circuito de modo que a sada Q seja ligada em D e determine a forma de

onda da sada Q.

9. Considere inicialmente que o flip-flop abaixo esteja com sua sada Q = 0

e determine a sua forma de onda. Lembre-se de que as entradas

assncronas sobrepem-se a todas as outras entradas.

10. Um registrador de deslocamento circular um registrador de

deslocamento que mantm a informao binria circulando atravs do

registrador conforme os pulsos de clock so aplicados. O registrador da

figura abaixo pode ser transformado em um registrador circular

conectando-se X0 na linha DATA IN. Nenhuma entrada externa usada.

Considere que este registrador comece com 1011 armazenando nele (X3

= 1, X2 = 0, X1 = 1 e X0 = 1). Relacione a seqncia de estados que os

flip-flops do registrador apresentam conforme oito pulsos de

deslocamento so aplicados.

4

11. Um contador assncrono de 4 bits, ou seja de mdulo 16, comea no

estado 0000 e ento os pulsos de clock so aplicados. Depois de algum

tempo, os pulsos so interrompidos e os flip-flops apresentam o estado

lgico 0011. Quantos pulsos de clock ocorreram.

12. Determine o mdulo de contador e a freqncia do contador

mostrado abaixo.

13. Construa um contador de mdulo 10 que contar de 0000 at 1001.

14. O smbolo de um contador lgico assncrono 74LS293 (TTL) como o

mostrado na figura abaixo, tem quatro flip-flops J-K com sadas Q0

(LSB), Q1, Q2 e Q3 (MSB). Cada entrada possui uma entrada CP (pulso de

clock) que apenas outro nome para CLK. Cada flip-flop possui ainda

uma entrada assncrona de CLEAR, CD, que so conectadas juntas na

sada de uma porta NAND de duas entradas, MR1 e MR2 onde MR

significa Master Reset (reset geral). Ambas as entradas MR devem estar

em ALTO para limpar o contador para 0000. Os flip-flops Q1, Q2 e Q3 j

esto conectados como um contador por pulsao de trs bits. O flip-

flop Q0 no internamente conectado a nada. Isto permite ao usurio a

opo de conectar Q0 e Q1 para formar um contador de quatro bits ou

usar Q0 separadamente se desejar. Mostre como o 74LS293 poderia ser

conectado para operar como um contador de mdulo 16 com uma

entrada de clock de 10 kHz.

5

15. Mostre como o CI 74LS293 do exerccio anterior pode ser ligado para

funcionar como um contador de mdulo 10.

16. No circuito contador sncrono de mdulo 16 como o mostrado

abaixo, cada flip-flop disparado pela descida do sinal de clock de

entrada, de modo que todas as transies dos flip-flops ocorrem ao

mesmo tempo. Determine: a) a freqncia mxima para o contador se o

tpd para cada FF de 50 ns e o tpd para cada porta AND de 20 ns.

Compare este valor com a freqncia mxima de um contador

assncrono de mdulo 16, b) o que deve ser feito para converter este

contador em um que tenha mdulo 32 e c) determine a mxima

freqncia para o contador paralelo de mdulo 32.

17. Consulte o contador mostrado na figura abaixo. Como voc pode

saber se ele um contador decrescente. Ele foi modificado, a fim de que

no conte a mxima seqncia binria completa de 111 at 000.

Determine a seqncia de contagem real que ele realiza.

6

18. Desenhe o diagrama para o contador em anel de cinco bits utilizando

flip-flops J-K.

19. Esquematize, utilizando flip-flops J-K mestre escravo, um contador

para trabalhar como divisor de freqncia por 5 e esboce as formas de

onda da entrada e sada para este contador.

20. Determine o diagrama de estados para o contador da figura abaixo,

sabendo-se que no instante inicial os flip-flops foram resetados.

You might also like

- ED - C8 - Registradores de Deslocamento e ContadoresDocument19 pagesED - C8 - Registradores de Deslocamento e ContadoresRodrigo Elias de SouzaNo ratings yet

- Aula 06 - Contadores DigitaisDocument2 pagesAula 06 - Contadores DigitaisArthur AndradeNo ratings yet

- LE4: Circuitos Sequencias: Latches (Aula 5-1)Document5 pagesLE4: Circuitos Sequencias: Latches (Aula 5-1)anyaNo ratings yet

- Circuitos Digitais - ListaDocument4 pagesCircuitos Digitais - ListaAndré Araújo de Souza SilvaNo ratings yet

- Lista III Circuitos SequenciaisDocument8 pagesLista III Circuitos SequenciaisPhilipp HassNo ratings yet

- Flip-Flops, +registradores e ContadoresDocument32 pagesFlip-Flops, +registradores e ContadoresRoberto MarçalNo ratings yet

- ExercÃ-cios ResExercÃ-cios ResolvidoolvidosDocument77 pagesExercÃ-cios ResExercÃ-cios ResolvidoolvidosGian Do Atacado Silveira0% (1)

- Aula 07 - Contadores AssncronosDocument45 pagesAula 07 - Contadores AssncronosRafaele Jéssica0% (1)

- Cap 10Document45 pagesCap 10Bruno MigueresNo ratings yet

- Contador JohnsonDocument2 pagesContador JohnsonMarcelo Dhom100% (1)

- Contadores Síncronos: Características e AplicaçõesDocument22 pagesContadores Síncronos: Características e AplicaçõesYuri MaiaNo ratings yet

- ED2 - Contadores AssincronosDocument8 pagesED2 - Contadores AssincronosNathan CamiloNo ratings yet

- Sistemas Digitais - Lista 2 sobre Latches, Flip Flops, Máquinas de Estados e Análise de TempoDocument3 pagesSistemas Digitais - Lista 2 sobre Latches, Flip Flops, Máquinas de Estados e Análise de TempoGabriel Lucas Bento GermanoNo ratings yet

- Eletrônica Digital: Flip-Flops, Registradores e ContadoresDocument72 pagesEletrônica Digital: Flip-Flops, Registradores e Contadoreswagns10100% (1)

- Lista FinalDocument9 pagesLista Final4paracompranoaliexpressNo ratings yet

- Contadores e registradores: tipos, aplicações e circuitosDocument31 pagesContadores e registradores: tipos, aplicações e circuitosAmanda De AlbuquerqueNo ratings yet

- UNIP Eng Eletrônica Digital Lista 01Document4 pagesUNIP Eng Eletrônica Digital Lista 01rmarques85No ratings yet

- Biblioteca 1828563Document20 pagesBiblioteca 1828563Franz C SchreiberNo ratings yet

- CL Cap 7 2019 2Document132 pagesCL Cap 7 2019 2Carllos LimmaNo ratings yet

- Aula2 - Unidade Lógica e AritméticaDocument32 pagesAula2 - Unidade Lógica e AritméticaJESSICA ANDRADE FURTADO DE LIMANo ratings yet

- Capítulo 3Document30 pagesCapítulo 3Abelardo Zcarias CardenasNo ratings yet

- Aula - Prática 1Document4 pagesAula - Prática 1GildoNo ratings yet

- Exercicios 2Document20 pagesExercicios 2matheus mendonçaNo ratings yet

- Cap 3Document61 pagesCap 3JoaquimCoutinhoNo ratings yet

- Sistema DigitalDocument20 pagesSistema DigitalEmanuella Carvalho AlmeidaNo ratings yet

- Exercicios Prova1 PDFDocument3 pagesExercicios Prova1 PDFAline DiasNo ratings yet

- Lista de Exercícios - Circuitos Digitais - Resolução - Frank VahidDocument19 pagesLista de Exercícios - Circuitos Digitais - Resolução - Frank VahidElder SantosNo ratings yet

- 6495 Assessoria Atividade 3 - Eletrônica Digital - 51 2024Document11 pages6495 Assessoria Atividade 3 - Eletrônica Digital - 51 2024matheus koniczNo ratings yet

- Cronômetro DigitalDocument5 pagesCronômetro DigitalDavid Da Silva BorgesNo ratings yet

- Exercícios Blocos Lógicos Memórias e ConversoresDocument6 pagesExercícios Blocos Lógicos Memórias e ConversoresCedeps facensNo ratings yet

- ContadoresDocument21 pagesContadoressergioNo ratings yet

- Flip-Flops e registradores de deslocamentoDocument7 pagesFlip-Flops e registradores de deslocamentoFernanda MartinsNo ratings yet

- Lista Exercícios ContadoresDocument4 pagesLista Exercícios ContadoresCaioGomesNo ratings yet

- Electronica Digital - D.timaneDocument31 pagesElectronica Digital - D.timaneAnaciano SafoNo ratings yet

- Circuitos-Logicos Aula 13-1Document22 pagesCircuitos-Logicos Aula 13-1Maluuh MarquesNo ratings yet

- Lista de Exercicios - Latches e FlipFlopsDocument5 pagesLista de Exercicios - Latches e FlipFlopsMarcelo CesarNo ratings yet

- Cronômetro DigitalDocument6 pagesCronômetro Digitalpaulohss1985No ratings yet

- Memória 3 bits e relógio digitalDocument19 pagesMemória 3 bits e relógio digitalGabriel PavanNo ratings yet

- Contadores síncronos decrescentes e CIs 74ALS163 e 74ALS191Document27 pagesContadores síncronos decrescentes e CIs 74ALS163 e 74ALS191rmarques85No ratings yet

- ListaExercíciosArquiteturaComputadoresDocument21 pagesListaExercíciosArquiteturaComputadoresoctaviooliNo ratings yet

- Registradores e ContadoresDocument34 pagesRegistradores e ContadoresWalterson SantosNo ratings yet

- Aula 09 - Contadores UP-DOWN e Carga ParalelaDocument28 pagesAula 09 - Contadores UP-DOWN e Carga ParalelaAntónio CorreiaNo ratings yet

- Circuito 555 aplicaçõesDocument6 pagesCircuito 555 aplicaçõesEdson Luis FreitasNo ratings yet

- Slide 1. Osciladores e TemporizadoresDocument26 pagesSlide 1. Osciladores e TemporizadoresInaldo FélixNo ratings yet

- dIMENSIONAMENTO FUSIVELDocument8 pagesdIMENSIONAMENTO FUSIVELIgor Capelo100% (1)

- Lista de exercícios de conversores CC-CC e CC-CADocument4 pagesLista de exercícios de conversores CC-CC e CC-CAGustavo Nunes RiosNo ratings yet

- Relatório Contador Síncrono em AnelDocument16 pagesRelatório Contador Síncrono em AnelFelix GabrielNo ratings yet

- Lista Flip FlopDocument7 pagesLista Flip FlopJose IsaiasNo ratings yet

- Flip FlopDocument13 pagesFlip FlopGuilherme Barbosa MendesNo ratings yet

- Introdução aos Flip-FlopsDocument12 pagesIntrodução aos Flip-FlopsAmerco TivaneNo ratings yet

- Resumo ContadoresDocument2 pagesResumo ContadoresJoão CarlosNo ratings yet

- Contador de Pulsos/ Divisor de ClockDocument3 pagesContador de Pulsos/ Divisor de ClockJoão Antônio MonfortNo ratings yet

- Simulado p2 - Sistemas DigitaisDocument2 pagesSimulado p2 - Sistemas DigitaisBrendow AlmeidaNo ratings yet

- SDex1998 1 1 ResolucaoDocument6 pagesSDex1998 1 1 ResolucaoluisjeNo ratings yet

- TP 1 Sistemas de Computação II - Yonder ArellanoDocument9 pagesTP 1 Sistemas de Computação II - Yonder ArellanoScribdTranslationsNo ratings yet

- M 1108a 1100 Aluno PorDocument23 pagesM 1108a 1100 Aluno PorDavid GuimarãesNo ratings yet

- Circuitos lógicos flip-flops e contadoresDocument5 pagesCircuitos lógicos flip-flops e contadoresMarcos CampeloNo ratings yet

- Catálogo Vol 1 EngrenagensDocument48 pagesCatálogo Vol 1 EngrenagensleandroNo ratings yet

- Handbook AntigaDocument98 pagesHandbook Antigagrtt90No ratings yet

- FA27DRE90M4 MotorDocument1 pageFA27DRE90M4 Motorgrtt90No ratings yet

- Dimensões EletrocalhasDocument20 pagesDimensões Eletrocalhasgrtt90No ratings yet

- UsrConColBasPin (Testes)Document34 pagesUsrConColBasPin (Testes)grtt90No ratings yet

- Maximos e MinimosDocument5 pagesMaximos e MinimosEriton SantosNo ratings yet

- Análise de Sistemas Fluidotérmicos - Combustão CompletaDocument1 pageAnálise de Sistemas Fluidotérmicos - Combustão Completagrtt90No ratings yet

- Handbook Oficial UTBRDocument133 pagesHandbook Oficial UTBRgrtt90No ratings yet

- Treinamento Básico Inventor 2013Document343 pagesTreinamento Básico Inventor 2013Morce Victor Silva100% (1)

- Nota Tecnica ANEELDocument19 pagesNota Tecnica ANEELFabio Assoni MoratoNo ratings yet

- 2014-03-24 - Rdo Nº65Document3 pages2014-03-24 - Rdo Nº65grtt90No ratings yet

- Nota Tecnica ANEELDocument19 pagesNota Tecnica ANEELFabio Assoni MoratoNo ratings yet

- Nota Tecnica ANEELDocument19 pagesNota Tecnica ANEELFabio Assoni MoratoNo ratings yet

- Carta de OposicaoDocument1 pageCarta de Oposicaogrtt90No ratings yet

- Comentários AdicionaisDocument1 pageComentários Adicionaisgrtt90No ratings yet

- Rdo 31-01Document1 pageRdo 31-01grtt90No ratings yet

- BiodieselDocument101 pagesBiodieselgrtt90No ratings yet

- Cópia de Orçamento Anual 2014Document7 pagesCópia de Orçamento Anual 2014grtt90No ratings yet

- Guarda-corpos em tubos de açoDocument3 pagesGuarda-corpos em tubos de açogrtt90No ratings yet

- Dimensões EletrocalhasDocument20 pagesDimensões Eletrocalhasgrtt90No ratings yet

- Guarda-corpos em tubos de açoDocument3 pagesGuarda-corpos em tubos de açogrtt90No ratings yet

- ControleDocument2 pagesControlegrtt90No ratings yet

- Apostila AutoCad MechanicalDocument66 pagesApostila AutoCad MechanicalJúlio Gallinaro Maranho100% (1)

- Lista Itens de InoxDocument2 pagesLista Itens de Inoxgrtt90No ratings yet

- LISTA DE ETIQUETAS DE TUBULAÇÃO - XLSMDocument8 pagesLISTA DE ETIQUETAS DE TUBULAÇÃO - XLSMgrtt90No ratings yet

- Ø de Tubos em MMDocument1 pageØ de Tubos em MMgrtt90No ratings yet

- Peso Das ConexõesDocument20 pagesPeso Das Conexõesgrtt90No ratings yet

- Estudo Materiais Suportes SaipemDocument33 pagesEstudo Materiais Suportes Saipemgrtt90No ratings yet

- Memorial de Cálculo Mezanino 2,5 t-m2Document9 pagesMemorial de Cálculo Mezanino 2,5 t-m2Bico BicottoNo ratings yet

- Ondas Transversais e LongitudinaisDocument2 pagesOndas Transversais e LongitudinaisManuela SofiaNo ratings yet

- Capitulo 4a PDFDocument39 pagesCapitulo 4a PDFRocopi EngenhariaNo ratings yet

- Av2 Sistema Eletrico Falta ResponderDocument5 pagesAv2 Sistema Eletrico Falta ResponderEliton rabeloNo ratings yet

- Geografia do Crescente FértilDocument39 pagesGeografia do Crescente FértilDavi G. NascimentoNo ratings yet

- A Origem Do Universo, de John. D. Barrow (Resumido Por Natan Ourives)Document3 pagesA Origem Do Universo, de John. D. Barrow (Resumido Por Natan Ourives)natanourivesNo ratings yet

- Problema de transporte - método stepping stoneDocument5 pagesProblema de transporte - método stepping stonedivino5No ratings yet

- Artigo HQ Proeja Revista Holos IFRNDocument16 pagesArtigo HQ Proeja Revista Holos IFRNAdriano Henrique FerrarezNo ratings yet

- 05 Aplicacoes de AutomacaoDocument97 pages05 Aplicacoes de AutomacaoledilsonNo ratings yet

- Guia para museus militaresDocument213 pagesGuia para museus militaresCaio GhirardelloNo ratings yet

- Manual Do Operador de Colhedora de Cana-21-09-2010 - Case-John Deere-Santal PDFDocument85 pagesManual Do Operador de Colhedora de Cana-21-09-2010 - Case-John Deere-Santal PDFWesley Ferracin92% (13)

- Simbologia e Tagueamento PDFDocument18 pagesSimbologia e Tagueamento PDFAdriano MarquesNo ratings yet

- Teste de Biologia 11Document10 pagesTeste de Biologia 11grelhada67% (3)

- Gases perfeitos: propriedades e aplicaçõesDocument1 pageGases perfeitos: propriedades e aplicaçõesPauloMesquitaNo ratings yet

- Aula 2 Biofisica T 7Document49 pagesAula 2 Biofisica T 7Thiago AndradeNo ratings yet

- Campo magnético condutor correnteDocument3 pagesCampo magnético condutor correntetaynarNo ratings yet

- Lista VetoresDocument3 pagesLista VetoresDoidin Da cobalNo ratings yet

- Medir resistência isolamento motoresDocument6 pagesMedir resistência isolamento motoresreisinho1000100% (1)

- EECT900 Multi-Probe MANUAL PortuguesDocument17 pagesEECT900 Multi-Probe MANUAL PortuguesRamises NeryNo ratings yet

- Gol de futebol analisado por físicaDocument23 pagesGol de futebol analisado por físicaApollo SilvaNo ratings yet

- Lab espectroscópio simples construçãoDocument5 pagesLab espectroscópio simples construçãolevi_santosNo ratings yet

- Exame Nacional Moçambique 12 Classe Matemática 2 Época 2008Document6 pagesExame Nacional Moçambique 12 Classe Matemática 2 Época 2008Dias Sozinho Joaque100% (2)

- Medir Pistão e AnelDocument2 pagesMedir Pistão e Anelcrpessoa100% (4)

- Avaliação de atividades presenciais sobre equipamentos de subestaçãoDocument2 pagesAvaliação de atividades presenciais sobre equipamentos de subestaçãoSEBASTIAO THIAGO PORTO MARQUESNo ratings yet

- BS-380 Operation Manual (Portuguese) (v2.0) PDFDocument403 pagesBS-380 Operation Manual (Portuguese) (v2.0) PDFLuana Zuffo100% (2)

- Prova Calculo Aplicado - UnifanorDocument4 pagesProva Calculo Aplicado - UnifanorSamirla MaraNo ratings yet

- Polimeros Na Construção CivilDocument60 pagesPolimeros Na Construção CivildacioferNo ratings yet

- Abril Geografia Coordenadas Geograficas 2Document2 pagesAbril Geografia Coordenadas Geograficas 2LuMandarinoNo ratings yet

- Relatório Construção CivilDocument5 pagesRelatório Construção CivilLuiz ItaloNo ratings yet

- Area1-Cristaloquimica Dos FilossilicatosDocument35 pagesArea1-Cristaloquimica Dos FilossilicatossvarggNo ratings yet