Professional Documents

Culture Documents

Asynchronous Implementation of Discrete Event Controllers Based On Safe Automation Petri Nets

Uploaded by

Ivan Plasencia0 ratings0% found this document useful (0 votes)

11 views18 pagesAsynchronous implementation of discrete event controllers based on safe automation Petri nets. Paper is expected to serve as a guideline to show how to obtain very high speed, concurrent and asynchronous Petri net-based controllers.

Original Description:

Original Title

Asynchronous Implementation of Discrete Event Controllers Based on Safe Automation Petri Nets

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentAsynchronous implementation of discrete event controllers based on safe automation Petri nets. Paper is expected to serve as a guideline to show how to obtain very high speed, concurrent and asynchronous Petri net-based controllers.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

11 views18 pagesAsynchronous Implementation of Discrete Event Controllers Based On Safe Automation Petri Nets

Uploaded by

Ivan PlasenciaAsynchronous implementation of discrete event controllers based on safe automation Petri nets. Paper is expected to serve as a guideline to show how to obtain very high speed, concurrent and asynchronous Petri net-based controllers.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 18

ORIGINAL ARTICLE

Asynchronous implementation of discrete event

controllers based on safe automation Petri nets

Murat Uzam & . Burak Ko & Gkhan Gelen &

B. Hakan Aksebzeci

Received: 10 April 2007 / Accepted: 26 March 2008 / Published online: 17 June 2008

# Springer-Verlag London Limited 2008

Abstract In this paper, a new method is proposed for

digital hardware implementation of Petri net-based specifi-

cations. The purpose of this paper is to introduce a new

discrete event control system paradigm, where the control

system is modeled with extended Petri nets and imple-

mented as an asynchronous controller using circuit ele-

ments. The applicability of the proposed method is

demonstrated by an asynchronous implementation of a

Petri net-based discrete event control system (DECS) for an

experimental manufacturing system using a Xilinx field

programmable gate array (FPGA). Unlike microprocessor,

microcontroller or programmable logic controller (PLC)-

based software implementations or hardware-based syn-

chronous implementations, the implementation method

used in this paper is asynchronous and based on hardware

offering very high speed to control fast plants at low cost.

This paper is expected to serve as a guideline to show how

to obtain very high speed, concurrent and asynchronous

Petri net-based controllers.

Keywords Petri nets

.

Discrete event systems

.

Hardware

implementation

.

Field programmable gate arrays (FPGA)

.

Manufacturing systems

.

Discrete event control system

1 Introduction

Discrete event systems (DES), examples of which include

communication networks, manufacturing systems, computer

networks, various transportation systems, robots, etc.,

exhibit properties such as non-determinism, asynchronous

operations, conflict, and concurrency. The study, i.e., design,

analysis, synthesis, etc., of DES has been carried out mainly

by using two modeling techniques: finite state machines

(FSM) and Petri nets. FSM-based studies suffer from so

called state explosion problem. FSMs provide sequential

models. When using FSMs graphical visualization of the

modeled system can not be realized easily [1]. Petri nets

have been used as an alternative formalism for the study of

DESs due to their easily understood graphical representa-

tion in addition to their well-formed mathematical for-

malism. For the Petri net basics, the reader is referred to [2].

In this paper, the main concern is the control of DES by

using Petri net-based specifications. The control of DESs is

done firstly by modelling the controller as a Petri net and

then by implementing it in software or hardware. The

implementation is carried out by simulating the Petri net

model in terms of software or hardware structures. The

software implementation has been done using either high or

low level languages. Examples of software implementations

may be found in [3, 4]. Some important literatures on

PLC-based software implementation are found in [59].

Synchronous or asynchronous controllers of Petri net-based

specifications have been obtained as hardware implemen-

tation. For detailed information on Petri nets and digital

hardware design, the reader is referred to [10]. Examples of

synchronous hardware implementations may be found in

[11, 12]. Program statements in software-based implemen-

tations run in a sequential manner by following a sequence

of commands. Therefore, they do not actually capture

the concurrency and asynchronous characteristics of the

modeled DES. Unlike a synchronous hardware circuit, in an

asynchronous circuit, there is no global clock, i.e., they are

self timed. Asynchronous circuits can be viewed as

Int J Adv Manuf Technol (2009) 41:595612

DOI 10.1007/s00170-008-1497-2

M. Uzam (*)

:

. B. Ko

:

G. Gelen

:

B. H. Aksebzeci

Nide University, Mhendislik-Mimarlk Fakltesi,

Elektrik-Elektronik Mhendislii Blm,

51200 Nide, Turkey

e-mail: murat_uzam@nigde.edu.tr

hardwired versions of parallel and distributed programs.

The program statements are physical components, i.e., logic

gates, memory elements, etc. Asynchronous circuits are

better than the synchronous counterparts in terms of

performance, robustness, low power, low electromagnetic

emission, modularity and re-use, and testability [10]. In this

paper, asynchronous circuit implementation of Petri net-

based specifications is considered. This type of implemen-

tation is carried out based on the idea of physical

simulation and achieved by associating each place in the

Petri net with a memory latch. Examples of this style can be

found in [1316].

In this paper, a new method is proposed for the digital

hardware implementation of Petri net-based specifications.

The purpose of this paper is to introduce a new discrete

event control system paradigm, where the control system is

modeled with extended Petri nets and implemented as an

asynchronous controller using circuit elements. The digital

hardware implementation of Petri net transitions proposed

in this paper may be viewed as a better version of a

previously introduced method [15]. In addition, the hard-

ware implementation of the timed-transition is proposed.

Moreover, the applicability of the proposed method is

demonstrated by a successful implementation of a Petri net-

based DECS for an experimental manufacturing system by

using a Xilinx FPGA. This paper can be regarded as an

extended version of the previous work presented in [17, 18].

The remainder of this paper is organized as follows: The

next section defines safe automation Petri nets (SAPN). In

the Sect. 3, the digital hardware implementation of SAPN is

explained by considering some important Petri net struc-

tures. Section 4 defines the Xilinx Spartan 2 XC2S200

FPGA and the Digilab 2 (D2) FPGA-based development

board. Section 5 describes the necessary technical arrange-

ments carried out in order to connect the Spartan 2

XC2S200 FPGA to the real world as a logic controller.

Xilinx FPGA implementation of the timed-transition is

proposed in Sect. 6. The experimental discrete manufactur-

ing system is introduced in Sect. 7. In Sect. 8, the SAPN

model of the DECS for the discrete manufacturing system

is described. The digital hardware implementation of the

SAPN model is explained in Sect. 9. Finally, conclusions

are given in the last section.

2 Safe automation Petri nets

Automation Petri nets (APN) have recently been introduced

as a new formalism for the design of discrete event control

systems [1]. Since ordinary Petri nets do not deal with

sensors and actuators, the Petri net concepts are extended,

by including actions and sensor readings as formal

structures within the APN. These extensions involve

extending the Petri nets to accommodate sensor signals at

transitions and to assign level actions to places (and

similarly to assign impulse actions to transitions). In this

section, safe (1-bounded) automation Petri nets (SAPN) to

be used for direct translation from Petri nets to circuit

elements are defined. A typical discrete event control

system (DECS) is shown in Fig. 1(a). It consists of a

discrete event system (DES), to be controlled and a discrete

event controller (DEC). Sensor readings are regarded as

inputs from the DES to the DEC, and control actions are

considered as outputs from the DEC to the DES. The main

function of the DEC is to supervise the desired DES

operation and to avoid forbidden operations. To do this, the

DEC processes the sensor readings and then forces the DES

to conform to the desired specifications through control

actions. Petri nets can be used to design such DECs.

However, ordinary Petri nets do not deal with actuators or

sensors. Because of this, it is necessary to define a Petri net-

based controller (automation Petri netAPN), which can

embrace both actuators and sensors within an extended

Petri net framework. An SAPN is shown in Fig. 1(b). In the

SAPN, sensor readings can be used as firing conditions at

transitions. The presence or absence of sensor readings can

be used in conjunction with the extended Petri net pre-

conditions to fire transitions. In the SAPN, two types of

Fig. 1 (a) A typical discrete event control system (DECS). (b) Safe automation Petri net (SAPN). (c) SAPN used as a controller in a DECS

596 Int J Adv Manuf Technol (2009) 41:595612

actuations can be considered, namely impulse actions and

level actions. Level actions are associated with places,

while impulse actions are associated with transitions. With

these additional features, it is possible to design discrete

event control systems. Figure 1(c) shows how an SAPN can

be used as a DEC in a DECS.

Formally, a safe automation Petri net can be defined as

follows:

SAPN P; T; Pre; Post; In; En; ; Q; M

0

where

P = {p

1

, p

2

,..., p

n

} is a finite, nonempty set of places,

T = {t

1

, t

2

,..., t

m

} is a finite, nonempty set of

transitions, P and P T = ,

Pre: (PT) {0,1} is an input function that defines

ordinary arcs from places to transitions.

Post: (TP) {0,1} is an output function that defines

ordinary arcs from transitions to places.

In: (PT) {0,1} is an inhibitor input function that

defines inhibitor arcs from places to transitions.

En: (PT) {0,1} is an enabling input function that

defines enabling arcs from places to transitions.

c = {c

1

, c

2

,..., c

m

} is a finite, nonempty set of firing

conditions associated with transitions.

Q = {q

1

, q

2

,..., q

n

} is a finite set of level actions that

might be assigned to places or impulse actions that

might be assigned to transitions.

M

0

: P {0,1} is the initial marking.

The SAPN consists of two types of nodes called places,

represented by circles (), and transitions, represented by

bars (). There are three types of arcs used in the SAPN,

namely, ordinary arcs, represented by a directed arrow (),

inhibitor arcs, represented by an arc, whose end is a circle

(), and finally enabling arcs, represented by a directed

arrow, whose end is empty (). Directed ordinary arcs

connect places to transitions and vice versa, while enabling

and inhibitor arcs connect only places to transitions. The

number of tokens in places represents the current state of

the system and firing of a transition represents the

movement of the system from one state to another state.

Each transition has a set of input and output places, which

represent the pre-condition and post-condition of the

transition. The level actions (Q), may be assigned to places,

and the impulse actions may be assigned to transitions.

Level actions may be enabled when there is a token at a

place, while impulse actions may be enabled at the instant

when a transition is fired. More than one action may be

assigned to a place or transition. Firing conditions in the

SAPN are recognized by external events (signals) such as

sensor readings, switch positions, etc. The firing condition

c is a Boolean variable that can be 0, in which case related

transition t is not allowed to fire, or it can be 1, in which

case t is allowed to fire if it is enabled, i.e., all input places

have one token each. The marking of the SAPN is

represented by the number of tokens in places. Tokens are

represented by black dots (). Movement of tokens between

places describes the evolution of the SAPN and is

accomplished by the firing of the enabled transitions. The

following rules are used to govern the flow of tokens:

Enabling rules:

1. If the input place p

1

of a transition t

1

is connected to t

1

with an ordinary arc Pre(p

1

, t

1

), then t

1

is said to be

enabled when p

1

contains a token, i.e., M(p

1

) = 1.

2. If the input place p

1

of a transition t

1

is connected to t

1

with an enabling arc En(p

1

, t

1

), then t

1

is said to be

enabled when p

1

contains a token, i.e., M(p

1

) = 1.

3. If the input place p

1

of a transition t

1

is connected to t

1

with an inhibitor arc In(p

1

, t

1

), then t

1

is said to be

enabled when p

1

contains no token, i.e., M(p

1

) = 0.

Firing rules: In the SAPN, an enabled transition t can or

can not fire depending on the external firing condition of

t. A firing condition of a transition t may include more than

one sensor reading with AND, OR and NOT logical

operators. When dealing with more than one sensor reading

as a firing condition, the logical operators of firing con-

ditions must be taken into account accordingly. In the

special case, where c = 1, transition t is always allowed to

fire when it is enabled. When an enabled transition t fires

with a related firing condition c, it removes one token from

each input place p

i

and deposits, at the same time, one

token to each output place p

o

. It should be noted that, the

firing of an enabled transition t does not change the

marking of the input places that are connected to t only

by an enabling or an inhibitor arc.

3 Digital hardware implementation of safe automation

Petri nets (SAPN): direct translation from SAPN

to circuit elements

The direct translation method from SAPN to circuit

elements, proposed in this paper, is based on the idea of

physical simulation of every Petri net marking reachable

from the initial marking in terms of the state of the circuit.

In order to achieve the direct translation, the following three

steps are followed: i) each place in the SAPN is associated

with a memory element, i.e., an SR-flip-flop (SR-latch), ii)

each transition in the SAPN is implemented with a logical

gate (NAND gate), and iii) the initial marking is set-up by

using an RC (resistor and capacitor) element. Let us now

consider each of these three steps:

The first step in achieving the direct translation is to use

a memory element to represent the presence or absence of a

Int J Adv Manuf Technol (2009) 41:595612 597

token in a place. If there is a token in a place then the

output of the memory element is set to 1. In contrast, if

there is no token in a place then the output of the memory

element is reset to 0. In order to implement this operation,

an SR-flip-flop, shown in Fig. 2(a) is used. An SR-flip-flop

is constructed from two NAND gates connected back to

back. The cross-coupled connections from the output of one

gate to the input of the other gate constitute a feedback

path. Therefore, the circuit is classified as asynchronous.

Each flip-flop has two outputs; Q and Q, and two inputs;

set (S) and reset (R). The truth table of the SR-flip-flop is

given in Fig. 2(d). The application of a momentary 0 to the

S input causes output Q to go to 1 and Q to go to 0. The

outputs of the circuit do not change when the S input

returns to 1. A momentary 0 applied to the R input causes

an output of Q = 0 and Q 1. The state of the flip-flop is

always taken from the value of its normal output Q. When

Q = 1, it is said that the flip-flop stores a 1 and is in the set

state. When Q = 0, it is said that the flip-flop stores a 0 and

is in the reset state. The SR-flip-flop manifests an

undesirable condition if both inputs go to 0 simultaneously.

When both inputs are 0, outputs Q and Q will go to 1, a

condition which is normally meaningless in flip-flop

operation. In Fig. 2(b) an SAPN is shown, in which there

are two places; p1 and its complement p1, and two

transitions; t1 and t2, with firing conditions c

1

and c

2

,

respectively. This is an explicit representation of the safe

place p1. The implementation of places using the SR-flip-

flop is shown in Fig. 2(c) Output Q of the SR-flip-flop is

used to represent place p1 and output Q is used to represent

place p1. When there is a token in p1, the SR-flip-flop is

set, i.e., Q = 1 and Q 0. When there is a token in p1, the

SR-flip-flop is reset, i.e., Q = 0 and Q 1. It is assumed

that the model will not permit both outputs becoming Q = 1

and Q 1. That is to say that the designer must take some

action to assure that S = R = 0 will never occur.

ii) The second step in achieving the direct translation is

to use a NAND gate to implement transition in SAPN. The

behavior of a transition in SAPN may be summarized as

follows: IF there is a token each in the input places of a

transition t AND the firing condition c of t occurs, THEN

all the tokens are removed from the input places and one

token each is deposited to the output places of t. To show

how this behavior is implemented, the SAPN shown in

Fig. 3(a) is used. In this case, the transition t fires when all

input places p1, p2, p3,... have one token each and the

firing condition c occurs. When t fires it removes all the

tokens from the input places p1, p2, p3,..., and at the same

time, it deposits one token each to the output places, p11,

p12, p13, etc. To implement the transition t, the structure

shown in Fig. 3(b) is used. In this case, when all input flip-

flops are set and c occurs t is fired by resetting all the input

flip-flops and at the same time by setting all the output flip-

flops. Please note that the difference between the proposed

approach and [15] is that, in [15] the removal of tokens

from input places and adding tokens to output places has a

duration and there is an intermediate state between the two

operations, while in the proposed approach the removal of

tokens from input places and adding tokens to output places

is instantaneous. Figure 3(c) shows the implementation of

transitions t1 and t2 of Fig. 2(c). In the SAPN, t1 fires when

there is a token in p1 and c

1

occurs. When fired, t1

removes the token from p1 and deposits a token in p1. The

NAND gate 1 implements t1 as follows: when output p1

1 and c

1

occurs, i.e., c

1

becomes 1, p1 is set to 1 by

applying an instantaneous 0 from the output of the NAND

gate 1 to the S input of the flip-flop and at the same time

the output p1 is reset, i.e., p1 0. The same applies to t2 in

a similar manner.

iii) The third and last step is about setting-up the initial

marking by using an RC (resistor and capacitor) element. It

is necessary for proper functioning to set-up the initial

marking before operating the circuit. It is a common

practice to use an RC element to establish the power on

reset (POR) and at the same time to use a button connected

parallel to the capacitor such that at any time desired by

pressing the button it is possible to set the system back to

the initial marking. The time delay = R.C defines how

long the setting-up time will be for the initial marking.

Fig. 2 a) An SR-flip-flop, b) an SAPN, c) The implementation of a

place with an SR-flip-flop. d) The truth table of the SR-flip-flop

598 Int J Adv Manuf Technol (2009) 41:595612

Figure 4(a) shows how this process is accomplished. When

the power is first applied to the circuit, a 0 is applied, for

the period of time, to the S inputs of flip-flops, which

represent places with initial marking 1, i.e., all places p1,

p2, p3,... are set to 1. At the same time, a 0 is also applied

to the R inputs of flip-flops, which represent places with

initial marking 0, i.e., all places p11, p12, p13,... are reset

to 0. After the power is is applied to the circuit, at any

time it is also possible to set up the circuit back to the initial

marking by pressing the button B. An example SAPN is

shown in Fig. 4(b). In this particular net, p1 is marked

before p2; therefore this example represents the concept of

sequence. The hardware implementation of the SAPN

shown in Fig. 4(b) is given in Fig. 4(c). In this circuit

places and transitions are implemented as described before.

The initial marking, i.e., M

0

p1; p1; p2; p2

1; 0; 0; 1

T

,

is implemented by setting the first flip-flop and by resetting

the second flip-flop.

To show how the proposed technique is applied to the

hardware implementation of the SAPN, in this paper the

following SAPN structures are considered:

Enabling arc

Inhibitor arc

Fork (concurrency)

Join (synchronization)

Merge

Conflict

Toggle

Select

Actions

Timed-transition

Note that in the following circuits, places and transitions

are implemented as described before. In addition, for the

sake of simplicity the implementation of the initial marking

in the following SAPN structures are not shown.

3.1 Hardware implementation of the enabling arc

The modeling power of Petri nets can be extended by

adding the one testing ability, i.e., the ability to test

whether a place has a token. This is achieved by

introducing an enabling arc. The enabling arc connects an

input place to a transition and is represented by a directed

arrow, whose end is empty. The presence of an enabling arc

connecting an input place to a transition means that the

transition is only enabled if the input place has a token. The

firing does not change the marking in the enabling arc

connected places. In an SAPN, an enabling arc, En(p

2

,t

2

), is

shown in Fig. 5(a). The transition t2 is fired if both p1 and

p2 have one token each and firing condition c

2

occurs.

When t2 is fired, a token is removed from place p1 and a

token is deposited into the output place p3, but the marking

Fig. 3 a) A transition in SAPN. b) Implementation of the transition, b) Implementation of transitions t1 and t2 of Fig. 2(c)

Fig. 4 a) Setting-up the initial marking. B) An example SAPN. c) Setting up the initial marking of the SAPN shown in Fig. 4(b)

Int J Adv Manuf Technol (2009) 41:595612 599

of enabling arc connected place p2 does not change.

Transition t2 is not enabled to fire, if there is no token in

place p2. Figure 5(b) shows the representation of this

SAPN with complement places. The hardware implemen-

tation of the SAPN shown in Fig. 5(b) is given in Fig. 5(c).

3.2 Hardware implementation of the inhibitor arc

The modeling power of Petri nets can be extended by

adding the zero testing ability, i.e., the ability to test

whether a place has no token. This is achieved by an

inhibitor arc. The inhibitor arc connects an input place to a

transition and is represented by an arc, whose end is a

circle. The presence of an inhibitor arc connecting an input

place to a transition means that the transition is enabled if

the input place has no token. The firing does not change the

marking in the inhibitor arc connected places. In an SAPN,

an inhibitor arc, In(p

2

,t

2

), is shown in Fig. 6(a). The

transition t2 is fired if place p1 has a token and p2 has no

token and firing condition c

2

occurs. When t2 is fired, a

token is removed from the input place p1 and a token is

deposited into the output place p3, but the marking of

inhibitor arc connected place p2 does not change. The

transition t2 is not enabled to fire, if there is a token in place

p2. Figure 6(b) shows the representation of this SAPN with

complement places. Note that the inhibitor arc In(p

2

,t

2

),

shown in Fig. 6(a), can be replaced by the enabling arc

En(p2,t

2

). The hardware implementation of the SAPN

shown in Fig. 6(b) is given in Fig. 6(c).

3.3 Hardware implementation of fork (concurrency)

A fork (concurrency) represents two or more concurrent

processes. In Petri nets, the concept of fork can be modeled

easily, as shown in Fig. 7, where p1 and p2 represent two

concurrent activities. When p1 is not marked, i.e., there is

no token in p1, and the firing condition c

1

occurs, a token is

put in p1. When p1 is marked, both p2 and p3 are not

marked and the firing condition c

2

occurs, the token is

removed from p1 and at the same time one token each is

deposited in p2 and p3. This means that with the firing of

t1, two concurrent processes are initiated by depositing one

token each in p2 and p3. Figure 7(b) shows the represen-

tation of this SAPN with complement places. The hardware

implementation of the SAPN shown in Fig. 7(b) is given in

Fig. 7(c).

3.4 Hardware implementation of join (synchronization)

A join Petri net is used to synchronize two or more ongoing

processes. An example is shown in Fig. 8, where p1 and p2

represent two separate activities synchronized by means of

t3. When p1 is not marked, i.e., there is no token in p1, and

the firing condition c

1

occurs, a token is put in p1.

Fig. 5 a) An enabling arc,

En(p

22

), in an SAPN. b)

Representation of the SAPN

with complement places.

c) Hardware implementation of

the SAPN shown in Fig. 5(b)

600 Int J Adv Manuf Technol (2009) 41:595612

Fig. 7 a) Fork (concurrency) in

an SAPN. b) Representation of

the SAPN with complement

places. c) Hardware implemen-

tation of the SAPN shown in

Fig. 7(b)

Fig. 6 a) An inhibitor arc,

In(p

2

,t

2

), in an SAPN. b) Rep-

resentation of the SAPN with

complement places. c) Hardware

implementation of the SAPN

shown in Fig. 6(b)

Int J Adv Manuf Technol (2009) 41:595612 601

Similarly, when p2 is not marked and the firing condition

c

2

occurs, a token is deposited in p2. In order to fire t3 both

p1 and p2 must have one token each. When both p1 and p2

are marked, and p3 is not marked and the firing condition

c

3

occurs, t3 fires by depositing a token in p1 and at the

same time by removing the tokens from p2 and p3. This

means that with the firing of t3, two concurrent processes,

represented by p1 and p2 are synchronized. Figure 8(b)

shows the representation of this SAPN with complement

places. The hardware implementation of the SAPN shown

in Fig. 8(b) is given in Fig. 8(c).

3.5 Hardware implementation of merge

Two or more activities (processes) can be merged in Petri

nets. An example is shown in Fig. 9, where p1 and p2

represent two separate activities merged by means of p3.

When p1 is not marked, i.e., there is no token in p1, and the

firing condition c

1

occurs, a token is put in p1. Similarly,

when p2 is not marked and the firing condition c

2

occurs, a

token is deposited in p2. When p1 is marked and p3 is not

marked, and the firing condition c

3

occurs, t3 fires by

depositing a token in p3 and at the same time by removing

the token from p1. Similarly, when p2 is marked and p3 is

not marked, and the firing condition c

4

occurs, t4 fires by

depositing a token in p3 and at the same time by removing

the token from p2. Note that only one token can be

deposited in p3, when it is not marked. This means that p3

receives one token from the merged places p1 or p2.

Figure 9(b) shows the representation of this SAPN with

complement places. The hardware implementation of the

SAPN shown in Fig. 9(b) is given in Fig. 9(c).

3.6 Conflict

In a system, when two or more users share the same

resource and both try to access it at the same time, this

situation leads to conflict. In a Petri net, a conflict situation

occurs when a place enables more than one transition at the

same time. In conflict, only one transition can fire. A

conflict in SAPN is shown in Fig. 10. As can be seen from

Fig. 10, when there is a token in place p1, both transitions

t2 and t3 are enabled. Since only one transition can fire in

the case of conflict, any conflict, arising in a Petri net, must

be resolved. The conflict can be resolved by assigning a

priority scheme between the conflicting transitions. In this

paper two such conflict resolution schemes, namely toggle

and select, are considered.

3.7 Hardware implementation of toggle

One of the approaches for resolving conflict between the

two transitions is called toggle. In this approach with the

help of the added net elements the conflicting transitions

Fig. 8 a) Join (concurrency) in

an SAPN. b) Representation of

the SAPN with complement

places. c) Hardware implemen-

tation of the SAPN shown in

Fig. 8(b)

602 Int J Adv Manuf Technol (2009) 41:595612

fire one after another. Toggle conflict resolution method is

shown in Fig. 11(a): p4 is the complement place of p4, i.e.,

M p4 M p4

1. This means that the sum of tokens in

p4 and will always be 1. Initially, there is a token in p4.

Therefore, when a token is deposited in p1 only t2 is

enabled to fire, because M(p1) = 1 and M(p4) = 1. In this

case, when t2 is fired with the firing condition c

2

, the

tokens are removed from p1 and p4 and at the same time

one token each is deposited to p2 and p4. Thus, it is the

turn of t3 to fire. Therefore, when M(p1) = 1, M p4

1,

and the firing condition c

3

occurs, t3 is fired by removing

tokens from p1 and p4, and at the same time by depositing

one token each in p3 and p4. Figure 11(b) shows the

representation of this SAPN with complement places. The

hardware implementation of the SAPN shown in Fig. 11(b)

is given in Fig. 11(c).

3.8 Hardware implementation of select

Another approach for resolving conflict between the two

transitions is called select. In this approach a selection has

been made between the two conflicting transitions with the

help of a firing condition S. Select-conflict-resolution-

method is shown in Fig. 12(a) As can be seen, the firing

condition of t2 is c

2

= S, while the firing condition of t3 is

#

3

S. This means that whenever a token is deposited in

p1, if S = 1 then t2 will fire. On the other hand, whenever a

token is deposited in p1, if S = 0 then t3 will fire. In this

configuration t2 and t3 can never fire at the same time.

Figure 12(b) shows the representation of this SAPN with

complement places. The hardware implementation of the

SAPN shown in Fig. 12(b) is given in Fig. 12(c).

3.9 Hardware implementation of actions

In the SAPN, two types of actuations can be considered,

namely impulse actions and level actions. Impulse actions

are associated with transitions and they are enabled at the

Fig. 9 a) Merge in an SAPN. b)

Representation of the SAPN

with complement places. c)

Hardware implementation of the

SAPN shown in Fig. 9(b)

Fig. 10 Conflict in an SAPN

Int J Adv Manuf Technol (2009) 41:595612 603

instant, when the related transition is being fired. Level

actions are associated with places and they are enabled

when there is a token in the related place. More than one

action may be assigned to a transition or a place. Figure 13(a)

shows an SAPNin which there is an impulse action (Action 1)

assigned to t2, and there is a level action (Action 2) assigned

to p3. The hardware implementation of the SAPN shown in

Fig. 13(a) is given in Fig. 13(b).

Fig. 11 a) Toggle in an SAPN.

b) Representation of the SAPN

with complement places. c)

Hardware implementation of the

SAPN shown in Fig. 11(b)

Fig. 12 a) Select in an SAPN.

b) Representation of the SAPN

with complement places. c)

Hardware implementation of the

SAPN shown in Fig. 12(b)

604 Int J Adv Manuf Technol (2009) 41:595612

3.10 Timed-transition

Ordinary Petri nets do not include any concept of time.

With this class of nets, it is possible only to describe the

logical structure of the modeled system, but not its time

evolution. Due to the need for the temporal analysis of

discrete event systems, time has been introduced into Petri

nets in variety of ways. In this paper the timed-transition

Petri net is considered. A timed-transition Safe Automation

net (TTSAPN) is a tuple defined as follows:

TTSAPN SAPN;

where SAPN is a safe automation Petri net and is a

function from the set of transitions to the set of positive or

zero rational numbers. (t

i

) = T

i

= timing associated with

transition t

i

. In this case, a token can have two states: it can

be reserved for the firing of a timed-transition t

i

or it can be

unreserved. If a timed transition is enabled, then it is ready

to fire. When the firing condition for the transition occurs,

the token of input place to this transition is said to be

reserved for a specified amount of time (T

i

). When the time

T

i

has elapsed, the transition is effectively fired: the

reserved token is removed from the input place and an

unreserved token is put into the output place(s). This is

illustrated in Fig. 14, where the transition t3 is a timed-

transition with the time delay T3. At the beginning, there is

a token in place p1, as shown in Fig. 14(a). When transition

t2 is fired the token is removed from p1 and a token is

deposited in place p2, thereby resulting in the enabling of

timed-transition t3, as shown in Fig. 14(b). Then, the firing

condition c

3

for transition t3 may occur at any moment

after this. When the firing condition

3

occurs, the token

required for this firing is reserved, as shown in Fig. 14(c).

When time delay T3, has elapsed, the transition is

effectively fired. The token reserved for firing is then

removed from place p2 and an unreserved token is

deposited in place p3, as shown in Fig. 14(d). The

implementation of a timed-transition will be considered in

Fig. 13 a) Actions in an SAPN.

b) Hardware implementation of

the SAPN shown in Fig. 13(a)

Fig. 14 Timed-transition in an

SAPN

Int J Adv Manuf Technol (2009) 41:595612 605

a further section as it depends on the chosen implementa-

tion technology.

4 Xilinx Spartan 2 XC2S200 FPGA and the Digilab 2

(D2) FPGA-based development board

The Spartan-II 2.5V field-programmable gate array family

provides high performance, abundant logic resources, and a

rich feature set, all at a very low price [19]. System

performance is supported up to 200 MHz. Features of

Xilinx Spartan 2 XC2S200 FPGA include 56K bits block

RAM, 75,264 bits distributed RAM, 16 selectable I/O

standards, and four DLLs. The Spartan-II family is a

superior alternative to mask-programmed application spe-

cific integrated circuits (ASICs). The FPGA avoids the

initial cost, lengthy development cycles, and inherent risk

of conventional ASICs. Also, FPGA programmability

permits design upgrades in the field with no hardware

replacement necessary (impossible with ASICs). The

Digilab 2 (D2) FPGA-based development board (http://

www.digilentinc.com) makes an excellent prototyping

platform for moderate to complex digital circuits and

systems. The D2 board features a 200K-gate Xilinx Spartan

2 XC2S200 FPGA in a PQ208 package that provides 143

user I/Os. All available I/O signals are routed either to the

expansion connectors, or to the ports and other on-board

devices.

5 Connecting the Xilinx spartan 2 XC2S200

FPGA to the real-world

In this section, let us briefly describe how a Xilinx Spartan

2 XC2S200 FPGA accommodated in a Digilab 2 (D2)

FPGA-based development board is connected to the real-

world as a logic controller. D2 board provides only the 143

user I/Os of the FPGA. In order to protect the FPGA from

high voltage levels and large voltage spikes and use it as a

logic controller it is necessary to electrically isolate it from

the real-world. This is accomplished by using optical

couplers. To be able to connect 5V or 24V DC inputs to

the FPGA as an input, a voltage level converter is designed

for the inputs. Another important issue for the inputs was

the problem of so called contact bounce problem. When a

contact is closed or opened, it will close and open

(technically speaking make and break), many times before

finally settling in a stable state. This behavior of a contact is

interpreted as multiple false input signals and a digital

circuit will respond to each of these on-off or off-on

transitions. This problem is known as contact bounce and

has always been a very important problem when interfacing

switches, relays, etc. to a digital control system. In some

industrial applications debouncing is required to eliminate

both mechanical and electrical effects. To solve the contact

bounce problem for the input of the FPGA, a PIC16F628

Fig. 15 Symbol of the imple-

mented timed-transition

Table 1 S and Q inputs of

the timed_t

Binary number

S3 S2 S1 S0

Selected time

period

Binary number Q7 Q6

Q5 Q4 Q3 Q2 Q1 Q0

Selected decimal

number

0 0 0 0 2,621 ms 0 0 0 0 0 0 0 0 0

0 0 0 1 5,242 ms 0 0 0 0 0 0 0 1 1

0 0 1 0 10,485 ms 0 0 0 0 0 0 1 0 2

0 0 1 1 20,971 ms 0 0 0 0 0 0 1 1 3

0 1 0 0 41,943 ms 0 0 0 0 0 1 0 0 4

0 1 0 1 83,886 ms 0 0 0 0 0 1 0 1 5

0 1 1 0 167,772 ms ........ .

0 1 1 1 335,544 ms ........ .

1 0 0 0 671,088 ms ........ .

1 0 0 1 1,342 s ........ .

1 0 1 0 2,684 s ........ .

1 0 1 1 5,368 s 1 1 1 1 1 0 1 1 251

1 1 0 0 10,737 s 1 1 1 1 1 1 0 0 252

1 1 0 1 21,474 s 1 1 1 1 1 1 0 1 253

1 1 1 0 42,949 s 1 1 1 1 1 1 1 0 254

1 1 1 1 85,899 s 1 1 1 1 1 1 1 1 255

606 Int J Adv Manuf Technol (2009) 41:595612

microcontroller (www.microchip.com)-based debouncer

has been developed and used [20]. Similar arrangements

have been carried out for interfacing the FPGA to the

outputs. When using too many discrete outputs, FPGA can

not provide the necessary output current for proper

operation; therefore it is necessary to use an interface in

order to provide necessary amount of current for all discrete

outputs. To serve as a current amplifier, the integrated

circuit 74HC373, three-state octal D-type latch is used.

Then, in order to drive discrete outputs of 5V or 24V DC

levels, an output voltage level converter is designed for the

outputs. All these mentioned signal conditioning arrange-

ments have been implemented on a printed circuit board,

which served as a I/O buffer between the FPGA and the

system to be controlled.

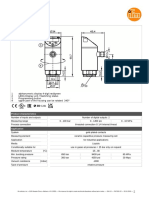

6 Xilinx FPGA implementation of the timed-transition

Before considering an asynchronous implementation of a

Petri net-based DECS for an experimental manufacturing

system, in this section let us explain the implementation of

a timed-transition using the schematic programming tool of

a Xilinx XC2S200 FPGA. The symbol of the implemented

timed-transition, called timed_t, is shown in Fig. 15.

Clock input is used to transfer the reference clock signal

into the timed_t symbol. This particular design is based on

D2 board; therefore the clock input is the 50MHz signal

provided on the D2 board. Inputs t_in1, etc., t_in5 are used

to check the pre and post conditions of the timed-transition

together with the firing condition. If all conditions are met,

then the predefined time-delay is started. Output t_out

issues an active signal (logic 0) when the time-delay has

elapsed. In order to establish a fixed time-delay there are

two groups of inputs: S inputs and Q inputs. S inputs are

used to choose one of the sixteen reference time-delays as

shown in Table 1. Q inputs are used to choose a number

(1 to 255) to be multiplied by the chosen reference time

delay as shown in Table 1. Therefore the fixed time delay is

obtained by multiplying the reference time delay with a

number from 1 to 255. For example, if S = S3S2S1S0 =

0110 and Q = Q7Q6Q5Q4Q3Q2Q1Q0 = 00001001, then

the time delay will be 167,772 ms 9 1.5 sec. So, the

minimum and the maximum time delays of this design are

2,621ms 1 = 2,621ms and 10,737s 255 6,084 hours,

respectively. Of course, shorter or longer time delays can be

achieved by modifying the design. vcc1 and vcc2 inputs are

used to define logic 1 levels, while gnd1 and gnd2 inputs

are used to define logic 0 levels necessary for S and Q

inputs.

Fig. 16 Schematic implementation of the timed-transition (inside view of the symbol timed_t)

Int J Adv Manuf Technol (2009) 41:595612 607

The schematic implementation of the timed-transition,

i.e., the inside view of the symbol timed_t, is shown in

Fig. 16. The symbols used within this design are as follows.

The divider is a frequency divider with the clock input

(50MHz signal) and sixteen outputs providing reference

clock signals as shown in Table 1. The symbol divider

and the inside view of the symbol divider are shown in

Fig. 17(a) and Fig. 17(b), respectively. M16_1E is a 16-to-1

multiplexer, M2_1 is a 2-to-1 multiplexer, and the CB4CE

is a 4-bit cascade binary counter with clock enable and

asynchronous clear. The pin functions of the CB4CE are

described as follows:

1. CE is the clock enable input, which is used to enable

the counter itself.

2. C stands for the clock

3. Q0, Q1, Q2, and Q3 constitute four data output bits.

They increment when CE is high during the low-to-

high clock transition.

4. CEO is the counter-enable output, which is used to

enable the next stage counter.

5. TC denotes terminal count. It is high when all Qs are

high.

6. CLR is the asynchronous clear. When CLR is high, all

other output are ignored and all Qs and TC outputs go

to logic zero level, independent of clock transition.

7 The experimental discrete manufacturing

system: problem description

The experimental discrete manufacturing system, shown in

Fig. 18, represents a component sorting and assembly

processes. The upper conveyor and lower conveyor are

driven by the upper conveyor motor (A3) and lower

conveyor motor (A4), respectively. A random selection of

metallic pegs and plastic rings are placed on the upper

conveyor. The rings and pegs need to be identified and

separated. This is done by two sensors, a proximity sensor

(B4) and an infra-red reflective sensor (B1). By using these

two sensors a distinction can be made between the peg and

the ring. By means of the sort solenoid (A0), plastic rings

can be ejected down the assembly chute, which can have up

to five plastic rings. Metallic pegs, meanwhile, continue on

the upper conveyor and are deflected down the feeder

chute. The feeder chute automatically feeds pegs onto the

lower conveyor. An infrared emitter/detector (B0) is used to

determine whether or not the assembly area is empty. If it is

empty, the assembly solenoid (A1) is used to dispense a

ring from the assembly chute into the assembly area. The

assembly area is positioned just above the lower conveyor

and, when a metallic peg passes, the peg engages with the

hole in the ring and the two components are assembled. The

lower conveyor is used to carry assembled components into

Fig. 17 a) The symbol divider, b) Inside view of the symbol divider

608 Int J Adv Manuf Technol (2009) 41:595612

the collection tray. For the sake of simplicity, it is assumed

that the assembly chute can have only one ring at a time. It

is also assumed that when the system is switched on, both

the upper conveyor motor and the lower conveyor motor

are switched on automatically.

8 SAPN model of the discrete event control system

Safe automation Petri net (SAPN) model of the discrete

event control system for the experimental manufacturing

system satisfying the specifications is shown in Fig. 19. In

the SAPN, there are ten places, P = {p1, p2, ..., p5, p1, p2, ...,

p5} and seven transitions, T = {t1, t2, ..., t7}, with which

firing conditions c

1

B1, c

2

B1 ^ B4, c

3

B1, c

4

= 0,

c

5

B0, c

6

= 1, c

7

= 1, are associated, respectively. Note

that transitions t3, t4 and t5 are timed transitions with time

delays 1.5 sec., 0.7 sec. and 2.5s, respectively. Places p4

and p4 represent the off and on states of the sort solenoid,

respectively. Likewise, places p5 and p5 represent the off

and on states of the assembly solenoid. A token each in

places p3, p2 and p1, represent the available spaces in the

sort area, in the assembly chute and in the assembly area,

respectively. A token in places p3, p2 and p1 depicts the

presence of a plastic ring in the sort area, in the assembly

chute and in the assembly area, respectively. Initially, both

solenoids are off and there are no plastic rings in the

manufacturing system. It can be verified that the SAPN

model is safe, live and reversible. (t2): When there is no

ring at the sort area, i.e., M p3

1, and the presence of a

ring is detected, i.e., c

2

B1 ^ B4, transition t2 fires by

removing the token from p3 and by depositing a token into

p3. This means that there is a ring at the sort area, i.e., M

(p3) = 1. When there is a ring at the sort area either it clears

the sort area through transition t1 or it is put into the

assembly chute through transition t3. (t1): If there is a ring

at the sort area, i.e., M(p3) = 1, the sort solenoid is off, i.e.,

M p4

1, and the absence of a ring is detected, i.e., c

1

B1 then transition t1 fires by removing the token from p3

and by depositing a token in p3. This means that the ring

cleared the sort area. (t3): If there is a ring at the sort area,

i.e., M(p3) = 1, the sort solenoid is on, i.e., M(p4) = 1, there

is space in the assembly chute, i.e., M p2

1, and the

absence of a ring is detected, i.e., c

3

B1, then timed-

transition t3 is being fired for 1.5 s, after which the ring at

ejected from the sort area into the assembly chute, i.e., the

tokens are removed from places p3, p4 and, p2 and a token

each is deposited into places p2, p3 and p4. This means that

Fig. 18 The experimental

discrete manufacturing system

Int J Adv Manuf Technol (2009) 41:595612 609

the ring at the sort area is put into the assembly chute by

means of the sort solenoid and this process takes 1.5 sec.

(t4): If there is a ring in the assembly chute, i.e., M(p2) = 1,

there is space at the assembly area, i.e., M p1

1, the

assembly solenoid is on, i.e., M(p5) = 1, and the presence

of a ring is detected, i.e., c

4

= B1, then timed-transition t4 is

being fired for 0.7 sec., after which the ring is dispensed

from the assembly chute to the assembly area, i.e., the

tokens are removed from places p2, p5 and and p1 a token

each is deposited into places p1, p2 and p5. (t5): If there is

a ring at the assembly area, i.e., M (p1) = 1, and a peg

engages with the hole in the ring, i.e.,

c

5 B0, then it takes

2.5 sec. for the ring and the peg to be assembled and to

clear the assembly area. After this, there is space at the

assembly area, i.e., M (p1) = 0 and M p1

1. Action A0

is assigned to p4. When there is a token in p4, A0 is 1

which is used to switch the sort solenoid on. (t6): If there is

a ring at the sort area, i.e., M(p3) = 1, there is space in the

assembly chute, i.e., M p2

1, and the sort solenoid is

off, i.e., M p4

1, then the sort solenoid is switched on,

by removing the token from p4 and by depositing a token

in p4. Action A1 is assigned to p5. When there is a token in

p5, A1 is 1 which is used to switch the assembly solenoid on.

(t7): If there is a ring in the assembly chute, i.e., M(p2) = 1,

there is space in the assembly area, i.e., M p1

1, and

the assembly solenoid is off, i.e., M p5

1, then the

assembly solenoid is switched on, by removing the token

from p5 and by depositing a token in p5.

9 Asynchronous digital hardware implementation

of the SAPN model

The SAPN model of the DECS shown in Fig. 19 was

converted into the related schematic using the proposed

direct translation method. The obtained asynchronous

digital hardware schematic of the SAPN is shown in

Fig. 20. On board 50 MHz clock signal is used to obtain

the necessary time delays. After converting the SAPN

model into the asynchronous digital hardware schematic

shown in Fig. 20, this design was implemented by using

Xilinx Project Navigator 6.3.i software as a schematic

program. The schematic program was then downloaded into

the Xilinx Spartan 2 XC2S200 FPGA of the D2 develop-

ment board and the experimental discrete manufacturing

system shown in Fig. 18 has been controlled successfully.

The following shows the used system resources of the

XC2S200 FPGA for the implementation of the controller.

10 Design summary

11 Conclusions and further research

In this paper, a new method has been proposed for the

digital hardware implementation of Petri net-based specifi-

cations. The purpose of this paper has been to introduce a

new discrete event control system paradigm, where the

control system is modeled with extended Petri nets and

implemented as an asynchronous controller using circuit

elements. When compared with the existing software and

hardware-based synchronous implementations, the asyn-

chronous hardware-based implementation method proposed

in this paper offers an alternative approach for the

implementation of discrete event controllers. It is expected

that the discrete event controllers obtained by the proposed

method would be very useful for time-critical-systems,

where the decision speed offered by the discrete event

controller is required to be much faster than the controlled

process. An experimental manufacturing system has been

used to show the applicability of the proposed method to

t1 t2

t5

p1

t3

t4

t6

t7

p3

T1

T2

1 = B1

2 = B1 B4

3 = B1

4 = B0

5 = B0

6 = 1

7 = 1

T1: 1.5 sec.

T2: 0.7 sec.

T3: 2.5 sec.

p4 ==> A0

p5 ==> A1

1

2

3

4

5

7

6

p1

p2

p3

p2

p4

p4

p5

p5

T3

Fig. 19 Safe automation Petri net (SAPN) model of discrete event

control system for the experimental manufacturing system satisfying

the specifications

Logic utilization:

Number of slice flip flops: 155 out of 4,704 3%

Number of four input LUTs: 194 out of 4,704 4%

610 Int J Adv Manuf Technol (2009) 41:595612

real-time control of DESs. Although this experimental

manufacturing system can easily be controlled by much

slower software or hardware-based synchronous implemen-

tations, it is just utilized to show the applicability of the

proposed method. The implementation of the controller has

been accomplished by using a Xilinx Spartan 2 XC2S200

FPGA, having 143 user I/Os and 200,000 system gates. The

system performance of the Xilinx Spartan 2 XC2S200

FPGA is supported up to 200 MHz. The design example

considered in this paper has been implemented by using

less than 5% of the system resources. The new generation

of FPGAs offer over 1000 user I/Os and more than

8 million system gates and their system performance is

supported for over 500 MHz. This means that with the help

of the technique explained in this paper and with the new

generation FPGAs, it will be possible to construct very high

speed, concurrent and asynchronous Petri net-based con-

trollers to control fast plants at low cost. The implementa-

tions considered in this paper are only for safe APNs. It is

possible to apply the proposed method to general APNs and

use up/down counters to represent places, instead of flip-

flops. The future research will be carried out in this

direction. As currently available FPGAs are more suitable

for synchronous implementations further research will also

be carried out on synchronous implementations of Petri net-

based specifications using FPGAs.

Acknowledgement This work has been carried out by using the

donated hardware (the Digilab 2 -D2- FPGA-based development board)

and WebPACK 6.3i software by Xilinx (http://www.xilinx.com/).

The authors would like to thank the AE and the anonymous

referees whose comments and suggestions greatly helped us to

improve the presentation and the quality of the paper.

Fig. 20 Asynchronous digital hardware schematic implementation of the SAPN shown in Fig. 18

Int J Adv Manuf Technol (2009) 41:595612 611

References

1. Uzam M (1998) Petri-Net-based supervisory control of discrete

event systems and their ladder logic diagram implementations.

PhD Dissertation, The University of Salford, UK, 395 pages

2. Murata T (1989) Petri nets: properties, analysis and application.

Proc of IEEE 77(4):541579 DOI 10.1109/5.24143

3. Hendry DC (1994) Heterogeneous Petri net methodology for

design of complex controllers. IEE Proc Comput Digt Tech 141

(5):293297 DOI 10.1049/ip-cdt:19941270

4. Stefano AD, Mirabella O (1994) A fast Petri-net-based sequence

controller implemented on a DSP. Int J of Adv Manuf Tech

9:375381 DOI 10.1007/BF01748482

5. Zhou MC, DiCesare F, Rudolph D (1992) Design and implemen-

tation of a Petri net based supervisor for a flexible manufacturing

system. Automatica 28(6):11991208 DOI 10.1016/0005

6. Zhou MC, Twiss E (1998) Design of industrial automated systems

via relay ladder logic programming and Petri nets. IEEE Trans. on

Systems, Man, and Cybernetics 28(1):137150 DOI 10.1109/

5326.661096

7. Peng SS, Zhou MC (2003) Sensor-based stage Petri net modeling

of PLC logic programs for discrete-event control design. Int J

Prod Res 41(3):629644 DOI 10.1080/0020754021000042364

8. Peng S-S, Zhou MC (2004) Ladder diagram and Petri net based

discrete-event control design methods. IEEE Trans. on Systems,

Man, and Cybernetic-Part C 34(4):523531

9. Uzam M, Jones AH (1998) Discrete event control system design

using automation Petri nets and their ladder diagram implemen-

tation. Int J of Adv Manuf Tech 14(10):716728 DOI 10.1007/

BF01438224

10. Yakovlev AV, Koelmans AB (1998) Petri nets and digital

hardware design. In: Reisig W, Rozenberg G (eds) LNCS,

Lectures on Petri Nets II: Applications, Advances in Petri Nets.

Springer, Heidelberg, pp 154236.

11. Chang N, Kwon WH, Park J (1998) Hardware implementation of

real-time Petri-net-based controllers. Control Eng Pract 6(7):889

895 DOI: 10.1016/S0967

12. Bulanch S, Brauchle A, Pfleiderer H-J, Kucerovsky Z (2002)

Design and implementation of discrete event control systems: a

Petri net based hardware approach. Discrete Event Dyn Syst 12

(3):287309

13. Varshavsky V, Kishinevsky M, Marakhovsky V, Peschansky V,

Rosenblum R, Taubin A, Tzirlin B (1990) Self-timed control of

concurrent processes. In: Varshavsky, VI (ed), Kluwer, Dordretch

14. Hollaar LA (1982) Direct implementation of asynchronous control

circuits. IEEE Trans Comput C-31(12):11331141 DOI 10.1109/

TC.1982.1675937

15. Varshavsky V, Marakhowsky V (1996) Hardware support for

discrete event coordination. In: Proc. of Int. workshop on

discrete event systems (WODES96), Edinburgh, UK, August

1996, (pp. 332340)

16. Varshavsky V, Marakhowsky V (1996) Asynchronous control

device design by net model behaviour simulation. LNCS, Vol.

1091: Proc. of the 17th Int. conf. on applications and theory of

Petri nets, Osaka, Springer, (pp. 497515)

17. Uzam M, Yaln MK, Avc M (2001) Digital hardware imple-

mentation of Petri net based specifications: direct translation from

safe automation Petri nets to circuit elements. In: Proceedings of

the international workshop on discrete event systems design,

Przytok near Zielona Gora, Poland (pp. 2533)

18. Uzam M, Ko B, Gelen G, Aksebzeci BH (2005) Asynchronous

implementation of a Petri net based discrete event control system

using a Xilinx FPGA. In: Proceedings of the 35th Inter. Conf. on

computers and industrial engineering, Istanbul, Turkey, June 20

22, vol. II, (pp. 20252030)

19. Xilinx (2003) Spartan-II 2.5V FPGA Family: Complete data

sheet, DS0011, http://www.xilinx.com/

20. Uzam M (2006) General purpose, cheap and flexible contact

debouncer. Electron World 112(1848):4148

612 Int J Adv Manuf Technol (2009) 41:595612

You might also like

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Philips+Chassis+TPM18 6LDocument90 pagesPhilips+Chassis+TPM18 6LJackson FerreiraNo ratings yet

- Worksheet 13 PDFDocument4 pagesWorksheet 13 PDFVijay Bhaskar50% (2)

- Sem102 Manual 1 PDFDocument11 pagesSem102 Manual 1 PDFricardo rodriguezNo ratings yet

- Electrical O&M ManualDocument28 pagesElectrical O&M ManualSopsky SalatNo ratings yet

- 1482267279amasadoras Univex Greenline FichaDocument2 pages1482267279amasadoras Univex Greenline FichaAdriana GalindoNo ratings yet

- Fixed Gas Detector Instruction Manual SI-1000Document21 pagesFixed Gas Detector Instruction Manual SI-1000Vũ Thiên ÂnNo ratings yet

- Buchholz Relay in Transformers (Working Principle) - Electrical4UDocument5 pagesBuchholz Relay in Transformers (Working Principle) - Electrical4UHarsh PatelNo ratings yet

- E-Wallet: Paper Presentation OnDocument7 pagesE-Wallet: Paper Presentation OnSiddhartha Choudary100% (1)

- Introduction to DSP systems, pipelining and parallel processingDocument1 pageIntroduction to DSP systems, pipelining and parallel processingNatheswaranNo ratings yet

- Vec 1180 KDocument35 pagesVec 1180 Kyu3zaNo ratings yet

- 8 isolated DC output module with optical isolation and diode protectionDocument1 page8 isolated DC output module with optical isolation and diode protectionDelshad DuhokiNo ratings yet

- SFC Start-Up Inverter of Gas Turbo-Sets: Integrated Compact UnitsDocument11 pagesSFC Start-Up Inverter of Gas Turbo-Sets: Integrated Compact Unitsfaiz fakhruroziNo ratings yet

- Degaussing Coil in CRT TelevisionDocument2 pagesDegaussing Coil in CRT TelevisionSanie D. AbarrientosNo ratings yet

- Comparing signals with comparatorsDocument4 pagesComparing signals with comparatorswojakNo ratings yet

- DatasheetDocument56 pagesDatasheetrajkumarmalathiNo ratings yet

- pdp8 DocDocument18 pagespdp8 DocalmeviNo ratings yet

- Graphics LCD Interfacing With Armv7 LPC 2148: Embedded System Design Mini ProjectDocument17 pagesGraphics LCD Interfacing With Armv7 LPC 2148: Embedded System Design Mini ProjectKiran BogamNo ratings yet

- JVC Car Stereo KD-S595 Service ManualDocument42 pagesJVC Car Stereo KD-S595 Service ManualAnonymous j5apk2AumNo ratings yet

- Nivotemp NT 64: Level and Temperature Switch With Display NV64DDocument6 pagesNivotemp NT 64: Level and Temperature Switch With Display NV64DSamad A BakarNo ratings yet

- R740 Tech GuideDocument80 pagesR740 Tech GuideRendy AjisokoNo ratings yet

- 4.catalogue Mog-Cat-13-ExDocument11 pages4.catalogue Mog-Cat-13-ExNicolas GallegosNo ratings yet

- 3SU11000AB401FA0 Datasheet enDocument4 pages3SU11000AB401FA0 Datasheet enpatrykk11195No ratings yet

- XEnergy Technical Guide en 158487Document88 pagesXEnergy Technical Guide en 158487Cris_eu09No ratings yet

- Bennic (Bi-Polar Radial-Axial) N10 SeriesDocument3 pagesBennic (Bi-Polar Radial-Axial) N10 Seriesester853No ratings yet

- PN7092 Pressure Sensor DisplayDocument5 pagesPN7092 Pressure Sensor DisplayEslam YehiaNo ratings yet

- Aim: To Test Differentiator and Integrator Circuits Using Ua741op-AmpDocument8 pagesAim: To Test Differentiator and Integrator Circuits Using Ua741op-AmpAvinash Nandakumar100% (1)

- 6 16Document2 pages6 16Indira KarimovaNo ratings yet

- Jabra A120s User ManualDocument51 pagesJabra A120s User Manualapi-26157899No ratings yet

- Forward Converter Design and AnalysisDocument56 pagesForward Converter Design and AnalysisJeanTsunaNo ratings yet

- TRIO 50.0 TL OUTD US 480 - Rev.G PDFDocument4 pagesTRIO 50.0 TL OUTD US 480 - Rev.G PDFmarcosNo ratings yet