Professional Documents

Culture Documents

Layout Consideration and Circuit Solution To Prevent EOS Failure Induced by Latchup Test in A High-Voltage Integrated Circuits

Uploaded by

EliasA.Tiongkiao0 ratings0% found this document useful (0 votes)

21 views6 pages...

Original Title

06226839

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Document...

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

21 views6 pagesLayout Consideration and Circuit Solution To Prevent EOS Failure Induced by Latchup Test in A High-Voltage Integrated Circuits

Uploaded by

EliasA.Tiongkiao...

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 6

IEEE TRANSACTIONS ON DEVICE AND MATERIALS RELIABILITY, VOL. 14, NO.

1, MARCH 2014 493

Layout Consideration and Circuit Solution to Prevent

EOS Failure Induced by Latchup Test in a

High-Voltage Integrated Circuits

Hui-Wen Tsai, Student Member, IEEE, and Ming-Dou Ker, Fellow, IEEE

AbstractThis paper presented a practical industry case of

electrical overstress (EOS) failure induced by the latchup test

in high-voltage integrated circuits (ICs). By using proper layout

modication and additional circuit, the unexpected EOS failure,

which is caused by negative-current-triggered latchup test, can

be successfully solved. The new design with proposed solutions

has been veried in the 0.6-m 40-V Bipolar CMOS DMOS

(BCD) process to pass the test for at least 500-mA trigger current,

which shows high negative-current-latch-up immunity without

overstress damage, compared with the protection of only the guard

ring. Such solutions can be adopted to implement high-voltage-ap-

plicable IC product to meet the industry requirement for the mass

production of IC manufactures and applications.

Index TermsElectrical overstress (EOS), high-voltage CMOS,

latchup, regulator.

I. INTRODUCTION

L

ATCHUP is a common failure mechanism in CMOS

ICs related to the occurrence of low impedance path

between the supply and ground, which is triggered by over-

shooting/undershooting voltage or current perturbation to the

parasitic PNPN structure. The trigger source can come from

other place in the chip or the terminal of the PNPN structure

which was distinguished to external or internal latchup, respec-

tively [1][3]. When current perturbation is applied to the pin

of ICs to examine the latchup immunity, it can be positive

or negative direction during positive or negative current test

(I-test). The specication and methodology of the examination

have been specied in the JEDEC latchup test standard [4] and

generally adopted by IC industry for production qualication.

As the supply voltage increases while the chip is expected

to be conserved in HV ICs, the co-use of HV and LV de-

vices becomes one of the trends for HV SOC designs. In the

operation of HV environment, the high-voltage-tolerated pre-

regulator is usually required to serve as the interface between

HV and LV blocks and provides the necessary low supply

Manuscript received March 16, 2012; revised May 18, 2012 and June 17,

2012; accepted June 20, 2012. Date of publication July 6, 2012; date of current

version March 4, 2014. This work was supported in part by the National Science

Council (NSC), Taiwan, under Contract NSC 101-2221-E-009-141 and in part

by the Aim for the Top University Plan of the National Chiao Tung University

and the Ministry of Education, Taiwan.

H.-W. Tsai is with the Institute of Electronics, National Chiao Tung Univer-

sity, Hsinchu 300, Taiwan.

M.-D. Ker is with the Institute of Electronics, National Chiao Tung Uni-

versity, Hsinchu 300, Taiwan, and also with the Department of Electronic

Engineering, I-Shou University, Kaohsiung 84001, Taiwan (e-mail: mdker@

ieee.org).

Digital Object Identier 10.1109/TDMR.2012.2206391

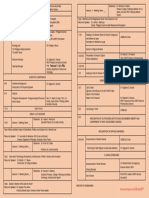

Fig. 1. Simplied circuit structure of a practical power regulator IC.

voltage to the inner low-voltage circuits. However, certain

node voltages in HV blocks as the HV pre-regulator may be

abnormal since the high-voltage drift Nwell (HVNW) junctions

in the HV devices are prone to the sink current brought by

the parasitic bipolar transistor, especially during the negative

I-test. Moreover, improper layout placement related with circuit

structure may cause misconduction between HV supply and

LV blocks. When voltage applied at the external supply is

higher than the tolerance of LV transistors, it can even lead to

ill function of ICs due to the electrical overstress (EOS) which

may cause permanent damages [5], [6] at the metal connections

or junctions of LV devices.

To increase the latchup immunity of the chips, guard ring

protection is often used to reduce the substrate current which

ows in the inner circuit blocks [7], [8]. Fabricate devices

surrounding with insulating oxide layer (trench) or lightly

doped epitaxial layers grown on heavily doped substrates can

also eliminate the sink current by breaking the parasitic bipolar

structures [9][11]. However, the protection of guard rings or

extra layers increases the chip area or the fabrication cost. Even

with the protection of guard rings, wider distance between the

trigger source at I/O pin and the inner circuit or inner guard

rings are still required [12], which may still be insufcient to

the HV devices with deep HVNW junctions.

In this work, a practical industry case of EOS damage

induced by the latchup negative I-test in a HV CMOS IC was

described. The proper layout modication, the additional circuit

solution, and the experimental latchup test have been veried in

silicon to illustrate the improvement.

1530-4388 2012 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission.

See http://www.ieee.org/publications_standards/publications/rights/index.html for more information.

494 IEEE TRANSACTIONS ON DEVICE AND MATERIALS RELIABILITY, VOL. 14, NO. 1, MARCH 2014

Fig. 2. Schematic of high-voltage-tolerable pre-regulator in this practical paper.

II. NEGATIVE I-TEST INDUCED EOS FAILURE WITH

ONLY GUARD RING PROTECTION

To operate at HV environment but maintain the compression

of chip area, a simplied structure for practical high-voltage-

tolerable IC has circuit blocks shown as Fig. 1. The high-

voltage-tolerable pre-regulator is composed of HV devices

or both HV and LV devices, which is used to generate the

necessary low supply voltage such as 3.3 V (at VAP node)

or 2 V (at VPD node) to the analog or digital LV inner

circuit, respectively. The high-voltage-tolerable pre-regulator in

the practical work is shown in Fig. 2. MHN1 to MHN4 of the

schematic in Fig. 2 are the HV NMOS transistors which can

tolerate drain-to-source voltage difference (|Vds|) up to 40 V

and MHP1 to MHP7 are the HV PMOS transistors with up

to 40-V tolerance of source-to-drain voltage difference (|Vsd|)

in a 40-V HV process. MN1, MN2, and MP1 are the 5-V LV

devices used to provide the necessary bias current and the com-

pensation for stability. The high-voltage-tolerable pre-regulator

is composed of a two-stage amplier with feedback connection

as a typical LDO structure [13]. With the high-voltage-tolerable

pre-regulator, the IC can operate normally under the desired

HV supply such as 40 V. However, the practical packaged IC

is still damaged during latchup test even guard ring protection

had been placed between the HV I/O PAD and inner circuit

blocks. After applying negative I-test with 100-mA sink current

at some I/O PAD (as the PAD 1 shown in Fig. 1) with the high

supply voltage (such as 30 V) over the tolerable range of LV

devices, the practical work shows high abnormal current (up to

mA) from the supply VDD to ground as depicted in Fig. 3(b)

compared with the normal result (under 120 uA) before the

test as shown in Fig. 3(a). The die photo of the damaged IC is

shown in Fig. 4(a) and the damages apparently happened at the

drain terminals of MHP6 and MHP7 which are the interfaces

of high-voltage-tolerable pre-regulator to the LV digital blocks.

Fig. 4(b) shows the partial layout presented with only HVNW

and P+implement layers that are nearby the PAD1 in Fig. 4(a).

The widths of the HVNW junctions in the guard ring and the

transistors (including MHN1, MHN2, and MHN4) are 15.9 m

(W1) and 9.2 m (W2), respectively, as shown in Fig. 4(b).

The minimum distances between the edges from the HVNW

junction at PAD 1 to the HVNW junctions in the guard ring, the

transistor MHN1, and MHN4 are also shown in Fig. 4(b), which

are 20 m (D1), 118 m (D2), and 154 m (D3), respectively.

The reasons for the damages can be attributed to the short-

through conductions from the supply voltage VDD to ground

GND. Such paths are caused by the conductions of the transis-

tor MHP6 and MHP7. The parasitic NPN structures from the

I/O PAD to p-type substrate and internal HVNW layer of the

HVNMOS transistors (such as the input pair of the amplier)

are shown as Fig. 5(a). With the consideration to avoid the

negative impact from mismatch, HV NMOS MHN1 and MHN2

are arranged as MHN1MHN2MHN2MHN1 placement in

layout, and the two multipliers of MHN2 share the same drain

area to make the die more compressive. The simplied cross-

section view is shown in Fig. 5(b). When a large negative

current is applied at the I/O PAD [as the PAD 1 depicted in

Fig. 4(a)], the parasitic NPN structure attributed by the guard

ring is triggered and expected to conduct the most current to

the I/O PAD. However, there is still some current induced by

another parasitic NPN structure. The node voltages such as the

drain terminals of HV NMOS MHN1, 2, and 4 are pulled down

due to the current ow induced by the sink current source,

which is through the N+-HVNW junctions to the substrate

as well as the I/O PAD to the source. The amount of induced

current is correlated with the amount of sink current at the

I/O PAD, the related location of the current source to the

TSAI AND KER: LAYOUT CONSIDERATION AND CIRCUIT SOLUTION TO PREVENT EOS FAILURE 495

Fig. 3. Measured supply voltage and related current for the original design

(without the modication) (a) before and (b) after the negative I-test applying

at the PAD 1 with 100-mA sink current during the latchup test.

affected victim, and the junction area of the parasitic structure.

Moreover, due to the layout structure shown in Fig. 5(a), the

area of the HVNW junction connected to the drain terminal of

MHN2 is double compared with that connected to the drain

terminal of MHN1. Therefore, more current are sunk at the

drain terminal of MHN1 and the voltage of gate terminal for

MHP6 is pulled low which leads to the conduction of MHP6

to cause the overstress failure in the practical work as shown

in Fig. 4(a).

III. RE-DESIGN FOR ELIMINATION OF LATCHUP TEST

INDUCED EOS FAILURE

A. Modication of Layout Placement

To prevent such EOS problem in the above mentioned HV

IC, the simplied improper layout placement for the input pair

MHN1 and MHN2 of the original work is shown in Fig. 6(a).

The proper modication with replacement in layout by metal

re-connection is shown in Fig. 6(b). The locations of transistor

MHN1 and MHN2 are exchanged so that the drain terminal of

MHN1 is connected to double area of HVNW junction than

that of MHN2. By such replacement, more current can be sunk

at the node connected to the drain terminal of MHN1 than

Fig. 4. (a) Die photo of the practical IC fabricated in 0.6-m 40-V BCD

process with negative I-test induced EOS damages. (dotted line) In guard ring

connected to VDD. (b) The partial layout presented with only HVNW and

P+ implement layers to show the widths and minimum distances of HVNW

junctions from the PAD 1 to the guard ring, transistor MHN1, and MHN4.

that of MHN2. Due to the current mirror structure, the sink

current at the drain terminal of MHN1 drawn by the parasitic

NPN is turned into the source current at the drain terminal of

MHN2 through MHP1 to MHP2 which is also above double

than the sink current. Thus, not only the sink current of the drain

terminal for MHN2 can be compensated, but also the voltage

at the gate terminal of MHP6 is pulled high to obstruct the

conductive path caused by MHP6 from external supply VDD

to inner supply VAP and VPD.

B. Modication With Additional Sensing and

Compensation Circuit

Another method with circuit solution is proposed as shown

in Fig. 7. The additional circuit is designed to compensate the

496 IEEE TRANSACTIONS ON DEVICE AND MATERIALS RELIABILITY, VOL. 14, NO. 1, MARCH 2014

Fig. 5. (a) Parasitic NPN structures from I/O PAD to p-type substrate and

internal HVNW. (b) Simplied cross-section view to show the parasitic NPN

structure.

induced sink current from I/O PAD to the HVNW junction

and also the drain terminal of HV NMOS transistors during

latchup negative I-test. The proposed circuit contains a sensing

part (implemented with HVNMOS MHN5 as well as a resistor)

and a current mirror part (implemented with HVPMOS as

MHP8 MHP10) to compensate the induced sink current.

The HVNMOS MHN5 is gate grounded to turn off HVPMOS

MHP8 10 in the normal operation, but offers a sink current

by the parasitic NPN structure when the large negative current

at PAD 1 is sensed. When induced sink current is larger, the

related sensing current is larger and the source to gate voltage of

the diode connected HVPMOS MHP8 is also larger to produce

more mirrored current at the HVPMOS MHP9 and MHP10.

By connecting the drain terminals of the HVPMOS transistors

as MHP9 and MHP10 to the nodes as the gate terminals of

MHP6 and MHP7, the latchup-test-induced sink current can be

compensated. Thus, the gate voltages of MHP6 and MHP7 were

prevented from pulled low to trigger low impedance paths from

external HV supply to inner LV supply. The sensing current

can be used to produce a sink current through NMOS current

mirror or a digital enable signal to launch protection mechanism

to prevent the effect brought by the mistrigger of certain logic

circuit under negative-current-triggered latchup test.

Fig. 6. (a) Improper layout placement for the input pair composed of

MHN1and MHN2 in the original work. (b) Proper modication of the revised

design with replacement in layout by metal re-connection.

C. Experimental Results

The proposed layout replacement and additional circuit so-

lution have been veried with 0.6-m 40-V BCD process in

the revised version of the HV IC. Fig. 8 shows the measured

results of certain signals in the original IC to depict the root

cause of the EOS problem, as shown in Figs. 3(a) and 4(a).

External voltage VDD is given as 6 V to perform the overstress

situation without damaging the IC directly. When a 30-mA

sink current is applied at the PAD 1, the inner supply voltage

VAP is pulled up from the normal value (3.3 V) to the

voltage near VDD. When a larger sink current is used, the

problem remains. The drain voltage of MHN1 is also shown

in Fig. 8 to see the effected drain voltage of MHN1 with sink

current through HVNW junction to HVNMOS devices. Since

the inner supply voltage VAP from the pre-regulator is pulled

up to VDD after the negative I-test, the 5-V LV blocks or

the metal line may have reliability problem with high voltage

at VDD. It is even damaged directly when the applied voltage

at VDD is higher than the breakdown voltage of LV junctions

such as 12 V in the 0.6-m 40-V BCD process. With the

exchange of layout locations, the inner supply voltage VAP will

be pulled low directly shown as Fig. 9 to prevent the damage

due to the electrical overstress. The sink current at the PAD 1

is increased to examine if the solution is suitable to prevent the

EOS problem for negative I-test with even large current over

500 mA.

The additional sensing and compensation circuits are also

applied to the revised version to verify the results shown in

Fig. 10. While current starts to be sunk at the PAD 1, the inner

supply voltage (VAP) in Fig. 10 is also pulled down to prevent

the overstress to the LV blocks. For the devices of the input

TSAI AND KER: LAYOUT CONSIDERATION AND CIRCUIT SOLUTION TO PREVENT EOS FAILURE 497

Fig. 7. Schematic of the revised design with new proposed sense and compensation circuit.

Fig. 8. Measured inner supply voltage when a 30-mA sink current is applied

at the PAD 1 of the original IC without modication.

Fig. 9. Measured inner supply voltage with a 500-mA sink current at the

PAD 1 of the revised design with proper layout at input pair of the pre-regulator.

pair, proper layout is already enough to eliminate the overstress

problem happened at the output of the HV pre-regulator as VAP

in Fig. 2. However, for the case of the damage happened at the

node as VPD in Fig. 2, the solution of additional sensing and

Fig. 10. Measured inner supply voltage with a 700-mA sink current at the

PAD 1 of the revised design with proper layout at input pair of the pre-regulator.

compensation circuits are also required at the gate of MHP7 to

prevent the conduction of MHP7 during negative I-test.

Fig. 11(a) shows the measured external supply current

I(VDD) corresponding to the related supply voltage (VDD) for

the revised design with both modications before the negative

I-test. Fig. 11(b) presents the measured results after 100-mA

sink current is applied at VDD during negative I-test at PAD

1. As shown in these two gures, the revised design with the

modications has almost the same IV curve before and after

the test, whereas the original design without the modications

suffers large leakage at supply pin which causes the overstress

damage. Therefore, both the analog and digital supply voltages

of the LV circuits in the revised design can be prevented from

the EOS problem to ensure qualied latch-up immunity.

IV. CONCLUSION

The proposed modications to solve the EOS problem in-

duced by the negative I-test have been veried successfully in

0.6-m 40-V BCD process. With proper layout replacement

and additional circuit, the inner power VAP and VPD are all

498 IEEE TRANSACTIONS ON DEVICE AND MATERIALS RELIABILITY, VOL. 14, NO. 1, MARCH 2014

Fig. 11. Measured external supply current I(VDD) to the related supply

voltage (VDD) for the revised design with the modications (a) before and

(b) after the negative I-test with 100-mA sink current at PAD 1.

prevented from conduction to the HV external supply VDD

in the revised design. With the proposed solutions, the imple-

mented chips pass at least 500-mA latchup test. The proposed

solutions in this work are useful to improve the robustness of

the circuit in HV environment and also remain qualied latchup

immunity of HV circuits in SoC applications.

ACKNOWLEDGMENT

The authors would like to thank Leadtrend Technology

Corp. for the support with chip fabrication, measurement, and

verications.

REFERENCES

[1] F. Farbiz and E. Rosenbaum, Modeling and understanding of external

latchup in CMOS technologiesPart I: Modeling latchup trigger cur-

rent, IEEE Trans. Device Mater. Reliab., vol. 11, no. 3, pp. 417425,

Sep. 2011.

[2] F. Farbiz and E. Rosenbaum, Modeling and understanding of external

latchup in CMOS technologiesPart II: Minority carrier collection ef-

ciency, IEEE Trans. Device Mater. Reliab., vol. 11, no. 3, pp. 426432,

Sep. 2011.

[3] M.-D. Ker and S.-F. Hsu, Transient-Induced Latchup in CMOS Integrated

Circuits. Hoboken, NJ: Wiley, 2009.

[4] IC Latch-Up Test, JESD78D Std., 2011.

[5] I.-C. Lin, C.-J. Chao, M.-D. Ker, J.-C. Tsen, C.-T. Hsu, L.-Y. Leu,

Y.-L. Chen, C.-K. Tsai, and R.-W. Huang, Latchup test-induced failure

within ESD protection diodes in a high-voltage CMOS IC product, in

Proc. EOS/ESD Symp., 2004, pp. 160165.

[6] J.-C. Tseng, Y.-L. Chen, C.-T. Hsu, F.-Y. Tsai, P.-A. Chen, and

M.-D. Ker, Mechanismof snapback failure induced by the latch-up test in

high-voltage CMOS integrated circuits, in Proc. IEEE Int. Reliab. Phys.

Symp., 2008, pp. 625626.

[7] J. Quincke, Novel test structure for the investigation of the efciency of

guard rings used for I/O latchup prevention, in Proc. IEEE Int. Conf.

Microelectron. Test Struct., 1990, pp. 3539.

[8] T.-L. Hsu, Y.-C. Chen, H.-C. Tseng, V. Liang, and J.-S. Jan, Psub guard

ring design and modeling for the purpose of substrate noise isolation in

the SOC era, IEEE Electron Device Lett., vol. 26, no. 9, pp. 693695,

Sep. 2005.

[9] M. Pfost, P. Brenner, T. Huttner, and A. Romanyuk, An experimental

study on substrate coupling in bipolar/BiCMOS technologies, IEEE J.

Solid-State Circuits, vol. 39, no. 10, pp. 17551763, Oct. 2004.

[10] S. Voldman, Latchup. Hoboken, NJ: Wiley, 2007.

[11] S.-F. Hsu and M.-D. Ker, Dependence of device structures on latchup

immunity in a high-voltage 40-V CMOS process with drain-extended

MOSFETs, IEEE Trans. Electron Devices, vol. 54, no. 4, pp. 840851,

Apr. 2007.

[12] M.-D. Ker and W.-Y. Lo, Methodology on extracting compact layout

rules for latchup prevention in deep-submicron bulk CMOS technology,

IEEE Trans. Semicond. Manuf., vol. 16, no. 2, pp. 319334, May 2003.

[13] G. A. Rincon-Mora, Analog IC Design With Low-Dropout Regulator.

New York: McGraw-Hill, 2009.

Hui-Wen Tsai (S07) was born in Taipei, Taiwan, in

1985. She received the B.S. degree in electrical en-

gineering from the National Chiao Tung University,

Hsinchu, Taiwan, in 2007, and the M.S. degree from

the dual degree program by Katholieke Universiteit

Leuven, Leuven, Belgium, and the National Chiao

Tung University, in 2008. She is currently working

toward the Ph.D. degree from the Institute of Elec-

tronics, National Chiao Tung University.

Her main research focus on the reliable and high-

performance circuit design.

Ming-Dou Ker (F08) received the Ph.D. degree

from the National Chiao Tung University, Hsinchu,

Taiwan, in 1993.

He was the Department Manager with the VLSI

Design Division, Computer and Communication Re-

search Laboratories, Industrial Technology Research

Institute, Hsinchu, Taiwan. Since 2004, he has been

a Full Professor with the Department of Electronics

Engineering, National Chiao Tung University. From

2008 to 2011, he was rotated to be Chair Professor

and Vice President of I-Shou University, Kaohsiung,

Taiwan. He is currently a Distinguished Professor with the Department of

Electronics Engineering, National Chiao-Tung University, Taiwan. He was

the Executive Director of the National Science and Technology Program on

System-on-Chip (NSoC), Taiwan from 2010 to 2011 and is currently the

Executive Director of the National Science and Technology Program on Nano

Technology, Taiwan for 20112014. In the technical eld of reliability and

quality design for microelectronic circuits and systems, he has published over

450 technical papers in international journals and conferences. He has proposed

many solutions to improve the reliability and the quality of integrated circuits

(ICs). He is the holder of 194 U.S. patents and 167 Taiwan patents. He had been

invited to teach and/or to consult the reliability and quality design for ICs by

hundreds of design houses and semiconductor companies in the worldwide IC

industry. His current research interests include reliability and quality design for

nanoelectronics and gigascale systems, as well as the biomimetic circuits and

systems for intelligent prosthesis.

Prof. Ker has served as a member of the Technical Program Committee and

the Session Chair of numerous international conferences for many years. He

served as the Associate Editor for the IEEE TRANSACTIONS ON VERY LARGE

SCALE INTEGRATION (VLSI) SYSTEMS from 2006 to 2007. He was selected

as the Distinguished Lecturer in the IEEE Circuits and Systems Society from

2006 to 2007 and in the IEEE Electron Devices Society from 2008 to 2012.

He was the Founding President of Taiwan ElectroStatic Discharge Association.

Since 2012, he has been the Editor of IEEE TRANSACTIONS ON DEVICE AND

MATERIALS RELIABILITY.

You might also like

- UVM Interview QuestionsDocument8 pagesUVM Interview QuestionsPriyank Patel100% (2)

- Analysis of Transfer Touch Voltages in Low-Voltage Electrical InstallationsDocument12 pagesAnalysis of Transfer Touch Voltages in Low-Voltage Electrical InstallationsMenaNo ratings yet

- Insulation Co-ordination in High-voltage Electric Power SystemsFrom EverandInsulation Co-ordination in High-voltage Electric Power SystemsRating: 4.5 out of 5 stars4.5/5 (5)

- Automated Broad and Narrow Band Impedance Matching for RF and Microwave CircuitsFrom EverandAutomated Broad and Narrow Band Impedance Matching for RF and Microwave CircuitsNo ratings yet

- Philippine Electronics Code - Volume 1Document28 pagesPhilippine Electronics Code - Volume 1janaisha_bai7170100% (3)

- VLSI Micro-Project Report Group A PDFDocument14 pagesVLSI Micro-Project Report Group A PDFganesh SawantNo ratings yet

- An SCR-Incorporated BJT Device For Robust ESD Protection With High Latchup Immunity in High-Voltage TechnologyDocument11 pagesAn SCR-Incorporated BJT Device For Robust ESD Protection With High Latchup Immunity in High-Voltage TechnologydabalejoNo ratings yet

- Fully Integrated Power Supply Design For Wireless Biomedical ImplantsDocument6 pagesFully Integrated Power Supply Design For Wireless Biomedical ImplantsDon ReloNo ratings yet

- Implementation and Performance Evaluation of A Fast Dynamic Control Scheme For Capacitor-Supported Interline DVRDocument14 pagesImplementation and Performance Evaluation of A Fast Dynamic Control Scheme For Capacitor-Supported Interline DVRRamphani NunnaNo ratings yet

- Slup 228Document32 pagesSlup 228cohama4No ratings yet

- Design and Testing of High Voltage High Frequency Transformer 0.6kV - 60kV For Power of 60kWDocument7 pagesDesign and Testing of High Voltage High Frequency Transformer 0.6kV - 60kV For Power of 60kWwessamNo ratings yet

- Safety Compl - SS Earthing DesignDocument5 pagesSafety Compl - SS Earthing DesignRahul SinganiaNo ratings yet

- 2006 Longitudinal InductionDocument8 pages2006 Longitudinal InductionmaheshNo ratings yet

- Bonding SystemDocument13 pagesBonding SystemHilman NurzenNo ratings yet

- Testing and evaluating grounding systems in urban areasDocument9 pagesTesting and evaluating grounding systems in urban areashaNo ratings yet

- 2015-IJ-AMM.771.145 Designing of A High Voltage Power Supply For Electrospinning Apparatus Using A High Voltage Flyback Transformer (HVFBT)Document4 pages2015-IJ-AMM.771.145 Designing of A High Voltage Power Supply For Electrospinning Apparatus Using A High Voltage Flyback Transformer (HVFBT)Dian Ahmad HapidinNo ratings yet

- Earthing System Commissioning, Current Injection Test CIT MethodDocument9 pagesEarthing System Commissioning, Current Injection Test CIT MethodvolkanNo ratings yet

- Chapter 5 - Analog Integrated Circuit Design by John ChomaDocument95 pagesChapter 5 - Analog Integrated Circuit Design by John ChomaAriana Ribeiro LameirinhasNo ratings yet

- 05735442Document2 pages05735442kothari_rubinNo ratings yet

- DC Pole To Pole Short Circuit Fault Analysis in VSC-HVDC Transmission SystemDocument6 pagesDC Pole To Pole Short Circuit Fault Analysis in VSC-HVDC Transmission SystemHarold De ChavezNo ratings yet

- Stacked High Voltage Switch Based S I C Vjfets: ISPSD 2003, April 14-17, UKDocument4 pagesStacked High Voltage Switch Based S I C Vjfets: ISPSD 2003, April 14-17, UKМилан ЛукићNo ratings yet

- Epe 2013111515302022Document5 pagesEpe 2013111515302022qais652002No ratings yet

- Power Upgrading of Transmission Lines by Combining Ac & DCDocument68 pagesPower Upgrading of Transmission Lines by Combining Ac & DCrashidmd42100% (2)

- A Comparison of VLF and 50Hz Field Testing of MV Cables PDFDocument10 pagesA Comparison of VLF and 50Hz Field Testing of MV Cables PDFGualadrakeNo ratings yet

- Philips - High Voltage Bipolar TransistorDocument41 pagesPhilips - High Voltage Bipolar TransistordanielsturzaNo ratings yet

- Circuit Design Concepts For Esd Protection 2008 PDFDocument32 pagesCircuit Design Concepts For Esd Protection 2008 PDFNguyen Van ToanNo ratings yet

- Impact of Modern Electronic Equipment On The Assessment of Network Harmonic ImpedanceDocument9 pagesImpact of Modern Electronic Equipment On The Assessment of Network Harmonic ImpedancedougmadasNo ratings yet

- Electromagnetic Disturbances: XIII International Conference OnDocument0 pagesElectromagnetic Disturbances: XIII International Conference Ongvsbabu63No ratings yet

- Neutral Point Clamped MOSFET Inverter WithDocument13 pagesNeutral Point Clamped MOSFET Inverter WithkrishnaNo ratings yet

- Voltage-To-Frequency Converter With High Sensitivity Using all-MOS Voltage Window ComparatorDocument6 pagesVoltage-To-Frequency Converter With High Sensitivity Using all-MOS Voltage Window ComparatorThony Tho'il PrasetyoNo ratings yet

- Simulation Effect of Switching Surge On The Overhead Line (With and Without Surge Arrestor)Document37 pagesSimulation Effect of Switching Surge On The Overhead Line (With and Without Surge Arrestor)Nafisah AbdullahNo ratings yet

- Combined Instrument TrasformersDocument6 pagesCombined Instrument Trasformersraghavendran raghuNo ratings yet

- Wyatt Na Ddg12Document6 pagesWyatt Na Ddg12Antonio BergnoliNo ratings yet

- 400V DC plug socket characteristicsDocument6 pages400V DC plug socket characteristicsRaspy ReddyNo ratings yet

- A 7V-To-30V-Supply 190A Per Μs Regulated Gate Driver in a 5V CMOS Compatible ProcessDocument17 pagesA 7V-To-30V-Supply 190A Per Μs Regulated Gate Driver in a 5V CMOS Compatible Processoht993No ratings yet

- A New Proposal For Power Quality and CustomDocument10 pagesA New Proposal For Power Quality and CustomChetan SoniNo ratings yet

- EDOC-Damped AC For CommissioningDocument19 pagesEDOC-Damped AC For CommissioningEl Comedor BenedictNo ratings yet

- Comparison of shunt capacitor, SVC, and STATCOM for static voltage stabilityDocument15 pagesComparison of shunt capacitor, SVC, and STATCOM for static voltage stabilityJayaprakash DasNo ratings yet

- Paper9 Zellagui PDFDocument17 pagesPaper9 Zellagui PDFGunjan GaganNo ratings yet

- 2008 Yin Man Development of Single-Transistor-Control LDO PDFDocument10 pages2008 Yin Man Development of Single-Transistor-Control LDO PDFrahmanakberNo ratings yet

- 2013 03 PotM Monitoring of 420 KV XLPE Cable System in Underground Tunnel ENU PDFDocument5 pages2013 03 PotM Monitoring of 420 KV XLPE Cable System in Underground Tunnel ENU PDFreza515heiNo ratings yet

- Low Voltage Low Power Pipelined ADC For Video Applications: Hameed Zohaib Samad, Patri Sriharirao, K. SarangamDocument5 pagesLow Voltage Low Power Pipelined ADC For Video Applications: Hameed Zohaib Samad, Patri Sriharirao, K. SarangamGayathri SrinivasaNo ratings yet

- EC Lecture 5 2020s2 - Circuit AnalysisDocument6 pagesEC Lecture 5 2020s2 - Circuit Analysisashfaq4985No ratings yet

- PD Measurement For HV Cable SystemDocument7 pagesPD Measurement For HV Cable SystemMichael Parohinog GregasNo ratings yet

- Dynamic Testing of An IEC 61850 Based - JPEE - 2014091714182282Document10 pagesDynamic Testing of An IEC 61850 Based - JPEE - 2014091714182282Diego Quintana ValenzuelaNo ratings yet

- EI2301 IE Notes FullDocument103 pagesEI2301 IE Notes FullVenkatesan SatheeswaranNo ratings yet

- Analytic Approximation of Fault Current Contributions From Capacitive Components in HVDC Cable NetworksDocument8 pagesAnalytic Approximation of Fault Current Contributions From Capacitive Components in HVDC Cable NetworksFelix GamarraNo ratings yet

- 2021 A High-Efficiency Self-Synchronous RF-DC Rectifier With A Fixed Broadband Phase OffsetDocument4 pages2021 A High-Efficiency Self-Synchronous RF-DC Rectifier With A Fixed Broadband Phase OffsetAzrinYunusNo ratings yet

- Wide Input Power Range X - Band Rectifier With Dynamic Capacitive Self-CompensationDocument4 pagesWide Input Power Range X - Band Rectifier With Dynamic Capacitive Self-Compensationsaeed gholamiNo ratings yet

- Base PaperDocument11 pagesBase PaperDhanush NNo ratings yet

- A Robust, High-Speed and Energy-Efficient Ultralow-Voltage Level ShifterDocument5 pagesA Robust, High-Speed and Energy-Efficient Ultralow-Voltage Level ShifterVani YamaniNo ratings yet

- Cao 2021Document5 pagesCao 2021blackyNo ratings yet

- 7225-Ichve2010 - Jankov - HVDC System Performance With A Neutral Conductor - V1Document5 pages7225-Ichve2010 - Jankov - HVDC System Performance With A Neutral Conductor - V1Anonymous OpLDOPNo ratings yet

- Chapter-2 Generation of High VoltageDocument20 pagesChapter-2 Generation of High VoltageYuusuf AbdirizakNo ratings yet

- Photovoltaic Cell AnDocument4 pagesPhotovoltaic Cell AnSreekanth SunkeNo ratings yet

- Vlsi Design: (EL-486) For B.E (EL)Document33 pagesVlsi Design: (EL-486) For B.E (EL)Deepak PatelNo ratings yet

- Hybrid Passive-Overcurrent Relay For Detection of Faults in Low-Voltage DC GridsDocument10 pagesHybrid Passive-Overcurrent Relay For Detection of Faults in Low-Voltage DC GridsKarthikkeyan SNo ratings yet

- Chapter 1-3 Construction of Auto-TransformerDocument20 pagesChapter 1-3 Construction of Auto-TransformerChristopher JohnNo ratings yet

- Der 035Document8 pagesDer 035Sthitaprajnyan SharmaNo ratings yet

- A Nonisolated Step-Up DC-AC Converter With Reduced Leakage Current For Grid-Connected Photovoltaic SystemsDocument8 pagesA Nonisolated Step-Up DC-AC Converter With Reduced Leakage Current For Grid-Connected Photovoltaic SystemsMiréli Binder VendruscoloNo ratings yet

- 4200 Pulsed-IV ApplicationsGuideDocument75 pages4200 Pulsed-IV ApplicationsGuideStefan-Marian IordacheNo ratings yet

- A 150V Subscriber Line Interface Circuit in A New Bicmos Dmos TechnologyDocument6 pagesA 150V Subscriber Line Interface Circuit in A New Bicmos Dmos TechnologyWang YuNo ratings yet

- Zimmermann2017 PDFDocument29 pagesZimmermann2017 PDFEliasA.TiongkiaoNo ratings yet

- 05395926Document6 pages05395926EliasA.TiongkiaoNo ratings yet

- Philippines-Marianas Relations: A History of Filipino ExilesDocument14 pagesPhilippines-Marianas Relations: A History of Filipino ExilesEliasA.Tiongkiao100% (1)

- Zimmermann2017 PDFDocument29 pagesZimmermann2017 PDFEliasA.TiongkiaoNo ratings yet

- 07893620Document4 pages07893620EliasA.TiongkiaoNo ratings yet

- Reduction of Data Transmission Time Delay With Object Detection in Underwater Acoustic Sensor NetworkDocument4 pagesReduction of Data Transmission Time Delay With Object Detection in Underwater Acoustic Sensor NetworkEliasA.TiongkiaoNo ratings yet

- IP Exam Answers October 2010Document1 pageIP Exam Answers October 2010EliasA.TiongkiaoNo ratings yet

- Install Photoshop CC Trial Without SoftwareDocument2 pagesInstall Photoshop CC Trial Without SoftwareAnonymous 7dsX2F8nNo ratings yet

- IP Exam Answers - April 2014Document1 pageIP Exam Answers - April 2014EliasA.TiongkiaoNo ratings yet

- Sathya 2016Document4 pagesSathya 2016EliasA.TiongkiaoNo ratings yet

- A System-Based View of The Standards and Certification Landscape For Electric VehiclesDocument12 pagesA System-Based View of The Standards and Certification Landscape For Electric VehiclesEliasA.TiongkiaoNo ratings yet

- 2011A IP AnswerDocument1 page2011A IP AnswerEliasA.TiongkiaoNo ratings yet

- Sensordevices 2017 9 10 20010Document3 pagesSensordevices 2017 9 10 20010EliasA.TiongkiaoNo ratings yet

- How Does This Fit in With My Research - Graphical Arguments - ELEN7070x Courseware - EdXDocument1 pageHow Does This Fit in With My Research - Graphical Arguments - ELEN7070x Courseware - EdXEliasA.TiongkiaoNo ratings yet

- Readings - 8.2. General Theory - TTE01x Courseware - EdXDocument3 pagesReadings - 8.2. General Theory - TTE01x Courseware - EdXEliasA.TiongkiaoNo ratings yet

- SimDocument2 pagesSimEliasA.TiongkiaoNo ratings yet

- Introduction - 8.1. Introduction - TTE01x Courseware - EdXDocument2 pagesIntroduction - 8.1. Introduction - TTE01x Courseware - EdXEliasA.TiongkiaoNo ratings yet

- Introduction to Computers FundamentalsDocument17 pagesIntroduction to Computers Fundamentalsdarmahnoor0% (1)

- Advanced Industrial Control Processing: 12 March 2012 Clive (Max) MaxfieldDocument28 pagesAdvanced Industrial Control Processing: 12 March 2012 Clive (Max) MaxfieldEliasA.TiongkiaoNo ratings yet

- 26th ANTS Call For Papers GuidelinesDocument1 page26th ANTS Call For Papers GuidelinesEliasA.TiongkiaoNo ratings yet

- NRCP Conference Focuses on EthicsDocument1 pageNRCP Conference Focuses on EthicsEliasA.TiongkiaoNo ratings yet

- Monique Frize-Ethics, Research Methods and Standards in Biomedical Engineering-Morgan & Claypool (2011)Document83 pagesMonique Frize-Ethics, Research Methods and Standards in Biomedical Engineering-Morgan & Claypool (2011)EliasA.TiongkiaoNo ratings yet

- Hktelec1t115-V019800 DTHDocument4 pagesHktelec1t115-V019800 DTHEliasA.TiongkiaoNo ratings yet

- ReadmeDocument1 pageReadmeAsad IslamNo ratings yet

- 0 5micronDocument2 pages0 5micronEliasA.TiongkiaoNo ratings yet

- Location of MSC LicenseDocument1 pageLocation of MSC LicenseEliasA.TiongkiaoNo ratings yet

- Ieee Copyright Consent Form 2 PDFDocument1 pageIeee Copyright Consent Form 2 PDFEliasA.TiongkiaoNo ratings yet

- Lab 1Document18 pagesLab 1EliasA.TiongkiaoNo ratings yet

- Ieee Copyright Consent Form 2 PDFDocument1 pageIeee Copyright Consent Form 2 PDFEliasA.TiongkiaoNo ratings yet

- What Is LatchupDocument15 pagesWhat Is LatchupNagendra BoyellaNo ratings yet

- Latch Up in VLSI Design and Why We Need To Use Tap CellDocument3 pagesLatch Up in VLSI Design and Why We Need To Use Tap CellESWAR TERLINo ratings yet

- Maharashtra State Board of Technical Education Mumbai. (M.S.)Document9 pagesMaharashtra State Board of Technical Education Mumbai. (M.S.)ythNo ratings yet

- 6 CMOS Twin Tub ProcessDocument17 pages6 CMOS Twin Tub ProcessRajesh PylaNo ratings yet

- Design Rules and Layout Techniques TutorialDocument10 pagesDesign Rules and Layout Techniques TutorialSaurabh Chakravarty0% (1)

- Dec50143 - Topic 2 - Ic Fabrication ProcessDocument139 pagesDec50143 - Topic 2 - Ic Fabrication ProcessNot GamingNo ratings yet

- ESD ClampsDocument30 pagesESD ClampsKishore RoyNo ratings yet

- Pe64904ds PDFDocument4 pagesPe64904ds PDFSandrine GallardNo ratings yet

- Fulltext MosfetDocument192 pagesFulltext MosfetMuhammad Khosyi'inNo ratings yet

- Ada302734, Tree HDBKDocument507 pagesAda302734, Tree HDBKRGK77No ratings yet

- Chapter 3 Fabrication of Cmos Integrated Circuits Jin Fu Li Department of Electrical Engineering National Central University Jhongli TaiwanDocument37 pagesChapter 3 Fabrication of Cmos Integrated Circuits Jin Fu Li Department of Electrical Engineering National Central University Jhongli TaiwanYusra AmeenNo ratings yet

- Attacking Embedded Systems Through Fault InjectionDocument5 pagesAttacking Embedded Systems Through Fault InjectionMegha RajNo ratings yet

- Vlsi Unit-IDocument45 pagesVlsi Unit-Isuneelanubolu7No ratings yet

- Lt1039 - Linear Tecnology-Rs232Document13 pagesLt1039 - Linear Tecnology-Rs232Alex SantosNo ratings yet

- dt97 3Document6 pagesdt97 3ofilipNo ratings yet

- An 6076Document13 pagesAn 6076Khúc Hành QuânNo ratings yet

- STK433-090-E: 2-Channel Class AB Audio Power IC, 80W+80WDocument11 pagesSTK433-090-E: 2-Channel Class AB Audio Power IC, 80W+80Wcarlosgabriel1971No ratings yet

- LayoutDocument42 pagesLayoutChandrashekarNo ratings yet

- An 6076Document13 pagesAn 6076Kannabhiran Arumugam100% (1)

- PD EssentialsDocument67 pagesPD EssentialsNikhil ManukondaNo ratings yet

- Floorplaning Guidelines for Macro and Memory PlacementDocument23 pagesFloorplaning Guidelines for Macro and Memory PlacementBindu MakamNo ratings yet

- VLSI Circuits and Systems Unit 1: MOS Transistors FundamentalsDocument86 pagesVLSI Circuits and Systems Unit 1: MOS Transistors FundamentalsChinna ChowdaryNo ratings yet

- An 6076Document16 pagesAn 6076Celso CastroNo ratings yet

- 3-CMOS Fab ProcessDocument5 pages3-CMOS Fab ProcessMarcus Jonathan SinsayNo ratings yet

- MB90F337Document85 pagesMB90F337Bin WangNo ratings yet

- VLSI Design Margin and Reliability ScalingDocument17 pagesVLSI Design Margin and Reliability ScalingRapolu SushmaNo ratings yet

- AT24C512 2tpDocument4 pagesAT24C512 2tpapi-3726520No ratings yet