Professional Documents

Culture Documents

Jerarquía de Buses

Uploaded by

Xaggy Krauser Contreras0 ratings0% found this document useful (0 votes)

1K views3 pagesCopyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

1K views3 pagesJerarquía de Buses

Uploaded by

Xaggy Krauser ContrerasCopyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 3

Jerarqua de Buses

Al aumentar el numero de dispositivos o componentes conectados al Bus, el rendimiento del sistema se

deteriora debido a:

La diferencia de velocidad de los dispositivos afecta negativamente al rendimiento global, ya que

mientras los dispositivos lentos realizan una nica transferencia, otro dispositivo ms rpido podra

haber realizado muchas ms.

Los buses pueden actuar de cuello de botella a medida que la demanda de transferencia de datos se

aproxima a la capacidad del bus, los dispositivos debern esperar mucho tiempo para poder

transmitir.

Existe un mayor retardo de propagacin, dado que el bus ha de tener mayor longitud para poder

soportar un mayor nmero de dispositivos

Para solucionar estos problemas se generar una jerarqua de buses

Esta jerarqua de buses ofrece un gran nmero de ventajas entre ellas:

El bus local entre el procesador y la cach asla el trfico de E/S del procesador.

Se puede transferir informacin entre la memoria y la E/S sin interrumpir la actividad del

procesador.

El bus de expansin reduce el trfico en el bus del sistema.

La transferencia entre cach y memoria principal se pueden realizar de forma ms eficiente.

Se pueden realizar una transferencia de memoria cach a memoria principal al mismo tiempo que

el interfaz recibe datos desde un dispositivo de E/S

El procesador+cach o el coprocesador tienen la misma prioridad en el acceso al bus que todos los

dispositivos conectados al bus de expansin de forma conjunta.

Se elimina el problema de la incompatibilidad.

El bus local y del sistema suelen ser propietarios (no estndar) y estn optimizados para cada

arquitectura particular.

Los buses de expansin son buses estndares o abiertos (ISA, EISA, PCI, VME, etc.).

Esto ultimo permite tener caractersticas y especificaciones perfectamente definidas, con conectores

estndar, podemos utilizar los mismos controladores y perifricos en otro computador que disponga del

mismo bus estndar.

Tipos de Buses

Dedicado: los buses dedicados o buses especficos, como indica su nombre estan dedicados cada uno a

una funcin. permiten un diseo sencillo, y que la capacidad de transferencia total sea mayor. Cada lnea

est asignada en forma permanente a una funcin o a un subconjunto de componentes.

Cuando el bus est dedicado a un subconjunto de componentes se utilizan mltiples buses y hay un

mdulo adaptador que los conecta y resuelve las disputas al nivel ms alto

Multiplexado en el tiempo: reducen el nmero de hilos que llegan a la UCP, por lo que es

especialmente til para microprocesadores. El tiempo de ciclo partido se divide en una serie de ranuras,

cada una de las cuales permite enviar un mensaje. Estas ranuras pueden tener duracin fija y predefinida,

y en caso de utilizarse una seal de reloj; es sncrona. Este bus es ms rpido que el anterior a costa de

complicar los dispositivos que lo integran, por tanto se suele emplear en sistemas multiprocesador. Las

lneas se utilizan para diferentes funciones en diferentes momentos, al usarse menos lineas see requieren

circuitos ms complejos en cada mdulo. Este tipo de buses tiene como consecuencia una reduccin

potencial del rendimiento.

Mtodos de arbitraje

En el caso de que varios dispositivos compartan el uso del bus, se establecen polcas de asignacin del

bus. Es similar a los protocolos de comunicaciones en redes de rea local. La funcin de estos protocolos

es garantizar el acceso al bus sin conflictos cuando existen varios dispositivos que pueden actuar como

master, determinando quien puede utilizar el bus en un momento dado

Centralizado: un dispositivo denominado controlador del bus o rbitro asigna el tiempo y acceso al bus

Este protocolo tiene como ventaja que permite aadir nuevos maestros aadindolos a la cadena donde

queramos.

Pero tiene como desventajas que: la prioridad es fija (daisy-chain), la propagacin de seales es lenta, si

un maestro falla, los de menor prioridad a este no tendran acceso al bus, a no ser que queden puenteadas

las seales correspondientes de peticin de bus y concesin de bus (2 hilos) o slo la de concesin (3

hilos).

Distribuido: en este arbitraje no existe un maestro que acte de rbitro en la gestin de la prioridad,

cada mdulo conectado al bus contiene lgica de control de acceso e interacta con los otros para

establecer quien utiliza el bus. Cada lnea de identificacin tiene asignada una prioridad, de manera que

si varios master activan sus lneas simultneamente, gana el de mayor prioridad.

El problema de este ultimo protocolo es que tenemos limitado el nmero de posibles master por el

nmero de lneas de arbitraje que podamos utilizar.

Timing del Bus: existen distintas formas de coordinar los eventos de bus.

Sincrnico: la ocurrencia de eventos en el bus est determinada por un reloj que produce una secuencia

de unos y ceros alternados de igual duracin. Este reloj es accesible a todos los dispositivos conectados

al bus, la secuencia de un 1 y un 0 constituye un ciclo de bus (o ciclo de reloj), los eventos se inician al

comienzo de un ciclo de reloj.

Asincrnico: la ocurrencia de un evento sigue a y depende de la ocurrencia de un evento previo. Esto

permite tomar ventaja de progresos en el rendimiento de los dispositivos y que una mezcla de

dispositivos lentos y rpidos que utilicen nuevas y viejas tecnologas- compartan el bus. Aunque este

tipo de medidas es ms difcil de implementar y probar que el timing sincrnico

You might also like

- Solucionario de Dennis G Zill - Ecuaciones DiferencialesDocument86 pagesSolucionario de Dennis G Zill - Ecuaciones Diferencialesdesigniusk84% (88)

- Desarrolla La Práctica 1 Instalación y Configuración de Un Modem.Document5 pagesDesarrolla La Práctica 1 Instalación y Configuración de Un Modem.Michell CabreraNo ratings yet

- Unidad 2Document7 pagesUnidad 2AldoEsauSolorzanoVazquez100% (1)

- UNIDAD 1 Arquitecturas de Cómputo 1.2Document8 pagesUNIDAD 1 Arquitecturas de Cómputo 1.2Agus OliveraNo ratings yet

- Guía Técnica para El Desarrollo de Competencias Sistemas ProgramablesDocument66 pagesGuía Técnica para El Desarrollo de Competencias Sistemas ProgramablesAidee FierroNo ratings yet

- Diseño e Implementación de Un Esquema de Direccionamiento VLSM TopologíaDocument7 pagesDiseño e Implementación de Un Esquema de Direccionamiento VLSM TopologíaAna Carolina Melendez MontesNo ratings yet

- U4E4 Dario Romario Damian AlexisDocument15 pagesU4E4 Dario Romario Damian AlexisBenito DelgadoNo ratings yet

- Unidad 4 MicrocontroladoresDocument45 pagesUnidad 4 MicrocontroladoresOchoa JoshuaNo ratings yet

- Seguridad física y planes contingenciaDocument50 pagesSeguridad física y planes contingenciaRosa Esmeralda Rojas Hernandez100% (3)

- Sistema de Interconexión Interna Arbitraje y Jerarquía de Buses TerminadoDocument39 pagesSistema de Interconexión Interna Arbitraje y Jerarquía de Buses TerminadoBiviana Katherine Rivera PeraltaNo ratings yet

- Unidad 4 - Operación y ManteniemientoDocument68 pagesUnidad 4 - Operación y ManteniemientoAlex RodríguezNo ratings yet

- Introducción A SwitchDocument14 pagesIntroducción A SwitchMichael Douglas Moreno Panchana100% (1)

- Modelos de Arquitecturas de Cómputo.Document7 pagesModelos de Arquitecturas de Cómputo.CAAMAL CARLOS ALBERTONo ratings yet

- Investigacion Tecnologias WANDocument53 pagesInvestigacion Tecnologias WANxavmarcial1978No ratings yet

- El Cable Utp o Cable de RedDocument4 pagesEl Cable Utp o Cable de RedJulio César López ConstanteNo ratings yet

- Caracteristicas de Operaciones de Puertos EstandarDocument24 pagesCaracteristicas de Operaciones de Puertos EstandarCecilia Leon Mateos100% (2)

- Componentes de Un MicrocontroladorDocument5 pagesComponentes de Un MicrocontroladorBrendaNo ratings yet

- CapaAplicación-FuncionesProtocolosDocument15 pagesCapaAplicación-FuncionesProtocolosAdriana VidalNo ratings yet

- SistemasProgramables Unidad-5 CompletaDocument9 pagesSistemasProgramables Unidad-5 CompletaLuis Alejandro Escárcega FernándezNo ratings yet

- Cisc - RiscDocument35 pagesCisc - RiscEins Ortiz MoralesNo ratings yet

- Comparación de Los SGBD Mas UsadosDocument9 pagesComparación de Los SGBD Mas UsadosAndré Jr SandovalNo ratings yet

- Automatización Industrial. Interfaz Hombre-Máquina: 1 Human Machine Interface - HMIDocument35 pagesAutomatización Industrial. Interfaz Hombre-Máquina: 1 Human Machine Interface - HMIRodrigoNo ratings yet

- Lab Designing and Implementing A VLSM Addressing Scheme ILMDocument16 pagesLab Designing and Implementing A VLSM Addressing Scheme ILMWilliam Lopez CedeñoNo ratings yet

- Investigacion EJBDocument6 pagesInvestigacion EJBHernan LeonNo ratings yet

- PIC16F887: Características básicas del microcontrolador RISC de 35 instruccionesDocument4 pagesPIC16F887: Características básicas del microcontrolador RISC de 35 instruccionesJuanJndNo ratings yet

- Conectividad WAN, configuración router y componentes internosDocument5 pagesConectividad WAN, configuración router y componentes internoslorenxitoNo ratings yet

- 1.5 Interface GpibDocument39 pages1.5 Interface GpibDany CANo ratings yet

- Unidad II Comunicacion Interna en La ComputadoraDocument16 pagesUnidad II Comunicacion Interna en La ComputadoraYuri AnayaNo ratings yet

- Ej Lenguaje Java 12Document2 pagesEj Lenguaje Java 12jaba2820No ratings yet

- Estándares buses manejoDocument6 pagesEstándares buses manejoBéjar Aguilar DavidNo ratings yet

- Traducción de Datasheet Atmega16Document3 pagesTraducción de Datasheet Atmega16Frank Cabrera Salazar100% (1)

- Arquitecturas RISC vs CISC y Harvard vs Von NeumannDocument8 pagesArquitecturas RISC vs CISC y Harvard vs Von NeumannVittorNúñezNo ratings yet

- Guía Rápida de Administración de MySQLDocument31 pagesGuía Rápida de Administración de MySQLSergio GarateNo ratings yet

- Escalamiento de Redes: La Necesidad de Escalamiento de RedesDocument11 pagesEscalamiento de Redes: La Necesidad de Escalamiento de RedesOscarNo ratings yet

- Introducción A Los Sistemas ProgramablesDocument7 pagesIntroducción A Los Sistemas Programablesevaob75No ratings yet

- Unidad 5 SeguridadDocument17 pagesUnidad 5 SeguridadGustGCNo ratings yet

- Tipos de Notacion para La Conversion de Expresiones.Document3 pagesTipos de Notacion para La Conversion de Expresiones.HernandezSalomonNo ratings yet

- SQL Server 2019 - Requisitos de Hardware y Software - SQL Server - Documentos de MicrosoftDocument8 pagesSQL Server 2019 - Requisitos de Hardware y Software - SQL Server - Documentos de MicrosoftAry Fernando PissoNo ratings yet

- Mapa - Conceptual Placa Madre y Sus ComponentesDocument2 pagesMapa - Conceptual Placa Madre y Sus ComponentesAlexaNo ratings yet

- El Procesador y Sus Registros InternosDocument6 pagesEl Procesador y Sus Registros InternosJerzain CarrilloNo ratings yet

- Dispositivos de ComunicaciónDocument2 pagesDispositivos de ComunicaciónCarmelita_16No ratings yet

- Actividad 5.2.2.2: Dominios de Broadcast de Segmentos de Routers.Document4 pagesActividad 5.2.2.2: Dominios de Broadcast de Segmentos de Routers.Paul Vintimilla TapiaNo ratings yet

- Presentación 4Document27 pagesPresentación 4mralero100% (2)

- 6 Ciclos de VidaDocument78 pages6 Ciclos de VidaLudis1100% (1)

- Las 35 Instrucciones Que Reconoce La CPU de Los PIC de Medio RangoDocument9 pagesLas 35 Instrucciones Que Reconoce La CPU de Los PIC de Medio RangoReinaldo MoreiraNo ratings yet

- Documentacion WUMPUSDocument7 pagesDocumentacion WUMPUSJOSE LUIS VAZQUEZNo ratings yet

- Tareas y Tecnicas de RequisitosDocument3 pagesTareas y Tecnicas de RequisitosjhiecooNo ratings yet

- Introduccion A Las Arquitecturas Paralelas PDFDocument51 pagesIntroduccion A Las Arquitecturas Paralelas PDFkanzazzNo ratings yet

- Fundamentos de RedesDocument26 pagesFundamentos de RedesalexisDavi100% (4)

- El Microprocesador Amc-400Document18 pagesEl Microprocesador Amc-400denisseNo ratings yet

- Preparatorio 2 DigitalesDocument3 pagesPreparatorio 2 DigitalesJefferson Guala FonsecaNo ratings yet

- Informa Practica 3 IOTDocument13 pagesInforma Practica 3 IOTFreddy MayorgaNo ratings yet

- Chipsets y Sus CaracteristicasDocument5 pagesChipsets y Sus CaracteristicaslikenspNo ratings yet

- HubDocument12 pagesHubRusbelHuamanMNo ratings yet

- Unidad 2 Redes de ComputadorasDocument61 pagesUnidad 2 Redes de ComputadorasengengermNo ratings yet

- Direccionamiento Fisico EthernetDocument6 pagesDireccionamiento Fisico Ethernetjuanitopedrito22No ratings yet

- Practica SubnettingDocument4 pagesPractica Subnettingjholianis2014No ratings yet

- Jerarquia de Buses MultiplesDocument7 pagesJerarquia de Buses MultiplesSergio RamirezNo ratings yet

- Las Líneas de Bus Se Pueden Dividir en Dos Tipos GenéricosDocument3 pagesLas Líneas de Bus Se Pueden Dividir en Dos Tipos GenéricosNovedades MLNo ratings yet

- Metodos de Arbitraje de BusesDocument8 pagesMetodos de Arbitraje de BusesStevenTM ReyesNo ratings yet

- Buses de sistemas: tipos, características y funcionalidadDocument6 pagesBuses de sistemas: tipos, características y funcionalidadOzz GarciaNo ratings yet

- UN2-3-Jerarquia de Buses MultiplesDocument7 pagesUN2-3-Jerarquia de Buses MultiplesMaria Eugenia GonzálezNo ratings yet

- Documento Porcentajes CalificacionDocument2 pagesDocumento Porcentajes CalificacionXaggy Krauser ContrerasNo ratings yet

- Arquitectura de Computadoras, 3° EDMorrisC1-2Document91 pagesArquitectura de Computadoras, 3° EDMorrisC1-2kaio_jimenezNo ratings yet

- Automatas y LenguajesDocument214 pagesAutomatas y LenguajesJorge100% (3)

- Auditoria InformaticaDocument14 pagesAuditoria InformaticaXaggy Krauser ContrerasNo ratings yet

- Manual Osticket UsuariosDocument7 pagesManual Osticket UsuariosXaggy Krauser ContrerasNo ratings yet

- Taller de Investigacion 21-11-2014Document1 pageTaller de Investigacion 21-11-2014Xaggy Krauser ContrerasNo ratings yet

- Gestion de PedidosDocument26 pagesGestion de Pedidosjkamus01No ratings yet

- Manual 2Document23 pagesManual 2Xaggy Krauser ContrerasNo ratings yet

- Activar Desactivar Tarjeta de RedDocument8 pagesActivar Desactivar Tarjeta de RedpuertalabsNo ratings yet

- Resolución de Sistemas de EDO Lineales Con Coefs. Ctes. (Método de Los Operadores)Document27 pagesResolución de Sistemas de EDO Lineales Con Coefs. Ctes. (Método de Los Operadores)Claudio VelasquezNo ratings yet

- Conversión de Infijo A Postfijo Usando PilasDocument5 pagesConversión de Infijo A Postfijo Usando PilasXaggy Krauser ContrerasNo ratings yet

- Codificacion y ModulacionDocument6 pagesCodificacion y ModulacionXaggy Krauser ContrerasNo ratings yet

- Metodosde OrdenacionDocument14 pagesMetodosde OrdenacionXaggy Krauser ContrerasNo ratings yet

- Funciones Del ChipsetDocument5 pagesFunciones Del ChipsetXaggy Krauser ContrerasNo ratings yet

- Codificacion y ModulacionDocument6 pagesCodificacion y ModulacionXaggy Krauser ContrerasNo ratings yet

- Tema 2 Transformada de Laplace-4721Document79 pagesTema 2 Transformada de Laplace-4721Fabian ArredondoNo ratings yet

- Sustentabilidad SocialDocument2 pagesSustentabilidad SocialXaggy Krauser ContrerasNo ratings yet

- Graficación - Unidad 1Document10 pagesGraficación - Unidad 1Xaggy Krauser ContrerasNo ratings yet

- Linea de Tiempo GaraficacionDocument1 pageLinea de Tiempo GaraficacionXaggy Krauser ContrerasNo ratings yet

- Las 10 megatendencias mundialesDocument17 pagesLas 10 megatendencias mundialesXaggy Krauser ContrerasNo ratings yet

- Requerimientos Svi Cinvestav 2 PDFDocument58 pagesRequerimientos Svi Cinvestav 2 PDFXaggy Krauser ContrerasNo ratings yet

- Breve Historia de La GraficacionDocument3 pagesBreve Historia de La GraficacionXaggy Krauser ContrerasNo ratings yet

- Geometria FractalDocument5 pagesGeometria Fractalcesart21No ratings yet

- BusesDocument8 pagesBusesJuan Pablo Corona MaberijasNo ratings yet

- Diodos y TransistoresDocument32 pagesDiodos y TransistoresXaggy Krauser ContrerasNo ratings yet

- Anexo-Formatos de Archivo de GráficosDocument2 pagesAnexo-Formatos de Archivo de GráficosXaggy Krauser ContrerasNo ratings yet

- Requerimientos Svi Cinvestav 2 PDFDocument58 pagesRequerimientos Svi Cinvestav 2 PDFXaggy Krauser ContrerasNo ratings yet

- Unidad 4 - ABDDocument19 pagesUnidad 4 - ABDXaggy Krauser ContrerasNo ratings yet

- Diodos y TransistoresDocument32 pagesDiodos y TransistoresXaggy Krauser ContrerasNo ratings yet

- EntonacionDocument19 pagesEntonacionEdy SanchezNo ratings yet

- VNX - Version1 - CaracteristicasDocument21 pagesVNX - Version1 - CaracteristicasJorge AvilaNo ratings yet

- Atermiter X79 Placa Base Con LGA2011 Combos Xeon E5 2640 CPU 2 Uds X 4GB 8GB de Memoria DDR3 RAM 1333Mhz PC3 10600R PCI E-In Placas Base From Ordenadores y Oficina On AliExpressDocument5 pagesAtermiter X79 Placa Base Con LGA2011 Combos Xeon E5 2640 CPU 2 Uds X 4GB 8GB de Memoria DDR3 RAM 1333Mhz PC3 10600R PCI E-In Placas Base From Ordenadores y Oficina On AliExpressMANUEL EUGENIO LOPEZ NEGRETE AMARILLAS0% (1)

- Para Imprimir Historia de La ComputadoraDocument9 pagesPara Imprimir Historia de La ComputadoraJuan Pablo Bermúdez MontoyaNo ratings yet

- Reparacion y Mantenimiento TP 4Document7 pagesReparacion y Mantenimiento TP 4Hector CornejoNo ratings yet

- Tarjeta CiudadanaDocument160 pagesTarjeta CiudadanaJosé Antonio Redondo IbáñezNo ratings yet

- Manual AccessDocument59 pagesManual AccessArmherpa RobertoNo ratings yet

- Guia DDR, DDR2 y DDR3 Caracteristicas y DiferenciasDocument4 pagesGuia DDR, DDR2 y DDR3 Caracteristicas y DiferenciasFabianNo ratings yet

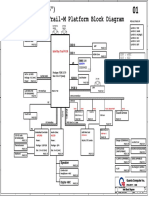

- Quanta ZHK R3a 20140630 SchematicsDocument34 pagesQuanta ZHK R3a 20140630 SchematicsAnonymous rePyCistNo ratings yet

- Cómo Proteger Memoria USB de Virus EficazmenteDocument10 pagesCómo Proteger Memoria USB de Virus EficazmenteMauricio FloresNo ratings yet

- Analogia Del RestauranteDocument4 pagesAnalogia Del RestauranteDiego50% (4)

- Logica de ProgramacionDocument45 pagesLogica de ProgramacionJose LuisNo ratings yet

- Memoria ConvenienteDocument3 pagesMemoria ConvenienteAlejandro PalaciosNo ratings yet

- Manual Microsistema Con DVD HitplusDocument30 pagesManual Microsistema Con DVD HitplusMatias Sallitto0% (1)

- Multiprogramación en Memoria Virtual - Clases 2.1Document92 pagesMultiprogramación en Memoria Virtual - Clases 2.1Ángel ZambranoNo ratings yet

- Configuración IO ScanningDocument15 pagesConfiguración IO ScanningViick MartinezNo ratings yet

- JADWAL DINAS FARMASI APRIL 2021 NewDocument38 pagesJADWAL DINAS FARMASI APRIL 2021 NewReny WidyaNo ratings yet

- 50 Verbos Con Ar, Er, Ir, Componentes Internos de Un Ordenador, Que Es Educacion FisicaDocument14 pages50 Verbos Con Ar, Er, Ir, Componentes Internos de Un Ordenador, Que Es Educacion FisicaWilmer Gonzales ArrueNo ratings yet

- Informatica PresentDocument18 pagesInformatica PresentFernanda VelázquezNo ratings yet

- Arq. hardware-softwareDocument6 pagesArq. hardware-softwarejvtoroNo ratings yet

- Simulación hardware computadora sencillaDocument10 pagesSimulación hardware computadora sencillaEstebanNo ratings yet

- Lenel Systems PDFDocument68 pagesLenel Systems PDFAtef IbrahimNo ratings yet

- Micros Mod 309696 PDFDocument256 pagesMicros Mod 309696 PDFalbergon78No ratings yet

- Positivo BGHDocument50 pagesPositivo BGHcarrizofNo ratings yet

- Electronica DigitalDocument6 pagesElectronica DigitalJulio Cesar Alvarez Orozco80% (5)

- Manual de Mantenimiento PSI 300Document24 pagesManual de Mantenimiento PSI 300Miguel Diabolo Duran100% (2)

- Generaciones de La ComputadoraDocument247 pagesGeneraciones de La ComputadoraLiliana VasquezNo ratings yet

- Mantenimiento de PCDocument42 pagesMantenimiento de PCAdan GonzalesNo ratings yet

- Boris VillarroelDocument4 pagesBoris VillarroelPinedo Carata Ivan A.No ratings yet