Professional Documents

Culture Documents

Digital Electronics Lab Report

Uploaded by

Mohammad Irfan YousufOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital Electronics Lab Report

Uploaded by

Mohammad Irfan YousufCopyright:

Available Formats

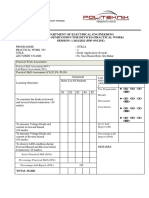

Title: Construction of Bipolar Transistor Logic Gate

Abstract:

In this experiment the objective is:

1) To build logic gates from bipolar transistors using the TL! "TL and TTL design#

$) To examine and compare the results of these technologies#

#

Theory and Methodology:

Resistor-Transistor Logic (RTL):

esistor%Transistor Logic &TL) is a large step be'ond "iode Logic &"L)# Basicall'! TL

replaces the diode s(itch (ith a transistor s(itch# If a )*v signal &logic 1) is applied to the base

of the transistor &through an appropriate resistor to limit base%emitter for(ard voltage and

current)! the transistor turns full' on and grounds the output signal# If the input is grounded &logic

+)! the transistor is off and the output signal is allo(ed to rise to )* volts# In this (a'! the

transistor not onl' inverts the logic sense of the signal! but it also ensures that the output voltage

(ill al(a's be a valid logic level under all circumstances# Because of this! TL circuits can be

cascaded indefinitel'! (here "L circuits cannot be cascaded reliabl' at all#

Diode-Transistor Logic:

"iode,Transistor Logic &"TL) is a class of digital circuits built from bipolar junction transistors

&B-T)! diodes and resistors. it is the direct ancestor of transistor,transistor logic &TTL)#

"TL offers better noise margins and greater fan%outs than TL! but suffers from lo( speed

&especiall' in comparison to TTL)#

TL allo(s the construction of /0 gates easil'! but /1/" gates are relativel' more difficult to

get from TL# "TL! ho(ever! allo(s the construction of simple /1/" gates from a single

transistor! (ith the help of several diodes and resistors#

Transistor-Transistor Logic:

2e can thin3 of a bipolar transistor as t(o diodes placed ver' close together! (ith the point

bet(een the diodes being the transistor base# Thus! (e can use transistors in place of diodes to

obtain logic gates that can be implemented (ith transistors and resistors onl'. this is called

transistor%transistor logic &TTL)#

0ne problem that "TL doesn4t solve is its lo( speed! especiall' (hen the transistor is being

turned off# Turning off a saturated transistor in a "TL gate re5uires it to first pass through the

active region before going into cut%off# Cut%off! ho(ever! (ill not be reached until the stored

charge in its base has been removed# The dissipation of the base charge ta3es time if there is no

available path from the base to ground# This is (h' some "TL circuits have a base resistor that4s

tied to ground! but even this re5uires some trade%offs# 1nother problem (ith turning off the "TL

output transistor is the fact that the effective capacitance of the output needs to charge up through

c before the output voltage rises to the final logic 414 level! (hich also consumes a relativel'

large amount of time# TTL! ho(ever! solves the speed problem of "TL elegantl'#

Pre-Lab Homework:

6xplain ho( n%p%n B-T transistors (or37

Answer:

The /8/ transistor can be used in t(o different modes: for(ard biased mode and the

reverse biased mode# In for(ard biased mode! the electric current can easily flow through

it# 9o it acts li3e a CL096" 92ITC:# :o(ever! in reverse biased mode! the current

through it is practicall' ;ero and thus! it acts li3e an 086/ 92ITC:#

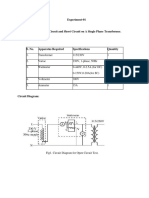

Apparatus:

1) /8/ silicon transistor : $/<1$< = > pcs?

$) esistors : 1*@A! 1@A! <#B @A = 9ufficient no?

C) Connecting (ires# : 9ufficient amount

Precautions:

Instructor chec3ed all 'our connections after (e (ere done setting up the circuit and made sure

that (e appl' onl' enough voltage &(ithin D"") to turn on the transistors andEor chip! other(ise it

ma' get damaged#

Experimental Procedure:

1# The circuit for TL inverter as sho(n in Fig#$ (as set up#

$# For each input combination! the output (as found and placed them in a Truth Table#

C# 9teps 1 and $ (ere repeated for each circuit set%up from Fig#C to Fig# G#

uestions !or report writing:

1) For! each of the above set%ups! describe in (ords (hat the data means# "id 'our results match

the expected ideal outputs7 If not! explain (h'7

"# "esign TL and TTL <%input 0 gates#

TL < input 0 Gate

TTL < input 0 Gate

$# "esign $%input TTL /1/" and /0 gates#

$ input TTL /or done in Fig# $#G

%esults:

0ur experimental value and expected values varied a little! this ma' be because the

s(itches (ere not providing exactl' *D# 1nother reason ma' be the drop across the

transistor junction (as not exactl' ideal#

&iscussion:

1s our experimental data approx# matched (ith the ideal data! (e ma' conclude that that

circuits (e implemented gave the oEp of respective gates#

%e!erence:

=1? Thomas L# Flo'd! Digital Fundamentals! Hth 6dition! $++G! 8rentice :all#

You might also like

- Term Paper Advantages of RTL DTL and TTLDocument5 pagesTerm Paper Advantages of RTL DTL and TTLDebashis Paul100% (2)

- American International University-Bangladesh: Title: Study of Different Flip-FlopsDocument7 pagesAmerican International University-Bangladesh: Title: Study of Different Flip-FlopsAbid ChowdhuryNo ratings yet

- Lab Report 1Document23 pagesLab Report 1hadri arif0% (1)

- Lab 8 Synchronous Sequential CircuitsDocument9 pagesLab 8 Synchronous Sequential Circuitsapi-385689610No ratings yet

- Lab 1Document4 pagesLab 1idasyarmilaNo ratings yet

- Lab Report 3 - Transistor As A SwitchDocument5 pagesLab Report 3 - Transistor As A Switchアベルジョン パランNo ratings yet

- Master Slave Flip FlopDocument3 pagesMaster Slave Flip FlophimanshuNo ratings yet

- LAB Experiment 1 GROUP NO.7Document6 pagesLAB Experiment 1 GROUP NO.7Janpherson BellecaNo ratings yet

- Long Report Lab 7Document15 pagesLong Report Lab 7Saragadam Naga Shivanath RauNo ratings yet

- UNIT1Document37 pagesUNIT1Azliana Mohd Taib0% (1)

- The Digital Encoder: 4-To-2 Bit Binary EncoderDocument10 pagesThe Digital Encoder: 4-To-2 Bit Binary EncoderJohn Brix BalisterosNo ratings yet

- Experiment-11 BCD Code To 7-Segment Decoder 11-1 ObjectDocument3 pagesExperiment-11 BCD Code To 7-Segment Decoder 11-1 ObjectMohammed Dyhia AliNo ratings yet

- 21425-9021-Digital Electronics Lab ManualDocument57 pages21425-9021-Digital Electronics Lab ManualAravind BalasundaramNo ratings yet

- Untitled 1Document109 pagesUntitled 1Ritesh SharmaNo ratings yet

- Karnaugh Maps - Rules of Simplification: Grouping OnesDocument14 pagesKarnaugh Maps - Rules of Simplification: Grouping OnesProfessor RajputNo ratings yet

- Chapter1 Det10013Document30 pagesChapter1 Det10013che syakirNo ratings yet

- Applied Electronics Lab 1Document9 pagesApplied Electronics Lab 1Rickel RoweNo ratings yet

- Experiment 7: Magnitude ComparatorsDocument5 pagesExperiment 7: Magnitude Comparatorsanirudh lakshminarasimhanNo ratings yet

- AIM:-To Write and Test The VHDL Code of 3TO 8 DECODER, USING 2 TO 4 DECODERDocument5 pagesAIM:-To Write and Test The VHDL Code of 3TO 8 DECODER, USING 2 TO 4 DECODERPhaniKumar ParvathamNo ratings yet

- Power BJT, Power Mosfet and IgbtDocument7 pagesPower BJT, Power Mosfet and IgbtHrishikesh TiwaryNo ratings yet

- Differentiator ExperimentDocument25 pagesDifferentiator ExperimentAlyaa Nadzirah Binti Shbini100% (1)

- Parity Generator Checker PDFDocument3 pagesParity Generator Checker PDFSujesh P Lal67% (3)

- 218 1499022343 - 02-07-2017 PDFDocument5 pages218 1499022343 - 02-07-2017 PDFEditor IJRITCCNo ratings yet

- 09-Wien Bridge Oscillator Using OpAmp PDFDocument4 pages09-Wien Bridge Oscillator Using OpAmp PDFVishesh Kumar SinghNo ratings yet

- Verilog HDL - 18ec56 AssignmentDocument2 pagesVerilog HDL - 18ec56 Assignmentsureshfm1No ratings yet

- Astable Using 555Document2 pagesAstable Using 555SumithNo ratings yet

- De Morgans LawDocument5 pagesDe Morgans LawJaber Al NahianNo ratings yet

- Eee de Lab Manual DiplomaDocument80 pagesEee de Lab Manual Diplomasiri.pogula0% (1)

- Unijunction TransistorDocument12 pagesUnijunction TransistorGogoi LeftoverNo ratings yet

- Machine LabDocument7 pagesMachine LabNurjahan-Ara StudentNo ratings yet

- 2 Experiment PSPICE RC RL and RLC SimulationDocument5 pages2 Experiment PSPICE RC RL and RLC Simulationsrinureddy2014No ratings yet

- SyllabusDocument5 pagesSyllabusChandan Prasai100% (1)

- Network Analysis and Synthesis QBDocument11 pagesNetwork Analysis and Synthesis QBGowthamNo ratings yet

- Combinational Circuits LDICDocument129 pagesCombinational Circuits LDIChemanth ramireddyNo ratings yet

- Experiment 7 - Flip-FlopsDocument4 pagesExperiment 7 - Flip-FlopsPrr PrrNo ratings yet

- UNIT-1: Architecture of 8086Document45 pagesUNIT-1: Architecture of 8086amoghNo ratings yet

- Operational Amplifier Exam QuestionDocument3 pagesOperational Amplifier Exam QuestionKuseswar Prasad100% (1)

- Warmly Welcome From My PresentationDocument59 pagesWarmly Welcome From My PresentationPrinces Ofattacker100% (4)

- Aim: To Test Differentiator and Integrator Circuits Using Ua741op-AmpDocument8 pagesAim: To Test Differentiator and Integrator Circuits Using Ua741op-AmpAvinash Nandakumar100% (1)

- EM308 Lab 001 Jan15Document7 pagesEM308 Lab 001 Jan15shakeeb mana0% (1)

- Level 4 Diploma in Electrical and Electronic Engineering v2 PDFDocument139 pagesLevel 4 Diploma in Electrical and Electronic Engineering v2 PDFD Gihan PereraNo ratings yet

- American International University-Bangladesh: Title: Design of A 2 To 4 Decoder and A Decimal To BCD EncoderDocument4 pagesAmerican International University-Bangladesh: Title: Design of A 2 To 4 Decoder and A Decimal To BCD EncoderAbid ChowdhuryNo ratings yet

- Lab2 - Combinational Logic CircuitsDocument2 pagesLab2 - Combinational Logic CircuitsFarishat Nusabbee An NafsNo ratings yet

- Bipolar Junction Transistor: E B CE CBDocument18 pagesBipolar Junction Transistor: E B CE CBMohammadAshraful100% (1)

- Experiment 9 (Flip Flops)Document7 pagesExperiment 9 (Flip Flops)groupidb3100% (3)

- Expt 5 - Wein Bridge Oscillator (2020)Document3 pagesExpt 5 - Wein Bridge Oscillator (2020)samarthNo ratings yet

- MSDFFDocument20 pagesMSDFFShweta KumariNo ratings yet

- Lecture Plan 1: S. No. Topic:-Introduction To Two Port Network, Z & Y Parameters - Time AllottedDocument0 pagesLecture Plan 1: S. No. Topic:-Introduction To Two Port Network, Z & Y Parameters - Time Allottedsreekantha2013No ratings yet

- CUK ConverterDocument13 pagesCUK ConverterpakalagopalNo ratings yet

- Complete Lab 2Document7 pagesComplete Lab 2Nur Afiqah Mohamad NayanNo ratings yet

- Single Phase Full Wave Voltage Multiplier PDFDocument3 pagesSingle Phase Full Wave Voltage Multiplier PDFJoshua Amiel javines0% (1)

- Uvufigigigi 747858 UfuDocument4 pagesUvufigigigi 747858 UfuHussein A. AlsameeNo ratings yet

- Stereo VU MeterDocument7 pagesStereo VU MeterVlatko KrstevskiNo ratings yet

- Ade Unit 2 XcvbgfreDocument21 pagesAde Unit 2 XcvbgfreRishabh Singh RajputNo ratings yet

- Dec Exp 2 Student Manual PDFDocument4 pagesDec Exp 2 Student Manual PDFS M AkashNo ratings yet

- Unit 4 Logic FamiliesDocument10 pagesUnit 4 Logic FamiliesJagat SinghNo ratings yet

- UNIT-5: Realization of Logic Gates and Sampling GatesDocument11 pagesUNIT-5: Realization of Logic Gates and Sampling GatesSanjana PulapaNo ratings yet

- Diploma in Electrical Engg. Semester-5 Power Electronics: Construction of SCRDocument6 pagesDiploma in Electrical Engg. Semester-5 Power Electronics: Construction of SCRDiogo RodriguesNo ratings yet

- RTL NotDocument9 pagesRTL Notمعتصم الكاملNo ratings yet

- TTL LOGIC Family - Hariram-1Document16 pagesTTL LOGIC Family - Hariram-1Hari RamNo ratings yet

- A Level Physics NotesDocument81 pagesA Level Physics NotesJames Chong100% (1)

- Thermister O Levels Typical QuestionDocument4 pagesThermister O Levels Typical QuestionMohammad Irfan YousufNo ratings yet

- Class 6 MlisDocument7 pagesClass 6 MlisMohammad Irfan YousufNo ratings yet

- CAD Exp 9Document7 pagesCAD Exp 9Mohammad Irfan YousufNo ratings yet

- Number Answer Notes MarksDocument1 pageNumber Answer Notes MarksMohammad Irfan YousufNo ratings yet

- Pre-Lecture Materials For Lecture 7 (Sentence Equivalence)Document4 pagesPre-Lecture Materials For Lecture 7 (Sentence Equivalence)Mohammad Irfan YousufNo ratings yet

- Thermister O Levels Typical QuestionDocument4 pagesThermister O Levels Typical QuestionMohammad Irfan YousufNo ratings yet

- Cover LetterDocument1 pageCover LetterMohammad Irfan YousufNo ratings yet

- Thermister Question MSDocument3 pagesThermister Question MSMohammad Irfan YousufNo ratings yet

- Schrodinger Equation Theory Hand NoteDocument12 pagesSchrodinger Equation Theory Hand NoteMohammad Irfan YousufNo ratings yet

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Parallel CircuitsDocument20 pagesParallel CircuitsMohammad Irfan YousufNo ratings yet

- De Broglie Wave & Heisenberg Uncertainty PrincipleDocument7 pagesDe Broglie Wave & Heisenberg Uncertainty PrincipleMohammad Irfan Yousuf100% (1)

- Nuclear Energy (Radioactivity, Nuclear Fission and Fusion)Document14 pagesNuclear Energy (Radioactivity, Nuclear Fission and Fusion)Mohammad Irfan YousufNo ratings yet

- Photo-Electric Effect and ComptonDocument7 pagesPhoto-Electric Effect and ComptonMohammad Irfan YousufNo ratings yet

- Lab 2 EshopDocument5 pagesLab 2 EshopMohammad Irfan YousufNo ratings yet

- Course Outline - Spring 2015 - 16 (Modern Physics)Document3 pagesCourse Outline - Spring 2015 - 16 (Modern Physics)Mohammad Irfan YousufNo ratings yet

- 6 Trans InvDocument1 page6 Trans InvMohammad Irfan YousufNo ratings yet

- 266 PermissionDocument1 page266 PermissionMohammad Irfan YousufNo ratings yet

- TSF Tanmoy DebnathDocument1 pageTSF Tanmoy DebnathMohammad Irfan YousufNo ratings yet

- My Name Is Irfan YousufDocument1 pageMy Name Is Irfan YousufMohammad Irfan YousufNo ratings yet

- EngineeringDocument6 pagesEngineeringMohammad Irfan YousufNo ratings yet

- 4PH0 1P Que 20130110Document32 pages4PH0 1P Que 20130110Tahmid SadatNo ratings yet

- Some Important QuatationsDocument1 pageSome Important QuatationsMohammad Irfan YousufNo ratings yet

- Wave Theory (Physics 2)Document15 pagesWave Theory (Physics 2)Mohammad Irfan YousufNo ratings yet

- m1 Jan 2012 MsDocument14 pagesm1 Jan 2012 MsMhmd Magdy KhalilNo ratings yet

- GhyhiDocument1 pageGhyhiMohammad Irfan YousufNo ratings yet

- Intro To ADCs FinalDocument58 pagesIntro To ADCs FinalAnonymous SsPiDQgphF100% (1)

- Funkuhren: Technical Information Operating InstructionsDocument22 pagesFunkuhren: Technical Information Operating InstructionsvdaNo ratings yet

- Ho3 (1) IntroDocument6 pagesHo3 (1) Introresizer20No ratings yet

- Hoja Caracteristicas 7476Document5 pagesHoja Caracteristicas 7476GroplyNo ratings yet

- High Performance Folded Cascode OTA Using Positive FeedbackDocument11 pagesHigh Performance Folded Cascode OTA Using Positive Feedbackekta jollyNo ratings yet

- M&a PresentationDocument12 pagesM&a PresentationAnushka SinhaNo ratings yet

- IPD075N03LGDocument12 pagesIPD075N03LGGeorge PietraruNo ratings yet

- Phidgets LabVIEW ManualDocument368 pagesPhidgets LabVIEW Manualkarol555No ratings yet

- Art Tech (E-Fly) ETC62 2.4 GHZ 6 Channel RC System (7-12)Document6 pagesArt Tech (E-Fly) ETC62 2.4 GHZ 6 Channel RC System (7-12)Arnold Nilgesz0% (1)

- Z600EDocument2 pagesZ600Esaleemut3No ratings yet

- Jual GPS Trimble Juno 3B, 3D With Terrasync Standard 087809762415Document3 pagesJual GPS Trimble Juno 3B, 3D With Terrasync Standard 087809762415TRANSSURVEYNo ratings yet

- ARPA - Chart Radar User Guide - 65900010-1 - Rev CDocument313 pagesARPA - Chart Radar User Guide - 65900010-1 - Rev Cjaidanfreites100% (1)

- Sokkia SDL1X - Digital LevelDocument2 pagesSokkia SDL1X - Digital LevelnunosobralNo ratings yet

- Connection Diagram, Parts List, Setup, OperationDocument4 pagesConnection Diagram, Parts List, Setup, OperationJ SNo ratings yet

- DocxDocument6 pagesDocxJotaro KujoNo ratings yet

- NGT SR Transceiver CodanDocument2 pagesNGT SR Transceiver CodanEdi PaNo ratings yet

- DP3400 3401 FinalDocument2 pagesDP3400 3401 FinalAdvantec SrlNo ratings yet

- Samsung Galaxy NoteDocument73 pagesSamsung Galaxy NotevagncarisiusNo ratings yet

- IC-7000 Product BrochureDocument4 pagesIC-7000 Product BrochurerdeagleNo ratings yet

- SSS Parameters V1Document3 pagesSSS Parameters V1Ravi KumarNo ratings yet

- Digital Stopwatch 0-99secDocument4 pagesDigital Stopwatch 0-99secSanjay BalwaniNo ratings yet

- Pin Diode RF ModulatorsDocument6 pagesPin Diode RF Modulatorsamit261287No ratings yet

- Frequency Divider Circuit Using 555 and 4017 Using 555 Timer IC and 4017 Counter ICDocument6 pagesFrequency Divider Circuit Using 555 and 4017 Using 555 Timer IC and 4017 Counter ICNamith NamithNo ratings yet

- 2.3.1 Mitsubishi ElectricDocument17 pages2.3.1 Mitsubishi ElectricBrad CowanNo ratings yet

- Homework 1 EE 240b Advanced Analog CircuitsDocument2 pagesHomework 1 EE 240b Advanced Analog Circuitsb98154No ratings yet

- ARCAM AVR400 Service Manual Issue 1 Page 15 Page 24Document34 pagesARCAM AVR400 Service Manual Issue 1 Page 15 Page 24RoJuNo ratings yet

- Maquet Lucea 10050 PDFDocument2 pagesMaquet Lucea 10050 PDFpatrick1009No ratings yet

- NPDCL New Connection Application FormDocument3 pagesNPDCL New Connection Application FormSangameshwar LabhishettyNo ratings yet

- DatasheetDocument20 pagesDatasheetBinh NguyenNo ratings yet