Professional Documents

Culture Documents

TD Aula8 PDF

Uploaded by

Kaciane MarquesOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

TD Aula8 PDF

Uploaded by

Kaciane MarquesCopyright:

Available Formats

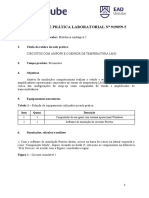

Universidade Federal de Pelotas

Instituto de Fsica e Matemtica

Departamento de Informtica

Bacharelado em Cincia da Computao

Aula 8

3. Implementao de circuitos digitais: Noes

sobre a tecnologia MOS, Transistores NMOS e PMOS,

Estrutura de portas lgicas CMOS estticas.

Prof. Jos Lus Gntzel

guntzel@ufpel.edu.br

www.ufpel.edu.br/~guntzel/TD/TD.html

T

T

cnicas Digitais

cnicas Digitais

slide 8.2

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

tomo de Silcio

Grande estabilidade fsica e

qumica em temperatura

4 eltrons na rbita externa:

valncia 4

permite uma obteno natural

do SiO2 - xido de silcio

Neutron Neutron

Pr Pr ton ton

N N cleo cleo

El El tron tron

Materiais Semicondutores

Reis99

slide 8.3

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

Cristal de Sil Cristal de Sil cio cio

Si Si

Si Si

Si Si

Si Si

Si Si

Si Si

Si Si

Si Si

Monocristal: Silcio Monocristalino

estrutura regular e homognea

ligaes covalentes

material quimicamente estvel

Em estado puro (intrnsico):

mau condutor a temperatura ambiente

isolante a baixas temperaturas

Aumento da temperatura:

provoca quebra das ligaes

um eltron livre provoca a formao de uma

lacuna

ocorre a gerao de pares eltrons-lacunas

Materiais Semicondutores

Reis99

slide 8.4

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

Mobilidade dos el Mobilidade dos el trons Mobilidade das lacunas trons Mobilidade das lacunas

! !n n ! !p p

OBS: Cerca de 3 vezes para o silcio e 30 vezes para o AsGa

Resistividade: capacidade de um material veicular corrente

depende: depende:

- concentrao de portadores (temperatura, dopagem)

- mobilidade dos portadores no material

Dopantes: tomos com excesso de eltrons ou de lacunas

dopantes do dopantes do tipo P tipo P: falta de eltrons exemplo: boro

dopantes do dopantes do tipo N tipo N: excesso de eltrons exemplo: fsforo

Materiais Semicondutores

Reis99

slide 8.5

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

Silcio Policristalino CONDUTOR

xido de Silcio SiO

2

Semicondutor Germnio ou

Silcio Monocristalino

xido de Silcio SiO

2

ISOLANTE

Silcio Monocristalino SEMICONDUTOR

Metal

Estrutura MOS

Reis99

slide 8.6

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

N

N

N

P

Poli

Silcio Policristalino

xido de Silcio

SiO

2

Silcio Monocristalino

Difuso N

Substrato P

Corte

transversal

Vista superior

(planta baixa)

O Transistor MOS

Reis99

slide 8.7

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

N N

N

N N

P P

Difuso N

Substrato P

planta baixa

Contato

Fonte

(source)

Dreno

(drain)

Grade

(gate)

corte

canal

G

D

S

Reis99

slide 8.8

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

N N N N

P P

Difuso N

Fonte Fonte Dreno

Grade= 0 V

canal aberto

N N N N

P P

Fonte Fonte

Dreno

Grade = VCC

canal fechado

G

D

S

Reis99

slide 8.9

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

Nas tecnologias MOS atuais:

Nveis Lgicos x Nveis de Tenso

0

0 Volts

(terra, massa, VSS, GND)

Nvel Lgico Nvel de Tenso

3.3, 1.5 ou

1.1 Volts

(Vdd, Vcc)

1

Smbolos

slide 8.10

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

NMOS

Os portadores majoritrios (responsveis

pela corrente eltrica) so os eltrons.

PMOS

Os portadores majoritrios so as lacunas

(falta de eltrons).

Transistores MOS

G

D

S

G

D

S

H dois tipos de transistores MOS:

slide 8.11

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

Funcionamento Simplificado: uma chave eletrnica

O Transistor NMOS

G = 0

D

S

G = 1

D

S

S

D

chave aberta

(sem corrente eltrica)

D!S

S

D

chave fechada

com corrente eltrica at que

D=S

slide 8.12

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

Funcionamento Simplificado: uma chave eletrnica

O Transistor PMOS

G = 0

D

S

G = 1

D

S

S

D

chave fechada

com corrente eltrica at que

D=S

S

D

chave aberta

(sem corrente eltrica)

D!S

slide 8.13

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

Srie

Associaes de Transistores NMOS

A

X

B

Y

X=Y Se A=1 E B=1

variveis de

controle

Problema:

o transistor NMOS no conduz

bem o nvel lgico 1

slide 8.14

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

Paralelo

Associaes de Transistores NMOS

A

X

B

Y

X=Y Se A=1 OU B=1

variveis de

controle

slide 8.15

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

Srie

Associaes de Transistores PMOS

X=Y Se A=0 E B=0

variveis de

controle

A

X

B

Y

Problema:

o transistor PMOS no conduz

bem o nvel lgico 0

slide 8.16

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

Paralelo

Associaes de Transistores PMOS

A

X=Y Se A=0 OU B=0

variveis de

controle

X

B

Y

slide 8.17

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

Portas Lgicas CMOS: o Inversor

Tabela-verdade

Esquemtico

lgico

Esquemtico de

transistores

E S

0 1

1 0

S E

E S

Vcc

slide 8.18

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

Representao como chaves

E

S

E S

C

L

Representao eltrica

da carga conectada na

sada da porta

Transistores vistos como

chaves eletrnicas

Portas Lgicas CMOS: o Inversor

slide 8.19

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

Funcionamento Esttico:

2 situaes possveis

Portas Lgicas CMOS: o Inversor

0 1

1 0

S E

E=1

S=0

C

L

= 0 V

3.3 V

E=0 S=1

C

L

= 3.3 V

3.3 V

slide 8.20

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

As redes pull-up e pull-down so duais.

Portas Lgicas CMOS: esquema geral

E1 E1

E2 E2

E3 E3

E1 E1

E2 E2

E3 E3

Vdd

GND GND

S = f (E1,E2,E3)

Somente transistores PMOS

Somente transistores NMOS

Rede P

(pull-up)

Rede N

(pull-down)

slide 8.21

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

Tabela-verdade

Esquemtico lgico Esquemtico de transistores

0 1 1

1 0 1

1 1 0

1 0 0

S B A

A

S

B

Portas Lgicas CMOS: NAND de 2 entradas

A

S

B

A B

Vcc

slide 8.22

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

Representao como chaves

A

S

B

A B

Este capacitor

representa a

carga conectada

na sada da

porta

A

S

B

A B

C

L

Portas Lgicas CMOS: NAND de 2 entradas

Vcc

slide 8.23

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

Portas Lgicas CMOS: NAND de 2 entradas

Funcionamento

Esttico:

4 situaes possveis

A=0

S=1

B=0

A=0 B=0

C

L

=3.3V

3.3V

A=0

S=1

B=1

A=0

B=1

C

L

=3.3V

3.3V

A=1

S=0

B=1

A=1

B=1

C

L

=0 V

3.3V

A=1

S=1

B=0

A=1 B=0

C

L

=3.3V

3.3V

0 1 1

1 0 1

1 1 0

1 0 0

S B A

slide 8.24

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

Esquemtico lgico

Esquemtico de transistores

A

S

B

C

A

S

B

A

B

C

C

0 1 1 1

1 0 1 1

1 1 0 1

1 0 0 1

1 1 1 0

1 0 1 0

1 1 0 0

1 0 0 0

S C B A

Por motivos eltricos,

no aconselhvel se

usar mais de 4

transistores em srie

Portas Lgicas CMOS: NAND de 3 entradas

Vcc

slide 8.25

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

Tabela-verdade

Esquemtico lgico

Esquemtico de transistores

0 1 1

0 0 1

0 1 0

1 0 0

S B A

A

S

B

Portas Lgicas CMOS: NOR de 2 entradas

A

S

B

A

B

Vcc

slide 8.26

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

Portas Lgicas CMOS: NOR de 2 entradas

A=0

S=1

B=0

A=0

B=0

C

L

=3.3V

3.3V

A=0

S=0

B=1

A=0

B=1

C

L

=0V

3.3V

A=1

S=0

B=0

A=1

B=0

C

L

=0V

3.3V

A=1

S=0

B=1

A=1

B=1

C

L

=0V

3.3V

0 1 1

0 0 1

0 1 0

1 0 0

S B A

Funcionamento

Esttico:

4 situaes possveis

slide 8.27

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

S = A+BC

Exemplo:

A

S

B

C

Portas Lgicas CMOS: portas complexas

Tambm chamadas SCCG

(Static CMOS Complex Gates)

Esquemtico de transistores

Esquemtico lgico

A

S

B

A

B

C

C

Vcc

slide 8.28

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

Como obter o esquemtico a partir da equao

Se a equao no for negada, imagine-a negada. No final,

ser necessrio colocar um inversor na sada

Tome a equao sem a negao e construa a rede N

Operao E equivale a srie

Operao OU equivale a paralelo

Construa a rede P, fazendo o dual da rede N, ou seja:

Tudo que est em srie na rede N aparecer em paralelo na rede P

Tudo que est em paralelo na rede N aparecer em srie na rede P

Portas Lgicas CMOS: portas complexas

slide 8.29

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

S = A(B+C)+DE

Construa o esquemtico de transistores para a seguinte

funo

Exerccio 3.1

A

S

B

D

E

C

Seu esquemtico lgico :

Portas Lgicas CMOS: portas complexas

slide 8.30

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

S = A(B+C)+DE

Soluo:

Portas Lgicas CMOS: portas complexas

A

C

B

D

E

C

B

A

D E

S

Vcc

slide 8.31

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

S = XY(red+blue)

Construa o esquemtico de transistores para a seguinte

funo

Exerccio 3.2

Como a funo fornecida no negativa, constri-se a porta complexa

negando-se a funo e colocando um inversor na sada da porta:

Portas Lgicas CMOS: portas complexas

Y

S

red

blue

X

slide 8.32

3. Implementao de Circuitos Digitais

ComputaoUFPel

Tcnicas Digitais - semestre 2006/2

Prof. Jos Lus Gntzel

Bibliografia para este captulo

Tecnologia de Fabricao CMOS:

REIS, Ricardo.(Organizador.) Concepo de Circuitos Integrados. Porto Alegre:

Sagra-Luzzatto/UFRGS, 2002. 2

a

edio. ISBN 85-241-0625-5 (Equivalente ao

livro da 1

a

Escola de Microeletrnica da SBC/Sul h 7 exemplares na Biblioteca.)

Portas Lgicas CMOS:

[1] BROWN, Stephen; VRANESIC, Zvonko. Fundamentals of Digital Logic

With VHDL Design. New York: McGraw Hill, 2004. 2

a

edio. (h um exemplar

na biblioteca, com previso de compra de mais 3 exemplares)

[3] UYEMURA, John P. Sistemas Digitais - uma abordagem integrada. So

Paulo: Pioneira Thomson Learning, 2002.

WAGNER, Flvio; REIS, Andr; RIBAS, Renato P. Fundamentos de Circuitos

Digitais. Porto Alegre: Sagra-Luzzatto/UFRGS, 2006. ISBN 85-241-0703-0

You might also like

- Resumao de Derivadas Do Responde AiDocument8 pagesResumao de Derivadas Do Responde AiKaciane MarquesNo ratings yet

- Cálculo I - FinalDocument221 pagesCálculo I - FinalandysarmientoNo ratings yet

- 2x - Matlab No ControloDocument8 pages2x - Matlab No Controlosoares.nguerra8634No ratings yet

- Filtros 2Document31 pagesFiltros 2Kaciane MarquesNo ratings yet

- CE II A7 Realimentacao 2Document25 pagesCE II A7 Realimentacao 2Kaciane MarquesNo ratings yet

- Minha Biblioteca - Ciências ExatasDocument18 pagesMinha Biblioteca - Ciências ExatasKaciane MarquesNo ratings yet

- Normalizacao1 PDFDocument5 pagesNormalizacao1 PDFdinei_2008No ratings yet

- Apostila - PSIMDocument25 pagesApostila - PSIMbruno_bit100% (2)

- Aula ADC 20131Document10 pagesAula ADC 20131Kaciane MarquesNo ratings yet

- Psi2223 Aula 20-2013Document16 pagesPsi2223 Aula 20-2013Kaciane MarquesNo ratings yet

- Um Pouco Mais de Cardinalidades e Relacionamentos1Document38 pagesUm Pouco Mais de Cardinalidades e Relacionamentos1Kaciane MarquesNo ratings yet

- Cap 3Document35 pagesCap 3Kaciane MarquesNo ratings yet

- 8a AulaDocument15 pages8a Aularele_lampagoNo ratings yet

- TCFE07082 10 Analise Circuitos TJBDocument30 pagesTCFE07082 10 Analise Circuitos TJBEverson Cabrera100% (1)

- Sinais Aleatórios e Processamento Da Fala - MatlabDocument9 pagesSinais Aleatórios e Processamento Da Fala - MatlabRil SilvaNo ratings yet

- Te072 Aula6Document50 pagesTe072 Aula6Kaciane MarquesNo ratings yet

- Apsi 02Document73 pagesApsi 02Kaciane MarquesNo ratings yet

- Elc 1115 PRG Sinais e SistemasDocument2 pagesElc 1115 PRG Sinais e SistemasKaciane MarquesNo ratings yet

- FILTROS 5PassaFaixaDocument14 pagesFILTROS 5PassaFaixaKaciane MarquesNo ratings yet

- Apostila HC08Document96 pagesApostila HC08Pedro DiasNo ratings yet

- DPEE 1069 PRG Circuitos Eletricos IIDocument2 pagesDPEE 1069 PRG Circuitos Eletricos IIKaciane MarquesNo ratings yet

- A Seguir, Uma Demonstração Do Livro. para Adquirir A Versão Completa em Papel, AcesseDocument8 pagesA Seguir, Uma Demonstração Do Livro. para Adquirir A Versão Completa em Papel, AcesseKaciane Marques100% (1)

- Livro Final 050813 RevisadoanaDocument254 pagesLivro Final 050813 RevisadoanaKaciane MarquesNo ratings yet

- 9TLA5 10RodriguesdaSilvaDocument10 pages9TLA5 10RodriguesdaSilvaKaciane MarquesNo ratings yet

- Calendar I o Academic o 2014Document9 pagesCalendar I o Academic o 2014Kiko LikoNo ratings yet

- Laplace Esiste MasDocument16 pagesLaplace Esiste MasKaciane MarquesNo ratings yet

- RESULTADOSUMULADocument1 pageRESULTADOSUMULAKaciane MarquesNo ratings yet

- Cont Adores V HDLDocument10 pagesCont Adores V HDLKaciane MarquesNo ratings yet

- Cont Adores V HDLDocument10 pagesCont Adores V HDLKaciane MarquesNo ratings yet

- SCR Triac 2017 PDFDocument42 pagesSCR Triac 2017 PDFSilva Joao100% (1)

- J1939 PDFDocument11 pagesJ1939 PDFEdson GoncalvesNo ratings yet

- Lista 2 CircuitosDocument7 pagesLista 2 Circuitosmvmonteiromv123No ratings yet

- Medidas de Proteção Coletiva.Document50 pagesMedidas de Proteção Coletiva.Leonardo MarinhoNo ratings yet

- Nestor Agostini - Circuitos Elétricos IndustriaisDocument75 pagesNestor Agostini - Circuitos Elétricos IndustriaisLuan SilvaNo ratings yet

- Questões EUF EletromagnetismoDocument10 pagesQuestões EUF EletromagnetismoCafis UfpaNo ratings yet

- Motor CC BasicoDocument3 pagesMotor CC BasicoDébora MartinsNo ratings yet

- Atividade Desafio - GabriellaDocument7 pagesAtividade Desafio - GabriellaHenrique MalloneNo ratings yet

- Bragamça Enem Eletricidade Aula 03Document16 pagesBragamça Enem Eletricidade Aula 03Dogo MakerNo ratings yet

- Ged 4101Document110 pagesGed 4101André Luis Marin SimõesNo ratings yet

- F329 - Relatorio Circuito RCDocument8 pagesF329 - Relatorio Circuito RCAnderson XavierNo ratings yet

- Fenômenos Ondulatórios - o Que São e Exemplos - PrePara ENEMDocument8 pagesFenômenos Ondulatórios - o Que São e Exemplos - PrePara ENEMluis cassimooNo ratings yet

- Relatório Da Aula Pratica: ResumoDocument3 pagesRelatório Da Aula Pratica: ResumoDjalma Neto50% (2)

- M. de Luz. O Convencionalismo de PoincaréDocument16 pagesM. de Luz. O Convencionalismo de PoincaréHelioNo ratings yet

- Mapa Eletromagnetismo Walter Barbosa Couto JuniorDocument10 pagesMapa Eletromagnetismo Walter Barbosa Couto Juniorwbarco93No ratings yet

- Exercícios OndasDocument7 pagesExercícios OndasEmilly NayaliNo ratings yet

- Instalações Elétricas Prediais Vol 4Document71 pagesInstalações Elétricas Prediais Vol 4Luis Ricardo Gonzalez SantosNo ratings yet

- Pratica 5EA2 CircuitoscomAmpopseosensorLM35Document6 pagesPratica 5EA2 CircuitoscomAmpopseosensorLM35João Victor de França GomesNo ratings yet

- Manual DWMM3Document87 pagesManual DWMM3Humberto Erler86% (7)

- Arc Calculator v1.5Document1 pageArc Calculator v1.5Hugo Pinheiro100% (1)

- Anexo III Modelo de Memorial Tecnico DescritivoDocument14 pagesAnexo III Modelo de Memorial Tecnico DescritivoRaquel Kobus LoskarNo ratings yet

- Segurança em Eletrotécnica - IFPR PDFDocument142 pagesSegurança em Eletrotécnica - IFPR PDFEdina AlvesNo ratings yet

- Curso de Eletrônica, TV, Vídeo, CD e DVD - Cursos Edubras PDFDocument5 pagesCurso de Eletrônica, TV, Vídeo, CD e DVD - Cursos Edubras PDFGilson BarbozaNo ratings yet

- AI Esquemas Eletricos de ComandoDocument40 pagesAI Esquemas Eletricos de ComandothiagoNo ratings yet

- Guia Aula Prática 01Document3 pagesGuia Aula Prática 01Milene OliveiraNo ratings yet

- Capitulo 07 - EletroquimicaDocument12 pagesCapitulo 07 - EletroquimicaPedro LessaNo ratings yet

- Catalogo IPCEDocument25 pagesCatalogo IPCEHernan GirautNo ratings yet

- Convertitori Di Frequenza ACS355: Manuale UtenteDocument434 pagesConvertitori Di Frequenza ACS355: Manuale UtenteAbrakain69No ratings yet

- Conversores DuaisDocument12 pagesConversores DuaisJohnantan SantosNo ratings yet

- 1 Perguntas Básicas EletricidadeDocument2 pages1 Perguntas Básicas EletricidadeFabio RodriguesNo ratings yet