Professional Documents

Culture Documents

Lecture 22

Uploaded by

Sivanantham SadhasivamCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lecture 22

Uploaded by

Sivanantham SadhasivamCopyright:

Available Formats

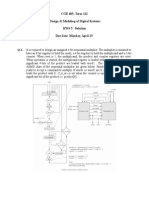

ECE 4514

Digital Design II

Spring 2008

Lecture 22:

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Lecture 22:

Design Economics:

FPGAs, ASICs, Full Custom

A Tools/Methods Lecture

Patrick Schaumont

Overview

Wows and Woes of scaling

The case of the Microprocessor

How efficiently does a microprocessor use transistors ?

Alternative Technologies: FPGA, ASIC, Full Custom

Energy Efficiency and Design Cost

ASIC Standard Cell Design

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

ASIC Standard Cell Design

Full Custom Design

Future Challenges in Digital Design

The Wows of scaling

Everybody is using Microprocessors because

PC's are everywhere

C compilers are everywhere

They get faster all the time

They get cheaper all the time

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

All this is thanks to technology scaling

Scaling enabled performance improvements

[Weste & Harris]

Feature Size =

Channel length L

of a transistor

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Microprocessor Transistor Count

[Weste & Harris]

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Microprocessor Clock Frequency

[Sima]

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Microprocessor Integer Performance

specint

92

[Sima]

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Microprocessor Architecture Efficiency

[Sima]

Breakpoint

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Microprocessor Architecture Efficiency

[Sima]

Breakpoint

Beyond this point,

improvements have been

obtained through

faster clock frequency

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

The Woes of scaling

Scaling provides more transistors that operate faster

Can do more operations per second

However

More transistors working faster will consume more power

(even when they're smaller)

Low-level electrical effects become dominant

Wires do not improve with scaling

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Wires do not improve with scaling

Processor Power Consumption

[Weste & Harris]

P

dyn

= a. C . V

2

. f

clk

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Low level electrical effects become dominant

dynamic power

[Weste & Harris]

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

static power

Wires do not improve with scaling

Chip

Area reachable in

a single clock cycle

in technology N

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Area reachable in

a single clock cycle

in technology N+1

Caused by scaled wire geometry (R increases)

Wires even become slower than gates

[SIA97]

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

medium-long wire ..

(43u @ 90nm =

500 transistors long)

Can Microprocessors keep up with scaling?

Let's first see how efficient microprocessors really are.

We will try to evaluate how well a microprocessor

makes use of transistors, i.e. how performance and

number of transistors relate

We will compare that to the performance of a

dedicated hardware circuit

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Just a back-of-the-envelope calculation ..

Performance

Performance = [Operations / Second]

Here's a full adder cell

Input A, B, C (carry in)

Output Cout, S

10 gates

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Performance

Here's the same full adder cell, with transistors

Input A, B, C (carry in)

Output Cout, S

28 transistors (~ 2.8 / gate)

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Performance

Let's see how well the transistors in a Pentium III operate

Approx 10 million transistors (note: a Core2 has ~ 400 million..)

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Performance

Let's see how well the transistors in a Pentium III operate

Approx 10 million transistors

Chip frequency is 500 MHz

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Performance

Let's see how well the transistors in a Pentium III

operate

Approx 10 million transistors

Chip frequency is 500 MHz

So a 'perfect' P-III could do N 1-bit additions per second

N = # gates / (gates/addition) x fclk

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

N = # gates / (gates/addition) x fclk

N = 10.10

6

/ 28 x 500 x 10

6

We need 32 additions for an ALU operation

So the P-III has enough transistors to do

N/32 = 5580 Giga Operations per Second!

But a 500 MHz P-III gets you about 500 MIPS ..

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Performance

So, the potential parallellism of the P-III silicon is

10,000X higher then the achieved parallellism

Theoretically we should get about 5000 Gops

Practically we get 500 Mops

Where do we waste all this performance?

Sequential Execution of Instructions

Memory-Processor Bottleneck

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Memory-Processor Bottleneck

Bottom line: Raw hardware can be far more

computationally efficient then what can be achieved

with software on a Microprocessor

However, making use of all that parallelism is the core of the

problem

Alternatives over a Microprocessor ?

Possibly many, but let's just consider

Field Programmable Gate Array

ASIC

Full-custom

Note that

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

FPGA = design + program ready-made chip

ASIC = design + fabricate custom chip

Full-custom = design + fabricate custom chip

Micro, FPGA, ASIC, Full Custom

Let's compare these four target technologies on the

basis of two arguments (which is incomplete ..)

Energy Efficiency: the amount of operations per unit of energy

Design Cost: the amount of $ per chip

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Energy Efficiency

Many applications need high performance but cannot

afford high power consumption: cell phones, ipods,

laptops, portable electronics, ..

Energy Efficiency = [Operations / Joule]

= [Operations / Second] / [Joule / Second]

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

= [Operations / Second] / [Joule / Second]

= Performance / Power

Energy Efficiency

Source: T.Claasen et al. (ISSCC99)

1000

100

10

Computing efficiency (GOPS/Watt)

Our back-of-the-envelope

Each time you reduce Voltage,

the Energy Efficiency improves

with a step

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

2 1 0.5 0.25 0.13 0.07

feature size( m)

1

0.1

0.01

0.001

Our back-of-the-envelope

calculations found this to

be four orders of magnitude

Here, it's bigger then two

P-III technology

The Energy-Flexibility Conflict

Source: T.Claasen et al. (ISSCC99)

1000

100

10

Computing efficiency (GOPS/Watt)

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

2 1 0.5 0.25 0.13 0.07

feature size( m)

1

0.1

0.01

0.001

P-III technology

The Energy-Flexibility Conflict

Source: T.Claasen et al. (ISSCC99)

1000

100

10

Computing efficiency (GOPS/Watt)

Let's say an application

requires 5 GOps/Watt

(e.g. speech recognition

on a cell phone)

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

2 1 0.5 0.25 0.13 0.07

feature size( m)

1

0.1

0.01

0.001

If you only have 0.5 micron technology,

you'll need to do a full hardware design

The Energy-Flexibility Conflict

Source: T.Claasen et al. (ISSCC99)

1000

100

10

Computing efficiency (GOPS/Watt)

Let's say an application

requires 5 GOps/Watt

(e.g. speech recognition)

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

2 1 0.5 0.25 0.13 0.07

feature size( m)

1

0.1

0.01

0.001

A few years later, when there is better technology,

you may be able to do it in software on a processor

Cost

The cost of a microprocessor is just a per-part cost,

maybe with some additional tools (GUI, compiler, etc,

..)

Eg. typical 32-bit microprocessor ~ $15 in small quantities

The cost of an FPGA is also just a per-part cost.

Eg. Spartan3E S500 ~ $30 in small quantities

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Cost of ASIC and Full-Custom Design

Total Cost of Design has two components:

Non-recurring engineering costs (NRE): Costs independent of

the number of components sold

Recurring costs (R): Costs proportional to the number of

components sold

Total Cost of Design = NRE + n . R, with n the number

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Total Cost of Design = NRE + n . R, with n the number

of components sold.

For high-volume products (e.g. RAM, Processors), n is very high,

and the role of NRE is less important

For low-volume products (e.g. Application-specific designs), n is

low, and the role of NRE is more important

Cost

NRE = Design + Prototype Creation

Design

Personnel and Engineering (~ $80K per MY)

Computers (~$5K per MY)

CAD Software ($10K .. $1M per seat)

Prototype Creation

For Custom chips (ASIC/Full Custom) ~ $1M

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

For Custom chips (ASIC/Full Custom) ~ $1M

PCB Development

R = Production Cost per component

Depends on process, package, testing complexity, yield

Typical NRE for medium-size custom chip

(7 digital designers, 3 analog designers, 5 support)

[Weste & Harris]

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Cost

Total Cost

$

Spartan 3ES500: $31

Atmel AT91: $16

FPGA,

Microprocessor

ASIC,

Full-Custom

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Units

Produced

NRE

For low-volume products,

programmable parts

are cheaper

For high-volume products,

custom parts are cheaper

NRE of programmable

products is very low, because

we don't need to build a chip

(Spartan Board ~ $100)

Performance, Efficiency, Cost, Design Time

Given a single application implemented on

Microprocessor, FPGA, ASIC, Full Custom, then a

relative appreciation of these factors is as follows

Recurring

Energy

Application

Design

Cost

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Microprocessor

FPGA

ASIC

Full Custom

NRE

Recurring

Cost Performance

Energy

Efficiency

Design

Time

FPGA vs Standard Cell ASIC

Compared to FPGA, ASIC uses custom wiring pattern,

and dedicated standard cells

Comparison 90nm FPGA with 90nm ASIC [Kuon 06] :

Area difference 40X (no custom blocks), 21 X (with custom)

Performance (f

max

) 4X

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Performance (f

max

) 4X

Dynamic Power 12X

Note that FPGA technology tends to be 1 - 2

generations ahead of ASIC designs

E.g. Now (04/08) Virtex5 FPGA uses 65nm, while standard

cell kit from IBM uses 130nm

Full Custom

Instead of using standard cells, we can design a full

chip at transistor level.

Certain regular structures (memory cells, datapath bit-

slices) can be made very dense in this manner

Designers have to work according

to 'design rules': specific

topological constraints

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

topological constraints

to guarantee that a resulting

chip will work

Full Custom vs ASIC

Additional effort of full custom over ASIC yields better

performance, area, and power consumption:

Speed: 3X .. 8X times faster

Area: 15X times smaller (depending on application)

Power: 3X .. 10X times smaller

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Technology Challenges for Digital Design

How to design faster ?

Raise the abstraction level

Reuse

How to build efficient on-chip communications?

On-chip busses

On-chip networks

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

How to reduce power consumption ?

A general trend: more parallellism

Example: RAW Microprocessor

Multiple CPU work in parallel, reduce f

max

CPUs pass around 'packets' among each other, chip traversal

takes multiple clock cycles

Addresses Challenge #1 and #2

Needs 16 parallel programs to run ... (ouch)

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

Summary

Wows and Woes of scaling

The case of the Microprocessor

How efficient does a microprocessor use transistors ?

Alternative Technologies: FPGA, ASIC, Full Custom

Energy Efficiency and Design Cost

ASIC Standard Cell Design

Patrick Schaumont

Spring 2008

ECE 4514 Digital Design II

Lecture 22: Design Economics

ASIC Standard Cell Design

Full Custom Design

Future Challenges in Digital Design

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Registration FormatDocument1 pageRegistration FormatSivanantham SadhasivamNo ratings yet

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Vlsid2021 CFP V1 PDFDocument2 pagesVlsid2021 CFP V1 PDFSivanantham SadhasivamNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Semiconductor IndustryDocument2 pagesSemiconductor IndustrySivanantham SadhasivamNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Ece5015 Digital-Ic-Design Eth 1.0 40 Ece5015Document2 pagesEce5015 Digital-Ic-Design Eth 1.0 40 Ece5015Sivanantham SadhasivamNo ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- CSIR JRF GuidelinesDocument13 pagesCSIR JRF GuidelinesSivanantham SadhasivamNo ratings yet

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Vlsid2021 CFP V1 PDFDocument2 pagesVlsid2021 CFP V1 PDFSivanantham SadhasivamNo ratings yet

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Vlsi Qa2 PDFDocument19 pagesVlsi Qa2 PDFamiteshtripathiNo ratings yet

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- RC DFT GuideDocument58 pagesRC DFT GuideSivanantham Sadhasivam0% (1)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- QuestionDocument16 pagesQuestionSivanantham SadhasivamNo ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Verilog Tutorial 1Document6 pagesVerilog Tutorial 1Sivanantham SadhasivamNo ratings yet

- Hierarchical ModelingDocument23 pagesHierarchical ModelingSivanantham SadhasivamNo ratings yet

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- COE 405, Term 122 Design & Modeling of Digital Systems HW# 5 Solution Due Date: Monday, April 15Document6 pagesCOE 405, Term 122 Design & Modeling of Digital Systems HW# 5 Solution Due Date: Monday, April 15Sivanantham SadhasivamNo ratings yet

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- v1Document5 pagesv1Sivanantham SadhasivamNo ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- 4106 Revised Syllabus Spring08Document9 pages4106 Revised Syllabus Spring08Sivanantham SadhasivamNo ratings yet

- School of Electronics EngineeringDocument1 pageSchool of Electronics EngineeringSivanantham SadhasivamNo ratings yet

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Keshab K Parhi Digital Signal Processing Architecture Chapter 3 SolutionDocument7 pagesKeshab K Parhi Digital Signal Processing Architecture Chapter 3 SolutionNESEGA29% (7)

- Verilog Lecture-Sequential LogicDocument41 pagesVerilog Lecture-Sequential LogicSivanantham SadhasivamNo ratings yet

- VLSI Design and Implementation of Low Power MAC Unit With Block Enabling TechniqueDocument11 pagesVLSI Design and Implementation of Low Power MAC Unit With Block Enabling TechniqueSivanantham SadhasivamNo ratings yet

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Chapter 2 Capacitor and Dielectrics 2016 ReviewedDocument69 pagesChapter 2 Capacitor and Dielectrics 2016 ReviewedSyaza IzzatyNo ratings yet

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Superconducting Magnetic Energy StorageDocument7 pagesSuperconducting Magnetic Energy StorageAnton Fatoni100% (1)

- 8.electrical Lighting - Large FontsDocument23 pages8.electrical Lighting - Large FontsAnuradha SkaNo ratings yet

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- TT2148 SanyoDocument4 pagesTT2148 Sanyokhawar mukhtarNo ratings yet

- Computer HistoryDocument3 pagesComputer HistoryNanda KishoreNo ratings yet

- Microfabrication Technologies: MECH 466 Microelectromechanical SystemsDocument19 pagesMicrofabrication Technologies: MECH 466 Microelectromechanical SystemsMohana Sundaram Ma NiNo ratings yet

- Electronic Circuits 1 SyllabusDocument2 pagesElectronic Circuits 1 SyllabusJonathon MartinezNo ratings yet

- Chapter 20 AssessmentDocument3 pagesChapter 20 AssessmentAlex Willis50% (2)

- Modulo Pesaje Hardy 1769 2WSDocument82 pagesModulo Pesaje Hardy 1769 2WSCarlos Alberto Vaca SuarezNo ratings yet

- Programming MicroprocessorsDocument282 pagesProgramming Microprocessorsconditioned_genesis1504100% (1)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Atc Q-Bridge Thermal ConductorDocument4 pagesAtc Q-Bridge Thermal ConductorwjsynNo ratings yet

- TRX Klopik Main Board V 2.1 ENGDocument5 pagesTRX Klopik Main Board V 2.1 ENGȺɌįfNo ratings yet

- FT Vitovolt 300, PXXX ADDocument2 pagesFT Vitovolt 300, PXXX ADovidiuNo ratings yet

- PR Elka AnalogDocument9 pagesPR Elka AnalogzackyzackNo ratings yet

- General Catalog en GrindingDocument10 pagesGeneral Catalog en GrindingkarthikNo ratings yet

- PTC Thermistors For DegaussingDocument9 pagesPTC Thermistors For DegaussingmetaldeathNo ratings yet

- DFDFDFDG SFDGDGFDocument5 pagesDFDFDFDG SFDGDGFmongiagoldyNo ratings yet

- Qcs 2014 - Sec21 p4 - Motor StartersDocument6 pagesQcs 2014 - Sec21 p4 - Motor StarterschandraNo ratings yet

- Online Sensors-Water SystemDocument41 pagesOnline Sensors-Water SystemsagbvnNo ratings yet

- Controlcat NewHorizionsDocument100 pagesControlcat NewHorizionsSergio Castillo PerezNo ratings yet

- Czujniki KCCDocument11 pagesCzujniki KCCDinhnamsgpNo ratings yet

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Flash MemoryDocument15 pagesFlash MemoryCRT07No ratings yet

- Design of High Gain LNA Using 180nm CMOS For Wearable Devices NetworkDocument7 pagesDesign of High Gain LNA Using 180nm CMOS For Wearable Devices NetworkIJRASETPublicationsNo ratings yet

- Az1084s2 Adje1Document21 pagesAz1084s2 Adje1Altamiro RochaNo ratings yet

- 8-Bit Single Chip Microcontroller LC87F67C8ADocument27 pages8-Bit Single Chip Microcontroller LC87F67C8AAlbert GTNo ratings yet

- BN44 00277a PDFDocument5 pagesBN44 00277a PDFOlivier OuinaNo ratings yet

- Method For Aluminum Oxide Thin Films Prepared Through Low Temperature Atomic Layer Deposition For Encapsulating Organic Electroluminescent DevicesDocument11 pagesMethod For Aluminum Oxide Thin Films Prepared Through Low Temperature Atomic Layer Deposition For Encapsulating Organic Electroluminescent DevicesjayaneNo ratings yet

- Ejercicios Cap05Document8 pagesEjercicios Cap05Miguel LiceagaNo ratings yet

- TDA5051Document28 pagesTDA5051memurtNo ratings yet

- Introduction To Pic 16F877ADocument37 pagesIntroduction To Pic 16F877AAbdul Muqeet Ahmed KhanNo ratings yet