Professional Documents

Culture Documents

Lab Manual

Uploaded by

Syaoran7LiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lab Manual

Uploaded by

Syaoran7LiCopyright:

Available Formats

LAB MANUAL

ELECTRICAL ENGINEERING MATERIALS &

SEMICONDUCTOR DEVICES LAB

(EC-317-F)

III SEMESTER ECS

Department of Electronics & Communication Engg.

Dronacharya College of Engineering

Khentawas, Gurgaon 123506

EEMSD LAB (EC-317-F)

LIST OF EXPERIMENTS

S.NO.

NAME OF THE EXPERIMENT

Page

No.

3-5

1.

Study of V-I Characteristics of a Diode.

2.

To Study the characteristics of transistor in Common Base

configuration.

6-8

To plot and study the input and output characteristics of BJT in

common-emitter configuration.

9-10

4.

Study of V-I characteristic of photovoltaic cell.

11-12

5.

To study and draw the characteristics of FET in common source

configuration.

13-15

Study of characteristics of JFET in Common Source Configuration.

16-18

7.

Study characteristics of SCR.

19-20

8.

9.

10.

Study of characteristics of UJT.

Study of characteristics of DIAC.

To plot V-I characteristic of TRIAC.

21-22

23-25

26-28

11.

To study photo-resist in metal pattern for planner technology/PCB

technology.

29-30

12.

To study zener diode characteristics.

31-34

13.

To study zener diode as voltage regulator.

35-36

14

To study and draw the characteristics of FET in common drain

configuration.

37-39

15

To study VMOS Technology.

40-41

6.

LAB MANUAL (III SEM ECS)

Page2

EEMSD LAB (EC-317-F)

EXPERIMENT NO. 1

AIM: To Study V-I Characteristics of a Diode.

APPARATUS REQUIRED:

Diode Characteristics Kit, Power Supply,

Ammeter (0-20mA), Voltmeter (0-20V), Connecting Leads.

BRIEF THEORY: A P-N junction is known as Semiconductor diode or Crystal

diode. It is the combination of P-type & N-type Semiconductor. This offers nearly

zero resistance to current on forward biasing & nearly infinite Resistance to the flow

of current when in reverse biased.

Forward biasing: When P-type semiconductor is connected to the +ve terminal and

N-type to ve terminal of voltage source. Nearly zero resistance is offered to the flow

of current.

Reverse biasing: When P-type semiconductor is connected to the ve terminal and

N-type to +ve terminal. Nearly zero current flow in this condition.

CIRCUIT DIGRAM:

(1) When diode is forward biased

R2A

1

(2) When diode is reverse biased

mA

R2A

16

BT2

mA

16

1

D10

V

BT2

D10

PROCEDURE:

(1)

(2)

(3)

(4)

(5)

(6)

Connect the circuit as shown in fig.

Switch on the power supply.

Vary the value of input dc supply in steps.

Note down the ammeter & voltmeter readings for each step.

Plot the graph of Voltage Vs Current.

Connect the circuit as shown in fig.

OBSERVATION TABLE:

S.NO

When Diode Is Forward

Biased

Current(m Voltage(V)

A)

When Diode Is Reverse

Biased

Current

Voltage(V)

[A)

1.

LAB MANUAL (III SEM ECS)

Page3

EEMSD LAB (EC-317-F)

2.

3.

GRAPH:

RESULT: The graph has been plotted between voltage and current.

DISCUSSION: The diode doesnt conduct in RB state and conduct in FB state.

PRECAUTIONS:

(1)Always connect the voltmeter in parallel & ammeter in series as shown in fig.

(2)Connection should be proper & tight.

(3)Switch ON the supply after completing the circuit

(4)DC supply should be increased slowly in steps

(5)Reading of voltmeter & Ammeter should be accurate.

QUIZ:

Q.1 Define semiconductor diode?

A. A PN junction is called semiconductor diode.

Q.2 Define depletion layer?

A. The region having uncompensated acceptor and donor ions.

Q.3 what do you mean by forward biased?

A. When +ve terminal of battery is connected to P side & -ve terminal to N side of

diode.

Q.4 what do you mean by reverse biased?

A. When +ve terminal of battery is connected to N side & -ve terminal to P side of

diode.

Q.5 Define Knee voltage?

A. The forward voltage at which current through the junction starts increasing rapidly.

Q.6 Define breakdown voltage?

A. Reverse voltage at which PN junction breaks down with sudden rise in reverse

current.

Q.7 Define max. Forward current?

LAB MANUAL (III SEM ECS)

Page4

EEMSD LAB (EC-317-F)

A. It is highest instantaneous forward current that a PN junction can conduct without

damage to Junction.

Q.8 Define max. Power rating?

A. Max. Power that can be dissipated at junction without damage to it.

Q.9. What is ideal diode?

A. Diode have been ideal if it acted as perfect conductor (resistance zero) when

forward biased and as a perfect insulator (resistance infinite) when reverse biased.

Q10.What are the application of pn diodes?

Ans. As rectifiers in dc power supplies, in demodulation or detector circuits.

LAB MANUAL (III SEM ECS)

Page5

EEMSD LAB (EC-317-F)

EXPERIMENT NO. 2

AIM: To Study the characteristics of transistor in Common Base

configuration.

APPARATUS REQUIRED : Power supply, Transistor characteristics Kit,

Connecting Leads, Voltmeter, Ammeter.

BRIEF THEORY: Transistor is a semiconductor device consists of two p-n

junctions. It has three terminals, to handle I/P and O/P four terminals are needed.

Therefore, one terminal is made common. A transistor can be connected in three

Ways CB, CE, and CC.

Common base: Base is made common. I/P is connected between base & emitter and

O/P is taken between base & collector.

Input charact. The curve plotted between emitter current I & the emitter-base

voltage constant collector-base voltage V.

Output charact. The curve plotted between collector current I & collector-base

voltage V constant emitter current I.

.

CIRCUIT DIAGRAM :

PROCEDURE:

Input charact.

(a) Make the connection as per circuit diagram .

(b) Switch ON the supply & set V = 0V

(c) Vary V in step & note down the emitter current I at each step .

(d) Set V = 1V & again repeat the same procedure .

(e) Draw the graph.

Output charact.

(a) Make the connection as per circuit diagram.

(b) Set the value of I = 1mA

LAB MANUAL (III SEM ECS)

Page6

EEMSD LAB (EC-317-F)

(c) Vary V in step & note down the collector current I at each step.

(d) Set I = 2mA & repeat the same procedure.

(e) Draw the graph.

OBSERVATION TABLE:

S.No

1.

2.

3.

Input charact.(Vcb=Cons.)

Ie(mA)

Veb(Volts)

Output charact. (Ie = Const.)

Ic(mA)

Vcb(Volts)

GRAPH:

RESULT: The input and output characteristics of transformer in CB configuration

has been plotted.

DISCUSSION: With the help of output characteristics we can calculate ac & dc

current gain in CB configuration.

PRECAUTIONS :

1.

2.

3.

4.

5.

Always connect the voltmeter in parallel & ammeter in series as shown in fig.

Connection should be proper & tight.

Switch ON the supply after completing the ckt.

DC supply should be increased slowly in steps

Reading of voltmeter & Ammeter should be accurate.

QUIZ:

Q1: What do you mean by biasing of transistor?

A. When dc voltages are applied across the different terminals of transistor, it is

called biasing.

Q2: What is d.c. current gain in common base configuration?

A. It is ratio of collector current(Ic) to emitter current (Ie).

Q3: What is typical value for d.c. current gain ?

A. 0.99

Q4: What is a.c. current gain in CB confifuration?

LAB MANUAL (III SEM ECS)

Page7

EEMSD LAB (EC-317-F)

A. It is ratio of change in collector current to change in emitter current.

Q5: What are input characteristics?

A. These curves relate i/p current & i/p voltage for a given value of o/p voltage.

Q6: What are output characteristics?

A. Thes curves relate o/p voltage & o/p current for a given value of input current.

Q7: Which configuration has highest voltage gain?

A. Common Emitter.

Q8: Which configuration is most widely used?

A. Common Emitter.

Q9: What is operating point?

A. The zero signal values of Ic & Vce.

Q10: Which reigon is heavily doped in Transistot?

A. Emitter

LAB MANUAL (III SEM ECS)

Page8

EEMSD LAB (EC-317-F)

EXPERIMENT NO. 3

AIM: - To plot and study the input and output characteristics of BJT

in common-emitter configuration.

APPARATUS REQUIRED: - Transistor Characteristic kit, Multimeter,

Connecting leads and Power Supply.

THEORY: - In common Emitter configuration input is applied between base and

emitter while the output is taken across emitter and collector. Thus the emitter forms

the terminal common to doth input and output circuits. The load resistance is

connected at collector.

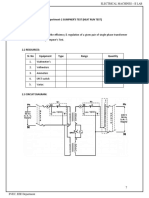

CIRCUIT DIAGRAM:R

mA

IC

mA

16 IB

R

16

1

VCE

12V

VBE

PROCEDURE:

(a)Connect the circuit as per the circuit diagram.

Input characteristics

a) Keep emitter - collector voltage constant.

b) Vary emitter-base voltage in steps and note down base current reading.

c) Readings are tabulated and graph is drawn.

Output characteristics

a) Keep base current constant.

b) Vary collector-emitter voltage in steps and note down emitter current.

c) Readings are tabulated and graph is drawn.

OBSERVATION TABLE:

Input charact.(Vce=Cons.)

S.No

Vbe(Volts)

Ib(mA)

1.

2.

3.

LAB MANUAL (III SEM ECS)

Output charact. (Ib = Const.)

Vce(Volts)

Ic(mA)

Page9

EEMSD LAB (EC-317-F)

GRAPH:-

RESULT:The input and output characteristic of transistor in common emitter

configuration has been plotted.

DISCUSSION: With the help of output characteristics we can calculate AC& DC

current gain in common emitter configuration.

PRECAUTIONS:

a) Connections should be tight

b) Handle the equipments with care

QUIZ:

Q1: What do you mean by biasing of transistor?

A. When dc voltages are applied across the different terminals of transistor, it is

called biasing.

Q2: What is d.c. current gain in common base configuration?

A. It is ratio of collector current(Ic) to emitter current (Ie).

Q3: What is typical value for d.c. current gain?

A. 0.99

Q4: What is a.c. current gain in CB configuration?

A. It is ratio of change in collector current to change in emitter current.

Q5: What are input characteristics?

A. These curves relate i/p current & i/p voltage for a given value of o/p voltage.

Q6: What are output characteristics?

A. The curves relate o/p voltage & o/p current for a given value of input current.

Q7: Which configuration has highest voltage gain?

A. Common Emitter.

Q8: Which configuration is most widely used?

A. Common Emitter.

Q9: What is operating point?

A. The zero signal values of Ic & Vce.

Q10: Which region is heavily doped in Transistor?

A. Emitter.

LAB MANUAL (III SEM ECS)

Page10

EEMSD LAB (EC-317-F)

EXPERIMENT NO. 4

AIM: Study of V-I characteristic of photovoltaic cell.

APPRATUS REQUIRED: Power supply, PVC characteristic Kit, connecting

leads, Voltmeter, Ammeter.

BRIEF THEORY : The silicon solar cell converts the radiant energy of the sun

into electrical power . The solar cell consist of a thin slice of single crystal p-type

silicon, unto 2cm square, into which a very thin(0.5 micron) layer of n-type material

is diffused . The conversion efficiency depends on the spectral content & the intensity

of the illumination.

CIRCUIT DIGRAM:

PROCEDURE :

(1)Connect the ckt. as shown in fig.

(2)Switch on the power supply.

(3)Vary the value of input dc supply in steps.

(4)Note down the ammeter & voltmeter readings for each step.

(5)Plot the graph of Voltage Vs Current.

OBSERVATION TABLE:

S.No Voltage(Volts)

1.

2.

3.

LAB MANUAL (III SEM ECS)

Current(mA)

Page11

EEMSD LAB (EC-317-F)

GRAPH:

RESULT: The V-I characteristics of photo voltaic cell has been plotted.

DISCUSSION: The solar cells are extensively employed as a source of power space

aircrafts & the advances in solar cell technology have found their way into many earth

based applications.

PRECAUTIONS:

6. Always connect the voltmeter in parallel & ammeter in series as shown in fig.

7. Connection should be proper & tight.

8. Switch ON the supply after completing the ckt.

9. DC supply should be increased slowly in steps

10. Reading of voltmeter & Ammeter should be accurate.

QUIZ:

Q1: What are photovoltaic cells?

A. These cells are semiconductor junction devices used for converting radiation

energy into electrical energy.

Q2: Which material is most commonly used for these cells?

A. Selenium & Silicon.

Q3: What are advantages of these cells?

A. They have ability to generate voltage without any bias & have fast response.

Q4: Compare use of photoconductive cells and photovoltaic cells.

A Photoconductive cells cannot be successfully switched at frequencies higher than

about 1 Khz , whereas photovoltaic cells can be switched successfully upto about 100

Khz and sometimes higher even.

LAB MANUAL (III SEM ECS)

Page12

EEMSD LAB (EC-317-F)

EXPERIMENT NO. 5

AIM: To study and draw the characteristics of FET in common

source configuration.

APPRATUS REQUIRED: Power supply, FET characteristic Kit, connecting

leads, two Multimeters.

BRIEF THEORY: A FET is a three terminal semiconductor device in which

current conduction is by one type of carries & is controlled by the effect of electric

field. There are two types of FET namely JFET & MOSFET. Again, a JFET can

either have N-channel or P-channel. A N-channel JFET has a N-type semiconductor

bar, the two ends of which make the Drain & source terminal. On the two sides of this

bar, P-N junction is made. This P region makes gate. Usually, these two gates are

connected Together to form a single gate .The gate is given a ve bias w.r.t source.

The Drain is given +ve potential w.r.t source.

CIRCUIT DIAGRAM:

mA

D

3 G

VDS

VGS

PROCEDURE:

(a)Connect the circuit as per the circuit diagram

Input characteristics

(b)Keep drain-source voltage constant

(c)Vary gate-source voltage in steps and note down drain current

(d) Readings are tabulated and graph is drawn

Output characteristics

(a)Keep gate-source voltage constant

(b)Vary drain-source voltage in steps and note down drain current.

(c) Readings are tabulated and graph is drawn

LAB MANUAL (III SEM ECS)

Page13

EEMSD LAB (EC-317-F)

INPUT CHARACTERISTIC

OUTPUT CHARACTERISTIC

OBSERVATION TABLE:

S. No

1

2

3

4

5

6

7

8

9

10

I/P at const. VDS

VGS (V)

ID (mA)

O/P at const. VGS

VDS (V)

ID (mA)

PRECAUTIONS:

(a)Connections should be tight

(b)Handle the equipments with care

RESULT: Input and output characteristics is obtained.

QUIZ:

Q.No QUESTION

1

Define FET?

How many types of FETs are there?

LAB MANUAL (III SEM ECS)

ANSWERS

The field effect transistor is a semi-conductor device

which depends for its operation on the control of

current by an electric field.

Two types (a) Junction field effect transistor (JFET).

(b) Metal Oxide Semiconductor FET(MOSFET

Page14

EEMSD LAB (EC-317-F)

Write advantages of FET over

conventional Transistor?

Advantages are

(a) Thermal stability. (b) Immunity to radiation

(c) High input impedance.

Write one disadvantage of FET?

Define Drain resistance?

Main disadvantage is relatively small Gain- Band

Width product.

Drain resistance can be defined as ratio of drain to

source voltage to drain current.

Define Tran conductance?

Define transfer characteristic of FET?

Write applications of a FET?

Applications of FET are

(A)Low noise amplifier (B) Buffer amplifier

(C) Cascade amplifier (D) Analog switch (E)Chopper

How is Drain current controlled in

JFET?

Define pinch-off voltage?

In JFET drain current is controlled by controlling the

reverse bias given to its base.

The value of drain-source voltage at which channel is

pinched off (i.e. all the free charges from the channel

are removed) is called pinch-off voltage.

10

LAB MANUAL (III SEM ECS)

Tran conductance can be defined as ratio of drain

current to gate to source voltage.

The curve drawn between drain current and gatesource voltage for a given value of drain-source

voltage.

Page15

EEMSD LAB (EC-317-F)

EXPERIMENT NO. 6

AIM: Study of characteristics of JFET in Common Source

Configuration.

APPARATUS REQUIRED: Power Supply, FET Characteristics Kit,

Connecting Leads, Voltmeter, and Ammeter.

BRIEF THEORY: A FET is a three terminal semiconductor device in which

current Conduction is by one type of carriers & is controlled by the effect of electric

field. There are two types of FET namely JFET & MOSFET. Again, a JFET can

either have N-channel or P-channel. A N-channel JFET has a N-type semiconductor

bar, the two ends of which make the Drain & source terminal. On the two sides of this

bar, P-N junction are made. This P region makes gate. Usually, these two gates are

connected together to form a single gate .The gate is given a ve bias w.r.t Source.

Drain is given +ve potential w.r.t Source.

CIRCUIT DIGRAM:

D

1

mA

3 G

VDS

VGS

PROCEDURE:

Drain characteristic

(a) Connect the circuit as shown in fig. Keep V & V supplies at minimum.

(b) Switch ON power, Increase V gradually & note the max. Current as I while

the V =0V

(c) Repeat the step for different values of V, & note corresponding I & V for

Increment.

(d) Tabulate the results.

Transfer characteristic

(a) Keep V fixed at 4V.

(b) Increase V in small steps & note corresponding I for each step.

(c) Repeat step 2 for different values of V .

(d) Tabulate the results.

LAB MANUAL (III SEM ECS)

Page16

EEMSD LAB (EC-317-F)

OBSERVATION TABLE:

S.No

1.

2.

3.

Transfer charact.(Vds=Cons.)

Id(mA)

Vgs(Volts)

Drain charact. (Vgs= Const.)

Id(mA)

Vds(Volts)

GRAPH:

RESULT: Transfer & Drain characteristics of JFET in common source

configuration have been plotted.

DISCUSSION: We observe that characteristics have 4 regions: Ohmic region,

curve AB, Pinch off region& Breakdown region.

PRECAUTIONS:

1.Always connect the voltmeter in parallel & ammeter in series as shown in fig.

2.Connection should be proper & tight.

3.Switch ON the supply after completing the ckt.

4.DC supply should be increased slowly in steps

5.Reading of voltmeter & Ammeter should be accurate.

QUIZ:

Q.1 Define FET ?

A It is a 3 terminal device in which current conduction is by only one type of

mazority carriers.

Q.2 Define pinch off Voltage ?

A. The value of Vds at which all the free charge carriers are removed from

channel.

Q.3 What is unipolar device ?

A. In which conduction is by only one type of mazority carriers.

Q.4 What is bipolar device ?

A. In which conduction is by both types of carriers.

Q.5 Write advantages of FET over conventional Transistor ?

A. It provides extremely high input impedance as compared to BJT.

LAB MANUAL (III SEM ECS)

Page17

EEMSD LAB (EC-317-F)

Q.6 Define drain Characteristics ?

A. The curve b/w drain current & Vds with Vgs as a parameter.

Q.7 Define transfer Characteristics ?

A. The curve b/w Id & Vgs keeping Vds constt.

Q.8 Write applications of a FET ?

A. FETs are used in ICs, voltage variable resistor in operational amplifier etc.

Q.9 Input impedance of a FET is more than a BJT , Why ?

A Because it always work in reverse biasing situation.

Q.10 Define amplification factor ?

A. Ratio of change in drain-source voltage to change in gate to source voltage at

constt. Id.

.

LAB MANUAL (III SEM ECS)

Page18

EEMSD LAB (EC-317-F)

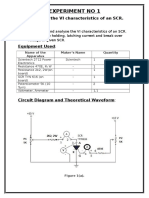

EXPERIMENT NO. 7

AIM: Study characteristics of SCR.

APPRATUS REQUIRED: Power Supply, SCR Kit. , Voltmeter, Ammeter,

Connecting Leads.

BRIEF THEORY: Silicon control rectifier (SCR) is a four layer, three terminal

semiconductor device, the end P forms the anode & the end N forms the cathode &

the gate terminal G is from the P layer next to cathode. It is a unidirectional

device. The device can exist upon either ON state or OFF state depending upon the

applied voltage. When anode voltage is +ve w.r.t to cathode the SCR start

Conducting. If some small gate voltage is applied, the SCR trigger at some low value

of anode voltage, but it loses its all control on the SCR Current after triggering.

Therefore, in order to turn the SCR to OFF position the anode voltage has to be

reduced to zero.

CIRCUIT DIGRAM:

R

mA

mA

R

1

16

1

16

A

V

12V

2

PROCEDURE:

1.

2.

3.

4.

5.

Connect the circuit according to the fig.

First set I = 0mA , vary input voltage V gradually & measure the current I.

Tabulate the readings.

Repeat the procedure for different values of I .

Draw the graph between V & I .

OBSERVATION TABLE:

S.No

Vak(Volts)

LAB MANUAL (III SEM ECS)

Iak (mA)

Page19

EEMSD LAB (EC-317-F)

GRAPH:

PRECAUTIONS:

1.

2.

3.

4.

5.

Always connect the voltmeter in parallel & ammeter in series as shown in fig.

Connection should be proper & tight.

Switch ON the supply after completing the circuit

DC supply should be increased slowly in steps

Reading of voltmeter & Ammeter should be accurate.

RESULT: The characteristics of thyristor have been plotted.

DISCUSSION: The SCR will not conduct until it is not triggered by gate voltage.

QUIZ:

Q.1 Define SCR?

A. It is a controlled rectifier constructed of a silicon material with third terminal

for control purpose.

Q.2 Define Forward Break over Voltage?

A. It is voltage in forward conducting mode after which SCR starts conducting.

Q.3 Define reverse Break down Voltage?

A. If reverse voltage is increased beyond certain value, SCR will break & this

voltage is Called reverse breakdown voltage.

Q.4 Why it is called controlled rectifier?

A. Because its operation as rectifier can be controlled by using gate terminal.

Q.5 Define peak forward Voltage?

A. It is limiting positive anode voltage above which SCR get damaged.

Q.6 Define peak reverse Voltage?

A. Max. reverse voltage that can be applied to SCR without conduction in

reverse direction.

Q.7 Define Holding Current?

A. Min. forward current that must be maintained to keep SCR in conducting state.

Q.8 Define forward current Rating?

A. The max. Value of anode current that SCR con handle safely.

Q. 9 Define latching current.

A. Min. device current which must be attained by the device before gate drive is

removed.

Q.10 What do you mean by commutation process?

A. Process of turning off the SCR

LAB MANUAL (III SEM ECS)

Page20

EEMSD LAB (EC-317-F)

EXPERIMENT NO.8

AIM: Study of characteristics of UJT.

APPARATUS REQUIRED : Power supply, UJT Charact., Connecting Leads,

Ammeter, Voltmeter.

BRIEF THEORY:

UJT: A Uni junction transistor is a three terminal semiconductor device having two

doped regions. In the three terminals, it has one Emitter (E) & two Bases (B1&B2).It

has only one junction. It Consist of an n-type silicon bar which is lightly doped. Two

end connections are taken from the bar called B1 & B2. A heavily doped p-region is

diffused to n-bar nearer to B2.

CIRCUIT DIGRAM:

16

Ckt. For UJT

11

R2

B2

mA

1

16

3

16

2

16

B1

R1

PROCEDURE:

(a) Make the connection as per circuit diagram.

(b) Make sure that the potentiometer is in its minimum position.

(c) Move the potentiometer in clock wise direction & note down the value of V &

I.

(d) Tabulate the value & plot the graph.

OBSERVATION TABLE:

S.No

1.

2.

UJT Charact.

I (mA)

V (Volts)

3.

LAB MANUAL (III SEM ECS)

Page21

EEMSD LAB (EC-317-F)

GRAPH:

UJT Charact.

RESULT: The characteristics of UJT have been plotted.

PRECAUTION:

(1) Always connect the voltmeter in parallel & ammeter in series as shown in fig.

(2)Connection should be proper & tight.

(3)Switch ON the supply after completing the ckt.

(4)DC supply should be increased slowly in steps

(5)Reading of voltmeter & Ammeter should be accurate.

QUIZ:

Q.1 Define UJT?

A. It is a 2 layer, 3- terminal solid state device having only one junction.

Q.2 Write application of UJT?

A. Relaxation oscillator.

Q.3 Define inter base Resistance?

A. The total resistance of silicon bar from one end to other end.

Q.4 Mention different region of UJT?

A. Cut off region, negative resistance region, saturation region.

Q.5 Define peak Point Emitter Current?

A. Min. current that is reqd. to trigger the device.

Q6. Define valley point Current?

A. It is the emitter current at valley point.

LAB MANUAL (III SEM ECS)

Page22

EEMSD LAB (EC-317-F)

EXPERIMENT NO.9

AIM: Study of characteristics of DIAC.

APPARATUS REQUIRED: Power supply, DIAC Characteristic, Connecting

Leads, Ammeter, and Voltmeter.

BRIEF THEORY:

Diac: A Diac is a two terminal & four layer bi-directional semiconductor switching

device.Di means two (two terminal device) and ac means alternating current hence

diac is a switch .In fact, it is a device which can conduct in both the directions. Only

when the applied voltage is more than its break over voltage. It is similar as if two

latches are connected in parallel. During +ve half-Cycle, the right four layer diode

conducts heavily. During ve half-cycle, the left diode conducts heavily only when

the supply voltage exceeds the break over voltage of the Diac.

CIRCUIT DIGRAM:

16

4.7K

A

1

Circuit for DIAC

12V

PROCEDURE:

a) Make connection as per circuit diagram.

b) Apply +ve supply to the circuit.

c) Increase the voltage step by step & note down the corresponding current

values.

d) After a certain voltage, the diac enter in ve resistance region.

e) Now apply reverse polarity & repeat the whole procedure again.

OBSERVATION TABLE:

S.No.

1.

2.

DIAC Characteristics

I (mA)

V (Volts)

3.

4.

LAB MANUAL (III SEM ECS)

Page23

EEMSD LAB (EC-317-F)

GRAPH:

DIAC Characteristic

RESULT: The characteristics of DIAC have been plotted.

PRECAUTION:

1.

2.

3.

4.

5.

Always connect the voltmeter in parallel & ammeter in series as shown in fig.

Connection should be proper & tight.

Switch ON the supply after completing the circuit

DC supply should be increased slowly in steps

Reading of voltmeter & Ammeter should be accurate.

QUIZ:

Q.1 Define DIAC?

A. It is a two electrode bidirectional avalanche diode.

Q.2 Define VBO?

A. The voltage before which DIAC acts as a open switch.

Q.3 Write application of Diac?

A. Heat control circuit..

Q.4 Define inter base Resistance?

A. The total resistance of silicon bar from one end to other end.

Q.5 Define valley Point?

A. Point beyond which if emitter current increases, device enters into saturation

region.

Q.6 Define peak Point Emitter Current?

A.6 Min. current that is required to trigger the device.

LAB MANUAL (III SEM ECS)

Page24

EEMSD LAB (EC-317-F)

Q7. What is a basic difference between thyristor,triac and a diac?

Ans. Thyristor is semiconductor device convert the stable dc to variable dc which has

a three terminals anode, cathode, and gate. The diac is similar to thyristor which is

bidirectional without gate terminal work on both ac & dc. The triac is known as diac

with gate.

Q8. What are the applications of thyristor?

Ans. It used at mine hauler, press machine, HVDC power supply. In future bracking

in automobile, regenerative braking.

Q9.

Identify the symbol:

Ans. SCS (Silicon controlled switch)

Q10. The silicon-controlled switch (SCS) is similar in construction to the

Ans. SCR

LAB MANUAL (III SEM ECS)

Page25

EEMSD LAB (EC-317-F)

EXPERIMENT NO.10

AIM: To plot V-I characteristic of TRIAC.

APPARATUS REQUIRED: Power supply, TRIAC characteristics kit,

Connecting leads, Ammeter & Voltmeter.

THEORY: The TRIAC is a three terminal AC switch that is triggered into

conduction when a low energy signal is applied to its gate terminal. The TRIAC

conducts in either direction when turned on either a positive or negative gate signal

triggers it into conduction. Thus, the TRIAC is a three terminals, four layer

bidirectional semiconductor device that5 controls ac power. Because of its

bidirectional conduction property, the TRIAC is widely used in the field of power

electronics for control purpose.

CIRCUIT DIAGRAM:

PROCEDURE:

(a) Make connection as per the circuit diagram.

(b) Apply +ve supply to the circuit.

LAB MANUAL (III SEM ECS)

Page26

EEMSD LAB (EC-317-F)

(c) Increase the voltage step by step & note down the corresponding current

values.

(d) After a certain voltage, the TRIAC enters into the negative resistance region.

(e) Now apply reserve polarity & repeat the whole procedure again.

OBSERVATION TABLE:

S.NO

Volts

Current

GRAPH:

RESULT: The characteristic of TRIAC have been plotted.

PRECAUTIONS:

(a) Always connect the voltmeter in parallel & ammeter in series.

(b) Connection should be proper & tight.

(c) Switch on the supply after completing the circuit.

(d) DC supply should be increased slowly in steps.

(e) Reading of voltmeter & ammeter should be accurate.

LAB MANUAL (III SEM ECS)

Page27

EEMSD LAB (EC-317-F)

QUIZ/ANSWER:

Q-1 Conduction take place in triac is bidirectional or unidirectional?

Ans: Bidirectional.

Q-2 Expanded form of the word abbreviated TRIAC ?

Ans

Triode and AC.

Q-3

Name three terminal of TRIAc?

Ans Main Terminal 1(MT1) ,Main Terminal 2 (MT2) and Gate G.

Q-4 What are the ratings of TRIAC available in market?

Ans Voltage 1200 and Current 300A(rms).

Q-5 Give application of TRIAC?

Ans TRIACS are extensively used in :A. Residential lamp dimmers.

B. Heat control

C. Speed control of small single phase series and induction motor.

Q-6 Is TRIAc have a capability to work in rectifier mode?

Ans: Yes

Q-7 By what manner TRIAC is different from SCR?

Ans 1. Bidirectional conduction.

2. TRIAC is a combination of two SCRs connected in anti parallel.

Q-8 How many layers are there in TRIAc?

Ans 5 layers.

Q-9 What is the symbol of TRIAC?

Ans

Q-10 how TRIAC is differ from DIAC?

Ans TRIAC have gate terminal and DIAc didnt.

LAB MANUAL (III SEM ECS)

Page28

EEMSD LAB (EC-317-F)

EXPERIMENT NO. 11

AIM: To study photo-resist in metal pattern for planner

technology/PCB technology.

THEORY: The variety of manufacturing process by which IC components are

fabricated take place through a single plane and hence

termed as a planar

technology. The principal constituent of a photo resist solution is a polymer, a

semitizer & a suitable solvent system. Polymers have properties of excellent film

forming & coating. Ploymers generally used are polyvinyl cinnamate, Partially

cyclized isoprene family and other types are phenol formaldehyde etc.

When photo resist is exposed to light, semitizer absorbs energy and initiates chemical

hanges in the resist. The sanitizers are chromophoric organic molecules they enhance

cross linking of the photoresist. Typical sensitizers are carbonyl compounds, benzoin,

benzoyl peroxide, benzoyl, disulphide, nitrogen compounds and halogen compounds.

The solvents are used to keep the polymers in solution are mixture of organic liquids.

They include aliphatic esters such as butyl acetate and cellosolve acetate and

aromatic hydrocarbon like xylene & ethylebenzene, chlorinated hydrocarbons like

chlorobenzene and methylene chloride and ketenes such as cyclopean. The same

solvents are used as thinners & developers.

DIAGRAM:

LAB MANUAL (III SEM ECS)

Page29

EEMSD LAB (EC-317-F)

Photo resists are of two types: negative & positive. Materials which are rendered less

soluble in a developer solution by illumination yield a negative pattern of the mask

and are called negative photo resists.

Photo resist became more soluble when subjected to light and therefore yield a

positive image of the mask. The selection if the photo resist depends upon specific

requirements of resolution and type of surface to be encountered differences in solid

contents and viscosity determine the flow characteristic & thus the thickness of

coating.

Example of negative photo resist is Kodak microney 747 suited to projection printing

and provide high throughput and resolution.

Example of positive photo resist is MP-2400 and HPR-206.

QUIZ/ANSWERS:

Q-1

Ans

Q-2

Ans

What is photo resist?

Resist which changes it behavior when exposed to light is called photo resist.

Name the types of photo resist?

1. Positive photo resist.

2. Negative photo resist.

Q-3 What is positive photo resist?

Ans the resist whose property get changes i.e. become more soluble when exposed

to light called Positive photo resist.

Q-4 What is Negative photo resist?

Ans the resist whose property get changes i.e. become less soluble when exposed

to light called Negative photo resist.

Q-5 Example of negative photo resists?

Ans Kodak Microney 747.

Q-6 Example of positive photo resist?

Ans MP-2400 and HPR-206.

Q-7 Give one application of photo resist?

Ans Sensor

Q-8 What is the principle constituent of photo resist?

Ans Polymer

Q-9 What is sensitizer?

Ans Sensitizer is choromophoric organic molecules.

Q-10 On what technology photo resist fabrication is based?

Ans Planner Technology

LAB MANUAL (III SEM ECS)

Page30

EEMSD LAB (EC-317-F)

EXPERIMENT NO. 12

AIM: To study Zener diode characteristics.

APPARATUS REQUIRED: Regulated DC power supply, Voltmeter,

Connecting Wires, kit

Specifications:

Breakdown Voltage = 5.1V

Power dissipation = 0.75W

Max. Forward Current = 1A

THEORY: An ideal P-N Junction diode does not conduct in reverse biased

condition. A zener diode conducts excellently even in reverse biased condition.

These diodes operate at a precise value of voltage called break down voltage. A zener

diode when forward biased behaves like an ordinary P-N junction diode. A zener

diode when reverse biased can either undergo avalanche break down or zener break

down.

Avalanche break down:-If both p-side and n-side of the diode are lightly doped,

depletion region at the junction widens. Application of a very large electric field at the

junction may rupture covalent bonding between electrons. Such rupture leads to the

generation of a large number of charge carriers resulting in avalanche multiplication.

Zener break down:-If both p-side and n-side of the diode are heavily doped,

depletion region at the junction reduces. Application of even a small voltage at the

junction ruptures covalent bonding and generates large number of charge carriers.

Such sudden increase in the number of charge carriers results in zener mechanism.

CIRCUIT DIAGRAM:

Fig (1) Forward Bias Condition:

LAB MANUAL (III SEM ECS)

Page31

EEMSD LAB (EC-317-F)

PROCEDURE:

Forward biased condition:

1. Connect the circuit as shown in fig (1).

2. Vary Vzf gradually and note down the corresponding readings of Izf.

3.. Step Size is not fixed because of non linear curve and vary the X-axis variable (i.e.

if output variation is more, decrease input step size and vice versa).

4. Tabulate different forward currents obtained for different forward voltages.

Reverse biased condition:

1. Connect the circuit as shown in fig (2).

2. Vary Vzr gradually and note down the corresponding readings of Izr.

7. Step Size is not fixed because of non linear curve and vary the X-axis variable (i.e.

if

output variation is more, decrease input step size and vice versa).

8. Tabulate different reverse currents obtained for different reverse voltages.

OBSERVATIONS:

Zener diode in Forward Zener diode & reverse biased condition should be observed.

LAB MANUAL (III SEM ECS)

Page32

EEMSD LAB (EC-317-F)

CALCULATIONS FROM GRAPH:

Static forward Resistance Rdc = Vf/If

Dynamic forward Resistance rac = Vf/If

Static Reverse Resistance Rdc = Vr/Ir

Dynamic Reverse Resistance rac = Vr/Ir

PRECAUTIONS:

1. While doing the experiment do not exceed the ratings of the diode. This may lead

to damage the diode.

2. Connect voltmeter and Ammeter in correct polarities as shown in the circuit

diagram.

3. Do not switch ON the power supply unless you have checked the circuit

connections as Per the circuit diagram.

RESULT:

1. The zener diode characteristics have been studied.

2. The zener resistance at the breakdown voltage was found to be =

QUIZ:

Q1 Give applications of Zener diode?

A 1: Applications of Zener diode are (a) Voltage regulation (b) Meter protection (c)

Zener diode as a peak clipper (d) Zener diode as a reference element

Q2 what is voltage regulation of Zener diode?

A 2: Voltage regulation is a measure of circuits ability to maintain a constant output

voltage even when either input voltage or load current varies.

Q3 what is Zener current?

A 3: The Zener current in the breakdown region of Zener diode is called Zener

current.

Q4 Give the equation from which series resistance of Zener diode regulator

determined?

A 4: The equation from which series resistance of Zener diode regulator determined is

RS = VS-VOUT / IZMAX Where VS is source voltage, VOUT is output voltage &

IZMAX is maximum current through Zener diode.

LAB MANUAL (III SEM ECS)

Page33

EEMSD LAB (EC-317-F)

Q5 Give advantages of Zener diode regulator over other regulators?

A 5: Advantages of Zener diode regulator over other regulators are that they are

smaller in size, lighter in weight and have longer life.

Q6. What is Zener diode?

A 6: Zener diode, also sometimes called the breakdown diode is a P-N junction diode

specially designed for operation in the breakdown region in reverse bias condition.

Q7 Give several methods used to manufacture of Zener diodes?

A 7: several methods used to manufacture of Zener diodes are diffused structure,

diffused and passivated structure and alloy diffused structure.

Q8 In passivated structure of a Zener diode by which layer edges of the junction are

covered?

A 8: In passivated structure of a Zener diode; Silicon Dioxide layer edges of the

junction are covered.

Q9 Give the voltage range availability of Zener diodes?

A 9: The voltage range availability of Zener diodes is 2.4v to 200v.

Q10. What is Zener voltage?

A 10: The voltage at which the Zener diode breaks down is called the Zener voltage.

LAB MANUAL (III SEM ECS)

Page34

EEMSD LAB (EC-317-F)

EXPERIMENT NO. 13

AIM: To study zener diode as voltage regulator.

APPRATUS REQUIRED: Power Supply, Zener Diode, Two Voltmeter and

connected leads Ammeter.

BRIEF THEORY:- The Zener diode is operated in the breakdown or zener

region, the voltage across it is substantially constant for a large current of current

through it. This characteristic permits it to be used as a voltage regulator. As the lode

Current increases, the Zener current decrease so that current through resistance Rs is

constant. As out put voltage = Vin Irs, and I is constant, Therefore, output Voltage

remains unchanged. The input voltage Vin increase, more current will flow through

the zener, the voltage drop across Rs will increase but lode voltage would remain

constant.

CIRCUIT DIAGRAM:

mA

1

16

1

0-15V

V

RL

16

Vs

PROCEDURE:

(a)Connect the circuit as per the circuit diagram

(b)Keep load resistance constant (take maximum value of load resistance)

(c)Vary input voltage and note down output voltage

(d)Now keep input voltage constant and vary load resistance and note down

corresponding voltmeter reading

(e)Plot the respective graph

OBSERVATION TABLE:

S. No

1

2

3

4

5

6

7

Vs( VOLT)

LAB MANUAL (III SEM ECS)

V( VOLT)

RL(E)

(VOLT)

Page35

EEMSD LAB (EC-317-F)

8

9

PRECAUTIONS:

(a)Connections should be tight

(b)Handle the equipments with care

RESULT: Studied how Zener diode is used as a voltage regulator.

QUIZ:

QNo

1

3

4

9

10

QUESTION

ANSWERS

Give applications of Zener Applications of Zener diode are

diode?

(a) Voltage regulation

(b) Meter

protection

(c) Zener diode as a peak

clipper (d) Zener diode as a reference

element

What is voltage regulation of Voltage regulation is a measure of

Zener diode?

circuits ability to maintain a constant

output voltage even when either input

voltage or load current varies.

What is Zener current?

The Zener current in the breakdown region

of Zener diode is called Zener current.

Give the equation from which The equation from which series resistance

series resistance of Zener diode of Zener diode regulator determined is

regulator determined?

RS = VS-VOUT / IZMAX

WhereVS is source voltage, VOUT is output voltage &

IZMAX is maximum current through Zener diode.

Give advantages of Zener diode Advantages of Zener diode regulator over

regulator over other regulators? other regulators are that they are smaller in

size, lighter in weight and have longer

life.

What is Zener diode?

Zener diode, also sometimes called the

breakdown diode ia a P-N junction diode

specially designed for operation in the

breakdown region in reverse bias

condition.

Give several methods used to several methods used to manufacture of

manufacture of Zener diodes?

Zener diodes are diffused structure,

diffused and passivated structure and alloy

diffused structure.

In passivated structure of a In passivated structure of a Zener diode;

Zener diode by which layer Silicon Dioxide layer edges of the junction

edges of the junction are are covered.

covered?

Give

the

voltage

range The voltage range availability of Zener

availability of Zener diodes?

diodes is 2.4v to 200v.

What is Zener voltage?

The voltage at which the Zener diode

LAB MANUAL (III SEM ECS)

Page36

EEMSD LAB (EC-317-F)

breaks down is called the Zener voltage.

EXPERIMENT NO.14

AIM: To study and draw the characteristics of FET in common drain

configuration.

APPRATUS REQUIRED: Power supply, FET charact. Kit,connecting leads,

two Multimeters.

BRIEF THEORY: A FET is a three terminal semiconductor device in which

current conduction is by one type of carries & is controlled by the effect of electric

field. There are two types of FET namely JFET & MOSFET. Again, a JFET can

either have N-channel or P-channel. A N-channel JFET has a N-type semiconductor

bar, the two ends of which make the Drain & source terminal. On the two sides of this

bar, P-N junction is made. This P region makes gate. Usually, these two gates are

connected Together to form a single gate .The gate is given a ve bias w.r.t source.

The Drain is given +ve potential w.r.t source. Drain is Common in input and output.

CIRCUIT DIAGRAM:

mA

2

3 G

VDS

VGD

PROCEDURE:

(a)Connect the circuit as per the circuit diagram

Input characteristics

(b)Keep drain-source voltage constant

(c)Vary gate-drain voltage in steps and note down drain current

(d) Readings are tabulated and graph is drawn

Output characteristics

(a)Keep gate-drain voltage constant

(b)Vary drain-source voltage in steps and note down drain current.

(c) Readings are tabulated and graph is drawn

LAB MANUAL (III SEM ECS)

Page37

EEMSD LAB (EC-317-F)

GRAPH:

OBSERVATION TABLE:

S. No

1

2

3

4

5

6

7

8

9

10

I/P at const. VDS

VGD (V)

ID (mA)

O/P at const. VGD

VDS (V)

ID (mA)

PRECAUTIONS:

(a)Connections should be tight

(b)Handle the equipments with care

RESULT: Input and output characteristics is obtained.

QUIZ:

Q. No QUESTION

LAB MANUAL (III SEM ECS)

ANSWERS

Page38

EEMSD LAB (EC-317-F)

4

5

6

7.

8.

9.

Which is the common log in Drain leg is common between input and

common drain FET amplifier output.

Between input and output.

Define Pinch off voltage.

The value of drainsource voltage at which

channel is pinched off (i.e. all the free

charges from the channel are removed)is

called pinchoff voltage

Write advantages of FET over Advantages are (a) Thermal stability. (b)

conventional Transistor.

Immunity to radiation. (c) High input

impedance.

How much is the gain of Gain of common drain amplifier is less than

common drain FET amplifier?

unity.

Define Drain resistance.

Drain resistance can be defined as ratio of

drain to source voltage to drain current.

Define Transconductance.

Transconductance can be defined as ratio of

drain current to gate to source voltage

A common-gate amplifier is Common base

similar in configuration to which

BJT amplifier?

A common-drain amplifier is Common Collector

similar in configuration to which

BJT amplifier?

What is (are) the function(s) of

A to create an open circuit for dc

the coupling capacitors C1 and

analysis

.

C2 in an FET circuit?

B

.

C

.

10.

to isolate the dc biasing

arrangement from the applied

signal and load

to create a short-circuit

equivalent for ac analysis

What is the input resistance 1 / gm

(Rin(source)) of a common-gate

amplifier?

LAB MANUAL (III SEM ECS)

Page39

EEMSD LAB (EC-317-F)

EXPERIMENT NO. 15

AIM: To study VMOS Technology.

THEORY: Power MOSFET are usually constructed in V-configuration that is why

the device is called V-MOSFET. V-shaped cut penetrates from the device surface

almost to the N+ substrate through N+, P and N- layers. The N+ layers are heavily

doped, low resistive material, while the N- layer is a lightly doped high resistance

region. The SiO2 dielectric layer covers both the horizontal surface and V-cut surface.

V-MOSFET is an E-Mode FET and no channel exists between drain & source until

the gate is made positive w.r.t the source. On making gate positive w.r.t the source, an

N-type channel is formed close to the gate, as in case of E-MOSFET.

DIAGRAM:-

In this case, N- type channel provides a vertical path for the charge carriers to flow

between the N+ substrate (i.e drain) and the N+ source termination. When Vgs is zero

or negative, no channel exists and the drain current is zero.With the increase in gate

voltage, the channel resistance is reduced and therefore the drain current Id increases.

Thus the drain current Id can be controlled bu gate voltage control. So that for a given

level of Vgs, Id remains constant over wide range of Vds levels.In V-MOSFET the

channel length is determined by the diffusion process, while in other MOSFETs the

LAB MANUAL (III SEM ECS)

Page40

EEMSD LAB (EC-317-F)

channel length depends upon the dimensions of the photographic masks employed in

the diffusion process. By controlling the doping density and the diffusion time much

shorter channels can be produced than are possible with mask control of channel

length. These shorter channels allow much more current densities which again

contribute to layer power dissipations. The shorter channel length allows a layer Tran

conductance gm to be attained in V-FET & improves frequency response.

QUIZ :

1. What is the power consumption of VMOS.

Ans: VMOS shows a very low power consumption as compared to other MOS.

2. What are the main advantages of VMOS.

Ans: Greater speed and greater packing density.

3. Which method is used in the fabrication of VMOS.

Ans: photolithography

4. VMOS can handle large .. current as compared to other MOS.

Ans: large

5. What is value of ON resistance in VMOS.

Ans About 3 ohm.

6. What is the application of VMOS.

Ans: Wideband amplifier.

7. Why VMOS is used for wideband amplifier.

Ans: It provides constant gain up to 10 MHz

8. Which layer decides the gate length in n-channel VMOS.

Ans: Thickness of p region

9. For n-channel VMOS which type of substrate is used.

Ans: heavily doped n+silicon wafer

10. Which layer is the outermost layer in VMOS.

Ans: silicon dioxide layer.

LAB MANUAL (III SEM ECS)

Page41

You might also like

- Rotating Electrical Machines - : Part 17: Cage Induction Motors When Fed From Converters - Application GuideDocument22 pagesRotating Electrical Machines - : Part 17: Cage Induction Motors When Fed From Converters - Application GuideAhmad RostomNo ratings yet

- Electromagnetic Compatibility (EMC) Design and Test Case AnalysisFrom EverandElectromagnetic Compatibility (EMC) Design and Test Case AnalysisNo ratings yet

- Hound of The BaskervillesDocument117 pagesHound of The BaskervillescipileNo ratings yet

- RectifierDocument18 pagesRectifierTussank Gupta71% (7)

- Analog Circuits LAB Manual - Adder, Subtractor, Integrator & DifferentiatorDocument13 pagesAnalog Circuits LAB Manual - Adder, Subtractor, Integrator & Differentiatorchaitanya100% (4)

- 5 Volt DC Power Supply Circuit DesignDocument6 pages5 Volt DC Power Supply Circuit DesignTarik Imran100% (2)

- Electrical Machines Lab ManualDocument67 pagesElectrical Machines Lab Manualkrishnandrk100% (2)

- Frequency Response of A Single Stage RC Coupled AmplifierDocument26 pagesFrequency Response of A Single Stage RC Coupled AmplifierkanchankonwarNo ratings yet

- DC Drives PDFDocument90 pagesDC Drives PDFkeerthi50% (2)

- Devices Experiment 1 - Inverting and Non-InvertingDocument16 pagesDevices Experiment 1 - Inverting and Non-InvertingYanique GibbsNo ratings yet

- VRLA SpecDocument41 pagesVRLA SpecsdvijayNo ratings yet

- EDC-I Easy Solution SEM3-1 PDFDocument112 pagesEDC-I Easy Solution SEM3-1 PDFSumedh SatamNo ratings yet

- 1.O.C. & S.C. Tests On Single Phase TransformerDocument6 pages1.O.C. & S.C. Tests On Single Phase Transformerchandrakanth100% (3)

- 220-12 Volt DC Power SupplyDocument16 pages220-12 Volt DC Power Supplychachunasayan89% (18)

- Load Test On Series GeneratorDocument3 pagesLoad Test On Series Generatorkudupudinagesh88% (8)

- Lab 4 - Differentiator & IntegratorDocument14 pagesLab 4 - Differentiator & IntegratorVickneswaran KalerwananNo ratings yet

- Half Wave and Full Wave RectifierDocument6 pagesHalf Wave and Full Wave RectifierBilal KhanNo ratings yet

- Expt 1 Voltage Series Feedback ApmlifierDocument5 pagesExpt 1 Voltage Series Feedback Apmlifiersamarth100% (3)

- Project Report On IC 555 Timer CircuitDocument21 pagesProject Report On IC 555 Timer CircuitAniket Chaudhari44% (25)

- IC 741 Comparator ExperimentDocument2 pagesIC 741 Comparator ExperimentJaideep Singh100% (2)

- Analog Circuits Lab Possible Viva QuestionsDocument18 pagesAnalog Circuits Lab Possible Viva Questionsarsp_0610198571% (14)

- Comparative Study of MOSFET and IGBT For High Repetitive Pulsed Power ModulatorsDocument8 pagesComparative Study of MOSFET and IGBT For High Repetitive Pulsed Power ModulatorsTainá tainlerschyahoo.com.brNo ratings yet

- Expt 10 - Monostable-MultivibratorDocument5 pagesExpt 10 - Monostable-Multivibratorsamarth0% (1)

- Proteus Lab Manual PDFDocument91 pagesProteus Lab Manual PDFAnie Said100% (1)

- Edc Lab ManualDocument70 pagesEdc Lab ManualreneeshczNo ratings yet

- Diode Clippers and Clampers Limit SignalsDocument7 pagesDiode Clippers and Clampers Limit SignalsIlham Santoso100% (1)

- Solved Examples For The Course Power ElectronicsDocument16 pagesSolved Examples For The Course Power ElectronicsSolomon Tadesse Athlaw100% (2)

- Expt - 2 - Verification of Theveninen's Theorem For Ac CircuitsDocument3 pagesExpt - 2 - Verification of Theveninen's Theorem For Ac CircuitsChaitanya Vivek Deshpande100% (1)

- Clap Switch Report EditedDocument47 pagesClap Switch Report EditedKeshav Krishna60% (5)

- Half Wave and Full Wave RectifierDocument8 pagesHalf Wave and Full Wave RectifierArun Jyothi82% (11)

- How to convert a Galvanometer into a VoltmeterDocument5 pagesHow to convert a Galvanometer into a VoltmeterAbdur Rehman100% (1)

- Half and Full Wave RectifierDocument12 pagesHalf and Full Wave Rectifierlucy lucy50% (2)

- Frequency Response of CE AmplifierDocument4 pagesFrequency Response of CE AmplifierShees Nadeem100% (2)

- 5.) Common Drain AmplifierDocument5 pages5.) Common Drain AmplifierJuay Mae Riano100% (1)

- Expt 10 Bistable MultivibratorDocument4 pagesExpt 10 Bistable MultivibratorsamarthNo ratings yet

- (CC) Transistor Characteristics in Common Collector ConfigurationDocument6 pages(CC) Transistor Characteristics in Common Collector ConfigurationjassiscNo ratings yet

- AbcdDocument5 pagesAbcdkumarchaturvedulaNo ratings yet

- Viva Questions Operation AmplifierDocument3 pagesViva Questions Operation AmplifierMalik HammadNo ratings yet

- LAB 3: Inverting and Non-Inverting Amplifier: ObjectivesDocument4 pagesLAB 3: Inverting and Non-Inverting Amplifier: ObjectivesKidist kefelegn100% (1)

- Transformer Turns Ratio TestDocument2 pagesTransformer Turns Ratio TestRaviNo ratings yet

- Experiment No 3a MOSFET CharacteristicsDocument5 pagesExperiment No 3a MOSFET CharacteristicsManikandan P Engineering EEENo ratings yet

- EEP851 POWER ELECTRONICS LAB- SCR, IGBT & MOSFET CHARACTERISTICSDocument16 pagesEEP851 POWER ELECTRONICS LAB- SCR, IGBT & MOSFET CHARACTERISTICSGaurav Verma100% (2)

- Turn ON and Off Characteristics of SCRDocument17 pagesTurn ON and Off Characteristics of SCRVedant .Chavan100% (2)

- 2.sumpner's Test On A Pair of Single Phase TransformersDocument5 pages2.sumpner's Test On A Pair of Single Phase Transformerschandrakanth100% (2)

- Plot Characteristics of FETDocument4 pagesPlot Characteristics of FETTapobroto Chatterjee100% (1)

- Swinburne'S Test: AIM: To Pre-Determine The Efficiency of A D.C Shunt Machine by PerformingDocument6 pagesSwinburne'S Test: AIM: To Pre-Determine The Efficiency of A D.C Shunt Machine by PerformingAshutosh SharmaNo ratings yet

- Lab ManualDocument7 pagesLab ManualMm MNo ratings yet

- Single Phase Series InverterDocument9 pagesSingle Phase Series InverterDhivya NNo ratings yet

- BEEE Important Questions 16 MarksDocument5 pagesBEEE Important Questions 16 Marksaeroheroz25% (4)

- Field TestDocument5 pagesField Testkudupudinagesh100% (3)

- RC Phase Shift OscillatorDocument4 pagesRC Phase Shift OscillatorReddyvari Venugopal67% (3)

- Unit 3 ComparatorsDocument54 pagesUnit 3 ComparatorsSoundararajan RajagopalanNo ratings yet

- Experiment No 2 (Fet)Document4 pagesExperiment No 2 (Fet)Jaideep SinghNo ratings yet

- Viva Question With AnswersDocument14 pagesViva Question With AnswersAsim AhmedNo ratings yet

- Experiment No: 4-Characteristics of BJT in CE Configuration AimDocument6 pagesExperiment No: 4-Characteristics of BJT in CE Configuration AimGANESH KUMAR B eee2018100% (2)

- Experiment No.2: Objective: Study of Characteristics of Silicon DiodeDocument5 pagesExperiment No.2: Objective: Study of Characteristics of Silicon DiodeUday BhartiyaNo ratings yet

- EC3361 EDC Lab ManualDocument74 pagesEC3361 EDC Lab Manualbhuvanesh14072005No ratings yet

- Construction and Working of A JFETDocument6 pagesConstruction and Working of A JFETSatish Mali100% (1)

- EC - Unit 5 - Sinusoidal and Non Sinusoidal OscillatorsDocument13 pagesEC - Unit 5 - Sinusoidal and Non Sinusoidal Oscillatorsnanobala15100% (2)

- Expt - 7 :transistorized Astable MultivibratorDocument4 pagesExpt - 7 :transistorized Astable Multivibratorsamarth100% (1)

- Electrical Machine-1 Manual PDFDocument40 pagesElectrical Machine-1 Manual PDFsoumencha80% (5)

- Experiment PE LABDocument5 pagesExperiment PE LABsureshfm1100% (1)

- Vi Characteristics of PN Junction DiodeDocument17 pagesVi Characteristics of PN Junction DiodePranay PathadeNo ratings yet

- Lab Manual: Electrical Engineering Materials & Semiconductor Devices Lab (EC-317-F)Document41 pagesLab Manual: Electrical Engineering Materials & Semiconductor Devices Lab (EC-317-F)Ilavarasan TamizhNo ratings yet

- EC 252 EDC Lab Manual PDFDocument63 pagesEC 252 EDC Lab Manual PDFMurali KrishnaNo ratings yet

- Baggage Rules PDFDocument5 pagesBaggage Rules PDFtripschoolNo ratings yet

- Anna University, Chennai University Departments Regulations - 2015 Choice Based Credit System M.E.Power Engineering and ManagementDocument63 pagesAnna University, Chennai University Departments Regulations - 2015 Choice Based Credit System M.E.Power Engineering and ManagementSyaoran7LiNo ratings yet

- Data STV148 140618 PDFDocument1 pageData STV148 140618 PDFSyaoran7LiNo ratings yet

- Computer CommunicationDocument2 pagesComputer CommunicationSyaoran7LiNo ratings yet

- 10th Science Onemark With Answer PDFDocument24 pages10th Science Onemark With Answer PDFSyaoran7LiNo ratings yet

- Operations Strategy PaperDocument24 pagesOperations Strategy PaperscribddmiNo ratings yet

- Lab Manual 15eclo2lDocument65 pagesLab Manual 15eclo2lSyaoran7LiNo ratings yet

- 10th Science Onemark With Answer TM PDFDocument24 pages10th Science Onemark With Answer TM PDFSyaoran7LiNo ratings yet

- Errata For Other SubjectsDocument1 pageErrata For Other SubjectsSyaoran7LiNo ratings yet

- Unit 4 and 5Document37 pagesUnit 4 and 5Syaoran7LiNo ratings yet

- Skills Worksheet1 PDFDocument8 pagesSkills Worksheet1 PDFSyaoran7LiNo ratings yet

- Lab Manual 15eclo2lDocument65 pagesLab Manual 15eclo2lSyaoran7LiNo ratings yet

- Maths Notes1Document9 pagesMaths Notes1Syaoran7LiNo ratings yet

- Internship Report1Document14 pagesInternship Report1Syaoran7LiNo ratings yet

- Guide to Short DocumentsDocument1 pageGuide to Short DocumentsSyaoran7LiNo ratings yet

- Environmental Science and Engineering B.E./B.Tech. DEGREE EXAMINATION, NOVEMBER/DECEMBER 2008.Document2 pagesEnvironmental Science and Engineering B.E./B.Tech. DEGREE EXAMINATION, NOVEMBER/DECEMBER 2008.vinothkumar42No ratings yet

- AbstractDocument18 pagesAbstractSyaoran7LiNo ratings yet

- AbstractDocument36 pagesAbstractSyaoran7LiNo ratings yet

- Matric HistoryCivics March2010Document8 pagesMatric HistoryCivics March2010Syaoran7LiNo ratings yet

- CS 1151 Data StructuresDocument19 pagesCS 1151 Data Structuresanon-845033100% (2)

- Anna University Master of Business Administration (Mba) Curriculum - 2005 - Full-Time Mode Semester - IDocument59 pagesAnna University Master of Business Administration (Mba) Curriculum - 2005 - Full-Time Mode Semester - IcmramarNo ratings yet

- GFDSTGFRDDocument23 pagesGFDSTGFRDSyaoran7LiNo ratings yet

- GFDSTGFRDDocument23 pagesGFDSTGFRDSyaoran7LiNo ratings yet

- Japanese Holidays and FunctionsDocument2 pagesJapanese Holidays and FunctionsSyaoran7LiNo ratings yet

- Bench MarkingDocument21 pagesBench MarkingSyaoran7LiNo ratings yet

- Maintenance Policy ProcessDocument13 pagesMaintenance Policy ProcessTor BlackNo ratings yet

- The Black CatDocument6 pagesThe Black CatSyaoran7LiNo ratings yet

- Indian Print Media Is at A Massive Business in The Media World and Its Newspapers Are Said To Offer Majority of National and International NewsDocument22 pagesIndian Print Media Is at A Massive Business in The Media World and Its Newspapers Are Said To Offer Majority of National and International NewsSyaoran7LiNo ratings yet

- V-I Characteristics of SCRDocument6 pagesV-I Characteristics of SCRRohitRaj100% (1)

- Designing of Two Terminal VSC Based HVDC Transmission SystemDocument15 pagesDesigning of Two Terminal VSC Based HVDC Transmission SystemShoaib KhizerNo ratings yet

- 1327 enDocument80 pages1327 enLuis FelipeNo ratings yet

- Yaskawa Servopack RepairDocument17 pagesYaskawa Servopack RepairVikash KumarNo ratings yet

- Thapar University, Patiala: Di DT Di DTDocument5 pagesThapar University, Patiala: Di DT Di DTNishant SaxenaNo ratings yet

- Company Technology: A Selling and Not A ProductDocument25 pagesCompany Technology: A Selling and Not A ProductrajkumaresanNo ratings yet

- Introduction to Silicon Controlled Rectifiers (SCRsDocument19 pagesIntroduction to Silicon Controlled Rectifiers (SCRsAlbin RobinNo ratings yet

- 09 Cycloconverter - Protection Functions PDFDocument14 pages09 Cycloconverter - Protection Functions PDFIrving Dirzo CarrilloNo ratings yet

- L2. Single Phase Ac Voltage ControllersDocument104 pagesL2. Single Phase Ac Voltage ControllersShivaram Vadla100% (2)

- Custom Power DevicesDocument16 pagesCustom Power Devicessubhadip sadhukhanNo ratings yet

- Electronic Components and DevicesDocument6 pagesElectronic Components and DevicesSelvam MNo ratings yet

- QB NewDocument13 pagesQB NewNarasimman DonNo ratings yet

- 11e601 - Unit 2Document8 pages11e601 - Unit 2nandhakumarmeNo ratings yet

- r05310206 Power ElectronicsDocument5 pagesr05310206 Power ElectronicsSRINIVASA RAO GANTANo ratings yet

- PedgkDocument32 pagesPedgkGokulakrishnanNo ratings yet

- Acs 2000Document65 pagesAcs 2000MAHESWARA RAO CHALLANo ratings yet

- Selector GuideDocument276 pagesSelector GuideEric GarciaNo ratings yet

- Power Switching DevicesDocument30 pagesPower Switching DevicesIlal TanzilalNo ratings yet

- Questionnaire On Medium Voltage Soft Starters For Induction and Synchronous MotorsDocument2 pagesQuestionnaire On Medium Voltage Soft Starters For Induction and Synchronous Motorsabdulyunus_amirNo ratings yet

- Seminar ReportDocument31 pagesSeminar ReportPriyanshu KumarNo ratings yet

- Tips For IesDocument3 pagesTips For Iesasheokand172No ratings yet

- Silicon Controlled RectifierDocument13 pagesSilicon Controlled RectifierdhanshreeNo ratings yet

- Asset Management Strategies For Power Electronic Converters in Transmission Networks: Application To HVDC and FACTS DevicesDocument19 pagesAsset Management Strategies For Power Electronic Converters in Transmission Networks: Application To HVDC and FACTS DevicesRene Alfonso Rodriguez PalaciosNo ratings yet

- Study V-I Characteristics of an SCRDocument9 pagesStudy V-I Characteristics of an SCRBals BalaNo ratings yet

- CT208 (Anglais)Document30 pagesCT208 (Anglais)fgfNo ratings yet