Professional Documents

Culture Documents

Data Sheet

Uploaded by

ΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Data Sheet

Uploaded by

ΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣCopyright:

Available Formats

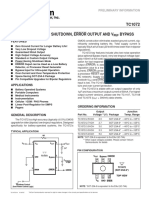

Preliminary

Revised August 2001

74LCX32373

Low Voltage 32-Bit Transparent Latch

with 5V Tolerant Inputs and Outputs (Preliminary)

General Description

Features

The LCX32373 contains thirty-two non-inverting latches

with 3-STATE outputs and is intended for bus oriented

applications. The device is byte controlled. The flip-flops

appear transparent to the data when the Latch Enable (LE)

is HIGH. When LE is LOW, the data that meets the setup

time is latched. Data appears on the bus when the Output

Enable (OE) is LOW. When OE is HIGH, the outputs are in

a high impedance state.

5V tolerant inputs and outputs

The LCX32373 is designed for low voltage (2.5V or 3.3V)

VCC applications with capability of interfacing to a 5V signal

environment.

The LCX32373 is fabricated with an advanced CMOS technology to achieve high speed operation while maintaining

CMOS low power dissipation.

2.3V3.6V VCC specifications provided

5.4 ns tPD max (VCC = 3.3V), 20 A ICC max

Power down high impedance inputs and outputs

Supports live insertion/withdrawal (Note 1)

24 mA output drive (VCC = 3.0V)

Uses patented noise/EMI reduction circuitry

Latch-up performance exceeds 500 mA

ESD performance:

Human body model > 2000V

Machine model > 200V

Packaged in plastic Fine-Pitch Ball Grid Array (FBGA)

(Preliminary)

Note 1: To ensure the high-impedance state during power up or down, OE

should be tied to VCC through a pull-up resistor: the minimum value or the

resistor is determined by the current-sourcing capability of the driver.

Ordering Code:

Order Number

74LCX32373GX

(Note 2)

Package Number

BGA96A

(Preliminary)

Package Description

96-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm Wide

[TAPE and REEL]

Note 2: BGA package available in Tape and Reel only.

Logic Symbol

2001 Fairchild Semiconductor Corporation

DS500547

www.fairchildsemi.com

74LCX32373 Low Voltage 32-Bit Transparent Latch with 5V Tolerant Inputs and Outputs (Preliminary)

January 2001

74LCX32373

Preliminary

Connection Diagram

Pin Descriptions

Pin Names

Description

OEn

Output Enable Input (Active LOW)

LEn

Latch Enable Input

I0 - I31

Inputs

O0 - O31

Outputs

FBGA Pin Assignments

(Top Thru View)

O1

O0

OE1

LE1

I0

I1

O3

O2

GND

GND

I2

I3

O5

O4

VCC

VCC

I4

I5

O7

O6

GND

GND

I6

I7

O9

O8

GND

GND

I8

I9

O11

O10

VCC

VCC

I10

I11

O13

O12

GND

GND

I12

I13

O14

O15

OE2

LE2

I15

I14

O17

O16

OE3

LE3

I16

I17

O19

O18

GND

GND

I18

I19

O21

O20

VCC

VCC

I20

I21

O23

O22

GND

GND

I22

I23

O25

O24

GND

GND

I24

I25

O27

O26

VCC

VCC

I26

I27

O29

O28

GND

GND

I28

I29

O30

O31

OE4

LE4

I31

I30

Truth Table

Inputs

Outputs

LEn

OEn

In

On

O0

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Z = High Impedance

O0 = Previous O0 before HIGH-to-LOW transition of Latch Enable

Functional Description

The LCX32373 contains thirty-two D-type latches with

3-STATE standard outputs. The device is byte controlled

with each byte functioning identically, but independent of

the other. Control pins can be shorted together to obtain full

32-bit operation. The following description applies to each

byte. When the Latch Enable (LEn) input is HIGH, data on

the In enters the latches. In this condition the latches are

transparent, i.e. a latch output will change state each time

www.fairchildsemi.com

its I input changes. When LEn is LOW, the latches store

information that was present on the I inputs a setup time

preceding the HIGH-to-LOW transition of LEn. The

3-STATE standard outputs are controlled by the Output

Enable (OEn) input. When OEn is LOW, the standard outputs are in the 2-state mode. When OEn is HIGH, the standard outputs are in the high impedance mode but this does

not interfere with entering new data into the latches.

Preliminary

74LCX32373

Logic Diagrams

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

www.fairchildsemi.com

74LCX32373

Preliminary

Absolute Maximum Ratings(Note 3)

Symbol

Parameter

Value

VCC

Supply Voltage

0.5 to +7.0

VI

DC Input Voltage

0.5 to +7.0

VO

DC Output Voltage

0.5 to +7.0

Conditions

Units

V

V

Output in 3-STATE

0.5 to VCC + 0.5

Output in HIGH or LOW State (Note 4)

IIK

DC Input Diode Current

50

VI < GND

IOK

DC Output Diode Current

50

VO < GND

+50

VO > VCC

V

mA

mA

IO

DC Output Source/Sink Current

50

mA

ICC

DC Supply Current per Supply Pin

100

mA

IGND

DC Ground Current per Ground Pin

100

mA

TSTG

Storage Temperature

65 to +150

Recommended Operating Conditions (Note 5)

Symbol

VCC

Parameter

Supply Voltage

VI

Input Voltage

VO

Output Voltage

IOH/IOL

Output Current

TA

Free-Air Operating Temperature

t/V

Input Edge Rate, VIN = 0.8V2.0V, VCC = 3.0V

Min

Max

Operating

2.0

3.6

Data Retention

1.5

3.6

5.5

HIGH or LOW State

VCC

3-STATE

5.5

VCC = 3.0V 3.6V

24

VCC = 2.7V 3.0V

12

VCC = 2.3V 2.7V

Units

V

V

V

mA

40

85

10

ns/V

Note 3: The Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated

at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the Absolute Maximum Ratings. The Recommended Operating Conditions table will define the conditions for actual device operation.

Note 4: IO Absolute Maximum Rating must be observed.

Note 5: Unused inputs must be held HIGH or LOW. They may not float.

DC Electrical Characteristics

Symbol

VIH

VIL

VOH

VOL

Parameter

Conditions

HIGH Level Input Voltage

LOW Level Input Voltage

HIGH Level Output Voltage

LOW Level Output Voltage

IOH = 100 A

VCC

TA = 40C to +85C

(V)

Min

2.3 2.7

1.7

2.7 3.6

2.0

Max

Units

V

2.3 2.7

0.7

2.7 3.6

0.8

2.3 3.6

VCC 0.2

IOH = 8 mA

2.3

1.8

IOH = 12 mA

2.7

2.2

IOH = 18 mA

3.0

2.4

IOH = 24 mA

3.0

2.2

IOL = 100 A

2.3 3.6

0.2

IOL = 8 mA

2.3

0.6

IOL = 12 mA

2.7

0.4

IOL = 16 mA

3.0

0.4

IOL = 24 mA

3.0

0.55

II

Input Leakage Current

0 VI 5.5V

2.3 3.6

5.0

IOZ

3-STATE Output Leakage

0 VO 5.5V

2.3 3.6

5.0

10

VI = VIH or VIL

IOFF

Power-Off Leakage Current

www.fairchildsemi.com

VI or VO = 5.5V

Preliminary

Symbol

(Continued)

Parameter

VCC

Conditions

(V)

ICC

ICC

Quiescent Supply Current

Increase in ICC per Input

TA = 40C to +85C

Min

Units

Max

VI = V CC or GND

2.3 3.6

20

3.6V VI, VO 5.5V (Note 6)

2.3 3.6

20

VIH = VCC 0.6V

2.3 3.6

500

A

A

Note 6: Outputs disabled or 3-STATE only.

AC Electrical Characteristics

TA = 40C to +85C, RL = 500

Symbol

Parameter

VCC = 3.3V 0.3V

VCC = 2.7V

VCC = 2.5V 0.2V

CL = 50 pF

CL = 50 pF

CL = 30 pF

Min

Max

Min

Max

Min

tPHL

Propagation Delay

1.5

5.4

1.5

5.9

1.5

6.5

tPLH

In to On

1.5

5.4

1.5

5.9

1.5

6.5

tPHL

Propagation Delay

1.5

5.5

1.5

6.4

1.5

6.6

tPLH

LE to On

1.5

5.5

1.5

6.4

1.5

6.6

tPZL

Output Enable Time

1.5

6.1

1.5

6.5

1.5

7.9

1.5

6.1

1.5

6.5

1.5

7.9

1.5

6.0

1.5

6.3

1.5

7.2

1.5

6.0

1.5

6.3

1.5

7.2

tPZH

tPLZ

Output Disable Time

tPHZ

Units

Max

ns

ns

ns

ns

tS

Setup Time, In to LE

2.5

2.5

3.0

ns

tH

Hold Time, In to LE

1.5

1.5

2.0

ns

tW

LE Pulse Width

3.0

3.0

3.5

ns

Dynamic Switching Characteristics

Symbol

VOLP

VOLV

VCC

TA = 25C

(V)

Typical

CL = 50 pF, VIH = 3.3V, VIL = 0V

3.3

0.8

CL = 30 pF, VIH = 2.5V, VIL = 0V

2.5

0.6

CL = 50 pF, VIH = 3.3V, VIL = 0V

3.3

0.8

CL = 30 pF, VIH = 2.5V, VIL = 0V

2.5

0.6

Parameter

Quiet Output Dynamic Peak VOL

Quiet Output Dynamic Valley VOL

Conditions

Units

V

V

Capacitance

Typical

Units

CIN

Symbol

Input Capacitance

Parameter

VCC = Open, VI = 0V or VCC

Conditions

pF

COUT

Output Capacitance

VCC = 3.3V, VI = 0V or VCC

pF

CPD

Power Dissipation Capacitance

VCC = 3.3V, VI = 0V or VCC, f = 10 MHz

20

pF

www.fairchildsemi.com

74LCX32373

DC Electrical Characteristics

74LCX32373

Preliminary

AC LOADING and WAVEFORMS Generic for LCX Family

FIGURE 1. AC Test Circuit (CL includes probe and jig capacitance)

Test

Switch

tPLH, tPHL

Open

tPZL, tPLZ

6V at VCC = 3.3 0.3V, and 2.7V

VCC x 2 at VCC = 2.5 0.2V

tPZH, tPHZ

GND

Waveform for Inverting and Non-Inverting Functions

3-STATE Output High Enable and

Disable Times for Logic

Propagation Delay. Pulse Width and trec Waveforms

Setup Time, Hold Time and Recovery Time for Logic

trise and tfall

3-STATE Output Low Enable and

Disable Times for Logic

FIGURE 2. Waveforms

(Input Characteristics; f = 1MHz, tr = tf = 3ns)

Symbol

www.fairchildsemi.com

VCC

3.3V 0.3V

2.7V

2.5V 0.2V

Vmi

1.5V

1.5V

VCC/2

Vmo

1.5V

1.5V

VCC/2

Vx

VOL + 0.3V

VOL + 0.3V

VOL + 0.15V

Vy

VOH 0.3V

VOH 0.3V

VOH 0.15V

Preliminary

74LCX32373

Schematic Diagram Generic for LCX Family

www.fairchildsemi.com

74LCX32373 Low Voltage 32-Bit Transparent Latch with 5V Tolerant Inputs and Outputs (Preliminary)

Preliminary

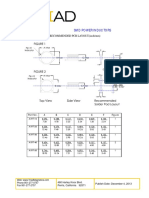

Physical Dimensions inches (millimeters) unless otherwise noted

96-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm Wide

Package Number BGA96A

Preliminary

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and

Fairchild reserves the right at any time without notice to change said circuitry and specifications.

LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD

SEMICONDUCTOR CORPORATION. As used herein:

2. A critical component in any component of a life support

device or system whose failure to perform can be reasonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

1. Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into the

body, or (b) support or sustain life, and (c) whose failure

to perform when properly used in accordance with

instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the

user.

www.fairchildsemi.com

www.fairchildsemi.com

You might also like

- Data SheetDocument8 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- Data SheetDocument16 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- Types MC and MCN Multilayer RF Capacitors High-Frequency OptionsDocument9 pagesTypes MC and MCN Multilayer RF Capacitors High-Frequency OptionsΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- Data SheetDocument9 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- Datasheet TL082 PDFDocument11 pagesDatasheet TL082 PDFJavier RenanNo ratings yet

- Types MC and MCN Multilayer RF Capacitors High-Frequency OptionsDocument9 pagesTypes MC and MCN Multilayer RF Capacitors High-Frequency OptionsΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- Data Sheet 1Document17 pagesData Sheet 1ΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- Axial Leads/Spinguard: General DescriptionDocument6 pagesAxial Leads/Spinguard: General DescriptionΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- 3.3 V Ecl/Pecl/Hstl/Lvds: ÷2/4, ÷4/5/6 Clock Generation ChipDocument12 pages3.3 V Ecl/Pecl/Hstl/Lvds: ÷2/4, ÷4/5/6 Clock Generation ChipΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- Data SheetDocument19 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- Data SheetDocument6 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- Data SheetDocument12 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- 54ACT283 4-Bit Binary Full Adder With Fast Carry: General Description FeaturesDocument8 pages54ACT283 4-Bit Binary Full Adder With Fast Carry: General Description FeaturesΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- LM1117Document21 pagesLM1117dipankaborahNo ratings yet

- TC1072 50ma Cmos Ldo With Shutdown, Error Output and V BypassDocument12 pagesTC1072 50ma Cmos Ldo With Shutdown, Error Output and V BypassΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- Data SheetDocument4 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- CD 4023Document12 pagesCD 4023giorgio19741No ratings yet

- Patented : SM6S10 Thru SM6S36ADocument5 pagesPatented : SM6S10 Thru SM6S36AΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- Data SheetDocument4 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- DMTH6004SPS: 60V 175°C N-Channel Enhancement Mode Mosfet PowerdiDocument7 pagesDMTH6004SPS: 60V 175°C N-Channel Enhancement Mode Mosfet PowerdiΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- AX97 Series: SMD Power InductorsDocument3 pagesAX97 Series: SMD Power InductorsΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- Wall Plug Ins Electrical SpecsDocument1 pageWall Plug Ins Electrical SpecsΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- Data SheetDocument16 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- 8K Microwire Compatible Serial EEPROM: 93AA76A/B/C, 93LC76A/B/C, 93C76A/B/CDocument26 pages8K Microwire Compatible Serial EEPROM: 93AA76A/B/C, 93LC76A/B/C, 93C76A/B/CΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣ100% (1)

- VN0610LL FET Transistor: N Channel - EnhancementDocument4 pagesVN0610LL FET Transistor: N Channel - EnhancementΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5783)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Pendola Suspendida MPK 450 1x150wDocument3 pagesPendola Suspendida MPK 450 1x150wwilber ticonaNo ratings yet

- Sustainable Urban Transport Index for Bhopal, IndiaDocument43 pagesSustainable Urban Transport Index for Bhopal, IndiaSayani MandalNo ratings yet

- Computers & Industrial Engineering: Guohui Zhang, Xinyu Shao, Peigen Li, Liang GaoDocument10 pagesComputers & Industrial Engineering: Guohui Zhang, Xinyu Shao, Peigen Li, Liang Gaocloud69windNo ratings yet

- MV Capacitor CalculationDocument1 pageMV Capacitor CalculationPramod B.WankhadeNo ratings yet

- Draft User Manual MISDocument306 pagesDraft User Manual MISkhajuriaonlineNo ratings yet

- Advanced View of Projects Raspberry Pi List - Raspberry PI ProjectsDocument186 pagesAdvanced View of Projects Raspberry Pi List - Raspberry PI ProjectsBilal AfzalNo ratings yet

- Annotated BibliographyDocument6 pagesAnnotated Bibliographyapi-282104538No ratings yet

- Draft Questionnaire - Identifying Good Practices, Documentation and Sharing - CP & VAC in (Host & Camps) - Introduction To Organization and PersonDocument3 pagesDraft Questionnaire - Identifying Good Practices, Documentation and Sharing - CP & VAC in (Host & Camps) - Introduction To Organization and PersonAminul QuayyumNo ratings yet

- HCTS Fabricated Products Group Empowers High Tech MaterialsDocument12 pagesHCTS Fabricated Products Group Empowers High Tech MaterialsYoami PerdomoNo ratings yet

- Ciara Mae G. Daguio Civil Engineer ResumeDocument1 pageCiara Mae G. Daguio Civil Engineer ResumeCiara Mae DaguioNo ratings yet

- Pipe Schedule MethodDocument4 pagesPipe Schedule MethodSanket PhatangareNo ratings yet

- Type AKP20 MICRO-Axial Piston Pumps: Up To 300 Bar 0,012 CM /revDocument6 pagesType AKP20 MICRO-Axial Piston Pumps: Up To 300 Bar 0,012 CM /revpeterNo ratings yet

- Altair's Student Guides - CAE and Design Optimization - AdvancedDocument70 pagesAltair's Student Guides - CAE and Design Optimization - AdvancedKFourMetrics100% (11)

- Afs General - Adjustment-TestDocument4 pagesAfs General - Adjustment-Testphuong leNo ratings yet

- Webpage Evaluation GuideDocument1 pageWebpage Evaluation Guideankit boxerNo ratings yet

- Week February 15TH To 19THDocument18 pagesWeek February 15TH To 19THQUETEVALGAMADRESNo ratings yet

- SH BSC Hons Pre Registration Nursing PDFDocument104 pagesSH BSC Hons Pre Registration Nursing PDFJogendra Singh PatelNo ratings yet

- List of Intel MicroprocessorsDocument46 pagesList of Intel MicroprocessorsnirajbluelotusNo ratings yet

- Giving OpinionsDocument3 pagesGiving OpinionsAndreea BudeanuNo ratings yet

- WorkshopDocument4 pagesWorkshopAmit GuptaNo ratings yet

- Latifa's Thesis PDFDocument182 pagesLatifa's Thesis PDFنذير امحمديNo ratings yet

- Additional MathematicsDocument10 pagesAdditional MathematicsAnonymous jqevOeP7No ratings yet

- Safety and Security Manual For Safety Manager SCDocument101 pagesSafety and Security Manual For Safety Manager SCk2tzgwmsc5No ratings yet

- Installing A Konica Minolta C220, C280, C360, C452, C652Document3 pagesInstalling A Konica Minolta C220, C280, C360, C452, C652nazerrulNo ratings yet

- 2016 MAEG 3040 SyllabusDocument2 pages2016 MAEG 3040 SyllabusJohnNo ratings yet

- Mooring AnalysisDocument17 pagesMooring AnalysisIfediora GodsonNo ratings yet

- Electric Power Distribution - Wikipedia, The Free EncyclopediaDocument3 pagesElectric Power Distribution - Wikipedia, The Free EncyclopediasacuarsNo ratings yet

- Egerton Genetics eLearning MaterialsDocument213 pagesEgerton Genetics eLearning MaterialsAringo ArumNo ratings yet

- Principles of Business Grade 10 Weeks 1-5 - Term 3Document49 pagesPrinciples of Business Grade 10 Weeks 1-5 - Term 3Daniel DowdingNo ratings yet

- Nordstrom Physical Security ManualDocument13 pagesNordstrom Physical Security ManualBopanna BolliandaNo ratings yet