Professional Documents

Culture Documents

Rapport Projet RS232

Uploaded by

Khalil FatehCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Rapport Projet RS232

Uploaded by

Khalil FatehCopyright:

Available Formats

UNIVERSITE SIDI MOHAMED BEN ABDELLAH

FACULTE DES SCIENCES ET TECHNIQUES FES

Filire dIngnieurs

SYSTEMES ELECTRONIQUES ET TELECOMMUNICATIONS

Communication srie RS232

avec une FPGA Cyclone IV

de ALTERA

Ralis par :

-

Mohammed Ayoub BOUKHRIS

Abdelmajid EL.BAHAOUI

Amal BOUAMOUTE

Encadr par :

Pr. M.RAZI

SET 2013-2014

UNIVERSITE SIDI MOHAMED BEN ABDELLAH

FACULTE DES SCIENCES ET TECHNIQUES FES

Cahier de charge :

Le but de ce projet est la ralisation dune communication entre un ordinateur et la

carte cyclone IV dALTERA via le port de communication srie le RS232 .

Cette application vise cre une partie hardware est une partie software qui vont tre

responsable de cette communication.

Prsentation du port de communication srie le RS232 :

I.

Prsentation gnrale

Les communications entre les quipements sont dfinies par des normes, dans le cadre

du CCITT (Comit Consultatif International des Tlphones et Tlgraphes) ; voici les

lments dune liaison entre quipements communicants :

ETTD : Equipement Terminal de Traitement de Donnes (DTE: Data Terminal Equipment).

Cest un quipement susceptible de transmettre des donnes (console, serveur, PC , ..).

ETCD : Equipement Terminal de Circuit de Donnes

Equipment).

(DCE : Data Communication

Cest un quipement situ chaque extrmit du support de transmission ; il a pour rle de

convertir (ou adapter) le signal transmettre en un signal compatible avec les possibilits de

transport.

La jonction : cest linterface physique entre le DTE et le DCE. Elle dfinit les caractristiques de la

connexion selon 3 types : physique, lectrique et fonctionnelle.

La caractristique physique dfinit laspect mcanique des connecteurs.

La caractristique lectrique concerne la transmission des bits et les niveaux de

tension.

La caractristique fonctionnelle dfinit le protocole dchange entre le DTE et le DCE.

2013-2014

UNIVERSITE SIDI MOHAMED BEN ABDELLAH

FACULTE DES SCIENCES ET TECHNIQUES FES

II.

Dfinition dune liaison srie :

Une liaison srie est une ligne o les bits d'information (1 ou 0) arrivent successivement

(en srie), soit intervalles rguliers (transmission synchrone), soit des intervalles

alatoires, en groupe (transmission asynchrone). Elle permet de faire dialoguer 2 quipements

(et seulement 2) entre eux.

III.

Description RS232 :

La connectique de cette liaison se prsente frquemment sous la forme du connecteur

DE-9 ou DB-25, mais peut aussi tre d'un autre type (RJ25). Seule la version DB-25 est

vraiment standardise, la DE-9 (trs souvent appele DB-9 dans le commerce) est une

adaptation d'IBM lors de la cration du PC. La transmission des lments d'information

(ou bit) s'effectue bit par bit, de manire squentielle.

Le standard RS232 prvoit des formats de transmission synchrone et asynchrone. La

transmission asynchrone tant beaucoup plus dmocratise en raison de sa souplesse

d'utilisation. Ce standard dfinit :

IV.

Le format des donnes transmises.

Le brochage des connecteurs.

Les niveaux de tension du support physique de transmission.

Le protocole d'change des informations.

Protocole RS232 :

Pour tablir une communication effective via RS-232, il est ncessaire de dfinir le protocole

utilis : notamment, le dbit de la transmission, le codage utilis, le dcoupage en trame, etc.

La norme RS-232 laisse ces points libres, mais en pratique on utilise souvent des UART qui

dcoupent le flux en trames d'un caractre ainsi constitues :

1 bit de dpart ;

7 8 bit de donnes ;

1 bit de parit optionnel ;

1 ou plusieurs bits d'arrt.

Le bit de dpart un niveau logique "0" tandis que le bit d'arrt est de niveau logique "1". Le

bit de donne de poids faible est envoy en premier suivi des autres.

La spcification RS-232 prescrit des dbits infrieurs 20 000 bit/s. Cependant, les dbits

utiliss en pratique varient entre 75 bit/s et 115 200 bit/s.

2013-2014

UNIVERSITE SIDI MOHAMED BEN ABDELLAH

FACULTE DES SCIENCES ET TECHNIQUES FES

V.

Le brochage pour une liaison RS232

les figures ci-dessous

VI.

montrent les pins de brochage pour une liaison RS232.

Description rapide des signaux :

2013-2014

UNIVERSITE SIDI MOHAMED BEN ABDELLAH

FACULTE DES SCIENCES ET TECHNIQUES FES

VII.

Format des trames RS232

La srialisation d'une donne envoyer est ralise par un circuit UART (ou contrleur

RS232). La transmission tant asynchrone, elle s'effectue sans signal d'horloge. Le rcepteur

peut recevoir sans erreur la donne srie condition :

De dtecter le dbut de la trame transmise

De connatre la frquence de transmission de chaque bit

De connatre le format prcis de la trame

Ainsi, les UART d'mission et de rception doivent tre configurs de manire identique et

conformment aux options choisies concernant le format des trames RS232 et la vitesse de

transmission.

Une trame RS232 est constitue des bits suivants :

1 bit de START : C'est un '0' logique. Lorsque la ligne est au repos, elle est au niveau

logique '1'. L'mission de ce bit permet au rcepteur de dtecter le dbut de la

transmission d'une trame, et de se synchroniser avec l'metteur.

La donne de 1 8 bits suivant les UART. Il faut savoir que le poids faible de la

donne est transmis en premier.

1 bit de parit (optionnel) : Il permet la dtection d'une ventuelle erreur de

transmission due un support dfaillant, ou une perturbation lectromagntique. Le

calcul du bit de parit est ralis par l'UART. On peut distinguer 2 type de parit :

La parit paire : Le nombre de '1' contenus dans l'ensemble donne et parit

doit tre un nombre pair.

La parit impaire : Le nombre de '1' contenus dans l'ensemble donne et parit

doit tre un nombre impair.

1 ou 1,5 ou 2 STOP bit : C'est un '1' logique transmis pendant une dure de 1 ou 1,5 ou

2 cycles de transmission. Il permet de maintenir la ligne au repos avant la transmission

ventuelle d'une nouvelle trame.

2013-2014

UNIVERSITE SIDI MOHAMED BEN ABDELLAH

FACULTE DES SCIENCES ET TECHNIQUES FES

Hardware

Le processeur Nios II est un soft processeur, dfinit avec un langage de description matrielle,

qui peut-tre implment sur les FPGA Altera en utilisant la suite logicielle Quartus II.

Pour implmenter un systme complet, il est ncessaire dajouter dautres lments au

processeur, tel que des mmoires, des interfaces dentres/sorties, des temporisateurs (timers)

et des interfaces de communications.

Un systme complet base de Nios II peut tre implment sur la carte DE2 comme le montre

la figure ci-dessous.

2013-2014

UNIVERSITE SIDI MOHAMED BEN ABDELLAH

FACULTE DES SCIENCES ET TECHNIQUES FES

Linterface UART dans la carte DE-115 :

Architecture matriel du projet :

Dans la configuration du projet, on a utilis :

-

CPU : Nios II

On-chip Memory de taille 200ko

JTAG-UART

UART (RS 232)

2013-2014

UNIVERSITE SIDI MOHAMED BEN ABDELLAH

FACULTE DES SCIENCES ET TECHNIQUES FES

Le schmatique est comme suit :

Entres du systme :

-

Signal dhorloge CLK_0

Signal Reset

RXD

Sorties du systme :

- LCD

- TXD

Le PIN Planner du projet :

Aprs la synthtisation du projet, on passe la partie dveloppement software.

2013-2014

UNIVERSITE SIDI MOHAMED BEN ABDELLAH

FACULTE DES SCIENCES ET TECHNIQUES FES

SOFTWARE :

Notre code C est comme suit, il repose sur lenvoi et la rception des donnes lUART, le

SOPC Builder contient un noyau UART nom uart_0 qui nest pas ncessairement

configur comme stdout.

Lexplication du code est en commentaire.

Conculsion :

Notre code a bien t compil et excut parfaitement, le fichier system.h a t aussi gnr

sans problme. Lorsquon a charg le programme dans la FPGA, on a remarqu que les 2

LED tmoins RXD et TXD se sont allums pour une dure trs brve (les deux LEDs sur la

carte cyclone IV), ce qui veut dire que la transmission et rception bien t faite, sauf quil

reste un problme juste au niveau de laffichage du rsultat dans le LCD.

2013-2014

You might also like

- Kromberg ShubertDocument9 pagesKromberg ShubertNa DerNo ratings yet

- Maths3 Optimisation ContrainteDocument8 pagesMaths3 Optimisation ContrainteDiop0% (1)

- Amina Jouineh Pfe - Amina JouinehDocument100 pagesAmina Jouineh Pfe - Amina Jouinehesfouna esfounaNo ratings yet

- Guide Redaction PFE WordDocument4 pagesGuide Redaction PFE WordJawad Maal0% (1)

- TD 10 0 PDFDocument9 pagesTD 10 0 PDFRahim MenadiNo ratings yet

- VideoExam01 PDFDocument20 pagesVideoExam01 PDFMohamed HachimiNo ratings yet

- Cours Bases de Données ENSAM-MEknès AHMADI 2020 2021Document38 pagesCours Bases de Données ENSAM-MEknès AHMADI 2020 2021redwane ouberriNo ratings yet

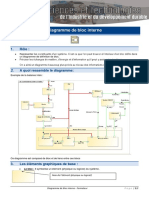

- 6 Diagramme de Bloc InterneDocument3 pages6 Diagramme de Bloc InternekamalNo ratings yet

- MemoireDocument108 pagesMemoirewael frajNo ratings yet

- Naitali-EIGE452 - TD BG Système de Suspension PDFDocument3 pagesNaitali-EIGE452 - TD BG Système de Suspension PDFEl Ghafraoui100% (1)

- Rapport TP 1Document15 pagesRapport TP 1Mounaim MatiniNo ratings yet

- M05 - Micro-Ordinateur, Production de Documents Techniques GE-ESA PDFDocument131 pagesM05 - Micro-Ordinateur, Production de Documents Techniques GE-ESA PDFHassan AzmiNo ratings yet

- 2 PhasesDocument6 pages2 Phasesياسين بوعيشيNo ratings yet

- Experiences Professionnelles: Ingenieur IndustrielDocument1 pageExperiences Professionnelles: Ingenieur Industrielahlam omariNo ratings yet

- Rapport TestDocument35 pagesRapport TestmarwaabdNo ratings yet

- Rpport Traitement - SignalDocument20 pagesRpport Traitement - SignalAdama COULIBALYNo ratings yet

- Introduction À L'electronique de PuissanceDocument7 pagesIntroduction À L'electronique de PuissanceBALLOUK SoufianeNo ratings yet

- Généralités: PIC 16F84Document8 pagesGénéralités: PIC 16F84Selmane SaoudNo ratings yet

- Rapport V0Document24 pagesRapport V0abderra7menNo ratings yet

- PFE Book HutchinsonDocument42 pagesPFE Book Hutchinsonshayma MensiNo ratings yet

- 01-Bases de Donnees IntroDocument5 pages01-Bases de Donnees Introredwane ouberriNo ratings yet

- Exercice N°1: Série TD 3Document4 pagesExercice N°1: Série TD 3Katia ChalalNo ratings yet

- 2 Classe Et ObjetDocument40 pages2 Classe Et ObjetWajdi MathlouthiNo ratings yet

- Rapport Final 1-ConvertiDocument73 pagesRapport Final 1-ConvertiAkram Ben HssanNo ratings yet

- Toutes Les Notes Hcia Ai Huawei Examen Simulé ÉcritDocument31 pagesToutes Les Notes Hcia Ai Huawei Examen Simulé ÉcritScribdTranslationsNo ratings yet

- Gautier EstimationDocument35 pagesGautier EstimationSahliMohamedNo ratings yet

- l3 Theorie Des Graphes Cour Chap1Document5 pagesl3 Theorie Des Graphes Cour Chap1Yacine AbedNo ratings yet

- Conc Math FI 2015 PDFDocument4 pagesConc Math FI 2015 PDFlaabissiNo ratings yet

- Rapport RihabDocument84 pagesRapport RihabMaissa OueslatiNo ratings yet

- QCMs de Culture DigitaleDocument68 pagesQCMs de Culture Digitaleouzidouh.lahcen.95No ratings yet

- 56eaed99d5d8b PDFDocument53 pages56eaed99d5d8b PDFYahya ChiguerNo ratings yet

- Cadenas de MarkovDocument10 pagesCadenas de MarkovArturo NogueraNo ratings yet

- Mini Projet Recherche Operationnelle Programmation Dans CDocument10 pagesMini Projet Recherche Operationnelle Programmation Dans CBitote ADNo ratings yet

- RE Chap1 ENSATe - 2010 2011Document87 pagesRE Chap1 ENSATe - 2010 2011Med Reda CheffiNo ratings yet

- Ch6 - Méthode de Diagnostic ADEPA-CETIMDocument6 pagesCh6 - Méthode de Diagnostic ADEPA-CETIMyoussef machkourNo ratings yet

- Rapport de Stage Cristal StrassDocument40 pagesRapport de Stage Cristal StrassToufik ZeroukNo ratings yet

- Chapitre 5 Ordonnancement Et Gestion Des Projets PDFDocument35 pagesChapitre 5 Ordonnancement Et Gestion Des Projets PDFSafa DridiNo ratings yet

- Acquisition Et Traitement D'un Signal PPG Pour Le Monitoring de Signes BiomédicauxDocument3 pagesAcquisition Et Traitement D'un Signal PPG Pour Le Monitoring de Signes BiomédicauxAmal Jellali100% (1)

- Rapport Stage - Elaboration Cahier de Cha PDFDocument96 pagesRapport Stage - Elaboration Cahier de Cha PDFatsoufienNo ratings yet

- Amelioration de La Productivite Au Niveau de La Ligne de Production Citroën Ami O2c - Nouhayla El OuardiDocument112 pagesAmelioration de La Productivite Au Niveau de La Ligne de Production Citroën Ami O2c - Nouhayla El Ouardiayoub OuddaaneNo ratings yet

- Enonce tp5 Reseaux Dut1-Id060 PDFDocument14 pagesEnonce tp5 Reseaux Dut1-Id060 PDFRomaissa MessNo ratings yet

- BacSSI2009 Correction CopieDocument10 pagesBacSSI2009 Correction CopieOmar RajadNo ratings yet

- GmaoDocument10 pagesGmaohamza elgarragNo ratings yet

- TP ΜContr 21Document2 pagesTP ΜContr 21Taha Chergui MouaneNo ratings yet

- TP1: Configuration Et Utilisation Du CODEC ButDocument2 pagesTP1: Configuration Et Utilisation Du CODEC ButNinå Så50% (2)

- Chapitre II Le GrafcetDocument16 pagesChapitre II Le Grafcetsociété ettrisiti oulad fares100% (1)

- Mini Projet Prceuse Indistrille PDFDocument25 pagesMini Projet Prceuse Indistrille PDFtinhinane hadjouNo ratings yet

- Examen Si 2bac STM 2022 Session Rattrapage CorrigeDocument11 pagesExamen Si 2bac STM 2022 Session Rattrapage CorrigeLOUNDOU orthegaNo ratings yet

- Presentation VendredipptxDocument37 pagesPresentation VendredipptxaminaNo ratings yet

- Corrigé S1 2013Document7 pagesCorrigé S1 2013youssefelalaouiNo ratings yet

- Ordo PDFDocument42 pagesOrdo PDFSa FiNo ratings yet

- Minimae PDFDocument5 pagesMinimae PDFSarah JijliNo ratings yet

- Reconnaissance de L'écritureDocument27 pagesReconnaissance de L'écritureNezha BENICHOUNo ratings yet

- Étude Des Différents Schémas CommandeDocument6 pagesÉtude Des Différents Schémas Commandeammar omarNo ratings yet

- GE S2 M8.2 Automatismes L&I TP Manip4 EL Hammoumi ConvertiDocument2 pagesGE S2 M8.2 Automatismes L&I TP Manip4 EL Hammoumi ConvertiMontasar MbarkiNo ratings yet

- Correction Complementaire Fast SadtDocument3 pagesCorrection Complementaire Fast SadtTasnym JalelNo ratings yet

- Support TP - Technologie Des Chaines de ProductionDocument8 pagesSupport TP - Technologie Des Chaines de ProductionFrançoise NicolasNo ratings yet

- Le système d'approvisionnement en terres dans les villes d'Afrique de l'Ouest: L’exemple de BamakoFrom EverandLe système d'approvisionnement en terres dans les villes d'Afrique de l'Ouest: L’exemple de BamakoNo ratings yet

- Cours Que D Instrumentation 2010 2011Document120 pagesCours Que D Instrumentation 2010 2011karimNo ratings yet

- DVB NGHDocument10 pagesDVB NGHKhalil FatehNo ratings yet

- Rapport de StageDocument75 pagesRapport de StageKhalil FatehNo ratings yet

- Codes Et TurbocodesDocument408 pagesCodes Et TurbocodesKhalil FatehNo ratings yet

- PHD Dore 26102007 VFDocument216 pagesPHD Dore 26102007 VFKhalil FatehNo ratings yet

- Astuces de Programmation en Assembleur EN C PDFDocument31 pagesAstuces de Programmation en Assembleur EN C PDFKhalil FatehNo ratings yet

- Jeu d'Instructions ΜC 16F84Document4 pagesJeu d'Instructions ΜC 16F84Khalil FatehNo ratings yet

- CsharpDocument253 pagesCsharploesouleymaneNo ratings yet

- 1 HacheursDocument14 pages1 HacheursZakaria Djahara100% (1)

- VHDLDocument16 pagesVHDLKhalil Fateh100% (2)

- AdjectifsDocument1 pageAdjectifsjesuisfracasNo ratings yet

- Le Micrôcontroleur PIC16F84Document403 pagesLe Micrôcontroleur PIC16F84fayssal22No ratings yet

- Gek110293a FRDocument6 pagesGek110293a FRKONANNo ratings yet

- 2 Rpi InstallationDocument3 pages2 Rpi InstallationkaraNo ratings yet

- 1.les Composants D'un Systeme InformatiqueDocument14 pages1.les Composants D'un Systeme InformatiqueTahar GFNo ratings yet

- Barbara Obermeier Ted Padova - Photoshop - Elements 2021 Pour Les NulsDocument567 pagesBarbara Obermeier Ted Padova - Photoshop - Elements 2021 Pour Les NulsIrie Fabrice ZRONo ratings yet

- Les Types de Variable en C++Document11 pagesLes Types de Variable en C++Venance Aimé KouaméNo ratings yet

- Rapport-Logiciel RDocument21 pagesRapport-Logiciel RchaymaNo ratings yet

- FR Dsmbisp SLM v40Document227 pagesFR Dsmbisp SLM v40ChristopheReyndersNo ratings yet

- Tp2 Et 3 LST Meca 21Document8 pagesTp2 Et 3 LST Meca 21Aâchak OumaymaNo ratings yet

- Memoire Online - Mise en Place D'un Système de Gestion Centralisé Des Logs Et Des Évènements  SIEM  - Joseph DEMBELEDocument3 pagesMemoire Online - Mise en Place D'un Système de Gestion Centralisé Des Logs Et Des Évènements  SIEM  - Joseph DEMBELEDavid DjidonouNo ratings yet

- VHDLDocument192 pagesVHDLWalid Amri0% (1)

- Administration Windows Server 2003Document177 pagesAdministration Windows Server 2003Yassine WannessiNo ratings yet

- SR7012U FRA PDF UG V00aDocument344 pagesSR7012U FRA PDF UG V00aDufourNo ratings yet

- Administration de Réseaux Informatiques - OpenLDAPDocument25 pagesAdministration de Réseaux Informatiques - OpenLDAPABDENNASSER REBHINo ratings yet

- Liste Fiches de Synthèse Cycle 4Document1 pageListe Fiches de Synthèse Cycle 4AbdelNo ratings yet

- DxO PhotoLab 4.0.0 Version EliteDocument2 pagesDxO PhotoLab 4.0.0 Version Elitezevotco jemmyNo ratings yet

- Verrouillage Des Périphériques de Stockage USBDocument20 pagesVerrouillage Des Périphériques de Stockage USBahoubaNo ratings yet

- Safeline mx3Document24 pagesSafeline mx3Justin RichardNo ratings yet

- Heritage PooDocument26 pagesHeritage Poojoairia lafhalNo ratings yet

- 2023-2024 - Deuxième Devoir de Réseau Tle IMI-LTCDocument5 pages2023-2024 - Deuxième Devoir de Réseau Tle IMI-LTCkamalouidrissou2No ratings yet

- OPU-1 Description Du Produit R2.5.1-F PDFDocument99 pagesOPU-1 Description Du Produit R2.5.1-F PDFSalvador FayssalNo ratings yet

- TP NfsDocument5 pagesTP Nfsali hakunaNo ratings yet

- ITN - Module - 1-3 BonDocument156 pagesITN - Module - 1-3 BonRoland KagboNo ratings yet

- Prepa IrssDocument92 pagesPrepa IrssAnt'Hony Koumba100% (1)

- Système de Gestion Des Fichiers: Ystemes D XploitationDocument4 pagesSystème de Gestion Des Fichiers: Ystemes D Xploitationsalma ben hssinNo ratings yet

- TD N°1 Avec Cor Alim À Dec Direct 2020Document18 pagesTD N°1 Avec Cor Alim À Dec Direct 2020Ala Massoudi100% (3)

- 1.initiation Réseaux Et Sécurité D'entrepriseDocument20 pages1.initiation Réseaux Et Sécurité D'entrepriseAmadou Mbaye100% (1)

- Countis E34: Compteur D'énergie Active Triphasé Direct 100 A Avec Homologation MID Et Communication JBUS/MODBUSDocument54 pagesCountis E34: Compteur D'énergie Active Triphasé Direct 100 A Avec Homologation MID Et Communication JBUS/MODBUSjemalikNo ratings yet

- Fiche Des Résultats Expérimentaux - 22Document7 pagesFiche Des Résultats Expérimentaux - 22Karima HamdanNo ratings yet

- TP2 Delpfi S3Document3 pagesTP2 Delpfi S3Leila BaNo ratings yet

- Les Différents Types de CapteursDocument1 pageLes Différents Types de CapteursAbdelhamid SammoudiNo ratings yet