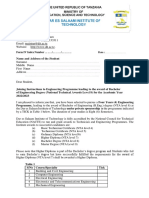

Professional Documents

Culture Documents

Design of A Low Power SRAM Cell by Tanner Tool 45 NM

Uploaded by

Editor IJRITCCOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Design of A Low Power SRAM Cell by Tanner Tool 45 NM

Uploaded by

Editor IJRITCCCopyright:

Available Formats

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 3 Issue: 12

ISSN: 2321-8169

6631 - 6636

______________________________________________________________________________________

Design of a Low Power SRAM Cell by Tanner Tool 45 NM

Yashwant Singh Parihar1, Ghansyam Jangid 2

1

M.Tech Scholar, Gyan Vihar University, Jaipur, Rajasthan, India

Assistant professor, E.C.E Deptt., Gyan Vihar University, Jaipur, Rajasthan, India

Abstract:- The absorption of power & SRAMs speed are major concern which followed several designs in accordance to the minimal

absorption of power. The main concern of this document is on decadence of power while operation of Write is executed in 6-T CMOS SRAM

also while operation of read as well. In this paper, an extra transistor is invaded in cell of SRAMs which will be regulate total capacitance while

execution of read & write operations & also optimize the capacitance so eventually leads to bring down decadence in power. In this document

we mainly focus on decadence of power during short circuits also the fluctuating decadence of power which can also be termed as power which

is dynamic. The tool of Tanner is deployed to evaluate the circuitry, the schema of cell of SRAM is formulated on S Edit & simulation of net list

is furnished by making use of T Spice & also assessment of waveforms is done by W Edit. The characterization of circuitry is done by making

use of technology of 45 nm which furnish a voltage of 1.2V. The outcomes are put in contrast to traditional 6T SRAM & 7T SRAM which also

characterizes the same in this document. Also we implement a cell with less power that is comprised of an additional transistor & also the gate of

that transistor will regulate the operations of write & read of information when we implement function of write operation, that additional

transistor will execute function of write & additional transistor will shorten the section in ground & Vdd & save the power.

Keyword :- Minimal Power, SRAM, 130nm, 7T SRAM cell.

__________________________________________________*****_________________________________________________

cells of memory is evaluated, its imitation can be done for

I.

INTRODUCTION

various times by making fewer variations in design in

regulatory circuitry of I/O.

A memory of semiconductor which is also ARAM is a bistate

circuitry that is ployed to retain every single bit. The static &

II.

SRAM CELL: SCHEMATIC AND WORKING

dynamic RAM which should be refreshed in a defined period

The figure 1 presents memory cell of SRAM for an individual

of time. Reminisce is also explained by SRAM but it has

bit. The latches which are static are deployed in cell of

volatile nature in a traditional way that means that data will

SRAM. The cell is formulated from a flip flop that is

not be retained if memory is turned off.

consisted of inverters which are coupled as cross.

While commencing the particulars of design to formulation of

layout of mask, the design of layout of an integral circuitry

have various steps in processing which needed to be focused

while execution. The steps invades design of schema at level

of transistor, simulation of SPICE at circuitry as per designed

proportions of W/L of a distinct transistor, formation of layout

by making use of editor of layout, designing check rule,

extraction in parasitic manner & exact evaluation &

simulation. Such methodologies for processing cant be

changed for operations which are free from error & same king

of methodology is deployed for design of IC of SRAM of 1

kilobyte. The cell of SRAM is its main constituent which

accumulates one bit of information at a time. The lines of bit

that are common can be written & read over cell of SRAM. A

standard tool for industry which is SPICE is ployed for

purpose of simulation & assessment of cell of SRAM &

eventually for complete design. The circuitry which is already

charged, the amplifier of sense & circuitry of read & write

accomplish memory of one SRAM. The arrangement of

matrix is done in form of rows & columns that enhance the

addressing of memory in an easy way of bits of memory &

also furnish flexibility in design. As the working of array of

Figure 1 :- Schema for cell of SRAM

The transistors of access which are 2 in number are ployed to

evaluate the information retained in cell. The line for control

that is WL, word line turns the transistors OFF or ON. In

6631

IJRITCC | December 2015, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 3 Issue: 12

ISSN: 2321-8169

6631 - 6636

______________________________________________________________________________________

general, the WL is linked to outcome of circuitry of decoder

of row. As the WL is equal to Vdd, BL is linked to cell of

SRAM & its complementary, which allows both write & read

operations. The function of read & write is executed by

transistors of access.

READ OPERATION

The Y node is taken as the node for reference for cell of

SRAM. As the node of Y at Vdd is high, value 1 is stored in

cell & bar of Y node retains value 0. For the circumstances

that have reverse voltage, cell retains value 0. It is taken that

cell retains the value of 0. As the operation of read

commences, the lines of BL & BL bar are charged to Vdd/2.

As by the initiation of WL, the flow of current is by M5 &

M6. Though current will flow through Vdd by M1 & M5

fluctuating the capacitance of line of bit, like Cbl. The present

capacitance on line of B Lbar like CBLbar dispenses the

transistors by M6 & M4. The process formulates a difference

in voltage among the node Y & Y bar which is detected by

amplifier to sense value of 1. To parallel to this, value of 0 is

sensed by amplifier.

when supply of power is less because margins in noise get

degraded.

There are 6 transistors in a cell of 6T-SRAM. The figure 4.1

presents a standard cell. The transistors for access are N2 &

N3 and other 4 transistors, N1, N2, P1, P2 formulates 2

inverters. Information is latched by these 2 inverters. The

information gets invaded to inverter of latching by transistor

of access. The method to introduce information is termed as

operation of writing & process to retrieve information is

termed as process of reading. A row of cell of SRAM is

chosen by WL. A column is chosen by BLbar & BL. A

defined cell of SRAM is chosen as BL & WL are turned on. A

6T-SRAM & extra circuitry of reading can formulate cell of

10T-SRAM.

A cell of 10T-SRAM gets designed by making use of cadence

virtuoso in technology of CMOS180mm & characteristics of

the performance like delay, power, delay in power are

assessed.

WRITE OPERATION

Here the operation to write value 0 is presumed to store 1

value. By this, amplifiers of sensing & circuitries which are

pre charged are disabled. This cell is chosen by triggering the

associating signal of WL. In order to write value of 0 to cell,

line of BL is taken down to the line of BLbar, which is

enhanced to Vdd by the circuitry of write. So the Ybar node is

raised to Vdd/2 eventually Y node is brought down to the

same. As the voltage gets over the level on 2 node feedback,

action commences. The capacitances are formulated by M4,

M6 & M3, M5 which are discharged & charged

consequentially. Eventually the Y node is made stable at 1

value. As the capacitances of parasitic are furnished by

transistors, which has value much lesser than capacitance of

line of bits, and operation of write works fast than read.

III.

Fig.2 :- A 6T cell of SRAMs

IV.

DESIGN AND SIMULATION OF A 10T SRAM

CELL

EXISTING DESIGN DESCRIPTION

SRAM is basically a cell of memory in semiconductor. In

accumulates a bit of data. it functions fast & absorbs minimal

power in contrast to other cells of memory. As it is robust &

has much more stability, more improvisations are being done

in cells of SRAM. SRAM is considered as a cardinal element

on a microprocessor chip. Formulating a cell of SRAM on a

nano scale is formulated as a task that is challengeable as

margins in noise are deduced & sensitivity has been raised to

fluctuations in voltage of threshold. The cell of 10T-SRAM

has better performance than 6T-SRAM on the factors of

stability & reliability. Cell of 6T-SRAM is not much reliable

Architecture of cell of 10T-SRAM is alike to cell of SRAM of

6T, but difference is that it has an extra circuitry for read.

Figure 2 presents cell of SRAM designed for 10T. In cell of

10T-SRAM, 10 transistors are ployed. It comprise of

traditional cells of 6T-SRAM & extra circuitry to read. The

issue arises in traditional cells of 6T-SRAM is that there are

chances to data to be lost while execution of operation of read.

Flipping can occur at voltage at node at Q & Qbar because of

inverters aligned back to back.

This problem can be eliminated by putting an additional

circuitry. The operations of read in 6T and 10T-SRAM cells

are similar. While in scenario of operation of reading, sharing

6632

IJRITCC | December 2015, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 3 Issue: 12

ISSN: 2321-8169

6631 - 6636

______________________________________________________________________________________

of charges occurs in RBL & no-transformed BL-BLB while

operation of read is executed. As charge are shared, so lines of

reading bit dont get discharged fully & remains at a mid level

of voltage. Thus, working of cell becomes like an automated

limiter for swinging lines of bit.

SRAM is requires to get assurance of actual operation. In this

document, a cell of SRAM suggested that incorporates an

additional transistor in way of pull down of both transistor of

driver. This additional transistor will disconnect way in

transistor driver & GND while execution of operation of

writing that decrease aggregated capacitance & power which

is dynamic. The suggested cell of SRAM is applied &

designed by making use of technology of CMOS of 130 nm.

Lastly, outcomes are put in contrast with traditional cell of

6T-SRAM which is signified in the theory of similar

technology.

V.

Fig.3:- Design of a 10T SRAM cell

STANDBY MODE

If insertion of WL is not done, transistors of Paas will be delinked from lines of bit & cell. The inverters which are

coupled cross formulate two inverters linked to each other in

an adjoined manner. They reinforce one & other as they been

de-lined from outer world. The data which is accumulated in

the cell of their memory will be retained in them.

PROBLEM STATEMENT

In a standard circuitry of 6T-SRAM, absorption of power is

greater because of additional current flow. As by image,

generally circuitry of 6T-SRAM is ployed in a standard

circuit. In a case, as function of reading will be initiated, then

flow of leakage in power is in operation of writing in

circuitry. In further scenario, when operation of write is

executed in circuitry, operation of reading will be off but a bit

power flow will be there. And because of this leakage in

power, there will be improvisation in absorption of power. So

we will focus to eliminate the leak in absorption of power.

VI.

PROPOSED METHODLOGY

READ MODE

PROPOSED 7T SRAM CELL

It is presumed that memory accumulates 1 which is stores at a

node. The cycle of read commence as both lines of bit gets pre

charged to logical value 1& embedding the signal of WL with

a pulse of high voltage that triggers both transistors of access.

In next step, as values are accumulated in a & B which gets

transferred to lines of bit, one BL will discharge transistor

drivers & other BL will get pulled by transistor of load in

direction of VDD that is logical 1. The process would have

worked in opposite manner if memory has accumulated 0 &

cell of memory would be at logical 1.

The given Figure 4 presents schema of cell of SRAM with

less power & signals related to it wherever, CS, WL are

required for making a selection for writing & data can be

written from bit bar & bar.

WRITE MODE

Commencement of cycle of writing starts when the values that

are written to BL are applied. If 0 is to be written, so same

will be applied to BLs which means putting BL=0 &

BLbar=1. It is just like to apply a pulse set to latch of SR that

fluctuate state of flip flop. As the values of BL are inverted, 1

is written over it. Assertion of WL is done & values that are to

be accumulated are latched. The factor that causes this is that

input drivers of BL are formulated in such a manner to be

strong than a related transistor in a cell by its own, in a case

that previous states can be over-ridden of inverters which are

coupled cross. A concentrated sizing of transistor in cell of

Figure 4 :- Proposed Circuit

6633

IJRITCC | December 2015, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 3 Issue: 12

ISSN: 2321-8169

6631 - 6636

______________________________________________________________________________________

As represented by Figure 4, cell with minimal power is

comprised of an additional transistor & gate of that additional

transistor will regulate operation of reading or writing

information & also when operation of write is executed as the

additional transistor cuts down the path in Vdd & ground &

save circuitry from short circuit. We can make use of input,

bit data or its complementary to execute operation of writing.

Functioning of cell of SRAM with less power & operation is

explained in the modes of write & read as below:

VII.

RESULTS

6T CONVENTIONAL CIRCUIT

In this circuitry, we deploy transistors 6 in numbers. BL &

WL is defined for write & read operations. The absorption of

power for figure 6.1 is 7.028097e-006 W & delay is 1.34ns.

READ MODE

Generally, cell of SRAM with less power in mode of reading

is alike to traditional cell of SRAM. In this mode, value 1 is

assigned to CS & an additional transistor will be activated on

the basic operation of reading for cell of SRAM when a high

voltage is provided to WLs, both the transistors of access will

get activated & data needed will be out by the sensing

amplifier.

WRITE MODE

Fig 6 :- 6T traditional circuitry

In mode of writing, node of B should be assigned higher value

which is achieved by putting CS as 0 invading signals of WL

value of data is implemented to BL. There may be a

possibility to write state of cell from 1 to 1. As bodes of B &

CS, both are 0, no transition in state occurs. As conductance

of N4 transistor has greater conductance than P2, the state of

cell is flipped easily from 0 to 1 as node B is discharged by

N4. As data can be written from 0 to the corresponding path

as presented in figure 6.

Fig 7 :- Waveform of 6T traditional circuitry

7T SRAM DESIGN

The absorption of power in figure 6.2 is 4.446633e-006W &

delay is 1.18ns.

Fig 5:- suggested circuitry in mode of writing

Parallel, 0 will be written in cell of SRAM at less power. The

path of circuitry is presented in figure.

6634

IJRITCC | December 2015, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 3 Issue: 12

ISSN: 2321-8169

6631 - 6636

______________________________________________________________________________________

Fig 11 :- Outcome of waveform for suggested 7T SRAM

Fig 8:- 7T SRAM Design wit implementation of circuitry of

CS

Power

4.6 micro watt

Reference paper [1]

81 micro watt

Reference paper [2]

50 micro watt

Reference paper [3]

Existing SRAM

7.028097 micro watt

design

Proposed SRAM

4.184023e-006 watts

Design

Table 1 :- Table of Contrast

VIII.

Fig 9 :- Waveform for design of 7T SRAM

PROPOSED 7T SRAM DESIGN

The absorption of power for design of 7T SRAM is

4.184023e-006W with delay of 840.06ps.

Delay

Not mention

7.5 ns

5.5 ns

1.34 ns

840.06 ps

CONCLUSION AND FUTURE SCOPE

As observations from outcomes reveal that in cells of

SRAAM with less power, aggregated power gets brought

down by 43%. It presents that cell of memory will absorb low

power in contrast to traditional cells of SRAM whose

outcomes are imitated in this document. In a situation of

power with short circuits, decadence of power gets down by

43% that is less in contrast to traditional cells of SRAM. Thus,

the cell of SRAM which is newly formulated absorbs low

power & it can be said that it is aware of power that can be

accepted in the present market of VLSI. The delay is also

improvised by 74%. So, cell of SRAM absorbs low power &

executes operation faster than a standard cell of SRAM. In

this cell lesser amount of power s taken in & so it saves

around 43% of power in contrast to the present cells of

SRAM. Thus these cells are deployed in electronics which are

portable & are operated by battery & so will need low cost

sink of heat to furnish heat to surroundings.

This documentation can be elaborated for future work in order

to bring down need of area that is around 16.72 % greater than

the present cell of SRAM. A methodology can be searched to

reduce this area & also there are no improvisations in cells of

low power when operation to write 1 is executed& so work

can be extended for improvisation in delay whenever,

operation of writing is executed.

Fig 10 :- Suggested design of 7T SRAM

6635

IJRITCC | December 2015, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 3 Issue: 12

ISSN: 2321-8169

6631 - 6636

______________________________________________________________________________________

References

[1] Saravanan, P., and Kalpana, P., A 16nm SRAM design for

low power and high read stability, 3rd International

Conference on Advances in Recent Technologies in

Communication and Computing, Bangalore, pp. 25-31,

2011.

[2] Verma, N., Chandrakasan, A. P., A 256kb 65nm 8T

Subthreshold SRAM Employing Sense Amplifier

Redundancy, IEEE Journal of Solid State Circuits, Vol.

43, No. 1, pp.141-149, 2008.

[3] Athe, P., and Dasgupta, S., A Comparative Study of 6T,

8T and 9T Decanano SRAM cell, IEEE Symposium on

Industrial Electronics and Applications, Kuala Lumpur, pp.

889-894, 2009.

[4] Sah, R. K., Hussain, I., and Kumar, M., Performance

Analysis of a 6T SRAM Cell in 180nm CMOS

Technology, IOSR Journal of VLSI and Signal

Processing, Vol. 5, Issue 2, Ver. 1, pp. 20-22, 2015.

[5] Sah, R. K., Hussain, I., and Kumar, M., Performance

Comparison for Different Configurations of SRAM Cells,

International Journal of Innovative Research in Science,

Engineering and Technology, Vol. 4, Issue 1, pp. 1854318546, 2015.

[6] Jain, S., Santhosh, K., Pattanaik, M., and Raj, B., A 10T

SRAM cell with inbuilt charge sharing for Dynamic power

Reduction, International conference on Advances in

technology and Engineering, Mumbai, pp. 1-6, 2013.

[7] Chang, I. J., Mohapatra, D., and Roy, K., A PriorityBased 6T/8T Hybrid SRAM Architecture for Aggressive

Voltage Scaling in Video Applications, IEEE

[8]

[9]

[10]

[11]

[12]

[13]

[14]

[15]

Transactions On Circuits And Systems For Video

Technology, Vol. 21, No. 2, pp.101-112, 2011.

Prashant Upadhyay, Mr. Rajesh Mehra,Low Power

Design of 64-bits Memory by using 8-T Proposed SRAM

Cell, International Journal of Research and Reviews in

Computer Science (IJRRCS), Vol. 1, No. 4, December

2010.

Sreerama Reddy G.M, P. Chandrashekara Reddy, Design

and VLSI Implementation of 8 Mb Low Power SRAM in

90nm,European Journal of Scientific Research, Vol. 26,

No. 2, pp. 305-314, 2009.

Keejong Kim, Hamid Mahmoodi,A Low-Power SRAM

Using Bit-Line Charge-Recycling, IEEE Journal Of SolidState Circuits , Vol. 43, No. 2, 2008.

K. Itoh, K. Sasaki, Y. Nakagome,Trends in low-power

RAM circuit technologies, in Dig. Tech. Papers, 1994

Symp. Low Power Electronics, 1994, pp. 8487.

Chang, Y., Lai, F., Yang, C.,Zero-aware symmetric

SRAM cell for reducing cache power in writing zero,

IEEE Trans. VLSI Systems, Vol. 12, No. 8, pp. 827-36,

2004.

J. L. Hennessy, D. A. Patterson,Computer Architecture: A

Quantitative Approach, 2nd ed. San Mateo, CA: Morgan

Kaufmann, 1995.

S. Kang, Y. Leblebici,CMOS Digital Integrated Circuits,

New York, McGraw-Hill,1999.

Sreenivasa Rao Ijjada, B.Ramparamesh, Dr. V.Malleswara

Rao,Reduction of Power-Dissipation in Logic Circuits,

International Journal of Computer Applications, Vol. 24,

No. 6, 2011.

6636

IJRITCC | December 2015, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

You might also like

- IJETR032745Document3 pagesIJETR032745erpublicationNo ratings yet

- Figure 1: 6T CellDocument4 pagesFigure 1: 6T CellShehryarNo ratings yet

- Design and Analysis of 4Kb Sram Array Cell For The Development of Sram ChipDocument8 pagesDesign and Analysis of 4Kb Sram Array Cell For The Development of Sram ChipRohit KumarNo ratings yet

- Reduction of Leakage Power in 8T Sram Cell Using Virtual GroundDocument5 pagesReduction of Leakage Power in 8T Sram Cell Using Virtual GroundSasi Kiran SNo ratings yet

- Designand Analysisof Low Power MTCMOSDocument10 pagesDesignand Analysisof Low Power MTCMOSseshu bradyNo ratings yet

- A Novel Four-Transistor SRAM Cell With Low Dynamic Power ConsumptionDocument5 pagesA Novel Four-Transistor SRAM Cell With Low Dynamic Power ConsumptionDinesh SinghNo ratings yet

- The International Journal of Engineering and Science (The IJES)Document7 pagesThe International Journal of Engineering and Science (The IJES)theijesNo ratings yet

- A Highly Stable 8T SRAM Cell: P.Rama Koteswara Rao and D.Vijaya KumarDocument6 pagesA Highly Stable 8T SRAM Cell: P.Rama Koteswara Rao and D.Vijaya KumarRakeshconclaveNo ratings yet

- SramDocument31 pagesSramParth RamanujNo ratings yet

- Read/Write Stability Improvement of 8T Sram Cell Using Schmitt TriggerDocument6 pagesRead/Write Stability Improvement of 8T Sram Cell Using Schmitt TriggerSasi Kiran SNo ratings yet

- Design and Simulation of Improved Memory Cell For Higher Read Stability, Mr. Kumar KeshamoniDocument7 pagesDesign and Simulation of Improved Memory Cell For Higher Read Stability, Mr. Kumar KeshamoniKumar Goud.KNo ratings yet

- Low Power SRAM for High Speed ApplicationsDocument10 pagesLow Power SRAM for High Speed ApplicationsshwetabhagatNo ratings yet

- 6T SRAM simulationDocument9 pages6T SRAM simulationAzza FaiadNo ratings yet

- IJSTE-SRAMDocument9 pagesIJSTE-SRAMpradeepkarraNo ratings yet

- Low Voltage and Low Power in Sram Read and Write Assist TechniquesDocument9 pagesLow Voltage and Low Power in Sram Read and Write Assist TechniquesIJSTENo ratings yet

- Performance of Low Power SRAM Cells On SNM and Power DissipationDocument5 pagesPerformance of Low Power SRAM Cells On SNM and Power DissipationInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Ultra-Low Leakage Static Random Access Memory DesignDocument10 pagesUltra-Low Leakage Static Random Access Memory DesignIJRES teamNo ratings yet

- Low Power 12T MTCMOS SRAM Based CAMDocument6 pagesLow Power 12T MTCMOS SRAM Based CAMmani_vlsiNo ratings yet

- Analysis of Leakage Reduction Technique On Different SRAM CellsDocument6 pagesAnalysis of Leakage Reduction Technique On Different SRAM Cellssurendiran123No ratings yet

- Analysis of Low Power 6T SRAM Using 45 NM Technology: Shatrughan SinghDocument5 pagesAnalysis of Low Power 6T SRAM Using 45 NM Technology: Shatrughan SinghShruti DasNo ratings yet

- ASIC-System On Chip-VLSI Design - SRAM Cell Design PDFDocument8 pagesASIC-System On Chip-VLSI Design - SRAM Cell Design PDFGowtham SpNo ratings yet

- 6T SRAM SimulationDocument9 pages6T SRAM SimulationAzza FaiadNo ratings yet

- Architecture of Static Random Access Memory Design Using 65nm TechnologyDocument3 pagesArchitecture of Static Random Access Memory Design Using 65nm Technologyanil kasotNo ratings yet

- PXC 3873796Document6 pagesPXC 3873796Sai PraveenNo ratings yet

- ,hrfikadsz NJSDFMV M VZDocument5 pages,hrfikadsz NJSDFMV M VZpalakNo ratings yet

- IJERM0204055Document5 pagesIJERM0204055Vishnu KSNo ratings yet

- SRAM Memory Cell Operation and ArchitectureDocument12 pagesSRAM Memory Cell Operation and ArchitectureAnimisha VermaNo ratings yet

- Static RAMDocument235 pagesStatic RAMAnjireddy ThatiparthyNo ratings yet

- Sram StudyDocument5 pagesSram StudyAjitaSPNo ratings yet

- 9th ICCCNT Paper 169Document7 pages9th ICCCNT Paper 169reeya agrawalNo ratings yet

- VAMSI Kumar SRAMfinalDocument28 pagesVAMSI Kumar SRAMfinalraghuippiliNo ratings yet

- Improved Stability SRAM Design For Low Power ApplicationsDocument5 pagesImproved Stability SRAM Design For Low Power ApplicationsInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- (New Paper On Sram) v39-15Document5 pages(New Paper On Sram) v39-15Pratap SaurabhNo ratings yet

- Low Power Sram Design Using Block PartitioningDocument4 pagesLow Power Sram Design Using Block PartitioningesatjournalsNo ratings yet

- 6Tvs7T Sram ComparisonDocument5 pages6Tvs7T Sram ComparisonPrateek AgrawalNo ratings yet

- Comparative Study of Sense Amplifiers for SRAMDocument4 pagesComparative Study of Sense Amplifiers for SRAMBhagyavant HanchinalNo ratings yet

- 8k Bit Using 6t SramDocument8 pages8k Bit Using 6t SramSwati Navdeep AggarwalNo ratings yet

- Analysis of SRAM Bitcells Using Ultralow-Voltage Schmitt-Trigger Based DesignDocument5 pagesAnalysis of SRAM Bitcells Using Ultralow-Voltage Schmitt-Trigger Based DesignerpublicationNo ratings yet

- Sju SRAM IP For DSPSoC ProjectsDocument50 pagesSju SRAM IP For DSPSoC Projectsraymar2kNo ratings yet

- Bicta2012 Submission 94Document23 pagesBicta2012 Submission 94Gurinder Pal SinghNo ratings yet

- Design of 6T-SRAM Cell Using Dual Threshold Voltage TransistorDocument4 pagesDesign of 6T-SRAM Cell Using Dual Threshold Voltage TransistorAbhijeet KumarNo ratings yet

- Low Power SramDocument6 pagesLow Power SramSuresh BharathNo ratings yet

- 6TSRAM Cell ReportDocument15 pages6TSRAM Cell ReportpalakNo ratings yet

- A Novel Design For Low-Power, High Performance and Space Efficient AddressDocument10 pagesA Novel Design For Low-Power, High Performance and Space Efficient AddressIJRASETPublicationsNo ratings yet

- Pardazeshgar Digital Project English TextDocument10 pagesPardazeshgar Digital Project English Textkazem.khaari77No ratings yet

- SRAMReportDocument42 pagesSRAMReportPremkumar ChandhranNo ratings yet

- SRAM Circuit Design and Operation: Prepared By: Mr. B. H. NagparaDocument49 pagesSRAM Circuit Design and Operation: Prepared By: Mr. B. H. NagparaBharatNo ratings yet

- Manage Enhancing Energy G.sakanaDocument10 pagesManage Enhancing Energy G.sakanaBESTJournalsNo ratings yet

- Static-Noise-Margin Analysis of Modified 6T SRAM Cell During Read OperationDocument5 pagesStatic-Noise-Margin Analysis of Modified 6T SRAM Cell During Read OperationidescitationNo ratings yet

- 8T Paper WTCM FinalDocument11 pages8T Paper WTCM Finaldeberjeet ushamNo ratings yet

- Design Simulation and Analysis of 5T-Sram Cell Using Different FoundriesDocument6 pagesDesign Simulation and Analysis of 5T-Sram Cell Using Different FoundriesPreeti SinghNo ratings yet

- Performance Evaluation of 6T, 7T & 8T SRAM at 180 NM TechnologyDocument7 pagesPerformance Evaluation of 6T, 7T & 8T SRAM at 180 NM TechnologyDr-Sanjeev KashyapNo ratings yet

- Sram Utilization and Power Consumption Analysis For Low Power ApplicationsDocument9 pagesSram Utilization and Power Consumption Analysis For Low Power ApplicationsHarshit RNo ratings yet

- A Proposed Design of Five Transistor CMOS SRAM Cell For High Speed ApplicationsDocument6 pagesA Proposed Design of Five Transistor CMOS SRAM Cell For High Speed ApplicationsShakeel RanaNo ratings yet

- A Novel 8T SRAM Cell With Reduction in Power Using Power Gating TechniqueDocument4 pagesA Novel 8T SRAM Cell With Reduction in Power Using Power Gating TechniqueArvind ChakrapaniNo ratings yet

- Venkata Lakshmi 2021 J. Phys. Conf. Ser. 1804 012185Document8 pagesVenkata Lakshmi 2021 J. Phys. Conf. Ser. 1804 012185seshu bradyNo ratings yet

- Pseudo Differential Multi-Cell Upset Immune Robust SRAM CellDocument20 pagesPseudo Differential Multi-Cell Upset Immune Robust SRAM Cellkazem.khaari77No ratings yet

- Array SubsystemDocument29 pagesArray SubsystemMukesh MakwanaNo ratings yet

- High-Performance D/A-Converters: Application to Digital TransceiversFrom EverandHigh-Performance D/A-Converters: Application to Digital TransceiversNo ratings yet

- Advanced Test Methods for SRAMs: Effective Solutions for Dynamic Fault Detection in Nanoscaled TechnologiesFrom EverandAdvanced Test Methods for SRAMs: Effective Solutions for Dynamic Fault Detection in Nanoscaled TechnologiesNo ratings yet

- Regression Based Comparative Study For Continuous BP Measurement Using Pulse Transit TimeDocument7 pagesRegression Based Comparative Study For Continuous BP Measurement Using Pulse Transit TimeEditor IJRITCCNo ratings yet

- A Review of Wearable Antenna For Body Area Network ApplicationDocument4 pagesA Review of Wearable Antenna For Body Area Network ApplicationEditor IJRITCCNo ratings yet

- Importance of Similarity Measures in Effective Web Information RetrievalDocument5 pagesImportance of Similarity Measures in Effective Web Information RetrievalEditor IJRITCCNo ratings yet

- A Review of Wearable Antenna For Body Area Network ApplicationDocument4 pagesA Review of Wearable Antenna For Body Area Network ApplicationEditor IJRITCCNo ratings yet

- IJRITCC Call For Papers (October 2016 Issue) Citation in Google Scholar Impact Factor 5.837 DOI (CrossRef USA) For Each Paper, IC Value 5.075Document3 pagesIJRITCC Call For Papers (October 2016 Issue) Citation in Google Scholar Impact Factor 5.837 DOI (CrossRef USA) For Each Paper, IC Value 5.075Editor IJRITCCNo ratings yet

- Modeling Heterogeneous Vehicle Routing Problem With Strict Time ScheduleDocument4 pagesModeling Heterogeneous Vehicle Routing Problem With Strict Time ScheduleEditor IJRITCCNo ratings yet

- Performance Analysis of Image Restoration Techniques at Different NoisesDocument4 pagesPerformance Analysis of Image Restoration Techniques at Different NoisesEditor IJRITCCNo ratings yet

- Channel Estimation Techniques Over MIMO-OFDM SystemDocument4 pagesChannel Estimation Techniques Over MIMO-OFDM SystemEditor IJRITCCNo ratings yet

- A Review of 2D &3D Image Steganography TechniquesDocument5 pagesA Review of 2D &3D Image Steganography TechniquesEditor IJRITCCNo ratings yet

- Comparative Analysis of Hybrid Algorithms in Information HidingDocument5 pagesComparative Analysis of Hybrid Algorithms in Information HidingEditor IJRITCCNo ratings yet

- A Review of 2D &3D Image Steganography TechniquesDocument5 pagesA Review of 2D &3D Image Steganography TechniquesEditor IJRITCCNo ratings yet

- Channel Estimation Techniques Over MIMO-OFDM SystemDocument4 pagesChannel Estimation Techniques Over MIMO-OFDM SystemEditor IJRITCCNo ratings yet

- Fuzzy Logic A Soft Computing Approach For E-Learning: A Qualitative ReviewDocument4 pagesFuzzy Logic A Soft Computing Approach For E-Learning: A Qualitative ReviewEditor IJRITCCNo ratings yet

- Diagnosis and Prognosis of Breast Cancer Using Multi Classification AlgorithmDocument5 pagesDiagnosis and Prognosis of Breast Cancer Using Multi Classification AlgorithmEditor IJRITCCNo ratings yet

- A Study of Focused Web Crawling TechniquesDocument4 pagesA Study of Focused Web Crawling TechniquesEditor IJRITCCNo ratings yet

- Efficient Techniques For Image CompressionDocument4 pagesEfficient Techniques For Image CompressionEditor IJRITCCNo ratings yet

- Prediction of Crop Yield Using LS-SVMDocument3 pagesPrediction of Crop Yield Using LS-SVMEditor IJRITCCNo ratings yet

- Network Approach Based Hindi Numeral RecognitionDocument4 pagesNetwork Approach Based Hindi Numeral RecognitionEditor IJRITCCNo ratings yet

- Predictive Analysis For Diabetes Using Tableau: Dhanamma Jagli Siddhanth KotianDocument3 pagesPredictive Analysis For Diabetes Using Tableau: Dhanamma Jagli Siddhanth Kotianrahul sharmaNo ratings yet

- 45 1530697786 - 04-07-2018 PDFDocument5 pages45 1530697786 - 04-07-2018 PDFrahul sharmaNo ratings yet

- 44 1530697679 - 04-07-2018 PDFDocument3 pages44 1530697679 - 04-07-2018 PDFrahul sharmaNo ratings yet

- Itimer: Count On Your TimeDocument4 pagesItimer: Count On Your Timerahul sharmaNo ratings yet

- A Clustering and Associativity Analysis Based Probabilistic Method For Web Page PredictionDocument5 pagesA Clustering and Associativity Analysis Based Probabilistic Method For Web Page Predictionrahul sharmaNo ratings yet

- Hybrid Algorithm For Enhanced Watermark Security With Robust DetectionDocument5 pagesHybrid Algorithm For Enhanced Watermark Security With Robust Detectionrahul sharmaNo ratings yet

- Safeguarding Data Privacy by Placing Multi-Level Access RestrictionsDocument3 pagesSafeguarding Data Privacy by Placing Multi-Level Access Restrictionsrahul sharmaNo ratings yet

- A Content Based Region Separation and Analysis Approach For Sar Image ClassificationDocument7 pagesA Content Based Region Separation and Analysis Approach For Sar Image Classificationrahul sharmaNo ratings yet

- Vehicular Ad-Hoc Network, Its Security and Issues: A ReviewDocument4 pagesVehicular Ad-Hoc Network, Its Security and Issues: A Reviewrahul sharmaNo ratings yet

- 41 1530347319 - 30-06-2018 PDFDocument9 pages41 1530347319 - 30-06-2018 PDFrahul sharmaNo ratings yet

- Image Restoration Techniques Using Fusion To Remove Motion BlurDocument5 pagesImage Restoration Techniques Using Fusion To Remove Motion Blurrahul sharmaNo ratings yet

- Space Complexity Analysis of Rsa and Ecc Based Security Algorithms in Cloud DataDocument12 pagesSpace Complexity Analysis of Rsa and Ecc Based Security Algorithms in Cloud Datarahul sharmaNo ratings yet

- LegoDocument30 pagesLegomzai2003No ratings yet

- White Box Testing Techniques: Ratna SanyalDocument23 pagesWhite Box Testing Techniques: Ratna SanyalYogesh MundhraNo ratings yet

- Ball Valves Pentair Valves and ControlsDocument16 pagesBall Valves Pentair Valves and ControlsABDUL KADHARNo ratings yet

- Iphoneos 31Document159 pagesIphoneos 31Ivan VeBoNo ratings yet

- Ailunce HD1 Software ManualDocument33 pagesAilunce HD1 Software ManualMarc LaBarberaNo ratings yet

- Audi Q5: First Generation (Typ 8R 2008-2017)Document19 pagesAudi Q5: First Generation (Typ 8R 2008-2017)roberto100% (1)

- Mil STD 2154Document44 pagesMil STD 2154Muh SubhanNo ratings yet

- Assignment - Final TestDocument3 pagesAssignment - Final TestbahilashNo ratings yet

- Bula Defense M14 Operator's ManualDocument32 pagesBula Defense M14 Operator's ManualmeNo ratings yet

- Marshall Stability Test AnalysisDocument5 pagesMarshall Stability Test AnalysisZick Zickry50% (2)

- Process Financial Transactions and Extract Interim Reports - 025735Document37 pagesProcess Financial Transactions and Extract Interim Reports - 025735l2557206No ratings yet

- Indian Standard: Pla Ing and Design of Drainage IN Irrigation Projects - GuidelinesDocument7 pagesIndian Standard: Pla Ing and Design of Drainage IN Irrigation Projects - GuidelinesGolak PattanaikNo ratings yet

- Applied Statics and Strength of Materials 6th Edition Ebook PDFDocument61 pagesApplied Statics and Strength of Materials 6th Edition Ebook PDFteri.sanborn87695% (44)

- British Universal Steel Columns and Beams PropertiesDocument6 pagesBritish Universal Steel Columns and Beams PropertiesjagvishaNo ratings yet

- Physics Derived Units and Unit Prefixes Derived UnitDocument15 pagesPhysics Derived Units and Unit Prefixes Derived UnitJohnRenzoMolinarNo ratings yet

- Paper SizeDocument22 pagesPaper SizeAlfred Jimmy UchaNo ratings yet

- The Dominant Regime Method - Hinloopen and Nijkamp PDFDocument20 pagesThe Dominant Regime Method - Hinloopen and Nijkamp PDFLuiz Felipe GuaycuruNo ratings yet

- Joining Instruction 4 Years 22 23Document11 pagesJoining Instruction 4 Years 22 23Salmini ShamteNo ratings yet

- PEDs and InterferenceDocument28 pagesPEDs and Interferencezakool21No ratings yet

- IELTS Speaking Q&ADocument17 pagesIELTS Speaking Q&ABDApp Star100% (1)

- Real Estate Broker ReviewerREBLEXDocument124 pagesReal Estate Broker ReviewerREBLEXMar100% (4)

- CENG 5503 Intro to Steel & Timber StructuresDocument37 pagesCENG 5503 Intro to Steel & Timber StructuresBern Moses DuachNo ratings yet

- Dep 32.32.00.11-Custody Transfer Measurement Systems For LiquidDocument69 pagesDep 32.32.00.11-Custody Transfer Measurement Systems For LiquidDAYONo ratings yet

- Special Power of Attorney: Benedict Joseph M. CruzDocument1 pageSpecial Power of Attorney: Benedict Joseph M. CruzJson GalvezNo ratings yet

- Listening Exercise 1Document1 pageListening Exercise 1Ma. Luiggie Teresita PerezNo ratings yet

- Manual WinMASW EngDocument357 pagesManual WinMASW EngRolanditto QuuisppeNo ratings yet

- Galaxy Owners Manual Dx98vhpDocument10 pagesGalaxy Owners Manual Dx98vhpbellscbNo ratings yet

- Kaydon Dry Gas SealDocument12 pagesKaydon Dry Gas Sealxsi666No ratings yet

- Inventory ControlDocument26 pagesInventory ControlhajarawNo ratings yet

- DOE Tank Safety Workshop Presentation on Hydrogen Tank TestingDocument36 pagesDOE Tank Safety Workshop Presentation on Hydrogen Tank TestingAlex AbakumovNo ratings yet