Professional Documents

Culture Documents

Tema 8 - Introduccion A Los Circuitos Digitales

Uploaded by

Verenisse Mishel CalleOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Tema 8 - Introduccion A Los Circuitos Digitales

Uploaded by

Verenisse Mishel CalleCopyright:

Available Formats

Captulo 3.

CIRCUITOS DIGITALES

TEMA S.

INTRODUCCIN A LOS CIRCUITOS

DIGITALES.

En general, los sistemas que tratan la informacin de forma digital emplean

variables elctricas que representan dicha informacin en forma bivalente. Los circuitos

digitales han de responder a seales que tengan dos valores, es decir, que sean de

naturaleza binaria, y deben producir seales de salida apropiadamente cuantificadas.

La informacin se puede representar en principio por unos niveles de tensin

discretos, pero debido a las tolerancias de los componentes y fuentes de alimentacin,

al ruido, distorsin, etc., debe representarse en la prctica por intervalos o rangos

de tensin para definir los dos estados lgicos.

En lgica positiva los valores de tensin del estado alto H (high) se asocian a

nivel 1 lgico, y los del estado bajo L (low) a nivel O lgico. Entre las dos regiones L y

H se sita una regin prohibida o no definida, como puede verse en la Figura 8.1.

Tensin(V)

VHmx

Estado alto "H"

VHmn

Regin prohibida

VLmx

Estado bajo "L"

VLmn

Fig. 8.1. Niveles de tensin en un circuito digital.

Lo importante de cualquier circuito integrado digital es asegurar que cumple su

funcin lgica y que su salida, para seales de entrada dentro de los intervalos

permitidos, no estar en la zona prohibida, salvo en las transiciones de un estado a otro.

Los circuitos integrados digitales han evolucionado en familias lgicas o tecnologas

digitales, cada una con sus ventajas e inconvenientes. Los miembros de una misma

familia son diseados para ser compatibles entre s, mientras que si se interconectan

dos circuitos de familias distintas puede ser necesario un circuito de acoplamiento o

interfaz.

APUNTES DE TEORA DE TE (2010/2011)

BRGAINS, CASTRO, IGLESIA, LAMAS

PG.

2 DE 8

TEMA OS: INTRODUCCIN A LOS CIRC. DIGITALES

La eleccin de una familia a utilizar en una aplicacin particular depende de

factores tales como velocidad, coste, inmunidad al ruido, disipacin de potencia,

disponibilidad de funciones lgicas, etc.

Los circuitos integrados de aplicacin especfica (ASIC, application-specific

integrated circuit), contienen en un nico chip la mayor parte de los circuitos

analgicos y digitales para una determinada aplicacin, as como sus interconexiones.

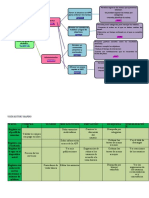

Los circuitos integrados digitales se pueden clasificar en funcin de su nivel de

integracin como se muestra en la siguiente tabla:

Nivel de integracin

SSJ (Integracin a pequea escala)

MSJ (Integracin a media escala)

LSJ (Integracin a gran escala)

VLSJ (Integracin a muy gran escala)

ULSJ (Integracin a ultra gran escala)

GLSJ (Integracin a giga gran escala)

No de puertas

Hasta 10

10 a 100

100 a 10.000

10.000 a 100.000

100.000 a 1.000.000

Ms de 1.000.000

Las principales tecnologas de circuitos integrados digitales en uso son:

a) CMOS. Es la tecnologa dominante en el diseo de circuitos integrados

digitales, por su baja disipacin de potencia, por su mayor nivel de integracin

(reducido tamao de componentes) y por la posibilidad de usar almacenamiento

de carga (elevada impedancia de entrada), aspectos que no pueden lograrse con

tecnologas bipolares.

b) Bipolar. Dos familias de circuitos integrados estn en uso en la actualidad: TTL

y ECL. La lgica transistor-transistor (TTL) fue la tecnologa dominante en los

aos 70 y 80, y se sigue utilizando en el diseo de sistemas digitales que

ensamblan bloques de bajo y medio nivel de integracin. La lgica de

emisores acoplados (ECL) utiliza transistores bipolares en activa, lo que le

permite una velocidad de operacin ms elevada, pero a costa de una disipacin

de potencia mayor.

c) BICMOS. Combina las altas velocidades de operacin de los BJT (debido a su

transconductancia inherentemente ms alta y elevada corriente de salida) y las

excelentes caractersticas de CMOS.

S.1CARACTERSTICAS GENERALES DE LOS CIRCUITOS DIGITALES.

APUNTES DE TEORA DE TE

(2010/2011)

BRGAINS, CASTRO, IGLESIA, LAMAS

PG.

3 DE 8

TEMA OS: INTRODUCCIN A LOS CIRC. DIGITALES

Vamos a estudiar las familias lgicas desde un punto de vista comparativo, para lo

cual vamos a definir las caractersticas o parmetros elctricos que nos van a servir de

comparacin. Esta caracterizacin se realiza a partir de medidas sobre los terminales

externos de una puerta bsica de cada familia, normalmente una puerta inversora, que se

recogen en las hojas caractersticas (datasheets) que proporciona cada fabricante.

APUNTES DE TEORA DE TE

(2010/2011)

BRGAINS, CASTRO, IGLESIA, LAMAS

S.1.1

Caracterstica de transferencia.

La caracterstica de transferencia del inversor lgico es la representacin grfica

de la tensin de salida Vo en funcin de la tensin de entrada Vi. Fijadas la tensin de

alimentacin, la temperatura ambiente y el nmero de puertas del mismo tipo

conectadas a la salida de la puerta, la relacin tensin de entrada-tensin de salida Vo=

f(Vi) ser nica, salvo por las tolerancias derivadas del proceso de fabricacin.

Considerando el caso de un inversor, existe un margen de entradas permitido

VJL correspondiente a nivel bajo (L) para el cual se garantiza que la salida es nivel alto

(H). Anlogamente, existe un margen de entradas permitido VJH correspondiente a nivel

alto

(H) para el cual la salida es nivel bajo (L). Sin embargo, debido a la dispersin de

caractersticas, habr toda una familia de posibles caractersticas de transferencia,

representada por sus envolventes (grfica a puntos). Para simplificar, lo que se hace es

considerar una nica curva de transferencia (grfica a trazo continuo) para toda la

familia. Esta curva se hace coincidir con la peor de las curvas de transferencia para cada

uno de los niveles alto y bajo.

Fig. 8.2. Caracterstica de transferencia del inversor lgico.

La caracterstica de transferencia tiene dos transiciones, para VJLmx-VOHmn y VJHmnVOLmx, definidas tericamente para los puntos en los que la pendiente de la

caracterstica de transferencia es -1 (dVoldVi= -1). En los circuitos digitales se

especifican siempre:

VILmx o tensin mxima de entrada a nivel bajo. Es la tensin mxima que puede

aplicarse al terminal de entrada de una puerta que an puede reconocerse como

nivel bajo (L).

VIHmn o tensin mnima de entrada a nivel alto. Es la tensin mnima que puede

aplicarse al terminal de entrada de una puerta que an puede reconocerse como

nivel alto (H).

VOLmx o tensin mxima de salida a nivel bajo. Es la tensin mxima de salida que

establecer la puerta a nivel bajo (L) para una corriente de salida especificada.

VOHmn o tensin mnima de salida a nivel alto. Es la tensin mnima de salida que

establecer la puerta a nivel alto (H) para una corriente de salida especificada

y mnimo valor de la tensin de alimentacin VCC.

Compatibilidad de tensiones: La puerta excitadora proporciona las tensiones de salida

Vo y la puerta receptora las tensiones de entrada Vi (ver Figura 8.3). Debe cumplirse:

VOLmx

VILmx VOHmn

VIHmn

Fig. 8.3. Compatibilidad de tensiones.

S.1.2

Caractersticas de entrada y salida.

Para cada estado (L o H) es necesario conocer las corrientes de entrada y de salida

de la puerta lgica. Por convenio, se toman las corrientes entrantes como positivas y las

corrientes salientes como negativas.

Para las entradas:

IIL o corriente en una entrada puesta a nivel bajo (L). Es la corriente que fluye hacia

el terminal de entrada cuando se le aplica una tensin especificada de nivel bajo.

IIH o corriente en una entrada puesta a nivel alto (H). Es la corriente que fluye

hacia el terminal de entrada cuando se le aplica una tensin especificada de

nivel alto.

Para las salidas:

IOLmx o corriente mxima de salida a nivel bajo (L). Es la corriente mxima que

puede fluir hacia el terminal de salida cuando se encuentra a nivel bajo.

IOHmx o corriente mxima de salida a nivel alto (H). Es la corriente mxima que

puede fluir hacia el terminal de salida cuando se encuentra a nivel alto.

Compatibilidad de corrientes: La puerta excitadora proporciona las corrientes de

salida Io y la puerta receptora las corrientes de entrada Ii (ver Figura 8.4). Debe

cumplirse:

IIOLmxI IIILmxI

IIOHmxI IIIHmxl

Fig. 8.4. Compatibilidad de corrientes.

Fan-out: Para medir la capacidad de excitacin, cargabilidad o factor de carga de una

puerta se usa el fan-out, que representa el mximo nmero N de puertas que una

determinada puede excitar del mismo tipo, permaneciendo los niveles en los mrgenes

garantizados.

OHmx

N = mn H

l J JHmx

J OLmx

J JLmx J

Otro factor que limita el fan-out de una puerta es la capacidad CL que presentan las

entradas y los cableados a otras puertas conectadas a su salida. Dado que la corriente

en una capacidad viene dada por i= CLdvldt, las transiciones rpidas de tensin

requieren grandes corrientes de excitacin. Por tanto, en aquellos sistemas donde es

deseable una rpida conmutacin, es necesario limitar el fan-out de tal modo que la

corriente requerida permanezca dentro de los lmites de la puerta excitadora.

S.1.3

Inmunidad al ruido (Mrgenes de ruido).

En la prctica, el ruido est siempre presente en cualquier sistema fsico. Puede ser

generado internamente o captado del exterior por acoplamiento inductivo (campo

magntico) o capacitivo (campo elctrico). Se entiende por ruido cualquier perturbacin

no voluntaria que puede causar un cambio indeseado en el nivel de salida de un circuito

integrado digital.

Para medir la cantidad de ruido admisible a la entrada de un circuito digital o

inmunidad al ruido se utilizan los mrgenes de ruido, que se definen como las

variaciones de tensin mximas admitidas a la entrada de un circuito integrado digital

sin que la salida cambie de estado.

Fig. 8.5. Mrgenes de ruido.

Margen de ruido para el nivel bajo: NML= VNL= VJLmx - VOLmx.

Margen de ruido para el nivel alto: NMH= VNH= VOHmn - VJHmn.

S.1.4

Disipacin de potencia (Consumo).

La disipacin de potencia esttica o en reposo (con niveles lgicos constantes)

se define bajo condiciones de trabajo de un 50% o valor medio de las potencias

disipadas en la puerta bsica en los estados bajo y alto, es decir:

PD =

PD (L) + PD (H )

.

2

Cuando una puerta est en conmutacin (supongamos por ejemplo que su salida

cambia de estado con una frecuencia f) debe considerarse adems la disipacin de

potencia dinmica necesaria para la carga y descarga de la capacidad CL a la salida de

la misma. Dado que dicha capacidad se carga y descarga completamente en cada ciclo

en un valor Q= CLVcc, la energa que se suministra desde la fuente de alimentacin es

2

W= Cc LVc , y la potencia disipada dinmica es:

Pd =

fC LVcc .

La disipacin de potencia dinmica es un problema en circuitos de computadores

y de comunicaciones de alta velocidad, donde se trabaja con frecuencias de

gigahercios.

Para reducir la disipacin de potencia dinmica se debe mantener una baja

capacidad de carga CL y reducir la amplitud de la tensin de alimentacin Vcc.

La potencia total disipada por la puerta, que ha de suministrar la fuente de

alimentacin Vcc, es la suma de la potencia disipada esttica y la dinmica.

S.1.5

Velocidad de conmutacin.

Una puerta inversora, debido a sus capacidades internas propias y a la capacidad

que carga su salida, no responde instantneamente a las transiciones de seal en su

entrada. Esto lleva a una limitacin en su velocidad de conmutacin que se expresa de

dos formas:

a. Retardo de propagacin.

Se define el retardo de propagacin tp o tpd como el tiempo que tarda una seal

en propagarse desde la entrada a la salida de una puerta bsica, o tambin, como el

tiempo medio transcurrido desde que se produce una transicin a la entrada de la puerta

hasta que se refleja en su salida.

En la figura 8.6 se muestra el pulso de entrada en un inversor lgico y la salida

resultante. Observe que el pulso de entrada cambia de estado de forma gradual. La

seal de entrada es suministrada por la salida de un circuito que debe cargar o

descargar la capacidad de entrada del inversor, por lo que en la prctica no se

producen cambios instantneos de la tensin de entrada.

Para la medida de los retardos de propagacin se toma como referencia el

instante del paso de las seales de entrada y salida por el 50% o punto medio de la

transicin entre niveles, es decir, cuando las seales Vi y Vo pasan por: (VOL+VOH)/2.

Obsrvese que en la seal de entrada Vi se indican los niveles VOL y VOH que

corresponden a los niveles que define la puerta excitadora conectada a la entrada Vi.

Vi

100%

Vi

Vo

VOH

50%

0%

VOL

VOL

t

Vo

100%

VOH

VOH

50%

VOL

0%

tpLH

tpHL

Fig. 8.6. Retardos de propagacin.

Por lo tanto, se definen los siguientes tiempos:

tpHL es el tiempo que transcurre desde que la entrada pasa por el 50% hasta que

la salida pasa por el 50% en una transicin de nivel alto a nivel bajo en la salida.

tpLH es el tiempo desde que la entrada pasa por el 50% hasta que la salida pasa

por el 50% en una transicin de nivel bajo a nivel alto en la salida.

As, el retardo de propagacin medio se define como:

+

t

t pHL= p

t pLH

b. Frecuencia mxima.

Otra forma de expresar la velocidad de conmutacin es mediante la frecuencia

mxima fmx de utilizacin de un biestable realizado con la familia lgica en estudio.

De forma aproximada se cumple:

fmx 1/4tp.

S.1.6

Producto retardo-potencia.

El producto retardo potencia DP= Pdtp se mide en pJ y representa la energa que

consume la puerta en cada ciclo a frecuencia mxima. Se usa para comparar familias

digitales como un factor de calidad: cuanto menor es el producto, mejor es la calidad de

la familia lgica.

S.1.7

Flexibilidad lgica.

Es una medida de la capacidad o versatilidad de una familia lgica. Se concreta

en la posibilidad de cableado lgico, es decir, unir dos o ms salidas para realizar una

nueva funcin, capacidad de excitacin, variedad en las salidas, compatibilidad con

otras tecnologas, variedad de bloques funcionales, etc.

You might also like

- Accidentes NuclearesDocument8 pagesAccidentes NuclearesVerenisse Mishel CalleNo ratings yet

- Recursos NaturalesDocument38 pagesRecursos NaturalesVerenisse Mishel CalleNo ratings yet

- Tablas Normal Chi T F PDFDocument6 pagesTablas Normal Chi T F PDFAnonymous WIDbfSVENo ratings yet

- 01 Intro Cods AritDocument76 pages01 Intro Cods AritJavier SacánNo ratings yet

- 06 Control PIDDocument14 pages06 Control PIDVerenisse Mishel CalleNo ratings yet

- Mineria Datos Arte PDFDocument45 pagesMineria Datos Arte PDFJose Angel Garcia Garcia100% (1)

- Sistema Mecatrónico XK 335BDocument4 pagesSistema Mecatrónico XK 335BVerenisse Mishel Calle0% (1)

- Presentación - Conceptos Básicos.41132532Document58 pagesPresentación - Conceptos Básicos.41132532Victoria Loza BastoNo ratings yet

- Asma y crisis asmática: causas, manifestaciones y tratamientoDocument15 pagesAsma y crisis asmática: causas, manifestaciones y tratamientoVerenisse Mishel CalleNo ratings yet

- Componentes de Los Sistemas de ControlDocument5 pagesComponentes de Los Sistemas de ControlVerenisse Mishel CalleNo ratings yet

- Ponenteselectronicos (4eso)Document35 pagesPonenteselectronicos (4eso)Pablo LópezNo ratings yet

- Marcapasos EnfermeriaDocument40 pagesMarcapasos EnfermeriaVerenisse Mishel Calle100% (1)

- Desviación de Fase, El Índice de Modulación y La Desviación de FrecuenciaDocument12 pagesDesviación de Fase, El Índice de Modulación y La Desviación de Frecuenciarudekane236No ratings yet

- Desviación de Fase, El Índice de Modulación y La Desviación de FrecuenciaDocument12 pagesDesviación de Fase, El Índice de Modulación y La Desviación de Frecuenciarudekane236No ratings yet

- Transcripción de Rotación MatlabDocument19 pagesTranscripción de Rotación MatlabVerenisse Mishel CalleNo ratings yet

- Ley de OhmDocument3 pagesLey de OhmVerenisse Mishel CalleNo ratings yet

- Circuitos Integrados DefenzaDocument12 pagesCircuitos Integrados DefenzaVerenisse Mishel CalleNo ratings yet

- Coeficiente de Dilatacion LinealDocument5 pagesCoeficiente de Dilatacion LinealVerenisse Mishel CalleNo ratings yet

- Balanza de JollyDocument4 pagesBalanza de JollyVerenisse Mishel CalleNo ratings yet

- Tabla de Resistencias Comerciales PDFDocument1 pageTabla de Resistencias Comerciales PDFRick GrimesNo ratings yet

- Técnicas de ConteoDocument6 pagesTécnicas de ConteoAdriana LópezNo ratings yet

- 035 - 044 - Cap2 - Motor de Corriente ContinuaDocument10 pages035 - 044 - Cap2 - Motor de Corriente ContinuaMoises BarraNo ratings yet

- Guia de Actividades y Rúbrica de Evaluación - Unidad 1 - Fase 2 - Contextualizacion Del ProDocument9 pagesGuia de Actividades y Rúbrica de Evaluación - Unidad 1 - Fase 2 - Contextualizacion Del Projhon buriticaNo ratings yet

- Instructivo Renovacion Licencia 1Document6 pagesInstructivo Renovacion Licencia 1Esteban VediaNo ratings yet

- 13 Cert. Garantia Masilla Plástica AnypsaDocument1 page13 Cert. Garantia Masilla Plástica AnypsaCarlosRobertoCamposJara100% (1)

- dv5 2247laDocument2 pagesdv5 2247laYulian BastoNo ratings yet

- Sistemas Eléctricos de Potencia: Ingeniería en ElectromecánicaDocument7 pagesSistemas Eléctricos de Potencia: Ingeniería en ElectromecánicaAna MarreroNo ratings yet

- 51 Presentacioin de Caso PracticoDocument3 pages51 Presentacioin de Caso PracticojohannaNo ratings yet

- Estoque - Diário 01.02.2023Document1 pageEstoque - Diário 01.02.2023Guilherme santanaNo ratings yet

- Impact Mapping, User History, Flujograma, Diseño AppDocument6 pagesImpact Mapping, User History, Flujograma, Diseño AppSantisteban Callacna FjNo ratings yet

- Trabajo #02 Dinamica Grupo N°03 Yugo EscosesDocument12 pagesTrabajo #02 Dinamica Grupo N°03 Yugo EscosesLiz RiveraNo ratings yet

- Sectorizacion en Redes de Agua PotableDocument109 pagesSectorizacion en Redes de Agua PotableMiguel Hernández100% (1)

- Lineamientos de Seguridad para ConductoresDocument7 pagesLineamientos de Seguridad para Conductoresayudante.transportes.alicorpNo ratings yet

- Tú Has Venido A La Orilla (Pescador de Hombres) - Canciones ReligiosasDocument1 pageTú Has Venido A La Orilla (Pescador de Hombres) - Canciones ReligiosasElyzabeth GaticaNo ratings yet

- Estrategias de Calculo Mental 4 Basico PDFDocument6 pagesEstrategias de Calculo Mental 4 Basico PDFWendy AlvarezNo ratings yet

- Trabajos Final de La EmpresaDocument9 pagesTrabajos Final de La EmpresaDeivisOroscoAlarconIpanaqueNo ratings yet

- Envío-Honduras Ebook - Año 13 #47Document68 pagesEnvío-Honduras Ebook - Año 13 #47Jared MelendezNo ratings yet

- Unidad 01 Introducción A La Higiene OcupacionalDocument27 pagesUnidad 01 Introducción A La Higiene OcupacionalJoel Hurtado MarchenaNo ratings yet

- Estudio saneamiento MelipeucoDocument21 pagesEstudio saneamiento MelipeucoPatricio Olivares OlivaresNo ratings yet

- Bitacora Ricardo RomanDocument12 pagesBitacora Ricardo RomanEl Tío Jugoso JuegaNo ratings yet

- Hoja de Vida JavierDocument2 pagesHoja de Vida JavierSilvia FigueroaNo ratings yet

- Archivo AdministrativoDocument7 pagesArchivo AdministrativoAdriana RonderosNo ratings yet

- Secuencia de Tecnol 7mo Grado Seño Lore OlmosDocument40 pagesSecuencia de Tecnol 7mo Grado Seño Lore OlmosGonzy Diaz Páez100% (1)

- Certi EzraDocument4 pagesCerti EzraJeremías Lutin CastilloNo ratings yet

- Tarea Semana 5 ServiciosDocument2 pagesTarea Semana 5 Serviciosclaudine.arriaza2151No ratings yet

- Longitud de EmpalmeDocument30 pagesLongitud de EmpalmeSebastián BourguignonNo ratings yet

- Normatividad vigente SST ColombiaDocument2 pagesNormatividad vigente SST ColombiaYOICESMID TORO ZULUAGANo ratings yet

- Preparacion de CianuroDocument12 pagesPreparacion de CianuroAldo Quispe100% (1)

- Corrupcion en La Adquisicion y Contratacion Del Estado PeruanoDocument106 pagesCorrupcion en La Adquisicion y Contratacion Del Estado PeruanoWilder Resurreccion EnriquezNo ratings yet

- Finiquito trabajador aluminioDocument2 pagesFiniquito trabajador aluminioCristopher Israel Espinoza MezaNo ratings yet