Professional Documents

Culture Documents

p2 Contadores

Uploaded by

BryanGutierrezOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

p2 Contadores

Uploaded by

BryanGutierrezCopyright:

Available Formats

CIRCUITOS ELECTRONICOS DIGITALES, ESCUELA POLITCNICA SUPERIOR

UNIVERSIDAD AUTNOMA DE MADRID

Prctica 2: Contadores

INTRODUCCIN

En esta prctica se introducir el concepto de diseo de contadores sncronos. La prctica durar

dos semanas; la primera (Parte A) se dedica al diseo de una serie de circuitos en el entorno Xilinx

ISE y la segunda (Parte B) al montaje hardware de los mismos. Cada semana vale hasta un

mximo de 10 puntos.

DESCRIPCIN DEL CONTADOR 74163

Principales Caractersticas:

Contador binario de 4 bits (cuenta de QDQCQBQA = 0000 a QDQCQBQA = 1111 y vuelve a

repetir desde 0000)

Tanto la carga (load) como el reset son sncronos. Es decir, actan cuando estn activas y

a la vez llega un flanco de reloj.

Con cada flanco de subida en CLK, el valor de las salidas QD..A se incrementa en una

unidad, donde QD es el bit ms significativo.

Si el flanco de subida de CLK ocurre cuando hay un cero en LOAD (entrada activa a nivel

bajo), las salidas QDQCQBQA se cargan con el valor que haya en las entradas DCBA (carga

sncrona).

Si el flanco subida de CLK se produce cuando hay un cero en CLR, entonces las salidas

QDQCQBQA se ponen a cero (reset sncrono).

La salida RCO (ripple carry out) se pone a 1 cuando todas las salidas QDQCQBQA estn a

uno. RCO se suele llamar a veces TC (terminal count).

El circuito tiene 2 clock enables llamados ENT y ENP. La cuenta slo se realiza cuando hay

un 1 en ambas entradas ENP y ENT.

RCO, ENT y ENP se utilizan cuando se ponen varios 74163 en cascada para aumentar el

nmero de bits de la cuenta: la salida RCO del primero (menos significativo) se conecta con

las entradas ENP y ENT del segundo, y as sucesivamente.

El pinout del 74xx163 (Motorola) es:

Simulacin: El circuito equivalente del 74HC163 es el 74_163

El 74HC163 existe como soft-macro bajo el nombre X74_163, para las familias Xilinx XC9500 y

Coolrunner.

No hace falta dibujar un 74HC163: ya est dibujado. Ud. slo debe utilizarlo.

Deber trabajar en el ISE con las familias Xilinx XC9500 o Coolrunner. En el resto de las

familias no existe este componente.

Cuando ubique el componente X74_163 en la hoja, puede pulsar el botn derecho del ratn

y seleccionar Push Into Symbol. Se encontrar con un nuevo esquemtico, donde est el

dibujo con puertas bsicas (llamadas primitivas) del 74xx163, probablemente copiado de un

manual original de TTLs.

Observe que puede modificar este tipo de hojas a base de primitivas para hacer un

contador diferente.

En la figura adjunta se muestra la hoja de datos del X74_163, que puede hallarla en el

catlogo de componentes Library Guide de Xilinx (se accede al mismo a travs del Help del

ISE, en On-Line Documentation).

EJERCICIO 1 Primera semana (3 puntos):

En todos los casos utilice la siguiente nomenclatura:

Nombre de la hoja con el sch: se debe llamar pr2ej1. No ponga ej1, juan1, etc.

Poner en el circuito dos conectores de entrada y uno de salida, llamados:

CLR : clear o reset (entrada)

CLK : reloj de entrada (entrada)

Z : salida del circuito (seal RCO del contador, salida)

Las seales de DCBA, Load, ENT y ENP sern controladas o fijadas a Vcc o GND

internamente.

Turno Lab Martes: Utilizando un 74_163 disear y simular un divisor x3 de la frecuencia

de reloj de entrada. Las entradas DCBA deben fijarse a VCC o GND.

Turno Lab Jueves: Utilizando un 74_163 disear y simular un divisor x5 de la frecuencia

de reloj de entrada.

Turno Lab Viernes Maana: Utilizando un 74_163 disear y simular un divisor x7 de la

frecuencia de reloj de entrada.

Turno Lab Viernes Tarde: Utilizando un 74_163 disear y simular un divisor x8 de la

frecuencia de reloj de entrada.

EJERCICIO 2 Primera semana: Sntesis de Contadores (7 puntos):

Introduccin

Utilice la siguiente nomenclatura:

Nombre de la hoja con el sch: pr2ej2

CLK : reloj de entrada

RST : Seal de reset o clear (Use en este caso RST y no CLR como en el ejercicio

anterior)

Z0 : bit 0 de la salida del contador (LSB) No confunda 0 con O.

Z1 : bit 1 de la salida del contador

Z2 : bit 2 de la salida del contador

Z3 : bit 3 de la salida del contador (MSB)

Seleccione la familia Spartan 3E (no la Spantan 3 - a secas - sin la E) al crear el Project.

Se pide realizar el circuito con puertas y FF tipo D con clear, NO DEBE UTILIZAR EN ESTE

EJERCICIO EL 74_163. Llegue al Lab con un plano hecho en papel con todos los mapas K

resueltos.

Utilice el FF tipo D con clear que se llama FDR (flip-flop D con reset).

Antes de simular ejecute el comando Check schematics del men Tools. Si hay errores no

funcionar la simulacin.

Enunciado comn para todo el Laboratorio de CED y particular para cada estudiante:

Sintetizar "con lpiz y papel" y simular un contador cclico que partiendo de 0000 pase en BCD por

los 4 ltimos nmeros de su DNI. Por ejemplo: si Ud. tiene DNI 13404239, entonces el contador

debe hacer: 0000-1001-011-0010-0100-1001-011-0010-0100-1001-

Observe que:

El contador parte de 0000 al inicializarse y despus no vuelve a pasar por dicho

valor.

Si su DNI contiene un cero entre los 4 ltimos dgitos, comience por dicho cero y

as aprovecha la inicializacin.

Si su DNI tiene dgitos repetidos su circuito se complica: debe agregar uno

o ms FF para distinguir los dgitos que son iguales. Si tiene ms de 2

dgitos repetidos consulte a su profesor de laboratorio.

NOTA:

No se pide en este ejercicio la solucin alternativa [contador tipo

163 + codificador]. Esa arquitectura se desarrolla en la Prctica 4.

En el entorno Xilinx, la clula soft-macro CB4CLE (contador binario 4 bit con clear

load y enable) tambin es un circuito equivalente al 74_163.

EJERCICIO 1 HARDWARE Segunda semana (10 puntos):

Antes de comenzar la prctica verifique con un cable largo que los LEDs, la

alimentacin de 5 volts y los interruptores de su equipo funcionan correctamente.

Turno Lab Martes: Utilizando el contador binario 74HC163 y puertas adicionales

realizar el montaje HW de un contador de 4 bits que slo pase por los nmeros del

0 al 9 cclicamente. Utilice un interruptor del laboratorio como entrada de reloj y los

LEDs del entrenador para visualizar la salida. Recuerde que puede utilizar el

multiplexor para realizar funciones lgicas.

Turno Lab Jueves: Utilizando el contador binario 74HC163 y puertas adicionales

realizar el montaje HW de un contador de 4 bits que slo pase por los nmeros de

0 al 12 cclicamente. Utilice un interruptor del laboratorio como entrada de reloj y

los LEDs del entrenador para visualizar la salida. Recuerde que puede utilizar el

multiplexor para realizar funciones lgicas.

Turno Lab Viernes Maana: Realizar el montaje HW del divisor de frecuencia x7

diseado en la semana anterior. Utilice un interruptor del laboratorio como entrada

de reloj y los LEDs del entrenador para visualizar la salida. Recuerde que puede

utilizar el multiplexor para realizar funciones lgicas.

Turno Lab Viernes Tarde: Realizar el montaje HW del divisor de frecuencia x8

diseado en la semana anterior. Utilice un interruptor del laboratorio como entrada

de reloj y los LEDs del entrenador para visualizar la salida. Recuerde que puede

utilizar el multiplexor para realizar funciones lgicas.

HOJAS DE DATOS

En http://focus-webapps.ti.com/general/docs/sitesearch/advancedsearch.tsp

y en http://www.ii.uam.es/~cedeps/ced-comp.htm

puede encontrar las hojas de datos de los componentes

El 74xx163 corresponde a las numeraciones: 74163 (Motorola) (Texas Instruments) y 7447

(Motorola) (Texas Instruments)

Concordancia entre la nomenclatura de pines de las versiones del 74xx163 de Motorola y Texas

Instruments:

Texas Instruments

Xilinx

CLR

CP

CLK

CK

P3..0

D..A

D..A

CEP

ENP

ENP

PE

LOAD

LOAD

CET

ENT

ENT

Q3..0

QD..A

QD..A

TC

RCO

RCO

Motorola

E. Boemo, S. Lpez-Buedo, Marzo 2006. Revisada Febrero 2015

You might also like

- Aprender Arduino, prototipado y programación avanzada con 100 ejerciciosFrom EverandAprender Arduino, prototipado y programación avanzada con 100 ejerciciosRating: 5 out of 5 stars5/5 (5)

- DECODIFICADOR BINARIO A DECIMALDocument5 pagesDECODIFICADOR BINARIO A DECIMALVin RiioNo ratings yet

- FisicaaaDocument10 pagesFisicaaaJuan Sebastian Qioñones OsorioNo ratings yet

- Laboratorio N°1 de Sistemas Digitales 2 Latch y Flip-Flop JKDocument7 pagesLaboratorio N°1 de Sistemas Digitales 2 Latch y Flip-Flop JKfranz barraNo ratings yet

- Práctica Técnicas Digitales Mar2022Document30 pagesPráctica Técnicas Digitales Mar2022Mateo ChNo ratings yet

- Contador BCD Mod 10Document9 pagesContador BCD Mod 10fonseca3No ratings yet

- A. Compuertas LógicasDocument37 pagesA. Compuertas LógicasDiego CastroNo ratings yet

- CUESTIONARIO PREVIO N°5 (QUINTANA, JOHN)Document16 pagesCUESTIONARIO PREVIO N°5 (QUINTANA, JOHN)John QuintanaNo ratings yet

- LAB5_DECODIFICADORES_BCD_7SEGMENTOSDocument9 pagesLAB5_DECODIFICADORES_BCD_7SEGMENTOSAngel Acosta TorresNo ratings yet

- Practica 4Document3 pagesPractica 4Christian OrtizNo ratings yet

- Informe Practica 3 SD Gerardo RodriguesDocument26 pagesInforme Practica 3 SD Gerardo RodriguesGerardo Rodrigues FlammiaNo ratings yet

- Activudad Evaluativa M2Document11 pagesActivudad Evaluativa M2Cristian valenzuelaNo ratings yet

- Lab 5Document13 pagesLab 5Manuel CoaguilaNo ratings yet

- Flip Flop ContadorDocument9 pagesFlip Flop ContadorAndrésCabreraSoriaNo ratings yet

- Lab de Control ElectricoDocument9 pagesLab de Control ElectricoGustavo Fuentes QNo ratings yet

- Proyecto Final123Document10 pagesProyecto Final123rayq6799No ratings yet

- Contador digital de dos dígitos con display de 7 segmentosDocument10 pagesContador digital de dos dígitos con display de 7 segmentosjoseNo ratings yet

- Tutorial Creación de Modulo 60 en ProteusDocument14 pagesTutorial Creación de Modulo 60 en ProteusJoel MontalvanNo ratings yet

- LABORATORIO 11 Contadores AsincronosDocument5 pagesLABORATORIO 11 Contadores AsincronosJimm AyllónNo ratings yet

- EE644 2023 1 Lab5 - 230629 - 110918Document4 pagesEE644 2023 1 Lab5 - 230629 - 110918ANGEL SAMIR PUCHO QUISPENo ratings yet

- Contadores y Divisores de FrecuenciaDocument11 pagesContadores y Divisores de FrecuenciaLimbert Alvaro Vargas LauraNo ratings yet

- Guía Laboratorio Lógica SecuencialDocument4 pagesGuía Laboratorio Lógica SecuencialJuan Camilo Betancur RicoNo ratings yet

- Resumen Técnico Del Análisis de Resultados Diseño y Simulación de Un Contador Ascendente y Descendente de L 0 Al 9Document12 pagesResumen Técnico Del Análisis de Resultados Diseño y Simulación de Un Contador Ascendente y Descendente de L 0 Al 9TAPUYO CHAPIRO DARWINNo ratings yet

- Preparatorio 6Document7 pagesPreparatorio 6Luis Edison TocaNo ratings yet

- LABORATORIO 05 - 2 Contadores AsincronosDocument5 pagesLABORATORIO 05 - 2 Contadores AsincronosDarwin YoverdNo ratings yet

- ContadorDocument13 pagesContadorEdwin GavilanezNo ratings yet

- Contador Decimal con Display 7 segmentosDocument15 pagesContador Decimal con Display 7 segmentosCristian ZavalaNo ratings yet

- Práctica 8Document7 pagesPráctica 8buanastareasbetovazquezNo ratings yet

- AvrDocument15 pagesAvrOmar BarrionuevoNo ratings yet

- Informe de Reloj Digital DDocument17 pagesInforme de Reloj Digital DRenato TrujilloNo ratings yet

- CerraduraDocument5 pagesCerraduraBranco Costa OrtegaNo ratings yet

- Contador binario de 0 a 255 con dos 74LS193Document9 pagesContador binario de 0 a 255 con dos 74LS193Ricardo salasNo ratings yet

- Practica2 ContadordigiDocument6 pagesPractica2 ContadordigiPily Onofre GonzálezNo ratings yet

- Reporte laboratorios contador 99-00Document3 pagesReporte laboratorios contador 99-00Maríale PolancoNo ratings yet

- Metrónomo DigitalDocument12 pagesMetrónomo DigitalFRANCO DANILO VERA TRUJILLONo ratings yet

- Informe N°4Document7 pagesInforme N°4Hans HuamanNo ratings yet

- Practica 8 74193Document7 pagesPractica 8 74193nohe_lemusNo ratings yet

- Tarea 4 Circuitos Secuenciales - 243004 - 32Document17 pagesTarea 4 Circuitos Secuenciales - 243004 - 32MiGue DAzaNo ratings yet

- SimuladorDigital GuiaPreliminar 0 9 1Document8 pagesSimuladorDigital GuiaPreliminar 0 9 1Jabato BravoNo ratings yet

- Electrónica II, Grupo IDocument19 pagesElectrónica II, Grupo IMoises VillarroelNo ratings yet

- Fase 4 ZULY GOMEZ Grupo53Document16 pagesFase 4 ZULY GOMEZ Grupo53chucho chavarroNo ratings yet

- Pines de 74HC595 y Sus FuncionesDocument10 pagesPines de 74HC595 y Sus FuncionesJuan Eduardo GivovichNo ratings yet

- Tarea 7 DiseñodelprogramadeuncontadorDocument8 pagesTarea 7 DiseñodelprogramadeuncontadorEstefania Rodriguez SanchezNo ratings yet

- 1IEE04 Diseño DigitalDocument12 pages1IEE04 Diseño DigitalLuis Sosa HernandezNo ratings yet

- Contador de Dos (2) DigitosDocument9 pagesContador de Dos (2) DigitosPAPOFULENo ratings yet

- Decodificador FinalDocument17 pagesDecodificador FinalAle UrNo ratings yet

- Tarea 3. Mauricio Rodríguez-3Document12 pagesTarea 3. Mauricio Rodríguez-3Mariela MarquezNo ratings yet

- Circuito de Memoria de 4 BitsDocument17 pagesCircuito de Memoria de 4 BitsYuselys Saavedra0% (1)

- Informe Plabo1 NMartinezDocument9 pagesInforme Plabo1 NMartinezNicky Martinez SalazarNo ratings yet

- Inf 3 DigitalesDocument7 pagesInf 3 DigitalesDuo Doble ANo ratings yet

- Digitales 6Document8 pagesDigitales 6Estela Albarracín CarmonaNo ratings yet

- Proyecto Sumador y Restador BCDDocument13 pagesProyecto Sumador y Restador BCDLiz Shermelyn Barrientos ValderramaNo ratings yet

- Arquitectura Del Computador Lab 1Document14 pagesArquitectura Del Computador Lab 1Jess Gabriel RojasNo ratings yet

- Informe Proyecto - Reloj BinarioDocument10 pagesInforme Proyecto - Reloj BinarioAlex TipantuñaNo ratings yet

- Manual de Practicas Sistemas DigitalesDocument30 pagesManual de Practicas Sistemas DigitalesTOLUCA FESTNo ratings yet

- Informe LaboratorioN°1 NMartinezDocument10 pagesInforme LaboratorioN°1 NMartinezNicky Martinez SalazarNo ratings yet

- Practica 8. Circuitos Digitales Secuenciales-AplicacionesDocument7 pagesPractica 8. Circuitos Digitales Secuenciales-AplicacionesJesús'Chucho'MohaliNo ratings yet

- Aprender Arduino, electrónica y programación con 100 ejercicios prácticosFrom EverandAprender Arduino, electrónica y programación con 100 ejercicios prácticosRating: 4.5 out of 5 stars4.5/5 (14)

- Manual ISO 690Document34 pagesManual ISO 690wellisNo ratings yet

- Apunte Matlab Parte1 y 2Document27 pagesApunte Matlab Parte1 y 2Kcho AnteloNo ratings yet

- Control en cascada para mejorar el rechazo de perturbacionesDocument30 pagesControl en cascada para mejorar el rechazo de perturbacionesBryanGutierrezNo ratings yet

- 74 0128 Ie PDFDocument233 pages74 0128 Ie PDFBryanGutierrezNo ratings yet

- Contadores integrados asincrónos y síncronosDocument13 pagesContadores integrados asincrónos y síncronosYulmanNo ratings yet

- Clasificacion de Procesos IndustrialesDocument2 pagesClasificacion de Procesos IndustrialesBryanGutierrezNo ratings yet

- Llenado de BombaDocument1 pageLlenado de BombaBryanGutierrezNo ratings yet

- Control en CascadaDocument24 pagesControl en Cascadamarco_reategui_2No ratings yet

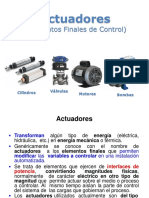

- Actuadores (Elementos Finales)Document20 pagesActuadores (Elementos Finales)RafaelLopezSalazarNo ratings yet

- DIODOSDocument2 pagesDIODOSBryanGutierrezNo ratings yet

- La Etica Del Siglo XxiDocument2 pagesLa Etica Del Siglo XxiMtroEdgarGuillénNo ratings yet

- 06 Motor SincronoDocument10 pages06 Motor SincronoJSNo ratings yet

- Ecuaciones Diferenciales: Tipos, Orden, Grado y SolucionesDocument13 pagesEcuaciones Diferenciales: Tipos, Orden, Grado y SolucionesBryanGutierrez100% (1)

- Ejercicios Resueltos Int LineaDocument8 pagesEjercicios Resueltos Int LineaMansouri KamalNo ratings yet

- Electronica Digital1Document62 pagesElectronica Digital1BryanGutierrezNo ratings yet

- Power Point de EstadisticaDocument16 pagesPower Point de EstadisticaBruno DiazNo ratings yet

- Reduccion Al Primer Cuadrante IDocument4 pagesReduccion Al Primer Cuadrante IProyectos BarneyNo ratings yet

- Principios TermodinamicaDocument13 pagesPrincipios TermodinamicaAlexx WolfmanNo ratings yet

- Ejemplos de Escalas de MediciónDocument3 pagesEjemplos de Escalas de MediciónArelyLopezNo ratings yet

- PID en PICDocument9 pagesPID en PICArmando Pérez ReynosoNo ratings yet

- Definición de Producto y Producto NotableDocument34 pagesDefinición de Producto y Producto NotableAmerica Rmz PatiñoNo ratings yet

- Ideas sobre la locura: el cerebro, los genes y el ambienteDocument210 pagesIdeas sobre la locura: el cerebro, los genes y el ambientememo leyNo ratings yet

- Taller InteractivoDocument5 pagesTaller Interactivomeredith Gutierrez CardonaNo ratings yet

- Clase 6 Elementos FinitosDocument73 pagesClase 6 Elementos FinitosJorGe IsRaelNo ratings yet

- Operaciones de Notación CientíficaDocument5 pagesOperaciones de Notación CientíficaCarito RubilarNo ratings yet

- PL PNLDocument2 pagesPL PNLEsthela VillanuevaNo ratings yet

- Lineas de TransmisiónDocument41 pagesLineas de TransmisiónJeyser BernillaNo ratings yet

- Razonamiento MatemáticoDocument8 pagesRazonamiento MatemáticoPoli Gonzalez GuerreroNo ratings yet

- CÁLCULOS Coeficiente de RepartoDocument8 pagesCÁLCULOS Coeficiente de RepartoLeandroFuentesMedina0% (1)

- Palabras clave JavaDocument4 pagesPalabras clave Javairlandis0% (1)

- Ejercicios Primera UnidadDocument2 pagesEjercicios Primera Unidadsip posNo ratings yet

- Ficha de Trabajo - Semana 6 - MCDDocument3 pagesFicha de Trabajo - Semana 6 - MCDCarlos GuerreroNo ratings yet

- 01 Tarea 1 Reservas Matemáticas PDFDocument5 pages01 Tarea 1 Reservas Matemáticas PDFjose zepeda0% (1)

- Pronóstico ventas madera 2018-2019 regresión linealDocument7 pagesPronóstico ventas madera 2018-2019 regresión linealParra Ruiz Raquel DaveibaNo ratings yet

- Actividades Fisica Unidad 5Document12 pagesActividades Fisica Unidad 5Irma Arroyo Juárez100% (1)

- Distribucion Normal-TablasDocument14 pagesDistribucion Normal-TablasFernanda DelgadoNo ratings yet

- Matrices Efe Efi y Foda 29163 PDFDocument25 pagesMatrices Efe Efi y Foda 29163 PDFCuentas EstrategicasNo ratings yet

- Actividad 01 Sistemas NuméricosDocument4 pagesActividad 01 Sistemas NuméricosLeonardo Ponce LeónNo ratings yet

- Lcin U1 Ea AlgsDocument10 pagesLcin U1 Ea AlgsLeonel GSNo ratings yet

- Examen I UnidadDocument1 pageExamen I UnidadANDREA MICHELLE GALLEGOS CAIZANo ratings yet

- Actividades 5° 18 Al 29 MayoDocument20 pagesActividades 5° 18 Al 29 MayoAnnelNo ratings yet

- Material Libro Trigonometría - GeometríaDocument32 pagesMaterial Libro Trigonometría - GeometríajoelNo ratings yet

- Problemas M A S I-2012Document1 pageProblemas M A S I-2012Edgar GonzalezNo ratings yet

- Criptografía I Sha-1Document34 pagesCriptografía I Sha-1Antonio Flores ChoqueNo ratings yet

- Recomendaciones para Redacc. de Acciones, Actividades e IndicadoresDocument3 pagesRecomendaciones para Redacc. de Acciones, Actividades e IndicadoresEdgar Martin Hernandez Huaripaucar100% (2)