Professional Documents

Culture Documents

Cmos RF Modeling For: GHZ Communication Ic'S

Uploaded by

shahebgoudahalladamaniOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Cmos RF Modeling For: GHZ Communication Ic'S

Uploaded by

shahebgoudahalladamaniCopyright:

Available Formats

10.

2

CMOS RF Modeling for GHz Communication ICs

Jia-Jiunn Ou, Xiaodong Jin, Ingrid Ma, Chenming Hu, and Paul R. Gray

Department of Electrical Engineering & Computer Sciences

University of California, Berkeley, CA 94720

Introduction

With the advent of submicron technologies, GHz RF circuits can now be realized in a standard CMOS process [ I ] . A

major barrier to the realization of robust commercial CMOS

RF components is the lack of adequate models which accurately predict MOSFET device behavior at high frequencies.

The conventional microwave table-lookup-based approach

requires a large database obtained from numerous device

measurements and computationally intense simulations for

accurate results. This method becomes prohibitively complex

when used to simulate highly integrated CMOS communication systems; hence, a compact model, valid for a broad range

of bias conditions and operating frequencies is desirable.

BSIM3v3 has been widely accepted as a standard CMOS

model for low frequency applications. Recent work has demonstrated the capability of modeling CMOS devices at high

frequencies by utilizing a complicated substrate resistance

network and extensive modification to the BSIM3v3 source

code [2]. This paper first describes a unified device model

realized with a lumped resistance network suitable for simulations of both R F and baseband analog circuits; then verifies

the accuracy of the model to measured data on both device

and circuit levels.

BSIM3v3 RF Model

The new BSIM3v3 RF model is realized with the addition

of three resistors R,, Rs+, and Rsubr to the existing

BSIM3v3.1 model (shown in Fig. I). R, models both the

physical gate resistance as well as the non-quasi-static (NQS)

effect. Rsubd and R,,,, are the lumped substrate resistances

between the source/dram junctions and the substrate contacts.

The values of R,,bd and Rsubs may not be equal as they are

functions of the transistor layout (illustrated in Fig. 2).

To demonstrate the accuracy of the model, s-parameters of

the BSIM3v3 RF model, BSIM3v3 model, and measured data

of a 0.35pm NMOS device are plotted in Fig. 3. The

improvement can be clearly seen from the 822 but hardly from

S l l . A better picture and more physical insight may be

obtained by separating the terminal impedance into the real

and imaginary parts with the following six parameters,

Rin = real(l/yll) ; Cin= -l/imag(l/yll)/ w ;

R,,( = 11 real022) ; C(,ur= imag@zz)/ w ;

g, = realbzl) ;

94

Cfi = -imagblz)/ 0 ,

dc characteristics but not the high frequency behavior. Fig. 5

shows the simulated Rol,, and C , , , of a 0.5pm NMOS device

with various body biases. Good agreement has been achieved

hctween the 2-D simulation and the proposed model.

Parameter Extraction

R, can be extracted in part from the gate sheet resistance.

With the NQS effect, lumped R, may be obtained from the

measured R,. For a fixed cell layout, Rsuhd can be extracted

from R,,,, by connecting the drain as port2. Similarly Rsubsis

found by using the source as port2. It is recommended to

adjust the low frequency source/drain junction capacitance to

fit-the s-parameter data accounting for distributed RC effects

and measurement inaccuracies.

Circuit Evaluation

To test the robustness of the BSIM3v3 RF model, a circuit

level evaluation was performed using two different

approaches. As a first example, a 5GHz single-ended lownoise amplifier (LNA) using a 0.35wm device was simulated

using BSIM3v3 RF model, as shown in Fig. 6(a). The tablelookup method was employed to compute overall circuit performance from the measured device data and the results were

compared with the SPICE simulation. Fig. 6(b) shows a good

agreement between the two methods for the Szl. In the second example, a 2GHz differential LNA was designed and fabricated in a 0.6pm CMOS process, as shown in Fig. 7(a). Fig.

7(b) shows the measured voltage gain compared to the simulated results. Clearly the low frequency BSIM3v3 model

overestimates the peak voltage gain by 2dB, while the RF

model accurately predicts the circuit performance within the

frequency of interest.

Conclusion

The BSIM3v3 RF model, which requires only three additional parameters and no modification of existing model

source code, has been proposed for accurately predicting

CMOS device behavior up to IOGHz. Both device and circuit

level evaluations were conducted and show excellent agreement. With the BSIM3v3 RF model, well suited for simulating both RF and mixed-signal circuits, it is now possible to

design highly integrated CMOS communication systems with

a unified device model and simulator.

Acknowledgment

where w is the frequency in rad/s (gate is portl, drain port2,

and body shorted to the source). As shown in Fig. 4,excellent

agreement up to lOGHz has been achieved. In particular, the

proposed model significantly improves the agreement

between the model and data for Rin and Rout over a wide frequency range.

This work is supported by National Semiconductor Fellowship and SRC 97-SJ-417. The authors would like to thank

SGS-Thomson and TSMC for wafer fabrication and G. Zhang

for assistance on model extraction.

A unique problem in modeling CMOS is the body bias

effect. To study this effect at high frequencies, a 2-D device

simulator was used to generate both dc and s-parameter data.

The results show that the body bias mainly affects the device

personal communications, in CICC, pp. 83-90, May 1995.

[2] W. Liu, et al., RF MOSFET modeling accounting for distributed

substrate and channel resistances with emphasis on the BSIM3v3

SPICE model, in IEDM, pp. 309-312, Dec. 1997.

0-7803-4700-6/98/$10.00 0 1998 IEEE

References

111 P. Gray and R. Meyer, Future directions of silicon ICs for RF

1998 Symposium on VLSl Technology Digest of Technical Papers

hubs

(b) Szz

Fig. I . Proposed BSIM3v3 R F model.

Fig. 2. Cross sectional view and top view

of a typical transistor cell layout.

Fig. 3. Smith Chart representation of a NMOS device with

L=0.3Spm, W=160pm, Wfing,,=IOpm, Vgs=2V and Vds=2V.

fmS)

- I

50

40

30

20

10

n

Fig. 4. Terminal impedance illustration of a NMOS device with L=0.3Spm, W=160pm,

WfingeilOpm,Vgs=ZV and Vds=2V. R,=9Q and R,y,,,,F90Rare extracted in this case.

(a)

1000

Vdd 2V

900

Out

0.25pF

-m

800

l o u t+

Bias

15010.6

700

600

9mA

(a) circuit schematic

(a)

60

R",,

(a) circuit schematic

(dB)

(fF)

56

52

20

(dB)

25

10

23

21

-10

19

48

44

3

(b) Cl,,,

10

(GW

Fig 5 . 2-D simulation result vs. BSIM3v3 RF model

with various body biases, L=O.Spm. W=IOOpm.

Vgs=2V, and Vds=2V.

5

(h) I %I 1

10

(GHz)

Fig. 6. A single-ended SGHz LNA using

a 160ptn/0.3SpmNMOS device

1.8

1.9

2.0

2.1

(h) voltage gain

2.2

(GHd

Fig 7.A 2GHz differential LNA designed

and fabricated in a 0.6pm CMOS process.

1998 Symposium on VLSl Technology Digest of Technical Papers

95

You might also like

- Macromodel ExtractionDocument11 pagesMacromodel Extractionapi-19668941No ratings yet

- Miniaturized Six-Port Receiver For 60 GHZ Communication ENDocument5 pagesMiniaturized Six-Port Receiver For 60 GHZ Communication ENWalter Santiago Campos ArandaNo ratings yet

- Microstrip Coupled Line Filter Design For Ultra Wideband ApplicationsDocument9 pagesMicrostrip Coupled Line Filter Design For Ultra Wideband Applicationsjmicrojouranl1No ratings yet

- MDLX Atc App Note Pi 026Document0 pagesMDLX Atc App Note Pi 026david_benavidez_3No ratings yet

- All Inversion RegionDocument4 pagesAll Inversion RegionAshwin BhatNo ratings yet

- MOS Transistor Modeling For RF IC Design (Enz)Document16 pagesMOS Transistor Modeling For RF IC Design (Enz)Sharabi.salahNo ratings yet

- Heterojunction Bipolar Transistors for Circuit Design: Microwave Modeling and Parameter ExtractionFrom EverandHeterojunction Bipolar Transistors for Circuit Design: Microwave Modeling and Parameter ExtractionNo ratings yet

- AnalogDocument8 pagesAnalogAhmed F RahimNo ratings yet

- A 77 GHZ Controllable Gain Low Noise AmplifierDocument4 pagesA 77 GHZ Controllable Gain Low Noise AmplifierMehrdad FahimniaNo ratings yet

- ACES Journal February 2011 Paper 06Document10 pagesACES Journal February 2011 Paper 06yasmineNo ratings yet

- RF Modeling of An MOS Varactor and MIM Capacitor in 0.18 - M CMOS TechnologyDocument5 pagesRF Modeling of An MOS Varactor and MIM Capacitor in 0.18 - M CMOS TechnologyDuc DucNo ratings yet

- Design of High Performance Dynamic CMOS Circuits in Deep Submicron TechnologyDocument15 pagesDesign of High Performance Dynamic CMOS Circuits in Deep Submicron TechnologyEeshwar Ram JNo ratings yet

- Design of A CMOS Tapered Cascaded Multistage Distributed AmplifierDocument10 pagesDesign of A CMOS Tapered Cascaded Multistage Distributed Amplifierindresh.vermaNo ratings yet

- Interr ConDocument4 pagesInterr Conjubincb2No ratings yet

- Modeling of Large-Area nMOS Devices For Smart-Power ApplicationsDocument4 pagesModeling of Large-Area nMOS Devices For Smart-Power ApplicationsSasi Kiran SNo ratings yet

- Ka BAND MICROSTRIPANTENNAARRAYS WITH EIGE EFFICIENCYDocument4 pagesKa BAND MICROSTRIPANTENNAARRAYS WITH EIGE EFFICIENCYMarcia Rizky HamdalaNo ratings yet

- EMC Modeling of Large Electronic SystemsDocument4 pagesEMC Modeling of Large Electronic SystemssmhbNo ratings yet

- Analysis of Propagation Model in Conformance With IEEE 802.16-2009-Based Fixed Wireless NetworksDocument6 pagesAnalysis of Propagation Model in Conformance With IEEE 802.16-2009-Based Fixed Wireless NetworksJoseVelascoNo ratings yet

- Broadband Electrical Modeling of Transitions and Interconnects Useful For PCB and Co-Fired Ceramic Packaging - ForPublicationDocument20 pagesBroadband Electrical Modeling of Transitions and Interconnects Useful For PCB and Co-Fired Ceramic Packaging - ForPublicationrickNo ratings yet

- Ultra-Dense Networks for 5G and Beyond: Modelling, Analysis, and ApplicationsFrom EverandUltra-Dense Networks for 5G and Beyond: Modelling, Analysis, and ApplicationsTrung Q. DuongNo ratings yet

- Multiband Antenna 5Document5 pagesMultiband Antenna 5Vaishnavi JohriNo ratings yet

- ContentDocument6 pagesContentashwingeorge101No ratings yet

- Equivalent Circuit Model of The Slotted Ground Structures (SGSS) Underneath The Microstrip LineDocument3 pagesEquivalent Circuit Model of The Slotted Ground Structures (SGSS) Underneath The Microstrip LinehmalrizzoNo ratings yet

- Ie3d FeaturesDocument5 pagesIe3d Featuresvishnuu06No ratings yet

- Efecto PielDocument9 pagesEfecto PielMilena AlarconNo ratings yet

- Geometric Programming Based Power-Delay Optimization Using Transistor-Sizing For Submicron and Deep Submicron CMOS InverterDocument4 pagesGeometric Programming Based Power-Delay Optimization Using Transistor-Sizing For Submicron and Deep Submicron CMOS Invertersuchi87No ratings yet

- A Tutorial: Subcircuit and Verilog-A RF Circuit Simulation Models For Axial and Surface Mounted ResistorsDocument17 pagesA Tutorial: Subcircuit and Verilog-A RF Circuit Simulation Models For Axial and Surface Mounted Resistorsiarcad9403No ratings yet

- Reliability Analysis and Optimization of Power-Gated IcsDocument12 pagesReliability Analysis and Optimization of Power-Gated Icskaushik_gupta_4No ratings yet

- Design of New DGS Hairpin Microstrip Bandpass Filter Using Coupling Matrix MethodDocument5 pagesDesign of New DGS Hairpin Microstrip Bandpass Filter Using Coupling Matrix MethodĐoàn GiangNo ratings yet

- Optical Communication For Dust MotesDocument8 pagesOptical Communication For Dust MotesApurvaNo ratings yet

- Millimeter-Wave Dual-Band Microstrip Patch Antennas Using Multilayer Gaas TechnologyDocument4 pagesMillimeter-Wave Dual-Band Microstrip Patch Antennas Using Multilayer Gaas TechnologyShivanandKalmaniNo ratings yet

- A Novel Rat Race Coupler Design For Dual-Band ApplicationsDocument3 pagesA Novel Rat Race Coupler Design For Dual-Band Applicationsmehrab_ramzan1194No ratings yet

- High Speed Layout AnalogDocument4 pagesHigh Speed Layout AnalogMahendra SakreNo ratings yet

- Ahuja CompensationDocument5 pagesAhuja CompensationCem ÇakırNo ratings yet

- A 1.8Ghz Cmos: Low-Power Truly-Modular Programmable Divider in Standard TechnologyDocument4 pagesA 1.8Ghz Cmos: Low-Power Truly-Modular Programmable Divider in Standard TechnologyMuhammad_Swilam_2010No ratings yet

- Design of Folded Cascode OTA in Different Regions of Operation Through gmID Methodology PDFDocument6 pagesDesign of Folded Cascode OTA in Different Regions of Operation Through gmID Methodology PDFAyush MalhotraNo ratings yet

- Advanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionFrom EverandAdvanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionNo ratings yet

- 0.9V 32Nm Dual-Gate Si Finfet: Low-Power Ptl-Based Multiplexer Design inDocument4 pages0.9V 32Nm Dual-Gate Si Finfet: Low-Power Ptl-Based Multiplexer Design inNamrata SaxenaNo ratings yet

- Advanced Multicarrier Technologies for Future Radio Communication: 5G and BeyondFrom EverandAdvanced Multicarrier Technologies for Future Radio Communication: 5G and BeyondNo ratings yet

- The Last BarrierDocument13 pagesThe Last BarrierGdv Santhosh KumarNo ratings yet

- Design of Folded Cascode OTA in Different Regions of Operation Through G /I MethodologyDocument6 pagesDesign of Folded Cascode OTA in Different Regions of Operation Through G /I MethodologyPramod SrinivasanNo ratings yet

- Towards All Optical DCI NetworksDocument3 pagesTowards All Optical DCI NetworksNipun SahniNo ratings yet

- Transfer Function and Impulse Response Simulation of Power Line ChannelDocument7 pagesTransfer Function and Impulse Response Simulation of Power Line ChannelIjsrnet EditorialNo ratings yet

- Optical Ring-Coupler Simulation Using CST MICROWAVE STUDIODocument3 pagesOptical Ring-Coupler Simulation Using CST MICROWAVE STUDIONgô Cự MạnhNo ratings yet

- Development of A FMCW LADAR Source Chip Using MEMS-Electronic-Photonic Heterogeneous IntegrationDocument4 pagesDevelopment of A FMCW LADAR Source Chip Using MEMS-Electronic-Photonic Heterogeneous IntegrationLukeNo ratings yet

- Op Amp PaperDocument6 pagesOp Amp PaperSrinivasu IrlapatiNo ratings yet

- IR Drop PDFDocument3 pagesIR Drop PDFarammartNo ratings yet

- D6 Transmission Model Parameter Draft1-2 - 9!3!2010Document38 pagesD6 Transmission Model Parameter Draft1-2 - 9!3!2010فیضان حنیفNo ratings yet

- A Multilayer Ultra-Wideband Directional CouplerDocument5 pagesA Multilayer Ultra-Wideband Directional Coupleragmnm1962No ratings yet

- 250 GHZ Sige-Bicmos Cascaded Single-Stage Distributed AmplifierDocument4 pages250 GHZ Sige-Bicmos Cascaded Single-Stage Distributed AmplifierAli HattabNo ratings yet

- A High-Speed Continuous-Time Bandpass VHF Filter in TechnologyDocument4 pagesA High-Speed Continuous-Time Bandpass VHF Filter in Technologyعاطف رضاNo ratings yet

- Modeling of Coplanar Waveguide Meander-LineInductorsDocument10 pagesModeling of Coplanar Waveguide Meander-LineInductorsalisazidNo ratings yet

- Understanding Baluns For Highly Integrated RF ModulesDocument10 pagesUnderstanding Baluns For Highly Integrated RF Modulesjigg1777No ratings yet

- Radio Frequency Identification and Sensors: From RFID to Chipless RFIDFrom EverandRadio Frequency Identification and Sensors: From RFID to Chipless RFIDNo ratings yet

- Electronically Reconfigurable HM-SIW Band-Pass Filter Based On New CSRR Design Using PIN DiodesDocument11 pagesElectronically Reconfigurable HM-SIW Band-Pass Filter Based On New CSRR Design Using PIN DiodesAnanya ParameswaranNo ratings yet

- Analysis, Reduction and Avoidance of Crosstalk On VLSI ChipsDocument8 pagesAnalysis, Reduction and Avoidance of Crosstalk On VLSI Chipsjubincb2No ratings yet

- Complex Antenna System Simulation Uses EM Software: ElectronicsDocument4 pagesComplex Antenna System Simulation Uses EM Software: Electronicshamid_arjmandNo ratings yet

- A Novel Method For Analysis of Power Consumption in VLSI Global InterconnectsDocument12 pagesA Novel Method For Analysis of Power Consumption in VLSI Global InterconnectsPranay KumarNo ratings yet

- Department of Electronics & Communication Engineering: Format For Internal Evaluation of Internship (III Sem M.Tech)Document1 pageDepartment of Electronics & Communication Engineering: Format For Internal Evaluation of Internship (III Sem M.Tech)shahebgoudahalladamaniNo ratings yet

- Exam One Kar2Document3 pagesExam One Kar2shahebgoudahalladamaniNo ratings yet

- Mtech 123 Res 2015Document39 pagesMtech 123 Res 2015shahebgoudahalladamaniNo ratings yet

- Time Table 2015-16 Even Ec DC VlsieDocument5 pagesTime Table 2015-16 Even Ec DC VlsieshahebgoudahalladamaniNo ratings yet

- Application Form For M.techDocument3 pagesApplication Form For M.techshahebgoudahalladamaniNo ratings yet

- New Microsoft Word DocumentDocument5 pagesNew Microsoft Word DocumentshahebgoudaNo ratings yet

- Embedded System of Shibu K VDocument10 pagesEmbedded System of Shibu K Vshahebgoudahalladamani0% (1)

- LFSR Verilog CodeDocument2 pagesLFSR Verilog CodeshahebgoudahalladamaniNo ratings yet

- Tagline TemplateDocument2 pagesTagline TemplateshahebgoudahalladamaniNo ratings yet

- Time Borrow LatchDocument4 pagesTime Borrow LatchSachin TanejaNo ratings yet

- User Manual User Manual User Manual User Manual: FA-2 Frequency CounterDocument15 pagesUser Manual User Manual User Manual User Manual: FA-2 Frequency CounterCarlos Guillermo VahnovanNo ratings yet

- 2700 Series Basic Extensions ManualDocument636 pages2700 Series Basic Extensions ManualHoàng ĐìnhNo ratings yet

- Gender Recognition System Using Speech SignalDocument9 pagesGender Recognition System Using Speech SignalijcseitNo ratings yet

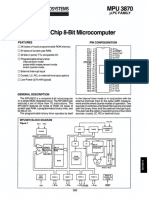

- Standard Microsystems Corporation: Features Pin ConfigurationDocument8 pagesStandard Microsystems Corporation: Features Pin ConfigurationВячеслав НебесныйNo ratings yet

- Instruction Manual Universal Fieldbus-Gateway Unigate CM - ProfibusDocument62 pagesInstruction Manual Universal Fieldbus-Gateway Unigate CM - ProfibusFakhri GhrairiNo ratings yet

- Wired Dynamic Vocal Mic With CableDocument2 pagesWired Dynamic Vocal Mic With CableMarius DanielNo ratings yet

- Datasheet LM2576TDocument19 pagesDatasheet LM2576TPLASTIC666No ratings yet

- ThesisDocument164 pagesThesisShi XIntianNo ratings yet

- Parameter Design For A 6.78-MHz Wireless Power Transfer SystemDocument12 pagesParameter Design For A 6.78-MHz Wireless Power Transfer Systemagmnm1962No ratings yet

- MSK Minimum-Shift KeyingDocument2 pagesMSK Minimum-Shift KeyingfiraszekiNo ratings yet

- Detection & Distinction of Colors Using Color Sorting Robotic Arm in A Pick & Place MechanismDocument42 pagesDetection & Distinction of Colors Using Color Sorting Robotic Arm in A Pick & Place MechanismTrinesh GowdaNo ratings yet

- Multimeter Parts and FunctionsDocument3 pagesMultimeter Parts and FunctionsDavid Dela CruzNo ratings yet

- BitvoicerDocument7 pagesBitvoicerSusetyo RomadhoniNo ratings yet

- Book List For EEE Job PreparationDocument5 pagesBook List For EEE Job PreparationTanvir Alam Shishir100% (1)

- OptimusDocument53 pagesOptimusMahmoud TabakhNo ratings yet

- 1244153Document86 pages1244153Caétano B MascarénhasNo ratings yet

- An PRC 119 Programming TroubleshootingDocument20 pagesAn PRC 119 Programming Troubleshootingdragon4036100% (1)

- EEE342-MP-13a-Buffering, Demultiplexing 8086 and 8088 MicroprocessorsDocument10 pagesEEE342-MP-13a-Buffering, Demultiplexing 8086 and 8088 MicroprocessorsBilal KhanNo ratings yet

- 4ipnet 2017 CatalogueDocument4 pages4ipnet 2017 CatalogueKleng KlengNo ratings yet

- DHI-KTA02: Video Intercom KitDocument2 pagesDHI-KTA02: Video Intercom KitÁngel GóticoNo ratings yet

- The Engineers Practical Guide To Emi Filters - WebDocument65 pagesThe Engineers Practical Guide To Emi Filters - WebChanwit PrasantanakornNo ratings yet

- Series 67XXB Swept Frequency Synthesizer Operation Manual: Important NoticeDocument86 pagesSeries 67XXB Swept Frequency Synthesizer Operation Manual: Important NoticeMohammed AliNo ratings yet

- Incubators: BD 240 - Incubator With Natural ConvectionDocument4 pagesIncubators: BD 240 - Incubator With Natural ConvectionangelstanzNo ratings yet

- MATLAB Projects List From SoftroniicsDocument11 pagesMATLAB Projects List From SoftroniicssoftroniicsNo ratings yet

- Maxon 49-SX 2-Way Radio MANUALDocument16 pagesMaxon 49-SX 2-Way Radio MANUALRich RitterbuschNo ratings yet

- Assignment 1: Implementation of A Processor (10marks) : Constant RDST OpcodeDocument6 pagesAssignment 1: Implementation of A Processor (10marks) : Constant RDST OpcodeTharakram KorripatiNo ratings yet

- Ra 766Document1 pageRa 766rabeaNo ratings yet

- Datasheet of DVR 204Q M1 - V4.71.000 - 20230118Document5 pagesDatasheet of DVR 204Q M1 - V4.71.000 - 20230118Andres MendozaNo ratings yet

- 1 (CHS) Materials, Tools, Equipment and Testing DevicesDocument5 pages1 (CHS) Materials, Tools, Equipment and Testing DevicesArtem ParriñasNo ratings yet