Professional Documents

Culture Documents

Cascaded H-Bridge Multilevel Inverter Using New Phase Shifted Carrier Pulse Width Modulation Technique

Uploaded by

Mefisto ElOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Cascaded H-Bridge Multilevel Inverter Using New Phase Shifted Carrier Pulse Width Modulation Technique

Uploaded by

Mefisto ElCopyright:

Available Formats

ISSN (Print) : 2320 3765

ISSN (Online): 2278 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 12, December 2014

Cascaded H-bridge Multilevel Inverter Using

New Phase Shifted Carrier Pulse Width

Modulation Technique

Ch.Lokeshwar Reddy1, P.Satish Kumar2, M.Sushama3

Dept of EEE, CVR College of Engineering, Hyderabad, India1

Dept of EEE, College of Engineering, Osmania University, Hyderabad, India2

JNTU College of Engineering, Kukatpally, Hyderabad, India3

ABSTRACT: This paper presents a new Phase shifted carrier PWM technique for Cascaded Multilevel Inverter. The

main objective of this technique is to reduce the THD of inverter output voltage. This strategy leads to the cancellation

of all carrier and associated sideband harmonics up to 2Ncth carrier group where Ncis the number of H-bridges in a

phase. In this modulation process, the switching frequency preferably high to reduce the undesired side effects of

discontinuous power flow at switching and to reduce lower harmonics in the output voltage. Comparison of harmonic

spectrum for different carrier frequencies and different modulation indexes for a eleven inverter is presented in this

paper. This technique can be extended to any number of levels.

KEYWORDS: Cascaded Multilevel Inverter (CMLI), Modulation Index, Phase shifted carrier PWM.

I.INTRODUCTION

Multilevel inverters are finding increased attention in industries for medium voltage and high power applications.

Multilevel converters are mainly used to get desired single or three phase voltage waveforms, because of improving

waveform of the inverter reduces its harmonic content, the size of the filter used and the level of electromagnetic

interference generated by switching operation[1]. The required multi staircase output voltage is obtained by combining

several dc voltage sources. Solar cells, fuel cells, batteries and ultra capacitors are the most common independent

sources used. Multilevel converters are mainly used for medium and high power applications. There exists three

commercial topologies of multilevel inverters; these are Diode clamped multilevel converters (or) Neutral Point

Clamped (NPC), Flying Capacitor (FC), and Cascaded Multilevel Inverter (CMLI)[2]. The CMLI appears to be

superior to other inverter topologies in application at high power rating due to its modular nature of modulation, control

and protection requirements of each full bridge inverter [3].

Diode clamped multilevel converters are used in conventional high power ac motor drive applications like conveyers,

pumps, fans, and mills. They are also utilized in oil, gas, metals, power, mining, water, marine, and chemical industries.

They have also been used in back-to-back configuration for regenerative applications. Flying capacitor multilevel

converters have been used in high bandwidth and high switching frequency applications such as medium voltage

traction drives. Cascaded multilevel inverters are used where high power and power quality are essential, for example,

Static synchronous compensators (STATCOM) and reactive power compensation applications, photovoltaic power

conversion, and uninterruptable power supplies. One of the increasing applications for multilevel converter is electric

and hybrid power trains.

In this paper Cascaded H-bridge eleven level inverter is modeled for different modulation indexes and different carrier

signal frequencies, harmonic analysis is carried out and compared among them. The most preferred PWM technique for

Cascaded H-bridge inverters is Phase shifted Carrier PWM [3].

Copyright to IJAREEIE

10.15662/ijareeie.2014.0310029

www.ijareeie.com

14001

ISSN (Print) : 2320 3765

ISSN (Online): 2278 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 12, December 2014

II. CASCADED MULTILEVEL INVERTERS

In this topology single phase full bridge inverter cells with different dc sources are connected in series. Fig 1 shows the

power circuit for three phase eleven level inverter with five cells in each phase and Fig 2 shows the circuit

representation of each H-bridge cell. The resulting phase voltage is the addition of voltages generated by the different

cells in that phase. Each single phase full bridge inverter generates three voltages: +Vdc, 0, and Vdc at the output. The

output phase voltage swings from -5Vdc to +5Vdc with eleven levels and the resulting waveform is nearly sinusoidal,

even without filtering. The number level in phase voltage is 2Nc+1, where Nc is number of single phase inverter cells

used in a phase and the number of level in line voltage is 2m-1, where m is the number of levels in phase voltage.

CMLI researches the higher output voltage and power levels (13.8 kV, 30 MVA) and the higher reliability due to its

modular topology [5].

Fig.1. Three phase eleven level Cascaded H-bridge inverter

Fig.2. Circuit of each H-bridge cell

III. NEW PHASE SHIFTED CARRIER PWM

Most of the modulation methods developed for multilevel inverters are based on carrier arrangements. The carriers can

be arranged with vertical shift (phase disposition-PD, phase opposition disposition-POD, and alternative phase

opposition disposition-APOD), or with horizontal displacements (phase shifted carrier PWM)[6]. For the cascaded

inverter, phase shifted carrier PWM is the most common strategy with an improved harmonic performance, it offers an

evenly power distribution across all cells and it is very easy to implement independently for the number of inverters[7].

In this approach, the carriers shifted by an angle 3600/Nc (where Nc is number of single phase inverter cells used in a

phase leg). This strategy leads to the cancellation of all carrier and associated sideband harmonics up to 2Ncth carrier

group[8]. The modulation index is always multiples of three to have symmetry in the output voltage. The switching

frequency preferably should be high, to reduce the undesired side effects of discontinuous power flow at switching and

Copyright to IJAREEIE

10.15662/ijareeie.2014.0310029

www.ijareeie.com

14002

ISSN (Print) : 2320 3765

ISSN (Online): 2278 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 12, December 2014

to reduce lower harmonics in the output voltage. Fig.3. shows the half cycle of sinusoidal reference and carrier signals

for eleven level PWM operation.

1

0.8

0.6

magnitude

0.4

0.2

0

-0.2

-0.4

-0.6

-0.8

-1

0

0.001

0.002

0.003

0.004

0.005

Time

0.006

0.007

0.008

0.009

0.01

Fig.3. Carrier and reference waveform arrangements (Half cycle only) for a eleven level phase shifted carrier strategy

IV.SIMULATION AND RESULTS

The eleven level CMLI was simulated with RL load, and the DC voltage given is 100V. Fig 4 shows the circuit

arrangement for eleven level CMLI with PWM generator. Fig 5 shows the generation of phase shifted carrier PWM

signals for one phase. The simulation was done for 900Hz and 1200Hz carrier frequencies, and for modulation indexes

M=0.8 and M=1.

Fig.4. Eleven level Cascaded H-bridge Multilevel Inverter

Fig.5. Circuit model to generate phase shifted carrier PWM signals (one phase) for eleven level CMLI

Copyright to IJAREEIE

10.15662/ijareeie.2014.0310029

www.ijareeie.com

14003

ISSN (Print) : 2320 3765

ISSN (Online): 2278 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 12, December 2014

Fig 6 and Fig 8 shows the output Line and phase voltages of eleven level CMLI and Fig 7 and Fig 9 shows the

corresponding FFT analysis, with modulation index M=0.8 and carrier frequency Fc=1200. From the Fig 7 and 9 all the

carrier and associated sideband harmonics up to 2Ncth carrier group i.e up to 12 kHz frequency was cancelled. It was

due to the phase shifted PWM strategy. And also the peak value of phase voltage is M*Nc*Vdc it can verified from the

Fig 8.

800

600

LineVoltage(Volt)

400

200

0

-200

-400

-600

-800

0

0.05

0.1

0.15

0.2

0.25

Time(Sec)

Fc=1200, M=0.8, Vdc=100

0.3

0.35

0.4

Fig.6. Eleven level CMLI output line voltage with M=0.8 and Fc=1200

Fig.7. FFT analysis of Eleven level CMLI output line voltage with M=0.8 and Fc=1200

400

300

PhaseVoltage(Volt)

200

100

0

-100

-200

-300

-400

0

0.05

0.1

0.15

0.2

0.25

Time(Sec)

Fc=1200, M=0.8, Vdc=100

0.3

0.35

0.4

Fig.8. Eleven level CMLI output Phase voltage with M=0.8 and Fc=1200

Copyright to IJAREEIE

10.15662/ijareeie.2014.0310029

www.ijareeie.com

14004

ISSN (Print) : 2320 3765

ISSN (Online): 2278 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 12, December 2014

Fig.9. FFT analysis of Eleven level CMLI output Phase voltage with M=0.8 and Fc=1200

Fig 10 and Fig 12 shows the output Line and phase voltages of eleven level CMLI and Fig 11 and Fig 13 shows the

corresponding FFT analysis, with modulation index M=1 and carrier frequency Fc=1200. From the Fig 11 and 13 all

the carrier and associated sideband harmonics up to 2Ncth carrier group i.e up to 12 kHz frequency was cancelled. It was

due to the phase shifted PWM strategy. And also the peak value of phase voltage is M*Nc*Vdc it can verified from the

Fig 12.Peak value of phase and line voltages are increased if the modulation index is increased.

1000

LineVoltage(Volt)

500

-500

-1000

0

0.05

0.1

0.15

0.2

0.25

Time(Sec)

Fc=1200, M=1, Vdc=100

0.3

0.35

0.4

Fig.10. Eleven level CMLI output line voltage with M=1 and Fc=1200

Fig.11. FFT analysis of Eleven level CMLI output line voltage with M=1 and Fc=1200

500

400

P

haseV

oltage(V

olt)

300

200

100

0

-100

-200

-300

-400

-500

0

0.05

0.1

0.15

0.2

0.25

Time(Sec)

Fc=1200, M=1, Vdc=100

0.3

0.35

0.4

Fig.12. Eleven level CMLI output Phase voltage with M=1 and Fc=1200

Copyright to IJAREEIE

10.15662/ijareeie.2014.0310029

www.ijareeie.com

14005

ISSN (Print) : 2320 3765

ISSN (Online): 2278 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 12, December 2014

Fig.13. FFT analysis of Eleven level CMLI output Phase voltage with M=1 and Fc=1200

Fig.14. FFT analysis of Eleven level CMLI output line voltage with M=1 and Fc=900

Fig 14 and 15 shows the FFT analysis of line and phase voltages for modulation index M=1 and the carrier frequency

Fc=900 Hz. It is observed that from the FFT analysis of line voltages and phase voltages, the total harmonic distortion

is reduced if the frequency for carrier signals is increased. Fig 16 shows the FFT analysis of phase voltage for

modulation index M=0.8 and carrier frequency Fc=900.

Fig.15. FFT analysis of Eleven level CMLI output Phase voltage with M=1 and Fc=900

Fig.16. FFT analysis of Eleven level CMLI output Phase voltage with M=1 and Fc=900

Copyright to IJAREEIE

10.15662/ijareeie.2014.0310029

www.ijareeie.com

14006

ISSN (Print) : 2320 3765

ISSN (Online): 2278 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 12, December 2014

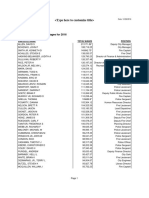

Fig 17 shows the load current for modulation index M=1 and carrier frequency Fc=1200, and Fig 18 shows FFT

analysis of the load current. It is observed that the load current seen almost sinusoidal wave and the harmonics it

consists of is very low. Table 1 shows the comparison of output voltage THDs for different carrier frequencies and

different Modulation indexes.

30

Current(Amps)

20

10

0

-10

-20

-30

0

0.05

0.1

0.15

0.2

Time(Sec)

0.25

0.3

0.35

0.4

Fig.17. Eleven level CMLI output load current with M=1 and Fc=1200

Fig.18. FFT analysis of Eleven level CMLI load current with M=1 and Fc=1200

S.No

Carrier

Frequency(Fc)

Modualtion

Index(M)

1200

0.8

%THD

(Phase

Voltage)

13.70

2

3

1200

900

1

0.8

10.96

13.71

900

11.03

Table 1. Comparison of results

V.CONCLUSION

Eleven level CMLI connected with RL load was simulated by using new phase shifted carrier PWM technique. The

results were compared and shown in Table 1 for different carrier frequencies and for different modulation indexes. The

total harmonic distortion was reduced by increasing carrier frequency. In this method the carrier frequency should

always be high. In this technique the lower order harmonics were gets cancelled up to the 2Ncth carrier group. This

technique can be increased to any number of levels but to implement practically the number of components and cost is

increased

Copyright to IJAREEIE

10.15662/ijareeie.2014.0310029

www.ijareeie.com

14007

ISSN (Print) : 2320 3765

ISSN (Online): 2278 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 12, December 2014

ACKNOWLEDGMENT

We thank the University Grants Commission (UGC), New Delhi, for providing support to carryout research on

Multilevel Inverters under the Major research project.

REFERENCES

[1] J.Rodriguez, S.Bernet, B.Wu, J.O.Pontt, and S.Kouro, Multilevel voltage-source-converter topologies for industrial medium-voltage drives,

IEEE Trans.Ind.Electron., vol.54, no.6,pp.2930-2945, Dec.2007.

[2] P.W.Hammond, A new approach to enhance power quality for medium voltage AC drives, IEEE Trans. Ind.Appl., vol.33, no.1, pp.202-208,

Jan./Feb. 1997.

[3] J.Rodriguez, J.S.Lai, and F.Z.Peng, Multilevel inverters: A survey of topologies, control and applications, IEEE Trans.Ind.Electron., vol.49,

no.4, pp.724-738, Aug.2002.

[4] B.P.McGrath, and D.G.Holmes, Multicarrier PWM Strategies for Multilevel Inverters, IEEE Trans.Ind.Electron., vol.49, No.4,pp.858-867,

Aug.2002

[5] M.Malinowski, K.Gopakumar, J.Rodriguez and A.Perez, A Survey on Cascaded Multilevel Inverters, IEEE Trans.Ind.Electron, vol.57, No.7,

pp.2197-2205, July 2010

[6] C.Govindaraju and K.Baskaran, Efficient Sequential Switching Hybrid-Modulation Techniques for Cascaded Multilevel Inverters, IEEE

Trans. Power Electronics, vol.26, No.6, pp.1639-1648, June 2011.

[7] R.Gupta , A.Ghosh, and A.Joshi, Switching characterization of cascaded multilevel-inverter-controlled systems,IEEE Trans.Ind.Electron.,

vol.55, no.3, pp.1047-1058, Mar.2008.

[8] R.Naderi and A.Rahmati, Phase shifted carrier PWM technique for general cascaded inverters, IEEE Trans.Power Electron., vol.23, no.3, pp.

1257-1269, May 2008.

Copyright to IJAREEIE

10.15662/ijareeie.2014.0310029

www.ijareeie.com

14008

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Calculus CourseDocument354 pagesCalculus CourseMefisto ElNo ratings yet

- High Performance Direct Torque Control of Induction Motor Drives Using Space Vector ModulationDocument9 pagesHigh Performance Direct Torque Control of Induction Motor Drives Using Space Vector ModulationMefisto ElNo ratings yet

- A Novel Approach For Modelling and Simulation of Sensor Less BLDC MotorDocument9 pagesA Novel Approach For Modelling and Simulation of Sensor Less BLDC MotorMefisto ElNo ratings yet

- Analise 2Document161 pagesAnalise 2Bruno MartinsNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- BSBITU314 Assessment Workbook FIllableDocument51 pagesBSBITU314 Assessment Workbook FIllableAryan SinglaNo ratings yet

- Aakriti 1Document92 pagesAakriti 1raghav bansalNo ratings yet

- FpsecrashlogDocument19 pagesFpsecrashlogtim lokNo ratings yet

- 2016 W-2 Gross Wages CityDocument16 pages2016 W-2 Gross Wages CityportsmouthheraldNo ratings yet

- Project Management TY BSC ITDocument57 pagesProject Management TY BSC ITdarshan130275% (12)

- This Study Resource Was: For The Next 6 ItemsDocument9 pagesThis Study Resource Was: For The Next 6 ItemsJames CastañedaNo ratings yet

- Contoh Discussion Text Tentang HomeworkDocument8 pagesContoh Discussion Text Tentang Homeworkg3p35rs6100% (1)

- Guidelines For Prescription Drug Marketing in India-OPPIDocument23 pagesGuidelines For Prescription Drug Marketing in India-OPPINeelesh Bhandari100% (2)

- Formula:: High Low Method (High - Low) Break-Even PointDocument24 pagesFormula:: High Low Method (High - Low) Break-Even PointRedgie Mark UrsalNo ratings yet

- Ring and Johnson CounterDocument5 pagesRing and Johnson CounterkrsekarNo ratings yet

- CLG418 (Dcec) PM 201409022-EnDocument1,143 pagesCLG418 (Dcec) PM 201409022-EnMauricio WijayaNo ratings yet

- Product NDC # Compare To Strength Size Form Case Pack Abcoe# Cardinal Cin # Mckesson Oe # M&Doe#Document14 pagesProduct NDC # Compare To Strength Size Form Case Pack Abcoe# Cardinal Cin # Mckesson Oe # M&Doe#Paras ShardaNo ratings yet

- Binge Eating Disorder ANNADocument12 pagesBinge Eating Disorder ANNAloloasbNo ratings yet

- Chapter 4 - Basic ProbabilityDocument37 pagesChapter 4 - Basic Probabilitynadya shafirahNo ratings yet

- Gaming Ports MikrotikDocument6 pagesGaming Ports MikrotikRay OhmsNo ratings yet

- Feed-Pump Hydraulic Performance and Design Improvement, Phase I: J2esearch Program DesignDocument201 pagesFeed-Pump Hydraulic Performance and Design Improvement, Phase I: J2esearch Program DesignJonasNo ratings yet

- Bank Danamon Organization ChartDocument4 pagesBank Danamon Organization ChartFaisal Agus NugrahaNo ratings yet

- Conservation Assignment 02Document16 pagesConservation Assignment 02RAJU VENKATANo ratings yet

- Business-Communication Solved MCQs (Set-3)Document8 pagesBusiness-Communication Solved MCQs (Set-3)Pavan Sai Krishna KottiNo ratings yet

- Grade 9 Science Biology 1 DLPDocument13 pagesGrade 9 Science Biology 1 DLPManongdo AllanNo ratings yet

- Faa Data On B 777 PDFDocument104 pagesFaa Data On B 777 PDFGurudutt PaiNo ratings yet

- DS Agile - Enm - C6pDocument358 pagesDS Agile - Enm - C6pABDERRAHMANE JAFNo ratings yet

- Predator U7135 ManualDocument36 pagesPredator U7135 Manualr17g100% (1)

- Pantalla MTA 100Document84 pagesPantalla MTA 100dariocontrolNo ratings yet

- Manual E07ei1Document57 pagesManual E07ei1EiriHouseNo ratings yet

- QP 12math Term 1Document11 pagesQP 12math Term 1sarthakNo ratings yet

- General Chemistry 2 Q1 Lesson 5 Endothermic and Exotheric Reaction and Heating and Cooling CurveDocument19 pagesGeneral Chemistry 2 Q1 Lesson 5 Endothermic and Exotheric Reaction and Heating and Cooling CurveJolo Allexice R. PinedaNo ratings yet

- Frellwits Swedish Hosts FileDocument10 pagesFrellwits Swedish Hosts FileAnonymous DsGzm0hQf5No ratings yet

- Implications of A Distributed Environment Part 2Document38 pagesImplications of A Distributed Environment Part 2Joel wakhunguNo ratings yet

- Water Pump 250 Hrs Service No Unit: Date: HM: ShiftDocument8 pagesWater Pump 250 Hrs Service No Unit: Date: HM: ShiftTLK ChannelNo ratings yet