Professional Documents

Culture Documents

PB NPS-400

Uploaded by

Sceptic GrannyOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

PB NPS-400

Uploaded by

Sceptic GrannyCopyright:

Available Formats

NETWORK

PROCESSORS

PRODUCT BRIEF

NPS-400

400Gbps NPU for Smart Networks

A game changing network processor that merges NPU performance with

CPU flexibility and ease of programmability. The NPS-400 C-programmable

packet processor at ultra-high 400-Gigabit throughput, supports all 7-layers

with integrated traffic management to enable the next wave of highperformance intelligent carrier routers, data-center network equipment, and

accelerates virtualized functions in emerging SDN and NFV networks.

Innovative CTOPs

The NPS provides C-programming capabilities

and a standard Linux OS for both data and control

plane. CTOPs (C programmable Task Optimized

Processors) offer the benefit of a C based

programming environment, while retaining all the

benefits of key TOP specialized instructions, which

are accessed thru in-line functions. Unlimited

code space for control plane and debugging

features, a Linux environment that offers access

to all the standard toolchain, debugger and other

features familiar to programmers.

and verify both control-plane and data-plane applications for the NPS. EZdk provides an Eclipsebased IDE (Integrated Development Environment),

optimized GNU toolchain and Linux kernel, control

and data plane software development kits, reference applications, and SW simulator.

Development Tools

EZide Eclipse-based Integrated

Development Environment

Industry standard-based symbolic software

debugging and profiling tools (GDB, perf) with

multi-core support

The NPC architecture is built on an array of

symmetrical processors, CTOPs, which run

software in a run to completion model. The core

hardware multi-threading conceals the latency of

memory accesses.

System on a chip (SoC) level performance

profiling and hot-spot analysis tools, allowing

detection of system-wide bottlenecks (DDR,

etc.)

The EZ-ISA instruction set, which includes legacy

TOP instructions, provides a smooth transition

from the NP-5 TOP to the NPS CTOP architecture.

GUI based editor for generating NPS device

configurations

Hardware level debugging via JTAG interface

NPS Programming

GUI based interface for exploring and

controlling NPS device status

EZdk Software Development Kit

Enables operation with the real hardware

targets and the software simulation tools

Mellanoxs Software Development Kit (EZdk) is a

comprehensive set of design and runtime tools for

developers, enabling a short time-to-market for

new designs based on Mellanoxs C programmable

NPS. EZdk allows developers to design, implement

2016 Mellanox Technologies. All rights reserved.

Supported on x86-64 development stations

running Linux

EZsim Instruction accurate simulation of

HIGHLIGHTS

FEATURES

C programmable 400Gbps Network Processor

for Smart Networks

Based on 10 times smaller and faster C

programmable Task Optimized Processors

(CTOPs)

NPU with 256 CTOPs, 4K threads, Traffic

Manager, DPI, Security, Search Engine and

960Gbps I/O in one chip

400-Gigabit wire-speed packet processing

Advanced services and full layers 2-7 stateful

processing

Easy to use C-programmable and Linux

operating system

Addressing carrier, cloud and data-center

networking equipment

Switching, routing, SDN/OpenFlow and

virtualization of network elements, load

balancing, DPI, TCP offload, firewall, VPNs,

intrusion detection/ prevention, network

analytics and more

TARGET APPLICATIONS

Carrier Ethernet switch/router line cards and

services cards

Data center and carrier appliances

Mobile packet network infrastructure

evolved packet core (EPC) routers

Software defined networking (SDN),

OpenFlow and virtual networking

Load balancing

Firewall and intrusion detection and

prevention systems (IDS/IPS)

IPsec and SSL VPN gateways

TCP offload

Traffic analytics and network monitoring

WAN optimization

DPI and lawful interception

Session border controllers

For illustration only. Actual products may vary.

NPS-400 400Gbps Network Processing Unit for Smart Networks

the CTOPs and the NPS SoC supporting

the running of full multi-core data plane

and control plane applications, including

SMP (Symmetric Multi-Processing) Linux.

acceleration block, as well as for creation

and management of lookup structures.

Access control list compiler for

Mellanoxs algorithmic TCAM

accelerators

Operating System

SMP Linux 4.x kernel ported to NPS

architecture to run on the CTOPs

PCRE (Perl Compatible Regular

Expression) rule compiler for Mellanoxs

DPI (Deep Packet Inspection) accelerators

Zero Overhead Linux (ZOL) supporting

bare-metal performance with the same

familiar and convenient Linux user-space

development environment

The control plane environment libraries

may be run on an external control CPU

or on one or more of the NPS HW

threads implementing the control CPU

functionality, for fully autonomous

operation without requiring an external

control CPU.

Linux file system and standard runtime

libraries

Device drivers for the NPS hardware

peripherals, such as the Ethernet network

interfaces and the UART interface for

console services

Boot loader (U-Boot)

Industry standard GNU toolchain

Data Plane Environment Libraries

Data-plane services libraries providing

a C-based application programming

interface (API) for data-plane applications

running on the NPS, abstracting the

complexities of the underlying CTOP core

instruction set and various hardware

accelerators.

Control Plane Environment Libraries

Control-plane services libraries providing

a C-based API for control-plane

applications for the NPS, abstracting the

complexities of the underlying hardware

interface. The control-plane service

libraries are used for configuration and

management of the NPS, including

its network and memory interfaces,

embedded traffic manager and statistics

page 2

Zero Overhead Linux (ZOL) Environment

Mellanox provides an integrated SMP Linux

runtime environment for both control and data

plane applications running on the NPS CTOP

cores.

To achieve the performance requirements for

data plane applications, Mellanoxs optimized

Linux kernel provides deterministic performance for data plane applications on par with

a bare metal application, while enjoying the

benefits of a standard OS support.

The data plane application processes run

on dedicated hardware threads, and are

isolated from all uncontrolled interferences.

They do not perform context switches unless

explicitly requested by the application or the

debugger, and are isolated from all interrupt

sources, including timer interrupts. The data

plane applications access all performance

critical code and data through a fixed memory

mapping table, avoiding any costly translation

lookaside buffer (TLB) misses. The data

Reference Applications

- IPsec gateway

- DPI based application recognition

- HTTP load balancer

- Carrier Ethernet switch/router

- OpenFlow forwarding plane

- Lawful interception & content filtering

Development tools

EZide - Eclipse-based IDE

EZsim - SoC SW simulator

Middleware

- Stateful flow table library

- ODP support

- PCIe endpoint stack

Data Plane Environment

Control Plane Environment

APIs for data plane services

APIs for control plane services

OS and Runtime Environment

- SMP Linux 4.x

- Linux file system

- Boot loader (U-Boot)

- Programming tools (GNU toolchain)

2016 Mellanox Technologies. All rights reserved.

plane applications interface directly with the

hardware services through the data plane

user-space library, removing the need for

context switching between user and kernel

space modes.

The data plane applications are developed,

controlled and debugged as standard Linux

processes. They can be started/ killed thru a

Linux shell, viewed using the standard ps or

top commands and debugged via the standard GDB GNU debugger. Furthermore, the

applications can perform any standard Linux

library and system call (e.g., printf). The

Linux kernel still provides the initialization,

exception handling and debug services for the

data plane applications, but will not involuntarily interrupt these applications unless there

is an exception (e.g. divide by zero) or when

requested by a debug process.

Software Libraries

Mellanox provides a rich set of software

middleware and reference applications.

Middleware is comprised of reusable building

blocks, modules or stacks that build on the

basic data and control plane API to facilitate

the fast and simple creation of applications.

Stateful Flow Library

OpenDataPlane Support

PCIe Endpoint Stack

Reference Applications

Carrier Ethernet Switch/Router

OpenFlow Forwarding Plane

Lawful Interception and Pattern

Matching

IPsec Gateway

DPI based Application Recognition

HTTP Load Balancer

For more information refer to the NPS Software Libraries Product Brief.

Reference Design

Mellanox also offers an NPS Evaluation

System, a compact hardware platform, which

can be used to accelerate the development of

the target hardware & software applications.

NPS-400 400Gbps Network Processing Unit for Smart Networks

page 3

SAMPLE APPLICATIONS

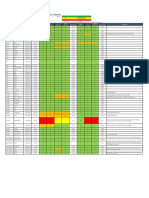

L2-L7 LINE CARD WITH FIC, TCAM AND HOST CPU

This figure shows an over-subscribed line card. The connection to

the switch fabric is provided by an Interlaken 24 lane interface via

a FIC. An external TCAM for applications requiring large ACL tables

is connected using an Interlaken LookAside 24 lane interface. An

external host CPU is connected for control applications that require

low memory latencies. The CPU is connected with an 8Gbps 1-lane

PCIe-host Gen 3 port that enables the CPU to access the NPU control

registers after boot.

12x DDR3/4 16b

SDRAM

Optics

CPU

ILKN-LA

24x 12.5Gbps

TCAM

SDRAM

Line Card

12x DDR3/4 16b

SDRAM

CAUI

2x 100GE

Optics

Optics

2x 100GE/

8x 40GE/

32x 10GE

NPS-400

PCIe

1x 8Gbps

CPU

SDRAM

12x DDR3/4 16b

SDRAM

4x 100GE/

12x 40GE/

48x 10GE

SDRAM

NPS-400

IEEE 802.1Qbb Priority based flow control (PFC). NPS

supports PFC on all Ethernet links.

SDRAM

IEEE 802.1Qau (Quantized) Congestion Notification (CN

and QCN). NPS-400 application supports the standard

form and E2E CN proprietary messages.

48x 10.3125Gbps

48x 10GBASE-KR

nx 10GBASE-KR

SDRAM

Boot

Flash

NPS-400

Up to m switch cards

nx 10GBASE-KR

Optics

48x 10.3125Gbps

48x 10GBASE-KR

Backplane Connector

Optics

Boot

Flash

NPS-400

Backplane Connector

SDRAM

4x 100GE/

12x 40GE/

48x 10GE

Boot

Flash

nx 10GBASE-KR

Optics

Multiple NPS-400 devices per line card

SDRAM

Pizza Box

Backplane Connector

Up to n line

cards

The fabric switches support Data Center Bridging (DCB). The DCB

requires:

FIC

12x DDR3/4 16b

SYSTEM APPLICATION FOR MULTI-TBPS OPERATION

This figure exemplifies a multi-Terabit/second system with multiple

480Gbps line cards inter-connected through fabric switch cards. The

system provides:

Multi-Tbps of non-blocking, QoS, unicast and multicast

operation

Multi-terabit chassis for mega data centers, enterprise and

service provider applications

NPS-400

PCIe

1x 8Gbps

PIZZA BOX APPLIANCE

In this figure, the NPS provides the entire network layer 2-7 processing

and traffic management. The NPS offloads these functions from the

CPU. The CPU receives selected packets from the NPS for exceptions

handling, and performs all the protocol, management and application

tasks. The CPU is connected with a 1-lane PCIe Gen 3 port providing

8Gbps throughput. PCIe enables the CPU to access the NPU control

registers after boot.

Multiple Ethernet switches

ILKN

24x

12.5Gbps

Backplane

Coinnector

4x 100GE/

12x 40GE/

48x 10GE

m

Ethernet

Switch

DCB Enabled

Switchcard

Ethernet

Switch

DCB Enabled

Switchcard

Ethernet

Switch

DCB Enabled

Line Card

Switchcard

Typical number of switch cards (m) is 4 (with 100GbE), 12 (with 40GbE), 48 (with 10GbE).

802.1Qaz Enhanced Transmission Selection by runtime configuration of TM via one of the CTOPs.

Each NPS allocates 48x 10GBASE-KR lanes for fabric connectivity. The line card distributes the fabric traffic for even load distribution over the backplane

fabric lanes. Each line card maintains virtual output queuing (VoQ) per system output port CoS. In-band signaling of end-to-end QCN messages maintains

the CoS aware fabric traffic engineering scheme.

Ordering Part

Number

Description

20785000

NPS-400 RoHS 400-Gigabit, C-programmable, 7-layer NPU with integrated traffic management and crypto

20785700

NPS-400 RoHS 400-Gigabit, C-programmable, 7-layer NPU with integrated traffic management, no crypto

350 Oakmead Parkway, Suite 100, Sunnyvale, CA 94085

Tel: 408-970-3400 Fax: 408-970-3403

www.mellanox.com

Copyright 2016. Mellanox Technologies. All rights reserved.

Mellanox, Mellanox logo, EZchip, EZchip logo, and Tilera are registered trademarks of Mellanox Technologies, Ltd. NPS-400 is a trademark of Mellanox Technologies, Ltd. All other trademarks are property of their

respective owners.

#27-8028-03 Rev. 2.1

You might also like

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- 4.6 Null Space, Column Space, Row SpaceDocument10 pages4.6 Null Space, Column Space, Row SpaceSceptic GrannyNo ratings yet

- Linear Line Voltage Halogen Under Cabinet Fixture: NUL-315 NUL-321Document1 pageLinear Line Voltage Halogen Under Cabinet Fixture: NUL-315 NUL-321Sceptic GrannyNo ratings yet

- Apm Terminals Operations Status Update 04072017 17h00 Cet Status Per TerminalDocument2 pagesApm Terminals Operations Status Update 04072017 17h00 Cet Status Per TerminalSceptic GrannyNo ratings yet

- Enrollment Kits PDFDocument4 pagesEnrollment Kits PDFSceptic GrannyNo ratings yet

- 4.2 Null Spaces, Column Spaces, & Linear Transformations: M A A A A ADocument6 pages4.2 Null Spaces, Column Spaces, & Linear Transformations: M A A A A ASceptic GrannyNo ratings yet

- ReadrDocument34 pagesReadrSceptic GrannyNo ratings yet

- Annals 07 03 PDFDocument10 pagesAnnals 07 03 PDFSceptic GrannyNo ratings yet

- Kenyon College Dana Paquin Paquind@kenyon - EduDocument3 pagesKenyon College Dana Paquin Paquind@kenyon - EduSceptic GrannyNo ratings yet

- Company Profile Jan de Nul Group enDocument8 pagesCompany Profile Jan de Nul Group enSceptic GrannyNo ratings yet

- The Structure of Nul! Lagrangians: P Olvert and J Sivaloganathan$Document10 pagesThe Structure of Nul! Lagrangians: P Olvert and J Sivaloganathan$Sceptic Granny100% (1)

- Throwers Ten Exercise Program: What You Will NeedDocument7 pagesThrowers Ten Exercise Program: What You Will NeedSceptic GrannyNo ratings yet

- 10year Impact Study 1325Document50 pages10year Impact Study 1325Sceptic GrannyNo ratings yet

- Successful Public/Private Partnerships: Ten Principles ForDocument42 pagesSuccessful Public/Private Partnerships: Ten Principles ForSceptic GrannyNo ratings yet

- Tenx Whitepaper FinalDocument51 pagesTenx Whitepaper FinalSceptic GrannyNo ratings yet

- Salzburg Report Final.1129817011146Document10 pagesSalzburg Report Final.1129817011146Sceptic GrannyNo ratings yet

- See Sections 203A and Rule 114ADocument4 pagesSee Sections 203A and Rule 114ASceptic GrannyNo ratings yet

- The Research Data Group 2012 v7 FinalDocument4 pagesThe Research Data Group 2012 v7 FinalSceptic GrannyNo ratings yet

- Belsorp MaxDocument6 pagesBelsorp MaxSceptic GrannyNo ratings yet

- 9780822955672exr PDFDocument1 page9780822955672exr PDFSceptic GrannyNo ratings yet

- Bel Brochure BM-A1-4SHD 2015Document2 pagesBel Brochure BM-A1-4SHD 2015Sceptic GrannyNo ratings yet

- Bel Air District PWS ID: MD0120003: A Message From The Maryland American Water PresidentDocument9 pagesBel Air District PWS ID: MD0120003: A Message From The Maryland American Water PresidentSceptic GrannyNo ratings yet

- Moisture Determination Balance Di1751 m44Document36 pagesMoisture Determination Balance Di1751 m44Sceptic GrannyNo ratings yet

- BEL AT A GlanceDocument22 pagesBEL AT A GlanceSceptic GrannyNo ratings yet

- Apocrypha Bel and The Dragon of The King James Bible 1611Document7 pagesApocrypha Bel and The Dragon of The King James Bible 1611Sceptic GrannyNo ratings yet

- Hepatitis A: Questions and Answers: Information About The Disease and VaccinesDocument4 pagesHepatitis A: Questions and Answers: Information About The Disease and VaccinesSceptic GrannyNo ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- VSP 70-03-37-00-M110Document5 pagesVSP 70-03-37-00-M110lgrypvNo ratings yet

- Wireless Sensor Network & Security: Presented byDocument21 pagesWireless Sensor Network & Security: Presented byamsaluNo ratings yet

- Host Driver Logs CurrentDocument5,726 pagesHost Driver Logs CurrentZafkielNo ratings yet

- UE D65 V UE D65 W UE D67 W UA D6400U UA D6600W: For LED TV D6000 SeriesDocument38 pagesUE D65 V UE D65 W UE D67 W UA D6400U UA D6600W: For LED TV D6000 SeriesJorge Fernando de Tivanta100% (2)

- Installing Exchange 2010 StepDocument4 pagesInstalling Exchange 2010 StepnangakumdistNo ratings yet

- PB-AppPerf 24622 V03 03-15-12Document2 pagesPB-AppPerf 24622 V03 03-15-12jcy1978No ratings yet

- Ict 2112 Long Quiz 4Document13 pagesIct 2112 Long Quiz 4Luisa RadaNo ratings yet

- Configuracion FSgatewayDocument9 pagesConfiguracion FSgatewayandrysbotabanNo ratings yet

- Hpe6-A15 - AccpDocument93 pagesHpe6-A15 - AccpNguyen Thai VinhNo ratings yet

- Incoming Ports: Product Purpose Ports ConfigurableDocument6 pagesIncoming Ports: Product Purpose Ports ConfigurableAyan NasNo ratings yet

- IoT Malware Detection PavlovskyDocument6 pagesIoT Malware Detection PavlovskykgbNo ratings yet

- Design Amba Based Ahb To Apb Bridge Using Verilog HDL: Prarthi Bhatt, Prof..Devang ShahDocument5 pagesDesign Amba Based Ahb To Apb Bridge Using Verilog HDL: Prarthi Bhatt, Prof..Devang ShahPotnuru KarishmaNo ratings yet

- Credential Harvesting Via MiTM Burp Suite TutorialDocument4 pagesCredential Harvesting Via MiTM Burp Suite TutorialAlison FreitasNo ratings yet

- Lecture 8 - Security at The Application LayerDocument34 pagesLecture 8 - Security at The Application Layermonaabdelaziz963No ratings yet

- SKALE Network Token EconomicsDocument1 pageSKALE Network Token EconomicsYusanYPNo ratings yet

- Protocol Family Encapsulations ChartDocument1 pageProtocol Family Encapsulations ChartbhzNo ratings yet

- AN5516-06 Optical Line Terminal Equipment Feature DescriptionDocument204 pagesAN5516-06 Optical Line Terminal Equipment Feature DescriptionbigdrsmithNo ratings yet

- Privilege Access Levels CiscoDocument3 pagesPrivilege Access Levels CiscoANGEL GuzmanNo ratings yet

- CS169: Mobile Wireless Networks: Lab1: NS3 IntroductionDocument17 pagesCS169: Mobile Wireless Networks: Lab1: NS3 IntroductionmwaraNo ratings yet

- Information: System Abbreviations Core NetworkDocument180 pagesInformation: System Abbreviations Core NetworkMokbelNo ratings yet

- NK44W0H-1TWDD Datasheet V5.5.120 20200821Document6 pagesNK44W0H-1TWDD Datasheet V5.5.120 20200821kybikNo ratings yet

- (Presentation) GPON Vs EPONDocument14 pages(Presentation) GPON Vs EPONLiêm TrầnNo ratings yet

- Android - ESewa SDK DocumentationDocument17 pagesAndroid - ESewa SDK Documentation1117No ratings yet

- Ise Use Case Secure Wired AagDocument2 pagesIse Use Case Secure Wired AagMalal NdiayeNo ratings yet

- EntraPass Corporate Detailed Synopsis - V8.10Document14 pagesEntraPass Corporate Detailed Synopsis - V8.10Juan D DiazNo ratings yet

- NSC-7298 Wer.1.0Document256 pagesNSC-7298 Wer.1.0RafNo ratings yet

- DP Bluetooth 15102 DriversDocument866 pagesDP Bluetooth 15102 DriversRaphael Fagundes LopesNo ratings yet

- Wideband Cdma (Wcdma)Document22 pagesWideband Cdma (Wcdma)Thang TranNo ratings yet

- VMS Presentation 2018Document17 pagesVMS Presentation 2018angga deri heryansyahNo ratings yet

- Kap3 Modbus Com 092009Document140 pagesKap3 Modbus Com 092009FelipeNo ratings yet