Professional Documents

Culture Documents

Tema 1 CPU

Uploaded by

Jak MartinOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Tema 1 CPU

Uploaded by

Jak MartinCopyright:

Available Formats

Fundamentos de Hardware Componentes Fsicos: la CPU Pg.

- 1 de 7

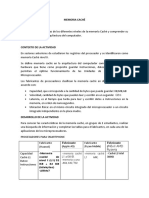

2.- COMPONENTES FSICOS: EL PROCESADOR O CPU

ESQUEMA DE BLOQUES FUNCIONALES DE UNA CPU CON ARQUITECTURA DE VON

NEWMAN

MEMORIA

CPU

(procesador)

RAM

Dispositivos

Dispositivos

ALU

UC

UNIDAD DE E/S

S

Registros

Coprocesador

Memoria masiva o auxiliar

reloj.- ciclo MHz (millones de ciclos por segundo)

longitud de palabra: n de bits que se transmiten simultneamente entre las unidades del ordenador, coincide

normalmente con el n de bits de las instrucciones datos con los que opera el procesador. (386, 486 y

pentium 32 bits)

PROCESADOR O CPU

- Componentes principales: registros, ALU y lgica de control.

a) Contiene REGISTROS en los que se pueden almacenar datos (usados por la ALU) o direcciones de memoria.

Algunos de los ms importantes son:

Acumulador (RA): Usado para operar con otro registro o bien con el contenido de una posicin de memoria

y almacenar en l el resultado.

Asociado a ste y a la ALU, existe un conjunto de circuitos biestables (0,1) que informan del estado de la

ltima operacin realizada en la ALU.

Ej.- Acarreo, Indicador de signo, Indicador de cero, Indicador de paridad, Indicador de desbordamiento,

etc.

Juntos forman lo que se llama Palabra de Estado (SW)

Fundamentos de Hardware Componentes Fsicos: la CPU Pg.- 2 de 7

Registros de Direccin de Memoria (DM) y Registro de Memoria (RM). El procesador se comunica con la

memoria mediante el Bus de direcciones y el Bus de datos.

Bus de datos: dato a escribir o leer en/desde la memoria

Bus de direcciones: direccin del dato a escribir/leer en la memoria.

Adems dispone de una Seal de control (R/W) que indica si se va a leer o a escribir.

Los datos que viajan por estos dos buses se almacenan temporalmente en los correspondientes registros

DM y RM.

Registro de Instruccin (RI):

CO: Cdigo operacin a realizar

MD: Modo de direccionamiento

CDE: Campo de direccin efectiva de la informacin1

El programa que el procesador est ejecutando estar almacenado en RAM. Para ejecutar ese programa,

el procesador toma una a una cada instruccin y la almacena temporalmente en este registro para poder

ejecutarla.

Muy relacionado con ste est el Contador de Programa (CP), que guarda la direccin de memoria RAM de

la instruccin que se est ejecutando. ste es un contador binario ascendente.

b) ALU: Est formada por circuitos electrnicos que realizan operaciones aritmticas y lgicas. Como hemos dicho, para

operar guarda los datos y sus resultados en los registros necesarios.

c) LGICA DE CONTROL: Son los circuitos que generan las seales de control que la UC manda a todos los dispositivos.

El reloj marca el ritmo con el que se realizan todas las operaciones, (a cada pulso una seal, una operacin, etc.),

todo sincronizado a ms frecuencia, mayor rapidez. La frecuencia de reloj se mide en MHz o ciclos de reloj por segundo.

Un ciclo es el tiempo que necesita la UC para ejecutar una instruccin, no obstante para incrementar la velocidad se puede

hacer que no todas las instrucciones duren lo mismo (ej.- direccionamiento directo, menos tiempo que indirecto robo

de ciclo). El circuito bsico del reloj suele ser un circuito secuencial llamado temporizador (contador binario ascendente).

Hay dos metodologas para disear la lgica de control:

a) lgica cableada: utilizando puertas lgicas que implementen sistemas combinacionales y secuenciales.

b) Microprogramacin: almacenar en una memoria de slo lectura las micrordenes que hay que seguir para

ejecutar cada instruccin de la CPU. Microprograma FIRMWARE.

1

MD.- Por ejemplo: Inmediato (en la propia instruccin se encuentra el dato efectivo), Directo (en la instruccin se

encuentra la direccin de RAM a la que hay que ir a buscar el dato) e Indirecto (en la instruccin se encuentra la

direccin de RAM en la que se indica a qu otra direccin de RAM hay que ir a buscar el dato).

Fundamentos de Hardware Componentes Fsicos: la CPU Pg.- 3 de 7

PROCESADOR (CPU)

Instrucciones

RA

E

RI

RM

CP

DM

Datos

S

Direcciones

Registros

.

.

.

MEMORIA

sw

Lgica De

Control

De Memoria

R/W

RAM

ALU

reloj

El conjunto de instrucciones de que dispone el procesador, es una lista de todas las operaciones que puede realizar.

Los procesadores de distintas empresas (intel, Motorota, etc) tienen distintos juegos de instrucciones, incluso

procesadores de una misma marca pueden tener distinto conjunto de instrucciones, no obstante se intenta agrupar los

procesadores por familias con conjuntos de instrucciones semejantes, de forma que cada vez que se desarrolla uno

nuevo de una familia, contiene las instrucciones anteriores y otras ms, esto permite que el software desarrollado para

un procesador pueda correr en procesadores nuevos de la misma familia. Esta estrategia se conoce como ESCALABILIDAD.

EJECUCIN DE UN PROGRAMA

-

Cuando un programa se va a ejecutar se almacena en posiciones consecutivas de memoria RAM.

La direccin de inicio del programa se carga en el CP y de ah se pasa a DM, indicando la UC R/W=1, esto es,

leer.

Pasado el tiempo necesario (tiempo de acceso a memoria), pasar al bus de datos / instrucciones la primera

instruccin del programa que se cargar en RM.

De ah pasa al RI

El CP se incrementa, apuntando as a la siguiente instruccin.

A continuacin hay que ejecutar la instruccin contenida en IR, para ello es decodificada y :

Si la instruccin no es ALU, la UC genera las seales de control necesarias para que

intervengan los elementos necesarios.

Si la instruccin es ALU, la UC genera las seales necesarias para indicar a la ALU que realice

la operacin.

Fundamentos de Hardware Componentes Fsicos: la CPU Pg.- 4 de 7

Segn esto, en la ejecucin de una instruccin hay dos fases: captacin y ejecucin.

CAPTACIN:

DM CP

RM M(DM)

RI RM

CP CP+1

EJECUCIN

Ejecutar las operaciones indicadas en el CodOp de RI.

Por tanto, para ejecutar una instruccin hay que hacer varias microinstrucciones (microoperaciones)

Ejemplo de procesamiento n 1

Suponemos la calculadora de Windows para efectuar 4x46=184. Se supone que 4, 46 y x ya estn en

memoria (la UC los mand). Al pulsar Intro, el programa de la calculadora manda a la CPU una instruccin de

multiplicar:

1.- Carga la instruccin desde memoria hasta RI

2.- Busca microcdigo asociado.

3.- Ejecuta microcdigo.

Microcdigo:

1.

2.

3.

4.

Carga primer nmero en R4

Carga segundo nmero en R5

Multiplica2 R4 por R5 y deja el resultado en R6

Guarda en memoria R6

Pasos:

R4 4 (1 instruccin microcdigo)

R5 46 (2 instruccin microcdigo)

Pasa control a la ALU (3 instruccin microcdigo)

ALGORITMO DE MULTIPLICACIN EN BINARIO: Rotar bits un lugar a la izquierda en cada multiplicacin por 2. Por 4,

dos veces.

As: 46)2=00101110)2 x 4)10= 10111000)2

Fundamentos de Hardware Componentes Fsicos: la CPU Pg.- 5 de 7

Enviar 184 a memoria (4 instruccin microcdigo)

Ejemplo de procesamiento n 2

Suponemos ordenador con:

-

Palabras de 16 bits. (2B XXXX)16)

Posicin de memoria 0032)16 se encuentra la instruccin 3BC7)16 que suma A + M(R7). El resultado se deja en

A.

R7 54C2)16

54C2)16 357A)16

A 274A)16

Indicar microoperaciones y seguimiento de CP, DM, RM,RI y A.

274A

.

A(R0)

.

.

54C2

.

.

R7

.

.

274A

.

Rn

RAM

RM

0032)16

3BC7

54C2)16

357A

3BC7 / 357A

DM

0032 / 54C2

CP

0032/0033

RI

3BC7

FASE

CAPTACIN

EJECUCIN

MICRO-OPERACIN

CP

RI

RM

DM

----

0032

---

274A

---

---

DM CP

0032

---

274A

---

0032

RM M(DM)

0032

---

274A

3BC7

0032

RI RM

0032

3BC7

274A

3BC7

0032

CP CP+1

0033

3BC7

274A

3BC7

0032

CM R7

0033

3BC7

274A

3BC7

54C2

Fundamentos de Hardware Componentes Fsicos: la CPU Pg.- 6 de 7

Captacin ss.

RM M(DM)

0033

3BC7

274A

357A

54C2

A A+RM

0033

3BC7

274A + 357A

357A

54C2

()

Ejercicio:

Suponemos un ordenador con palabras de 16 bits.

En la posicin de memoria 0010)16 se encuentra la instruccin C532)16 que carga en R5 el contenido de la

posicin de memoria F212)16.

En la posicin F212)16 se encuentra la instruccin 0005)16

En la posicin siguiente (0011)16), se encuentra la instruccin C032)16 que carga en el acumulador el

contenido de F213)16. En la F213 se encuentra 0002)16.

En la posicin siguiente, se encuentra A2B7)16 que suma el contenido del acumulador con R5 y deja el

resultado en A.

Hacer el seguimiento de microoperaciones.

INTERRUPCIONES

Una interrupcin es una parada de la ejecucin del programa en curso antes de su finalizacin, para ejecutar otro

programa que es el procedimiento de gestin de la interrupcin. Cuando ste finaliza, se contina con la ejecucin del

primer programa.

Algunas causas:

a) Fallo de alimentacin. Si el ordenador dispone de dispositivos auxiliares que detecten una inminente cada de

tensin, se puede lanzar una interrupcin que salve informacin.

b) Anomala hardware. En este caso, hay una interrupcin que lanza un mensaje indicando del fallo.

c) Peticin de E/S de un perifrico. Por ejemplo, el teclado.- Buffer Intro Peticin interrupcin atencin

de la interrupcin.

d) Desbordamiento (en un clculo matemtico, por ejemplo)

e) Gestin de tiempo compartido: multitarea. Se usa el reloj de tiempo real para asignar tiempos a cada uno de

los programas que se estn ejecutando.

f) Violacin de la proteccin de memoria. Un programa invade la zona de memoria de otro.

g) Peticiones del usuario, como por ejemplo, ctrl.+Alt+Supr o ctrl.+C.

Fundamentos de Hardware Componentes Fsicos: la CPU Pg.- 7 de 7

El proceso que se sigue para gestionar una interrupcin es (suponiendo que despus se contina en el programa

interrumpido):

1. Peticin de interrupcin: Se hace por medio de una seal elctrica que se enva al procesador (W

seal de estado). Normalmente, antes de atender la interrupcin se termina de ejecutar la

instruccin en curso. Suele haber varias lneas de interrupcin, puede establecerse en caso de

necesidad, cual es la prioritaria. Adems, pueden enmascararse (inhibirse), si el proceso en curso es

muy importante.

2. Tratamiento o atencin de la interrupcin: Comienza con el servicio de inicio de al interrupcin, en el

que se analiza la causa de la interrupcin y se decide si hay que enmascarar otras. Se salva el contenido

de los registros y sw en la memoria principal3 y se pasa el control al procedimiento preferente.

3. Se ejecuta el procedimiento preferente.

4. Se ejecuta el procedimiento de fin de la interrupcin, que normalmente restaura los registros del

procesador sacndolos de la pila y habilita, en su caso, las interrupciones enmascaradas (si las hay).

5. Se pasa el control al programa interrumpido.

Utilizando el sistema PILA (LIFO), en contraposicin al BUFFER (FIFO), o COLA.

You might also like

- Arquitectura Von NeumannDocument8 pagesArquitectura Von NeumannDaniel Medrano IzquierdoNo ratings yet

- Arquitectura de Un OrdenadorDocument27 pagesArquitectura de Un Ordenadorluis - peligroNo ratings yet

- Presentacion No. 2Document28 pagesPresentacion No. 2Einie VegaNo ratings yet

- Tarea 4 ODC - Yael MonteroDocument4 pagesTarea 4 ODC - Yael MonteroYael MonteroNo ratings yet

- UD1. Funcionamiento de Un Ordenador: Sistemas InformáticosDocument26 pagesUD1. Funcionamiento de Un Ordenador: Sistemas InformáticosJavi PerezNo ratings yet

- Arqcom - Jose Ignacio Nota - TP2 - 1K4Document6 pagesArqcom - Jose Ignacio Nota - TP2 - 1K4Nacho NotaNo ratings yet

- FDH t1 Introduccion A Sistemas InformaticosDocument7 pagesFDH t1 Introduccion A Sistemas InformaticosRubenSlimNo ratings yet

- Tema 1Document62 pagesTema 1ferdigar UwUNo ratings yet

- FPP-2-2013 - Tema2 - Plataformas-Programacion-Paralela - Clase2 PDFDocument19 pagesFPP-2-2013 - Tema2 - Plataformas-Programacion-Paralela - Clase2 PDFfranfranscribNo ratings yet

- Diagrama Bloques ComputadoraDocument6 pagesDiagrama Bloques ComputadoraLuis Felipe OsorioNo ratings yet

- Sistemas Operativos - Introduccion A Los ComputadoresDocument9 pagesSistemas Operativos - Introduccion A Los ComputadoresJuan Segundo ArgayoNo ratings yet

- Componentes hardware CPU memoriaDocument4 pagesComponentes hardware CPU memoriaNoeliaNo ratings yet

- Arquitectura de Computadoras (Clase 2) Estructura BásicaDocument39 pagesArquitectura de Computadoras (Clase 2) Estructura BásicaVictor Junco RenteraNo ratings yet

- Curso de ArquitecturaDocument8 pagesCurso de Arquitectura54u1No ratings yet

- Tema 2 y 3. Resumen de ArquitecturaDocument19 pagesTema 2 y 3. Resumen de Arquitecturaroko112No ratings yet

- T2 Arquitectura de Un ComputadorDocument7 pagesT2 Arquitectura de Un ComputadorSamuelNo ratings yet

- 1P TALLER GRUPAL #1 Arquitectura 4SC IIC 22Document6 pages1P TALLER GRUPAL #1 Arquitectura 4SC IIC 22Johnn JimenezNo ratings yet

- Unidad IDocument10 pagesUnidad IJose Manuel Godoy EscribarNo ratings yet

- Unidad 2Document24 pagesUnidad 2Rogelio Anguiano SantosNo ratings yet

- Lógica de CPUDocument5 pagesLógica de CPURafael HernandezNo ratings yet

- Ensayo Unidad 1 Arquitectura CISC y RISCDocument15 pagesEnsayo Unidad 1 Arquitectura CISC y RISCing_jonny23No ratings yet

- Primer Taller SO - Conceptos - Arquitec - Comp 2020-1Document11 pagesPrimer Taller SO - Conceptos - Arquitec - Comp 2020-1Oscar Leonardo Atara RosoNo ratings yet

- Desarrollo Prueba 2018Document7 pagesDesarrollo Prueba 2018Mauricio VegaNo ratings yet

- Organización Básica y Diseño Del ComputadorDocument11 pagesOrganización Básica y Diseño Del ComputadorJeikel JosueNo ratings yet

- SOM - Procesos y Memoria - r01Document63 pagesSOM - Procesos y Memoria - r01adayfernandez57No ratings yet

- Estructura Interna Del Computador-2Document37 pagesEstructura Interna Del Computador-2rocco palmettNo ratings yet

- Diagrama de Computadora y Funcionamiento-El Fenómeno CibernéticoDocument8 pagesDiagrama de Computadora y Funcionamiento-El Fenómeno CibernéticoAli SerranoNo ratings yet

- Estructura y Funcionamiento de La CpuDocument6 pagesEstructura y Funcionamiento de La CpuJose BanquezNo ratings yet

- Sistema de buses en computadorasDocument42 pagesSistema de buses en computadorasluisoswal91No ratings yet

- Perspectivas de Alto Nivel Del Funcionamiento y de Las Interconexiones Del ComputadorDocument17 pagesPerspectivas de Alto Nivel Del Funcionamiento y de Las Interconexiones Del ComputadorAldair Huamani Cusi0% (1)

- Introducción a la arquitectura de una computadoraDocument27 pagesIntroducción a la arquitectura de una computadoraFrancisco RamirezNo ratings yet

- Apuntes Libro AcDocument5 pagesApuntes Libro AcMilagros VegaNo ratings yet

- Hardware de Los Sistemas de Computacion 2Document19 pagesHardware de Los Sistemas de Computacion 2Aylen MtñNo ratings yet

- Diagrama bloques computadoraDocument15 pagesDiagrama bloques computadoraAnabelJulianaVarhenVilelaNo ratings yet

- TEMA1Document10 pagesTEMA1Mion Sonozaki 23No ratings yet

- Capitulo 3 ExpoDocument53 pagesCapitulo 3 ExpoChristianLojanNo ratings yet

- Trabajo Sobre La UNIDAD 1 Y UNIDAD 2Document12 pagesTrabajo Sobre La UNIDAD 1 Y UNIDAD 2mauricio armasNo ratings yet

- Presentacion Unidad1 - Arquitectura de ComputadorasDocument29 pagesPresentacion Unidad1 - Arquitectura de ComputadorasrelthiNo ratings yet

- U2 - Ensamblador Rev1.0Document30 pagesU2 - Ensamblador Rev1.0Iam Anthony Marcelo Alvarez OrellanaNo ratings yet

- Tema 3 - El - ProcesadorDocument18 pagesTema 3 - El - Procesadorlespi primoNo ratings yet

- Modelo Von NeumanDocument32 pagesModelo Von NeumanCandelaria Bartolo EmeterioNo ratings yet

- Areli Bravo - Actividad 1Document19 pagesAreli Bravo - Actividad 1Juari RamosNo ratings yet

- 2.3 Estructura Lógica de Un OrdenadorDocument8 pages2.3 Estructura Lógica de Un OrdenadorLuis UbeNo ratings yet

- UNIDAD 1 Clase 02 Modelo de VNDocument63 pagesUNIDAD 1 Clase 02 Modelo de VNDaniel JimenezNo ratings yet

- TP 4Document7 pagesTP 4Nacho NotaNo ratings yet

- Sistemas I Informe 1Document21 pagesSistemas I Informe 1alexNo ratings yet

- Organización del Computador y sus Unidades FuncionalesDocument9 pagesOrganización del Computador y sus Unidades Funcionalesluisl sosaNo ratings yet

- ArquiDocument24 pagesArquiangelmauriciormzNo ratings yet

- Tema 2 Elementos OrdenadorDocument11 pagesTema 2 Elementos Ordenadorsromero_245118No ratings yet

- Apuntes Del Microprocesador 8085 2017 ED15Document114 pagesApuntes Del Microprocesador 8085 2017 ED15MEKArot100% (1)

- Arquitectura Del ComputadorDocument10 pagesArquitectura Del ComputadorDavid PinoNo ratings yet

- Cristian ToledoDocument5 pagesCristian ToledoLuis Alfredo Bayena TorresNo ratings yet

- Investigacion para Diapositiva InformaticaDocument10 pagesInvestigacion para Diapositiva InformaticaErika PerazaNo ratings yet

- Modelo Von NewmanDocument32 pagesModelo Von NewmanGuillermoNo ratings yet

- Sanchez - Practica 6Document12 pagesSanchez - Practica 6Edison Sànchez50% (2)

- Microprocesador 8bits ResumenDocument23 pagesMicroprocesador 8bits ResumenAdolfo AguilarNo ratings yet

- Arquitectura y Organizacion Del OrdenadorDocument4 pagesArquitectura y Organizacion Del OrdenadorFacundo Esteban PalermoNo ratings yet

- Microprocesador CuestionarioDocument7 pagesMicroprocesador CuestionarioFelipe MenesesNo ratings yet

- UF0852 - Instalación y actualización de sistemas operativosFrom EverandUF0852 - Instalación y actualización de sistemas operativosRating: 5 out of 5 stars5/5 (1)

- Desarrollo de componentes software para el manejo de dispositivos. IFCT0609From EverandDesarrollo de componentes software para el manejo de dispositivos. IFCT0609No ratings yet

- CuestionarioDocument3 pagesCuestionariosantiago peña100% (1)

- Texto Guia Asignatura Eln-362-E1Document34 pagesTexto Guia Asignatura Eln-362-E1Ulises Alejandro Romagera OsinagaNo ratings yet

- Unidad 01 2019 02 Laboratorio de Computadoras Automotrices (3449)Document89 pagesUnidad 01 2019 02 Laboratorio de Computadoras Automotrices (3449)German ElecrogermainNo ratings yet

- Listado Ledacom - 15 02 2021Document14 pagesListado Ledacom - 15 02 2021crlsNo ratings yet

- Trabajo Registros y ContadoresDocument17 pagesTrabajo Registros y ContadoresLuisandraNo ratings yet

- Historia de Las FpgaDocument10 pagesHistoria de Las FpgaAle RQNo ratings yet

- Arquitectura de MicrocontroladoresDocument57 pagesArquitectura de Microcontroladoresoconer51No ratings yet

- Contador Ascendente Descendente Modulo 1 PDFDocument42 pagesContador Ascendente Descendente Modulo 1 PDFnelson david pineda higueraNo ratings yet

- Ameco Micov MXTronics SolucionadasDocument1 pageAmeco Micov MXTronics SolucionadasPablo VargasNo ratings yet

- Preparatorio 2Document3 pagesPreparatorio 2Veronica GuerreroNo ratings yet

- Tecnologia de Montaje Superficial - Variantes en El Cogido de IdentificacionDocument2 pagesTecnologia de Montaje Superficial - Variantes en El Cogido de Identificacionargenis velasquezNo ratings yet

- Historia de La MicroelectrónicaDocument1 pageHistoria de La MicroelectrónicaJhon Brandon100% (2)

- Memoria CachéDocument4 pagesMemoria CachéDavid SalamancaNo ratings yet

- Tipos de Encapsulamiento y Evolucion de Los MicroprocesadoresDocument47 pagesTipos de Encapsulamiento y Evolucion de Los MicroprocesadoresAxel Mackleyn Barrezueta AlbercaNo ratings yet

- Tecnologia de Montaje Superficial - Encapsulados de C.I SMDDocument2 pagesTecnologia de Montaje Superficial - Encapsulados de C.I SMDGeovanny SanJuanNo ratings yet

- Instrucciones ArquitectuarDocument86 pagesInstrucciones Arquitectuardome cadenaNo ratings yet

- Práctica 1Document19 pagesPráctica 1Ivan Saul Montalvo GarciaNo ratings yet

- Transistores FetDocument16 pagesTransistores FetgonzaloNo ratings yet

- Almacenamiento Hay Que TerminarDocument9 pagesAlmacenamiento Hay Que TerminarYORDY HERRERANo ratings yet

- Lista de Precios Corp MMDocument16 pagesLista de Precios Corp MMPhilip AnselmoNo ratings yet

- Memoria RAM, ROM, virtual y flashDocument6 pagesMemoria RAM, ROM, virtual y flashGonzaloIkerNicoToledoNo ratings yet

- Arq - 1 El Microprocesador Mc6802Document7 pagesArq - 1 El Microprocesador Mc6802Servand Gunzand RosesNo ratings yet

- Funcionamiento interno del 8085Document7 pagesFuncionamiento interno del 8085Percy VillegasNo ratings yet

- MC ItachiDocument29 pagesMC ItachiEdwin Alex Ovando SaavedraNo ratings yet

- SeparataDocument8 pagesSeparataFader BedoyaNo ratings yet

- Guía completa sobre conceptos básicos de microprocesadoresDocument3 pagesGuía completa sobre conceptos básicos de microprocesadoresp4ncyy jjNo ratings yet

- Unidad 2 - Familias LogicasDocument46 pagesUnidad 2 - Familias LogicasCristian Ortiz100% (1)

- IC-1400. FOC. Tema 3. Arquitectura de ComputadorasDocument74 pagesIC-1400. FOC. Tema 3. Arquitectura de ComputadorasPablo PérezNo ratings yet

- Investigación Tema2 JMUADocument10 pagesInvestigación Tema2 JMUAJuan Manuel UgaldeNo ratings yet

- Catalogo 18-05-2022Document4 pagesCatalogo 18-05-2022Samuel HilariNo ratings yet