Professional Documents

Culture Documents

A 5.4mW 0.07mm 2.4GHz Front-End Receiver in 90nm For WPAN

Uploaded by

jaberyemeni0 ratings0% found this document useful (0 votes)

15 views3 pagesdfdfdfdfdfdfdfdfgh mghm gbfgfgfgfgfgfgfgfgfgfgfgfgfgfgfgfgfgfg

Original Title

A 5.4mW 0.07mm² 2.4GHz Front-End Receiver in 90nm for WPAN

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentdfdfdfdfdfdfdfdfgh mghm gbfgfgfgfgfgfgfgfgfgfgfgfgfgfgfgfgfgfg

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

15 views3 pagesA 5.4mW 0.07mm 2.4GHz Front-End Receiver in 90nm For WPAN

Uploaded by

jaberyemenidfdfdfdfdfdfdfdfgh mghm gbfgfgfgfgfgfgfgfgfgfgfgfgfgfgfgfgfgfg

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 3

Please click on paper title to view Visual Supplement.

ISSCC 2008 / SESSION 20 / WLAN/WPAN / 20.7

20.7

A 5.4mW 0.07mm 2.4GHz Front-End Receiver in

90nm CMOS for IEEE 802.15.4 WPAN

Manuel Camus1,2, Benoit Butaye1, Luc Garcia1, Mathilde Sie1,

Bruno Pellat1, Thierry Parra2

1

STMicroelectronics, Crolles, France

LAAS-CNRS, Toulouse, France

The aim of the 2.4GHz front-end receiver presented in this paper

is the minimization of both cost and energy consumption, focusing

on WPAN IEEE 802.15.4 transceivers. It includes the entire RF

part, from the balun to the first stage of the channel filter, as well

as the LO signal conditioning cells. The proposed architecture uses

an unmatched inductorless LNA and a new clocking scheme on a

standard passive mixer. Compared to previously reported

IEEE 802.15.4 receivers [1-3], an area reduction by at least 70% is

achieved. The power consumption is relatively low at 5.4mW with

a state-of-the-art noise and linearity performance. The receiver

front-end operates at 1.35V. It is implemented in a 90nm CMOS

technology using two thick metals, and alucap with RFMOM

capacitors.

The receiver block diagram is shown in Fig. 20.7.1. It is based on

a 6MHz low-IF topology which leads to 30dB rejection of IEEE

802.11b interferers when a 34dB image-rejection third-order

polyphase channel filter is implemented. Special attention has

been paid to power consumption and cost reduction by minimizing

the area and the number of external components. To this aim, the

receiver uses an integrated balun with a 50 input and two differential 100 and 200 output ports, in order to optimize both the

RX noise figure and the TX output power. It also uses an inductorless LNA with a high input impedance, a low-loss passive mixer

and a LO divide-by-two with low dynamic-current latches. In this

design, only the first stage of the channel filter is implemented,

which consists of a 3MHz-bandwidth active-RC polyphase filter,

reaching 35dBv/dBm of total receiver gain. A 1st-order 400kHz

high-pass filter is added before the filter for DC-offset suppression.

Resulting gain and NF measured frequency responses are shown

in Fig. 20.7.2.

The low gain of the single-stage LNA (14dB) is compensated by setting a high input impedance value for the receiver. Since no impedance matching is used between the antenna and the LNA, the voltage magnitude at the LNA input can be up to twice as large, as

compared to that of a receiver with input matching. Of course, this

principle makes the receiver performance more sensitive to the

package and board implementation. Nevertheless, if there is no

impedance mismatch between the antenna and its connection line,

the voltage at the LNA input remains maximum whatever the line

length is. As a limit, series resistances of the integrated balun

reduce the parallel receiver input impedance, resulting in a final

measured extra gain value of 3.9dB instead of the 6dB value theoretically expected. This extra gain prior to the LNA improves the

overall noise figure of the receiver (Fig. 20.7.2).

The LNA uses a cascaded pseudo-differential structure with resistive loads (Fig. 20.7.3). A control loop maintains its bias current at

1.2mA, reducing its sensitivity versus supply and process variations. To meet gain specifications, the LNA is loaded with a high

value resistor (RL=800). An output buffer realizes an interface

with the mixer (Fig. 20.7.3). This buffer draws 500A, has a constant 4dB gain and sets the IIP3 to 10dBm at the receiver input.

The buffer transistor sizes are chosen relatively small so as not to

impact the LNA bandwidth while maintaining good noise performance. Moreover, for the purpose of mixer image rejection, the split

of the signal into I and Q channels cannot be done with two buffers

because of matching. For this reason, the receiver consists of only

one buffer and the split is realized with series capacitors (Fig.

20.7.1).

368

The passive mixer (Fig. 20.7.4) is implemented with four switches

(W=5m), and operates like a voltage conveyor. A mixer driven by

a classical square-wave LO presents losses (about 4dB) due to

averaging of half a period of a sinusoidal wave (Fig. 20.7.4).

Moreover, due to the ratio between the high output impedance of

the buffer and the mixer series resistance, an additional 4dB

attenuation will occur, because of interactions between I and Q

channels. The proposed solution thus uses the voltage output of a

capacitatively loaded mixer whose square-wave LO duty cycle is

lower than 1/4. Since there is no longer a commutation of I channel when the Q switch is ON, or vice versa, there is no longer interaction between channels. Moreover, the averaging window is

reduced and the mixer peak output voltage becomes close to its

peak input voltage (Fig. 20.7.4). A -duty-cycle square-wave LO

therefore reduces total losses from 8 down to 1.2dB. The passive

mixer linearity is a function of the time it takes for the switch

impedance to vary. By keeping LO slopes steep enough, the linearity is unchanged.

The LO path is composed of a divide-by-two, which generates signals in quadrature, a buffer and NOR gates setting the duty

cycle. The divider involves two dynamic latches (Fig. 20.7.5), which

are built-up by two inverters, two memory cells and only two

switches. Compared to a classical solution, this topology presents

improved differential performance and tolerates lower input signal

levels. By reducing transistor sizes, the divider is optimized for

small dynamic current draw. However, because it is part of the

image-rejection budget, the I/Q phase mismatch limits this reduction. Monte-Carlo simulations gives 2 phase mismatch at 3,

while the LO path draws 1mA.

A voltage conveyor mixer operation needs a high input impedance

channel filter. Moreover, because the LNA and the mixer exhibit

limited gain values (less than 17dB for the combination), a lownoise first stage has been designed for the channel filter (input

noise<12nV/Hz). The proposed solution uses two single-ended

opamps (Fig. 20.7.1). It presents the best trade-off between input

impedance value, noise and linearity performance. A value of

350MHz of GBW is reached for a 800A current draw, which is sufficient to realize a 6MHz polyphase filter. Five calibration bits are

used on the capacitive resonator, in order to compensate both temperature and process variations. Three gain steps of 6dB are

implemented just before the channel filter by means of resistive

dividers.

The chip is fabricated in a 90nm CMOS process. A die micrograph

is shown in Fig. 20.7.7. In addition to Fig. 20.7.2, Fig. 20.7.6 summarizes measurements performed on the receiver with and without an input integrated balun. Performance results are de-embedded at the chip input and the results are averaged over 12 dies.

Compared to previously reported IEEE 802.15.4 front-end

receivers, this work presents favorable trade-off between noise,

linearity and power consumption. Moreover, the main improvement remains the area reduction, since the receiver front-end area

is 0.07mm, and 0.23mm when the input balun is integrated on

chip.

References:

[1] I. Nam, K. Choi, J. Lee et al., A 2.4GHz Low-Power Low-IF Receiver and

Direct-Conversion Transmitter in 0.18-m CMOS for IEEE 802.15.4 WPAN

Applications, IEEE Trans. Microwave Theory and Techniques, vol. 55,no. 4,

pp. 682-689, Apr. 2007.

[2] W. Kluge, F. Poegel, H. Roller et al., A Fully Integrated 2.4GHz IEEE

802.15.4-Compliant Transceiver for ZigBee Applications, IEEE ISSCC Dig.

Tech. Papers, pp. 372-373, Feb. 2006.

[3] T.-K. Nguyen, V. Krizhanovskii, J. Lee et al., A Low-Power RF DirectConversion Receiver/Transmitter for 2.4-GHz-Band IEEE 802.15.4

Standard in 0.18-m CMOS Technology, IEEE Trans. Microwave Theory

and Techniques, vol. 54, no. 12, pp. 4062-4071, Dec. 2006.

2008 IEEE International Solid-State Circuits Conference

978-1-4244-2011-7/08/$25.00 2008 IEEE

Please click on paper title to view a Visual Supplement.

Please click on paper title to view Visual Supplement.

ISSCC 2008 / February 5, 2008 / 4:45 PM

Figure 20.7.2: Measured front-end receiver frequency and noise responses.

Figure 20.7.1: Receiver block diagram.

2 + 2 4

20

Figure 20.7.4: Passive-mixer schematic and transient signals versus LO duty cycle,

when LO and RF have the same frequency and are in phase.

Figure 20.7.3: LNA and Buffer Schematics.

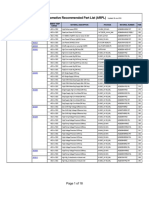

This work This work

[1]

[2]

[3]

NA

<10dB

15dBm

NA

>35dB

5mA

1.8V

9mW

NA

5.7dB

16dBm

NA

34dB

4.5mA

1.8V

8.1mW

40dB/dBm

7.3dB

8dBm

18dBm

NA

3.5mA*

1.8V

6.3mW*

W/ Balun W/O Balun

Gain

NF

IIP3

ICP1

35dB/dBm 37dB/dBm

7.5dB

6dB

10dBm

12dBm

18dBm

20dBm

IR

>32dB

>32dB

Current

4mA

4mA

Supply

1.35V

1.35V

Power

5.4mW

5.4mW

Process 90nm CMOS 90nm CMOS

0.23mm 0.07mm

Area

Figure 20.7.5: Divider-by-two and latch schematics .

0.18m CMOS 0.18m CMOS 0.18m CMOS

0.5mm

0.3mm

1.8mm

Current draw does not include divider-by-two and LO buffers.

Figure 20.7.6: Measurement results and performance comparison of 2.4GHz IEEE

802.15.4 front-end receivers.

Continued on Page 620

DIGEST OF TECHNICAL PAPERS

Please click on paper title to view a Visual Supplement.

369

Please click on paper title to view Visual Supplement.

ISSCC 2008 PAPER CONTINUATIONS

Figure 20.7.7: Die Micrograph of the test chip in 90nm CMOS.

620

2008 IEEE International Solid-State Circuits Conference

978-1-4244-2011-7/08/$25.00 2008 IEEE

Please click on paper title to view a Visual Supplement.

You might also like

- Rent 101 Nov2023Document1 pageRent 101 Nov2023jaberyemeniNo ratings yet

- Aaaaáaaaaavpc NagDocument230 pagesAaaaáaaaaavpc NagLaloNo ratings yet

- Check It Out For AS ABAP Performance IssuesDocument3 pagesCheck It Out For AS ABAP Performance IssuesjaberyemeniNo ratings yet

- Basis TcodesDocument4 pagesBasis TcodesjaberyemeniNo ratings yet

- Basis TcodesDocument4 pagesBasis TcodesjaberyemeniNo ratings yet

- Basis TcodesDocument4 pagesBasis TcodesjaberyemeniNo ratings yet

- How To Create Transport of Copies (Toc) in SapDocument7 pagesHow To Create Transport of Copies (Toc) in SapjaberyemeniNo ratings yet

- Post Installation Steps For ECC 5Document6 pagesPost Installation Steps For ECC 5Pradeep KumarNo ratings yet

- M.J.C.E.T ECE Staff Meeting Notice August 17Document1 pageM.J.C.E.T ECE Staff Meeting Notice August 17jaberyemeniNo ratings yet

- 1b - E - Detached PronounDocument19 pages1b - E - Detached PronounjaberyemeniNo ratings yet

- 435faculty Complaints - ComplianceDocument1 page435faculty Complaints - CompliancejaberyemeniNo ratings yet

- 2019 08 07Document4 pages2019 08 07jaberyemeniNo ratings yet

- 2b - E - Singular Plural-1Document3 pages2b - E - Singular Plural-1jaberyemeniNo ratings yet

- SAP Client Copy / System Refresh: What Is System Refresh When and Why It Is Done?Document2 pagesSAP Client Copy / System Refresh: What Is System Refresh When and Why It Is Done?jaberyemeniNo ratings yet

- Guhghkihi BHJGFFGHDocument1 pageGuhghkihi BHJGFFGHjaberyemeniNo ratings yet

- Wa0005 PDFDocument2 pagesWa0005 PDFsrinivasanNo ratings yet

- Lec 2 Types of SemiconductorsDocument46 pagesLec 2 Types of SemiconductorsjaberyemeniNo ratings yet

- Revised Be Library Books 2017Document4 pagesRevised Be Library Books 2017jaberyemeniNo ratings yet

- Vasa College Recruitment Guide for Electrical EngineeringDocument5 pagesVasa College Recruitment Guide for Electrical EngineeringjaberyemeniNo ratings yet

- Oman Job Openings Lecturers TechniciansDocument3 pagesOman Job Openings Lecturers TechniciansjaberyemeniNo ratings yet

- 2019 Holidays ListDocument2 pages2019 Holidays ListjaberyemeniNo ratings yet

- Arrival and Departure InfoDocument1 pageArrival and Departure InfojaberyemeniNo ratings yet

- Syllabus For Written Test - Asst. Prof. in ECE-June-2019 Electronics and Communication Engineering PART - A (Common For All Candidates)Document3 pagesSyllabus For Written Test - Asst. Prof. in ECE-June-2019 Electronics and Communication Engineering PART - A (Common For All Candidates)jaberyemeniNo ratings yet

- SET A 2018-19 - Key 2019Document14 pagesSET A 2018-19 - Key 2019jaberyemeniNo ratings yet

- Seminar Marks DistributionDocument2 pagesSeminar Marks DistributionjaberyemeniNo ratings yet

- BE401 Syllabus 1Document2 pagesBE401 Syllabus 1jaberyemeniNo ratings yet

- Mrs Amina 5957845 Orange Tours & TravelsDocument2 pagesMrs Amina 5957845 Orange Tours & TravelsjaberyemeniNo ratings yet

- B.E. V-SEM (SEC-A) - E.C.E. Automatic Control Systems (PC 504 EC) Part-A Answer All The Questions (2 2 4)Document1 pageB.E. V-SEM (SEC-A) - E.C.E. Automatic Control Systems (PC 504 EC) Part-A Answer All The Questions (2 2 4)jaberyemeniNo ratings yet

- Historical Perspective of ElectronicsDocument40 pagesHistorical Perspective of ElectronicsjaberyemeniNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5784)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Akg c3000b Condenser Microphone SM PDFDocument3 pagesAkg c3000b Condenser Microphone SM PDFРубен БогдаянNo ratings yet

- PCM55SAW Installation ManualDocument7 pagesPCM55SAW Installation ManualPedro Luis Loredo SánchezNo ratings yet

- IEC 61810-1 PreviewDocument21 pagesIEC 61810-1 Previewvinay gayate0% (1)

- Flat Panel Antenna SpecificationsDocument1 pageFlat Panel Antenna Specificationsana camila escobarNo ratings yet

- Rolling Door Operator ManualDocument8 pagesRolling Door Operator ManualHector MoragaNo ratings yet

- YDocument26 pagesYAshutosh PatilNo ratings yet

- Aiwa Cx-jds20 Cx-jds50 Ver1.1 SMDocument69 pagesAiwa Cx-jds20 Cx-jds50 Ver1.1 SMmientrasvivoNo ratings yet

- 2 Kontrolleri ATS 021 enDocument36 pages2 Kontrolleri ATS 021 enFranky Roi SiahaanNo ratings yet

- ARPLDocument18 pagesARPLLily SternNo ratings yet

- Ohm's Law electrical concepts quiz answers and explanationsDocument14 pagesOhm's Law electrical concepts quiz answers and explanationsDerlyn FernandezNo ratings yet

- ACTURA Durus 48350 BrochureDocument2 pagesACTURA Durus 48350 BrochurePowerstorm0% (1)

- Equipment Definition: Component LiteratureDocument4 pagesEquipment Definition: Component LiteratureAbbas AkbarNo ratings yet

- H1Pzplot - JPG.: Coe 121 Programming Exercise 06: Frequency-Domain Analysis of Lti Systems 2 Semester 2018-2019Document3 pagesH1Pzplot - JPG.: Coe 121 Programming Exercise 06: Frequency-Domain Analysis of Lti Systems 2 Semester 2018-2019Apricot BlueberryNo ratings yet

- Coaxial CableDocument36 pagesCoaxial CableAmit SinghNo ratings yet

- USB Charging Port Power Switch and Controller: Features DescriptionDocument42 pagesUSB Charging Port Power Switch and Controller: Features DescriptionJagopati Jr.No ratings yet

- Presentation On Photonics by Prince Kushwaha (RJIT) PPT 2Document1 pagePresentation On Photonics by Prince Kushwaha (RJIT) PPT 2anumandlajeevansai100% (1)

- 1LE1003-2AA434 Certificate 2 2Document1 page1LE1003-2AA434 Certificate 2 2Rasek ResolfNo ratings yet

- Proprietary Electronics For Reactor Safety and ControlsDocument13 pagesProprietary Electronics For Reactor Safety and ControlsVarshaNo ratings yet

- Rotating Electrical Machines - : Part 17: Cage Induction Motors When Fed From Converters - Application GuideDocument22 pagesRotating Electrical Machines - : Part 17: Cage Induction Motors When Fed From Converters - Application GuideAhmad RostomNo ratings yet

- E380Document88 pagesE380Luis JaramilloNo ratings yet

- Circuits 2 Lab Report No. 5Document4 pagesCircuits 2 Lab Report No. 5Carlo Caniedo80% (5)

- IEEE STD 519 1992vs2014Document50 pagesIEEE STD 519 1992vs2014DaniNurFaruqNo ratings yet

- Mag Apps+Instal v1.5Document19 pagesMag Apps+Instal v1.5electron13No ratings yet

- Heating Cable Selection GuideDocument4 pagesHeating Cable Selection Guidehassan3012No ratings yet

- PV Cell ModelingDocument12 pagesPV Cell Modelingtran duyNo ratings yet

- IC Fabrication Process StepsDocument40 pagesIC Fabrication Process StepsRajkumari MishraNo ratings yet

- CCC To Cic Hu and Amp Wiring RetrofitDocument2 pagesCCC To Cic Hu and Amp Wiring Retrofitvlashent semaNo ratings yet

- Inverter Power SocketsDocument2 pagesInverter Power SocketsrandelmacocoNo ratings yet

- Hisim HV 1.2.2 User'S Manual: 2011 Hiroshima University & Starc All Rights ReservedDocument84 pagesHisim HV 1.2.2 User'S Manual: 2011 Hiroshima University & Starc All Rights ReservedIoan VasiliuNo ratings yet