Professional Documents

Culture Documents

Article

Uploaded by

AbdullahCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Article

Uploaded by

AbdullahCopyright:

Available Formats

Journal of the Korean Physical Society, Vol. 45, December 2004, pp.

S716S719

Annealing Effects of HfO2 Gate Thin Films Formed by Inductively Coupled

Sputtering Technique at Room Temperature

Won Joon Choi, Eun Joung Lee, Kap Soo Yoon, Jung Yup Yang, Jong Hyun Lee, Chae Ok Kim and Jin Pyo Hong

New Functional Materials and Device Laboratory,

Department of Physics, Hanyang University, Seoul 133-791

Hee Jae Kang

Department of Physics, Chungbuk National University, Cheongju 361-763

Ultrathin HfO2 dielectrics for gate oxide layer in metal-oxide-semiconductor devices were pre-

pared on Si substrates by using an inductively coupled rf magnetron sputtering method at room

temperature. This new sputtering method is designed to improve the uniformity and efficient for-

mation of high quality HfO2 gate dielectric. As-grown HfO2 gate dielectrics were also systematically

annealed with a rapid thermal annealing. Electrical transport of as-grown and post-annealed HfO2

thin films was characterized by the C-V and I-V measurements. The post-annealed HfO2 gate dielec-

tric exhibited more significant reduction of gate leakage current from 105 A/cm2 to 106 A/cm2

at 1 V, together with the enhanced capacitance values. In addition, the combined measurements

of X-ray photoemission spectroscopy and X-ray diffraction confirm the structural improvement of

post-annealed HfO2 gate dielectrics.

PACS numbers: 73.40.Qv

Keywords: High-k, Gate dielectric, Gate oxide, HfO2 , MOS, MOSFET

I. INTRODUCTION crystalline or amorphous phases, depending on experi-

mental conditions [7]. In particular, the crystallization

of HfO2 gate dielectric is known to induce increased cur-

Recently, high-k gate dielectrics have become attrac- rent density through the grain boundaries.

tive to replace well-known SiO2 or SiON thin film as In this work, ultrathin HfO2 gate dielectrics of about

gate oxide layers of sub-20 A metal-oxide-semiconductor 100 A were prepared by an inductively coupled rf mag-

field-effect transistors (MOSFET) [1,2]. As the gate ox- netron sputtering system at room temperature. This

ide layer of SiO2 or SiON thin films is scaled down, these method was designed to reduce a self-bias effect on gate

films easily induce higher leakage current density due to dielectrics by internal rf external power and to increase

direct tunneling through the gate oxide layer [3]. There- atomic oxygen concentrations, compared with those in

fore, the high leakage current density requires the urgent the conventional rf reactive sputtering method [8,9]. This

development of new materials with dielectric constants technique shows the useful capability of suppressing the

higher than that of SiO2 or SiON material. Up to now, crystallization of HfO2 gate dielectric, depending on the

following materials for HfO2 , ZrO2 , Al2 O3 , TiO2 , Ta2 O3 , externally applied rf power. As-grown HfO2 gate di-

silicate (HfSix Oy ) and Al2 O3 /HfO2 stack gate dielectrics electrics result in more excellent leakage current density

have been studied [4, 5]. Among these materials, HfO2 and C-V properties at optimum conditions. In addition,

thin film has become a promising gate dielectric candi- as-grown HfO2 gate dielectrics were annealed by a rapid

date to replace Si-based gate oxide layer in MOSFET be- thermal annealing (RTA) process in ambient of N2 from

cause of its large bandgap and high-k value of about 25. 650 C to 850 C for 2 min in order to obtain better elec-

It is also well known to be thermally compatible with Si trical properties, as a compared with as-deposited HfO2

substrate[1]. Therefore, a lower effective electrical thick- gate dielectrics.

ness of HfO2 gate dielectric can possibly avoid the direct

tunneling effect of carriers between the gate and the Si

channel[6]. In addition, currently available HfO2 gate di-

electrics have been prepared by conventional rf reactive II. EXPERIMENTS

sputtering, atomic layer deposition techniques or chem-

ical vapor deposition methods. They frequently reveal p-type Si (100) substrates were etched with a 10 %

HF solution in methyl alcohol in order to remove nat-

E-mail: jphong@hanyang.ac.kr ural oxide and contaminants from the substrates. This

-S716-

Annealing Effects of HfO2 Gate Thin Films Formed by Inductively Coupled Sputtering Won Joon Choi et al. -S717-

Fig. 1. Schematic of inductively coupled rf sputtering sys-

tem.

Fig. 3. XPS spectra of the HfO2 (100

A) gate dielectrics

as a function of external power (EP). EP= (a) 0 W, (b) 60

W.

this paper) varies from the weak crystalline phase to an

amorphous phase with increasing external power. This

variation may be due to a large number of active oxy-

Fig. 2. XRD results of the HfO2 (600 A) gate dielectric

fabricated by an inductively coupled rf sputtering method. gen radicals around an external electrode controlled by

external rf power. The control of external rf power was

proven to be relevant for the efficient deposition of HfO2

cleaning method produces a hydrogen-passivated surface gate thin film at room temperature. The chemical char-

on the substrate. Then, the HfO2 gate dielectrics were acterization of HfO2 gate oxide was accomplished by the

deposited by using an inductively coupled rf magnetron X-ray photoemission spectroscopy (XPS). Figure 3 re-

reactive sputtering method. A more detailed descrip- veals the chemical compositions of HfO2 gate oxides pre-

tion of our modified sputtering system is given in Figure pared at external power of 0 and 60 W. As shown in

1. The internal sputtering power of the HfO2 gate di- this figure, the Hf4f core-level spectra of HfO2 gate di-

electrics was fixed at 50 W, with variation of external electric clearly show typical spin-orbit splitting values of

power from 0 W to 60 W. The post annealing of the 16.85 eV and 16.90 eV. They are considered in the fit to

HfO2 gate dielectrics was performed by the RTA process the 4f doublet. In addition, no peak at lower binding

from 650 C to 850 C for 2 min in N2 ambient. As gate energy is detected, which means that no Hf-Hf or Hf-Si

electrode, aluminum (Al) was sputtered on the HfO2 gate bond is present within the detection limit [12].

dielectric for the C-V curve and leakage current measure- Figure 4 shows the C-V measurements of HfO2 sam-

ments by using a shadow mask with gate area of 7.0 ples formed without and with external power. The sam-

104 cm2 . Structural characterizations of the HfO2 gate ple thickness was about 100 A, and the measurement was

dielectrics were measured by X-ray diffraction ( XRD ) made at 100 kHz. The HfO2 gate dielectric fabricated at

by using a Cu source and XPS systems. external power of 60 W indicates C-V hysteresis of less

than 80 mV in a 4 V range at a flatband voltage of

+0.2 V. The maximum values of capacitance and capac-

itance density are found to be 254 pF and 0.36 F/cm2 ,

III. RESULTS AND DISCUSSION respectively. However, the HfO2 gate dielectric prepared

at zero external power does not exhibit any accumula-

Figure 2 shows typical XRD patterns as a function of tion capacitance in a bias voltage range of 4 V, together

external power. In general, the HfO2 gate dielectric pre- with large C-V hysteresis. As mentioned with reference

pared by the conventional rf sputtering method at room to Figure 2, the possible poor C-V characteristics might

temperature mainly exhibits the monoclinic phase peak be due to the large leakage current through the grain

at 2 = 28.4 [10, 11]. However, the HfO2 gate dielec- boundaries [13, 14]. As shown in this figure, the basic

tric formed by our process indicates a weak crystalline properties of leakage current densities of 0W and 60 W

phase at 0 W. The crystalline of HfO2 film (not shown in samples are 105 and 102 A/cm2 , respectively.

-S718- Journal of the Korean Physical Society, Vol. 45, December 2004

Fig. 6. Leakage current characteristics of Si / HfO2 (100

A) structure as a function of annealing temperature in N2

ambient.

) structure

Fig. 4. Electrical properties of Si / HfO2 (100 A

as a function of external power: (a) C-V curve, (b) J-V curve.

Fig. 7. XRD results of as-deposited and annealed

HfO2 (100 A) gate dielectrics. The gate dielectric was an-

nealed at 750 C in N2 ambient.

bonds at interface layers between the HfO2 gate dielec-

tric and Si substrate [15]. This additional result induces

a higher leakage current at high annealing temperatures.

In our process, all annealed samples display better C-V

hysteresis properties of less than 80 mV.

Figure 6 shows typical leakage current densities as a

) structure

Fig. 5. C-V characteristics of Si / HfO2 (100 A function of annealing temperature from 650 C to 850

as a function of annealing temperature in N2 ambient. The C. As shown in this figure, the leakage current decreased

HfO2 gate dielectrics were fabricated at external power of 60 to 106 A/cm2 at 750 C, but above 750 C the leakage

W. current density started to increase and then reached

103 A/cm2 . Therefore, it is expected that the high leak-

age current of crystalline samples is due to grain bound-

Figure 5 shows the C-V curves of samples annealed aries that serve as high leakage paths of the gate oxide

from 650 C to 850 C for 2 min in N2 ambient. When layer. Therefore, a weak crystalline phase of gate oxide is

the HfO2 gate dielectrics fabricated at an external power critically desirable, due to the lack of grain boundaries,

of 60 W were annealed from 650 C to 750 C, the max- for future new applications.

imum capacitance value increased to 783 pF. This ex- Figure 7 shows typical X-ray diffraction patterns of

perimental result suggest that as-deposited HfO2 gate as-deposited and annealed HfO2 gate dielectrics of 100

dielectrics may locally have many defect states inside

A. As shown in this figure, the post-annealed HfO2 gate

HfO2 films, but the annealing process can reduce the de- dielectric still shows a very weak crystalline phase, even

fect densities with increasing dielectric constant. How- though it was annealed at 750 C in N2 ambient. In addi-

ever, the capacitance value decreased to above 750 C. tion, the electrical properties of the post-annealed HfO2

The significant reduction of the capacitance at higher an- gate thin film seem not to be affected by the variation

nealing temperatures was due to the formation of Hf-Si of crystalline phases. More experiments are currently in

Annealing Effects of HfO2 Gate Thin Films Formed by Inductively Coupled Sputtering Won Joon Choi et al. -S719-

progress to investigate the relationship between electri- [1] D. C. Gilmer, R. Hegde, R. Garcia and V. Dhandapani,

cal and structural properties under a high temperature Appl. Phys. Lett. 81, 1288 (2002).

annealing process of gate oxides. [2] Y. Hoshino, K. Yamamoto, S. Hayashi and Y. Kido,

Appl. Phys. Lett. 81, 2650 (2002).

[3] Kazuhiko Yamamoto, Shigenori Hayashi and Masaaki

Niwa, Appl. Phys. Lett. 81, 2053 (2002).

IV. CONCLUSION [4] P. D. Kirsh, C. S. Kang, J. Lozano and J. C. Lee, J.

Appl. Phys. 91, 4353 (2002).

[5] Byoung Hun Lee, Laegu Kang, Renee Nieh and Jack C.

A new inductively coupled rf magnetron sputtering Lee, Appl. Phys. Lett. 76, 1926 (2000).

method was used to fabricate ultrathin HfO2 gate di- [6] Y. S. Lin, R. Puthenkovilakam and J. P. Chang, Appl.

electrics with better electrical and structural quality by Phys. Lett. 81, 2041 (2002).

reducing the self-bias effect of the conventional rf sput- [7] Hyeoksu Kang and Yonghan Roh, J. Vac. Sci. Technol.

tering system. Our process was designed to increase B 20, (2002).

atomic oxygen concentrations with high energies, for [8] Chae Ok Kim, Kap Soo Yoon, Jung Yup Yang and Jin

room temperature formation and efficient deposition. Pyo Hong, J. Korean Phys. Soc. 41, 110 (2002).

Experimental results indicate that the gate dielectrics [9] K. S. Yoon, J. Y. Yang, W. J. Choi and J. P. Hong, J.

with a weak crystalline phase have enhanced electrical Korean Phys. Soc. 42, S195 (2003).

properties, compared with those of strong crystalline [10] M. Y. Ho, G. D. Wilk, P. M. Voyles and H. Gong, Appl.

Phys. Lett. 81, 4218 (2002).

phases. In addition, the post-annealed HfO2 gate di-

[11] H. Y. Yu, N. Wu and M. F. Li, Appl. Phys. Lett. 81,

electrics at optimum conditions clearly reduce gate leak- 3618 (2002).

age current, with enhancement of the capacitance value, [12] O. Renault, D. Samour, J.-F. Damlencourt and D. Blin

at an optimum annealing temperature of about 750 C. Appl. Phys. Lett. 81, 3627 (2002).

[13] G. D. Wilk and R. M. Wallace, Appl. Phys. Lett. 74,

2854 (1999).

[14] G. D. Wilk and R. M. Wallace, J. Appl. Phys. 87, 484

ACKNOWLEDGMENTS (2000).

[15] P. D. Kirsh, C. S. Kang, J. Lozano, J. C. Lee and J. G.

This work was supported by Hynix Semiconductor Inc. Ekerdt, J. Appl. Phys. 91, 4353 (2002).

REFERENCES

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5795)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Terms and Conditions STPDocument3 pagesTerms and Conditions STPAbdullahNo ratings yet

- Demerit - Point - Structure Utown PDFDocument2 pagesDemerit - Point - Structure Utown PDFAbdullahNo ratings yet

- Checklist Safety and Health Induction For New Laboratory UsersDocument3 pagesChecklist Safety and Health Induction For New Laboratory UsersAbdullahNo ratings yet

- Demerit Point Structure (DPS) For Housing OffencesDocument2 pagesDemerit Point Structure (DPS) For Housing OffencesAbdullahNo ratings yet

- Air-Con Servicing For South Tower Level 1 To 13Document1 pageAir-Con Servicing For South Tower Level 1 To 13AbdullahNo ratings yet

- PHD Qualifying Exam NUS PhysicsDocument3 pagesPHD Qualifying Exam NUS PhysicsAbdullahNo ratings yet

- Qualifying Exam Physics NUS 01 Oct 2012Document5 pagesQualifying Exam Physics NUS 01 Oct 2012AbdullahNo ratings yet

- Applicant User Guide For Graduate Admission SystemDocument36 pagesApplicant User Guide For Graduate Admission SystemAbdullahNo ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- SLL VS NLRCDocument11 pagesSLL VS NLRCJepski ScopeNo ratings yet

- The Perception of College Students About A Healthy Lifestyle and Its Effect On Their Health 2155 9600 1000437Document4 pagesThe Perception of College Students About A Healthy Lifestyle and Its Effect On Their Health 2155 9600 1000437onnNo ratings yet

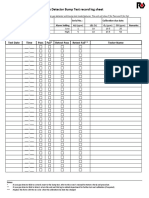

- Gas Detector Bump Test Record Log Sheet: Bump Test Result Test Date Time Pass Fail Retest Pass Retest Fail Tester NameDocument2 pagesGas Detector Bump Test Record Log Sheet: Bump Test Result Test Date Time Pass Fail Retest Pass Retest Fail Tester NameAndry Kurnia100% (2)

- Pharmacist Workup of Drug Therapy in Pharmaceutical Care: Problem Oriented Pharmacist RecordDocument20 pagesPharmacist Workup of Drug Therapy in Pharmaceutical Care: Problem Oriented Pharmacist RecordNurwahidah Moh WahiNo ratings yet

- 2022 CA Security Assessment and Authorization StandardDocument25 pages2022 CA Security Assessment and Authorization StandardDonaldNo ratings yet

- Assignment - Certificate of Pre & Primary Teacher TrainingDocument4 pagesAssignment - Certificate of Pre & Primary Teacher TrainingSuganya VimalNo ratings yet

- Cast Metal RestorationDocument48 pagesCast Metal RestorationRosa Faraon EspeñaNo ratings yet

- Fluoroscopy Initial TestDocument3 pagesFluoroscopy Initial Testthepharaoh1234No ratings yet

- Recent Advances in Natural Polymer-Based Drug Delivery SystemsDocument18 pagesRecent Advances in Natural Polymer-Based Drug Delivery SystemsTelmoNo ratings yet

- User Munual For DENAIR Diesel Portable Air CompressorDocument25 pagesUser Munual For DENAIR Diesel Portable Air CompressorBoumediene CHIKHAOUINo ratings yet

- Safety Health & Environment MethodologyDocument14 pagesSafety Health & Environment MethodologymusengemNo ratings yet

- Mothership Zine Rulebook v5 PDFDocument44 pagesMothership Zine Rulebook v5 PDFAna Luiza FernandesNo ratings yet

- A Qualitative Study of Depression in Primary Care: Missed Opportunities For Diagnosis and EducationDocument8 pagesA Qualitative Study of Depression in Primary Care: Missed Opportunities For Diagnosis and EducationTeam BEENo ratings yet

- Obstetrical EmergencyDocument41 pagesObstetrical EmergencyDrPreeti Thakur ChouhanNo ratings yet

- Sociology Review QuestionsDocument6 pagesSociology Review QuestionsNIYONSHUTI VIATEURNo ratings yet

- Sigma MP 102 (US) EN SdsDocument9 pagesSigma MP 102 (US) EN SdsEduardo GarzaNo ratings yet

- Bible Secrets of Moses and Solomon Vol2Document40 pagesBible Secrets of Moses and Solomon Vol2jamjam_9567885389% (80)

- Blok-Aid Sewer Overflow Monitoring and Alarm SystemDocument2 pagesBlok-Aid Sewer Overflow Monitoring and Alarm SystemTomas LarsenNo ratings yet

- National Conservation Strategy1Document8 pagesNational Conservation Strategy1haroonrafiq94No ratings yet

- Transcritical Co2 Refrigeration - PDFDocument11 pagesTranscritical Co2 Refrigeration - PDFHector Fabian Hernandez Algarra100% (1)

- Formatof Indenity BondDocument2 pagesFormatof Indenity BondSudhir SinhaNo ratings yet

- Project Planning Template - Castillo JiselleDocument7 pagesProject Planning Template - Castillo Jiselleapi-692396370No ratings yet

- New Tenant Welcome LetterDocument1 pageNew Tenant Welcome Letterkristen uyemuraNo ratings yet

- More Evidence Confirms Diet's Link To Mental Health: Could An Apple A Day Really Keep Depression and Anxiety Away?Document5 pagesMore Evidence Confirms Diet's Link To Mental Health: Could An Apple A Day Really Keep Depression and Anxiety Away?psychologyconceptsNo ratings yet

- Modelling The Transport of Crude Oil in Sandy Soil: Ejikeme Ugwoha, Victor Emeka Amah, Precious Ehis Agharese-AduDocument12 pagesModelling The Transport of Crude Oil in Sandy Soil: Ejikeme Ugwoha, Victor Emeka Amah, Precious Ehis Agharese-AdusfNo ratings yet

- Central University of Rajasthan: Department of Social WorkDocument4 pagesCentral University of Rajasthan: Department of Social WorkShravan RajNo ratings yet

- Road To Sustainable SHG-Bank Linkage Programme: Formulating Strategies For Managing Credit Risk With Respect To Rural BengalDocument6 pagesRoad To Sustainable SHG-Bank Linkage Programme: Formulating Strategies For Managing Credit Risk With Respect To Rural BengalAnimesh TiwariNo ratings yet

- NTCP TCPDocument54 pagesNTCP TCPSAlonii Chawla100% (2)

- ForwardInvoice ORD660948335Document4 pagesForwardInvoice ORD660948335Nitin GuptaNo ratings yet

- Learning Activity 4 Evidence: My View On Colombia: 1. Write A Composition Describing What The LifestyleDocument2 pagesLearning Activity 4 Evidence: My View On Colombia: 1. Write A Composition Describing What The LifestyleYenifer PatiñoNo ratings yet