Professional Documents

Culture Documents

Aca Midsem2011 Question Paper

Uploaded by

Kartik MakkarCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Aca Midsem2011 Question Paper

Uploaded by

Kartik MakkarCopyright:

Available Formats

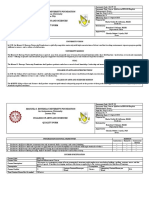

Total No. of Pages: 1 Roll Number:..

B.E. (COE) 6th SEMESTER MID SEMESTER EXAMINATION, MARCH 2011

COE 315:- ADVANCED COMPUTER ARCHITECTURE

TIME: 1.5 HOURS MAX. MARKS: 20

NOTE: Attempt all questions. Assume suitable missing data, if any, and specify it clearly.

----------------------------------------------------------------------------------------------------------------------------------

Question 1 [2]

In the CPU performance equation how do following technologies affect different parameters?

(i) RISC (ii) Superscalar

Question 2 [2]

What type of branch predictor would you recommend for a branch with the following behavior and why?

T, T, T, T, N, T, T, T, T, T, T, N, T, T, T, T, T, T, T, N, N, N, N, N, T, N, N, N, N, N, N, T, N, N, N, N

Question 3 [2]

Why can loop unrolling improve performance? Are there any potential downsides to using loop unrolling?

Explain in brief.

Question 4 [2]

Consider a pipeline that has four stages with the specified time requirement: Fetch (30 ns); Decode (20 ns);

Execute (20 ns); Writeback (30 ns). Assume that every instruction in its instruction set needs use of all

stages. Also, each stage is clocked with a common clock. What is the latency of an instruction flowing

through the pipeline? Also, what is idealized throughput of the pipeline?

Question 5 [2]

Consider two machines, machine A and machine B. For both machines, all instructions except for loads take

one cycle. Loads take one cycle plus an additional "cache penalty." Machine A has a clock rate of 1.0 GHz

and a cache penalty of 5 cycles. Machine B has a clock rate of 2.0 GHz and a cache penalty of 20 cycles.

Loads are 33% of all instructions. Which machine is faster, machine A or B and how much?

Question 6 [2]

A processor runs at 2 GHz and has a CPI of 1.2 without including the stall cycles due to cache misses. Load

and store instructions count 30% of all instructions. The processor has an I-cache and a D-cache. The hit

time is 1 clock cycle for these caches. The I-cache has a 2% miss rate. The D-cache has a 5% miss rate on

load and store instructions. The miss penalty is 50 ns, which is the time to access and transfer a cache block

between main memory and the processor. What is the Average Memory Access Time for Instruction Access

and Data Access (in clock cycles)? What is the number of stall cycles per instruction and the overall CPI?

(AMAT = hit time + miss rate * miss penalty)

Question 7 [3]

Suppose we have a pipelined architecture that has 7 stages and on a particular benchmark, it has the

following dynamic instruction mix: LOADS: 24%; STORES: 15%; ALU: 37%; BRANCHES (taken): 19%;

BRANCHES (not taken): 5% . Suppose we are using dynamic branch prediction and that each misprediction

costs a 2 cycle penalty. Assume there are no additional hazards. What branch prediction accuracy rate (in

%) is needed in order to achieve a throughput of 0.90 instructions per cycle?

Question 8 [5]

Consider the following assembly code:

Loop: LOAD R2, 0(R1) ; R2 = memory[R1]

LOAD R3, 4(R1) ; R3 = memory[R1+4]

ADD R4, R2, R3 ; R4 = R2 + R3

STORE R4, 0(R1) ; memory[R1] = R4

ADDI R1, R1, 4 ; R1 = R1 + 4

ADDI R2, R1, -400 ; for comparing R1 to 400

BEQZ R2, Loop ; if R2 = 0 then goto Loop

Assume that: R1 is initially 0; Branches resolve in the ID stage; WB writes registers in the 1st half and

ID reads registers in the 2nd half of the same cycle; Branches are handled by stalling until they are

resolved; All functional units take one cycle; There are no structural hazards. For the classic 5-stage

pipeline (IF-ID-EX-MEM-WB) without forwarding, how many cycles will this loop take?

You might also like

- Assignment QuestionsDocument3 pagesAssignment QuestionsSarbendu PaulNo ratings yet

- CS641Document2 pagesCS641sanjay hansdakNo ratings yet

- Coss MidSemester RegularDocument3 pagesCoss MidSemester RegularUdayChanderAmbatiNo ratings yet

- 06 CS81 ACADec 10Document2 pages06 CS81 ACADec 10Mohammed YasinNo ratings yet

- EXAMDec2012 SolutionDocument8 pagesEXAMDec2012 Solutionخالد ناهض نايف نجمNo ratings yet

- Mit VliwDocument30 pagesMit VliwjahNo ratings yet

- COSS Makeup QuestionDocument3 pagesCOSS Makeup Questionharshavardhini saravana kumaranNo ratings yet

- Nmam Institute of Technology: Department of Computer Science and EngineeringDocument8 pagesNmam Institute of Technology: Department of Computer Science and Engineeringsmitha shettyNo ratings yet

- High Performance Computer Architecture (CS60003)Document2 pagesHigh Performance Computer Architecture (CS60003)Venkata PranavNo ratings yet

- CS-3010 (HPC) - CS Mid Sept 2023Document7 pagesCS-3010 (HPC) - CS Mid Sept 2023rajeevkgrd20No ratings yet

- CS G524 2006 C 2011 1Document6 pagesCS G524 2006 C 2011 1Aman AgnihotriNo ratings yet

- F10 E1 SolutionDocument5 pagesF10 E1 Solutionkashi13No ratings yet

- OS Assignment1-1 PDFDocument7 pagesOS Assignment1-1 PDFYash KhilosiyaNo ratings yet

- Coa AppliedDocument13 pagesCoa AppliedIshanNo ratings yet

- CS433 hw1 Fall 07Document3 pagesCS433 hw1 Fall 0798140207No ratings yet

- KCS401 - OS - Final Question BankDocument6 pagesKCS401 - OS - Final Question Bankparidhiagarwal129No ratings yet

- OS Set 3Document2 pagesOS Set 3sriranganathan120No ratings yet

- ArchitectureDocument21 pagesArchitecturepriyankaNo ratings yet

- Os 19Document5 pagesOs 19Sneha Tiwari100% (1)

- Itr3g1 - CoaDocument5 pagesItr3g1 - Coaanish231003No ratings yet

- 18 MHC 205 JDocument3 pages18 MHC 205 JSem 4thNo ratings yet

- Coa R4it2004s Ese Dec2021 Paper2Document2 pagesCoa R4it2004s Ese Dec2021 Paper2Pranav ShuklaNo ratings yet

- Ra5210505 Computer OrganizationDocument2 pagesRa5210505 Computer OrganizationSRINIVASA RAO GANTANo ratings yet

- ES Final Jan10 PDFDocument6 pagesES Final Jan10 PDFKaemryn SaeNo ratings yet

- Gandhinagar Institute of Technology: Computer Engineering DepartmentDocument6 pagesGandhinagar Institute of Technology: Computer Engineering Departmentshah mananNo ratings yet

- Assignment Nov 19Document7 pagesAssignment Nov 19CSE ANo ratings yet

- Os 19Document5 pagesOs 19Sneha Tiwari100% (1)

- CS60003 High Performance Computer ArchitectureDocument3 pagesCS60003 High Performance Computer ArchitectureNarayan KunalNo ratings yet

- Ovn MainDocument54 pagesOvn MainAvenir BajraktariNo ratings yet

- HCT222 - 22computer Architecture and Organization 2021 July Test1Document6 pagesHCT222 - 22computer Architecture and Organization 2021 July Test1Nyasha ChiroroNo ratings yet

- Assignment 1Document4 pagesAssignment 1Vishal BhaskarNo ratings yet

- DFT QnsDocument6 pagesDFT QnsRajishaNo ratings yet

- Tutorial Sheet2014Document6 pagesTutorial Sheet2014Julia DanielNo ratings yet

- Dronacharya College of Engg Gr. Noida Operating System Subject Code: TCS-601 Cse/It ViDocument4 pagesDronacharya College of Engg Gr. Noida Operating System Subject Code: TCS-601 Cse/It ViziddirazanNo ratings yet

- DSE 3153 26 Sep 2023Document10 pagesDSE 3153 26 Sep 2023KaiNo ratings yet

- S.V. National Institute of Technology, Surat: EC306: Embedded SystemsDocument2 pagesS.V. National Institute of Technology, Surat: EC306: Embedded SystemsBittu GoswamiNo ratings yet

- Compre Regular Final Answer KeyDocument7 pagesCompre Regular Final Answer KeyManisha JaiswalNo ratings yet

- CST206 Operating Systems, July 2021Document3 pagesCST206 Operating Systems, July 2021Althaf AsharafNo ratings yet

- Tutorial Sheet2014Document7 pagesTutorial Sheet2014Julia DanielNo ratings yet

- Comparch Comparch-002 Exams Midterm A8Xj46NCRoDocument9 pagesComparch Comparch-002 Exams Midterm A8Xj46NCRoMattia LeNo ratings yet

- Reg No: Course CodeDocument8 pagesReg No: Course Codemamudu francisNo ratings yet

- Cse-Viii-Advanced Computer Architectures (06CS81) - Question PaperDocument5 pagesCse-Viii-Advanced Computer Architectures (06CS81) - Question PaperDeepak Ravi ShankarNo ratings yet

- Mca C106Document2 pagesMca C106akhilchaudhary712No ratings yet

- Computer Architecture hw6Document3 pagesComputer Architecture hw6Jason WheelerNo ratings yet

- Indian Institute of Technology, Kharagpur: Mid-Spring Semester 2021-22Document4 pagesIndian Institute of Technology, Kharagpur: Mid-Spring Semester 2021-22Utkarsh PatelNo ratings yet

- NDocument4 pagesNAzri Mohd Khanil0% (1)

- Assignment 1 2020coaDocument5 pagesAssignment 1 2020coaAmit ChinaraNo ratings yet

- Computer Architecture & Organization Assignment Based On PipeliningDocument1 pageComputer Architecture & Organization Assignment Based On Pipeliningsomsom39No ratings yet

- OSDocument148 pagesOSA K SharmaNo ratings yet

- Question Bank - 10ECE65Document4 pagesQuestion Bank - 10ECE65Harshavardhan SJNo ratings yet

- Computer Organization and Architecture Cs2253: Part-ADocument21 pagesComputer Organization and Architecture Cs2253: Part-AjanukarthiNo ratings yet

- Final Sup ExamDocument10 pagesFinal Sup ExamtesfuNo ratings yet

- Computer Science 2Document9 pagesComputer Science 29a37sanskarpitaleNo ratings yet

- Questions 4 1Document95 pagesQuestions 4 1Anik PaulNo ratings yet

- RTOS Question Bank-1Document13 pagesRTOS Question Bank-1SIDDESHWAR VASAMNo ratings yet

- Semester:-Sem IV Branch: - Computer Science and Engineering Subject: - Operating SystemDocument14 pagesSemester:-Sem IV Branch: - Computer Science and Engineering Subject: - Operating SystemYash SugandhiNo ratings yet

- VLSI Interview Questions and AnswersDocument5 pagesVLSI Interview Questions and AnswersMahesh S GourNo ratings yet

- Exec SODocument9 pagesExec SOMohamedAlyNo ratings yet

- Mid+End - September 2022 (Sem 5 - E17)Document21 pagesMid+End - September 2022 (Sem 5 - E17)Sasmitha KalharaNo ratings yet

- Online Food Order System For RestaurantsDocument19 pagesOnline Food Order System For RestaurantsharNo ratings yet

- Unordered - Map - C++ ReferenceDocument3 pagesUnordered - Map - C++ ReferenceKartik MakkarNo ratings yet

- Full AddDocument1 pageFull AddKartik MakkarNo ratings yet

- Suffix Array TutorialDocument17 pagesSuffix Array Tutorialarya5691No ratings yet

- 304 - COE LIC (Raj Senani Sir-2015)Document143 pages304 - COE LIC (Raj Senani Sir-2015)Kartik MakkarNo ratings yet

- Micro-Notes On Microprocessors 2.0Document19 pagesMicro-Notes On Microprocessors 2.0Varun VermaNo ratings yet

- Linux Bash Shell Cheat SheetDocument7 pagesLinux Bash Shell Cheat SheetArdit MeziniNo ratings yet

- Bin SearchDocument1 pageBin SearchKartik MakkarNo ratings yet

- G Soc SelectedDocument1 pageG Soc SelectedKartik MakkarNo ratings yet

- DailyDocument1 pageDailyKartik MakkarNo ratings yet

- Tutorials Point, Simply Easy Learning: Javascript TutorialDocument39 pagesTutorials Point, Simply Easy Learning: Javascript TutorialT.Irudaya Minu PriyaNo ratings yet

- TODODocument1 pageTODOKartik MakkarNo ratings yet

- STL SummaryDocument9 pagesSTL SummaryKartik Makkar100% (1)

- EmptyDocument2 pagesEmptyKartik MakkarNo ratings yet

- FtestDocument1 pageFtestKartik MakkarNo ratings yet

- THNBR EdcjikDocument13 pagesTHNBR EdcjikKartik MakkarNo ratings yet

- Himanshu South AfricaDocument1 pageHimanshu South AfricaKartik MakkarNo ratings yet

- SQLDocument2 pagesSQLKartik MakkarNo ratings yet

- 5 Microprogrammed ControlDocument7 pages5 Microprogrammed ControlKartik MakkarNo ratings yet

- Himanshu South AfricaDocument1 pageHimanshu South AfricaKartik MakkarNo ratings yet

- STL SummaryDocument9 pagesSTL SummaryKartik Makkar100% (1)

- Suffix Array TutorialDocument17 pagesSuffix Array Tutorialarya5691No ratings yet

- Speech WatermarkingDocument7 pagesSpeech WatermarkingKartik MakkarNo ratings yet

- L9 PersprojDocument13 pagesL9 PersprojTrần Bính ĐườngNo ratings yet

- File 18Document6 pagesFile 18Kartik MakkarNo ratings yet

- VLC Media Player Shortcuts: Most UsedDocument1 pageVLC Media Player Shortcuts: Most UsedKartik MakkarNo ratings yet

- Netaji Subhas Institute of Technology: Cut-Off (CRL Rank) SECOND Round (Result Declared On 19/july/2015)Document1 pageNetaji Subhas Institute of Technology: Cut-Off (CRL Rank) SECOND Round (Result Declared On 19/july/2015)Kartik MakkarNo ratings yet

- Scan Conversion Algorithms-2Document22 pagesScan Conversion Algorithms-2Kartik MakkarNo ratings yet

- VLC Media Player Shortcuts: Most UsedDocument1 pageVLC Media Player Shortcuts: Most UsedKartik MakkarNo ratings yet

- Eng100 FL SyllabusDocument13 pagesEng100 FL SyllabusAMPONIN EUNICENo ratings yet

- Kindergarten EllDocument78 pagesKindergarten Elllcpender0% (1)

- Maria Socorro Cancio (National Book Store)Document3 pagesMaria Socorro Cancio (National Book Store)Hadassah AllatisNo ratings yet

- The Big Five Personality Test (BFPT)Document6 pagesThe Big Five Personality Test (BFPT)FatimaNo ratings yet

- Resume Abdullah AljufayrDocument5 pagesResume Abdullah AljufayrAbdullah SalehNo ratings yet

- ARNJE Rosales - EditedDocument18 pagesARNJE Rosales - EditedDarwinNo ratings yet

- KiDS COR Policies and Procedures 2009-2010Document3 pagesKiDS COR Policies and Procedures 2009-2010Nick RansomNo ratings yet

- Pre Nursery To Grade 10 Sports Day Circular Circular 58 19.12.2022-1Document3 pagesPre Nursery To Grade 10 Sports Day Circular Circular 58 19.12.2022-1Yashraj SNo ratings yet

- Caribbean Secondary Examination Certificate School Based Assignment English Language SBADocument15 pagesCaribbean Secondary Examination Certificate School Based Assignment English Language SBASSGXCR0% (1)

- R. Bieringer, D. Kurek-Chomycz, E. Nathan 2 Corinthians A Bibliography Biblical Tools and Studies, Vol 5 2008 PDFDocument367 pagesR. Bieringer, D. Kurek-Chomycz, E. Nathan 2 Corinthians A Bibliography Biblical Tools and Studies, Vol 5 2008 PDFManticora Caelestis100% (1)

- Rubric SDocument3 pagesRubric SFritzie AileNo ratings yet

- Toast Master - MentoringDocument14 pagesToast Master - MentoringYogeeshwaran PonnuchamyNo ratings yet

- Condonation Application Form 2018 - 12 - 6 - 18Document2 pagesCondonation Application Form 2018 - 12 - 6 - 18tom jacobNo ratings yet

- Creative WritingDocument5 pagesCreative WritingAbegail FernandoNo ratings yet

- Experiments With An Axial Fan: Page 1/3 10/2010Document3 pagesExperiments With An Axial Fan: Page 1/3 10/2010Priyam ParasharNo ratings yet

- v1 AC7163 AutoCAD Certified Associate HandoutDocument11 pagesv1 AC7163 AutoCAD Certified Associate HandoutaudioxtraNo ratings yet

- Fast FashionDocument13 pagesFast FashionHelmi SuhaimiNo ratings yet

- Manual Critical Reading Analytical Writing and Peer FeedbackDocument9 pagesManual Critical Reading Analytical Writing and Peer FeedbackMaria ChernykhNo ratings yet

- Writers Craft LP - Day 1Document9 pagesWriters Craft LP - Day 1api-357297274No ratings yet

- Cyclothymia, A Circular Mood Disorder by Ewald Hecker Introduction by Christopher Baethge, A, B Paola Salvatoreb, C and Ross J. BaldessarinibDocument15 pagesCyclothymia, A Circular Mood Disorder by Ewald Hecker Introduction by Christopher Baethge, A, B Paola Salvatoreb, C and Ross J. Baldessarinibrustycarmelina108No ratings yet

- Unit 8 E10 KeyDocument7 pagesUnit 8 E10 KeyThảo Nguyên-32-9350% (4)

- Chapter 8 Conflict & NegotiationDocument15 pagesChapter 8 Conflict & NegotiationJiaChuin PangNo ratings yet

- The Worst Jam Flavour - Traffic Jam (Form 4 Lesson Plan)Document4 pagesThe Worst Jam Flavour - Traffic Jam (Form 4 Lesson Plan)Katherine TeoNo ratings yet

- HRM7503A - 2 Individual and Reflective LearningDocument20 pagesHRM7503A - 2 Individual and Reflective LearningHafsa YousufNo ratings yet

- Facebook Addiction and Academic Anxiety Among University StudentsDocument16 pagesFacebook Addiction and Academic Anxiety Among University StudentsLawson SohNo ratings yet

- Used Strategies For Providing Timely, Accurate and Constructive Feedback To Improve Learner PerformanceDocument17 pagesUsed Strategies For Providing Timely, Accurate and Constructive Feedback To Improve Learner PerformancemaristellaNo ratings yet

- Guiding Young ChildrenDocument4 pagesGuiding Young ChildrenAljon MalotNo ratings yet

- How To Tame A Wild Tongue Dual Entry NotesDocument2 pagesHow To Tame A Wild Tongue Dual Entry Notesapi-336093393No ratings yet

- We Said Feminist Fairy Tales Not Fractured Fairy TDocument6 pagesWe Said Feminist Fairy Tales Not Fractured Fairy TMaggie Tang100% (1)

- Narrative On Parents-Teachers Orientation 22-23Document3 pagesNarrative On Parents-Teachers Orientation 22-23Giselle Sadural CariñoNo ratings yet

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsFrom EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsRating: 5 out of 5 stars5/5 (2)

- CompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)From EverandCompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)Rating: 5 out of 5 stars5/5 (1)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]From EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Rating: 5 out of 5 stars5/5 (2)

- Chip War: The Fight for the World's Most Critical TechnologyFrom EverandChip War: The Fight for the World's Most Critical TechnologyRating: 4.5 out of 5 stars4.5/5 (82)

- Chip War: The Quest to Dominate the World's Most Critical TechnologyFrom EverandChip War: The Quest to Dominate the World's Most Critical TechnologyRating: 4.5 out of 5 stars4.5/5 (227)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102From EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Rating: 5 out of 5 stars5/5 (2)

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XFrom EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XRating: 3 out of 5 stars3/5 (2)

- Computer Science: A Concise IntroductionFrom EverandComputer Science: A Concise IntroductionRating: 4.5 out of 5 stars4.5/5 (14)

- Mastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFFrom EverandMastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFNo ratings yet

- Hacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxFrom EverandHacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxNo ratings yet

- Windows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertFrom EverandWindows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertRating: 3.5 out of 5 stars3.5/5 (6)

- Amazon Web Services (AWS) Interview Questions and AnswersFrom EverandAmazon Web Services (AWS) Interview Questions and AnswersRating: 4.5 out of 5 stars4.5/5 (3)

- iWoz: How I Invented the Personal Computer and Had Fun Along the WayFrom EverandiWoz: How I Invented the Personal Computer and Had Fun Along the WayRating: 3.5 out of 5 stars3.5/5 (317)

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002From EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Rating: 5 out of 5 stars5/5 (1)

- How to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideFrom EverandHow to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideRating: 1 out of 5 stars1/5 (1)

- Essential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XFrom EverandEssential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XRating: 5 out of 5 stars5/5 (1)

- Programming with STM32: Getting Started with the Nucleo Board and C/C++From EverandProgramming with STM32: Getting Started with the Nucleo Board and C/C++Rating: 3.5 out of 5 stars3.5/5 (3)

- Amazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesFrom EverandAmazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesNo ratings yet

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-2-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1714829744?v=1)