Professional Documents

Culture Documents

Sic 789 A

Uploaded by

FlorinMacoveiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Sic 789 A

Uploaded by

FlorinMacoveiCopyright:

Available Formats

SiC789, SiC789A

www.vishay.com

Vishay Siliconix

60 A VRPower Integrated Power Stage

DESCRIPTION FEATURES

The SiC789 and SiC789A are integrated power stage Thermally enhanced PowerPAK MLP66-40L

solutions optimized for synchronous buck applications to package

offer high current, high efficiency, and high power Vishays Gen IV MOSFET technology and a

density performance. Packaged in Vishays proprietary low-side MOSFET with integrated Schottky

6 mm x 6 mm MLP package, SiC789 and SiC789A enable diode

voltage regulator designs to deliver up to 60 A continuous Delivers up to 60 A continuous current

current per phase.

95 % peak efficiency

The internal power MOSFETs utilize Vishays High frequency operation up to 1.5 MHz

state-of-the-art Gen IV TrenchFET technology that delivers

Power MOSFETs optimized for 12 V input stage

industry benchmark performance to significantly reduce

switching and conduction losses. 3.3 V (SiC789A) / 5 V (SiC789) PWM logic with tri-state and

hold-off

The SiC789 and SiC789A incorporate an advanced

MOSFET gate driver IC that features high current driving SMOD# logic for light load efficiency improvement

capability, adaptive dead-time control, an integrated Low PWM propagation delay (< 20 ns)

bootstrap Schottky diode, a thermal warning (THWn) that Thermal monitor flag

alerts the system of excessive junction temperature, and Faster enable / disable

skip mode (SMOD#) to improve light load efficiency. The

Under voltage lockout for VCIN

drivers are also compatible with a wide range of PWM

controllers and supports tri-state PWM, 3.3 V (SiC789A) / Material categorization: for definitions of compliance

5 V (SiC789) PWM logic. please see www.vishay.com/doc?99912

APPLICATIONS

Multi-phase VRDs for CPU, GPU, and memory

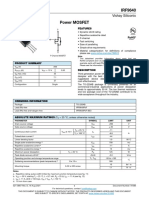

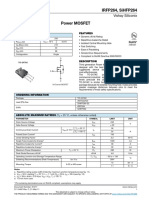

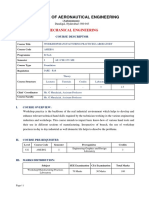

TYPICAL APPLICATION DIAGRAM

5V VIN

VDRV

GH

V IN

BOOT

VCIN PHASE

SMOD#

VSWH

DSBL# Gate VOUT

PWM

controller PWM driver

THWn

C GND

GL

PGND

Fig. 1 - SiC789 and SiC789A Typical Application Diagram

S14-2287-Rev. B, 08-Dec-14 1 Document Number: 62972

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

SiC789, SiC789A

www.vishay.com

Vishay Siliconix

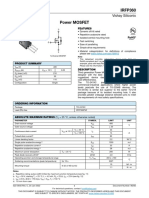

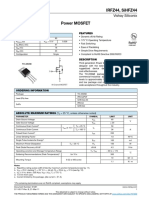

PINOUT CONFIGURATION

39 DSBL#

39 DSBL#

37 CGND

35 VSWH

34 VSWH

33 VSWH

32 VSWH

31 VSWH

31 VSWH

32 VSWH

33 VSWH

34 VSWH

35 VSWH

37 CGND

38 THWn

38 THWn

40 PWM

40 PWM

36 GL

36 GL

SMOD# 1 30 VSWH VSWH 30 1 SMOD#

VCIN 2 29 VSWH VSWH 29 2 VCIN

VDRV 3 41 28 PGND PGND 28 41 3 VDRV

CGND CGND

BOOT 4 27 PGND PGND 27 4 BOOT

CGND 5 26 PGND PGND 26 5 CGND

43 43

VSWH VSWH

GH 6 25 PGND PGND 25 6 GH

PHASE 7 24 PGND PGND 24 7 PHASE

42 42

VIN 8 VIN 23 PGND PGND 23 VIN 8 VIN

VIN 9 22 PGND PGND 22 9 VIN

VIN 10 21 PGND PGND 21 10 VIN

PGND 18

PGND 20

PGND 19

PGND 17

PGND 16

VSWH 15

PGND 16

PGND 17

PGND 18

PGND 19

PGND 20

VSWH 15

VIN 14

VIN 13

VIN 12

VIN 11

VIN 11

VIN 12

VIN 13

VIN 14

Top view Bottom view

Fig. 2 - SiC789 and SiC789A Pin Configuration

PIN DESCRIPTION

PIN NUMBER NAME FUNCTION

1 SMOD# Low-side gate turn-off logic. Active low

2 VCIN Supply voltage for internal logic circuitry

3 VDRV Supply voltage for internal gate driver

4 BOOT High-side driver bootstrap voltage

5, 37, 41 CGND Analog ground for the driver IC

6 GH High-side gate signal

7 PHASE Return path of high-side gate driver

8 to 14, 42 VIN Power stage input voltage. Drain of high-side MOSFET

15, 29 to 35, 43 VSWH Switch node of the power stage

16 to 28 PGND Power ground

36 GL Low-side gate signal

38 THWn Thermal warning open drain output

39 DSBL# Disable pin. Active low

40 PWM PWM control input

ORDERING INFORMATION

PART NUMBER PACKAGE MARKING CODE OPTION

SiC789ACD-T1-GE3 SiC789A 3.3 V PWM optimized

PowerPAK MLP66-40L

SiC789CD-T1-GE3 SiC789 5 V PWM optimized

SiC789ADB and SiC789DB Reference board

S14-2287-Rev. B, 08-Dec-14 2 Document Number: 62972

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

SiC789, SiC789A

www.vishay.com

Vishay Siliconix

ABSOLUTE MAXIMUM RATINGS

ELECTRICAL PARAMETER CONDITIONS LIMIT UNIT

Input Voltage VIN -0.3 to +25

Control Logic Supply Voltage VCIN -0.3 to +7

Drive Supply Voltage VDRV -0.3 to +7

Switch Node (DC voltage) -0.3 to +25

VSWH

Switch Node (AC voltage) (1) -8 to +30

BOOT Voltage (DC voltage) 32 V

VBOOT

BOOT Voltage (AC voltage) (2) 38

BOOT to PHASE (DC voltage) -0.3 to +7

VBOOT- PHASE

BOOT to PHASE (AC voltage) (3) -0.3 to +8

All Logic Inputs and Outputs

-0.3 to VCIN + 0.3

(PWM, DSBL#, and THWn)

fS = 300 kHz, VIN = 12 V, VOUT = 1.8 V 60

Output Current, IOUT(AV) (4) A

fS = 1 MHz, VIN = 12 V, VOUT = 1.8 V 50

Max. Operating Junction Temperature TJ 150

Ambient Temperature TA -40 to +125 C

Storage Temperature Tstg -65 to +150

Human body model, JESD22-A114 5000

Electrostatic Discharge Protection V

Charged device model, JESD22-C101 1000

Note

(1) The specification values indicated AC is V

SWH to PGND, -8 V (< 20 ns, 10 J), min. and 30 V (< 50 ns), max.

(2) The specification value indicates AC voltage is V

BOOT to PGND, 36 V (< 50 ns) max.

(3) The specification value indicates AC voltage is V

BOOT to VPHASE, 8 V (< 20 ns) max.

(4) Output current rated with testing evaluation board at T = 25 C with natural convection cooling. The rating is limited by the peak evaluation

A

board temperature, TJ = 150 C, and varies depending on the operating conditions and PCB layout. This rating may be changed with different

application settings.

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation

of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum

rating conditions for extended periods may affect device reliability.

RECOMMENDED OPERATING RANGE

ELECTRICAL PARAMETER MINIMUM TYPICAL MAXIMUM UNIT

Input Voltage (VIN) 4.5 - 18

Drive Supply Voltage (VDRV) 4.5 5 5.5

V

Control Logic Supply Voltage (VCIN) 4.5 5 5.5

BOOT to PHASE (VBOOT-PHASE, DC voltage) 4 4.5 5.5

Thermal Resistance from Junction to PAD - 1 -

C/W

Thermal Resistance from Junction to Case - 2.5 -

S14-2287-Rev. B, 08-Dec-14 3 Document Number: 62972

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

SiC789, SiC789A

www.vishay.com

Vishay Siliconix

ELECTRICAL SPECIFICATIONS

(DSBL# = SMOD# = 5 V, VIN = 12 V, VDRV and VCIN = 5 V, TA = 25 C)

LIMITS

PARAMETER SYMBOL TEST CONDITION UNIT

MIN. TYP. MAX.

POWER SUPPLY

VDSBL# = 0 V, no switching, VPWM = FLOAT - 85 -

Control Logic Supply Current IVCIN VDSBL# = 5 V, no switching, VPWM = FLOAT - 290 - A

VDSBL# = 5 V, fS = 300 kHz, D = 0.1 - 295 -

fS = 300 kHz, D = 0.1 - 16 25

mA

fS = 1 MHz, D = 0.1 - 50 -

Drive Supply Current IVDRV

VDSBL# = 0 V, no switching - 35 -

A

VDSBL# = 5 V, no switching - 60 -

BOOTSTRAP SUPPLY

Bootstrap Diode Forward Voltage VF IF = 2 mA 0.4 V

PWM CONTROL INPUT (SiC789)

Rising Threshold VTH_PWM_R 3.4 3.7 4.0

Falling Threshold VTH_PWM_F 0.72 0.9 1.1

Tri-state Voltage VTRI VPWM = FLOAT - 2.3 - V

Tri-state Rising Threshold VTRI_TH_R 0.9 1.15 1.38

Tri-state Falling Threshold VTRI_TH_F 3.1 3.35 3.6

Tri-state Rising Threshold

VHYS_TRI_R - 225 -

Hysteresis

mV

Tri-state Falling Threshold

VHYS_TRI_F - 325 -

Hysteresis

VPWM = 5 V - - 350

PWM Input Current IPWM A

VPWM = 0 V - - -350

PWM CONTROL INPUT (SiC789A)

Rising Threshold VTH_PWM_R 2.2 2.45 2.7

Falling Threshold VTH_PWM_F 0.72 0.9 1.1

Tri-state Voltage VTRI VPWM = FLOAT - 1.8 - V

Tri-state Rising Threshold VTRI_TH_R 0.9 1.15 1.38

Tri-state Falling Threshold VTRI_TH_F 1.95 2.2 2.45

Tri-state Rising Threshold

VHYS_TRI_R - 225 -

Hysteresis

mV

Tri-state Falling Threshold

VHYS_TRI_F - 275 -

Hysteresis

VPWM = 3.3 V - - 225

PWM Input Current IPWM A

VPWM = 0 V - - -225

TIMING SPECIFICATIONS

Tri-State to GH/GL Rising

tPD_TRI_R - 30 -

Propagation Delay

Tri-state Hold-Off Time tTSHO - 130 -

GH - Turn Off Propagation Delay tPD_OFF_GH - 18 -

GH - Turn On Propagation Delay No load, see fig. 4

tPD_ON_GH - 10 -

(Dead time rising)

GL - Turn Off Propagation Delay tPD_OFF_GL - 12 -

ns

GL - Turn On Propagation Delay

tPD_ON_GL - 10 -

(Dead time falling)

DSBL# Low to GH/GL Falling

tPD_DSBL#_F Fig. 5 - 15 -

Propagation Delay

DSBL# High to GH/GL Rising

tPD_DSBL#_R Fig. 5 - 20 -

Propagation Delay

PWM Minimum On-Time tPWM_ON_MIN 30 - -

S14-2287-Rev. B, 08-Dec-14 4 Document Number: 62972

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

SiC789, SiC789A

www.vishay.com

Vishay Siliconix

ELECTRICAL SPECIFICATIONS

(DSBL# = SMOD# = 5 V, VIN = 12 V, VDRV and VCIN = 5 V, TA = 25 C)

LIMITS

PARAMETER SYMBOL TEST CONDITION UNIT

MIN. TYP. MAX.

DSBL# SMOD# INPUT

VIH_DSBL# Input logic high 2 - -

DSBL# Logic Input Voltage

VIL_DSBL# Input logic low - - 0.8

V

VIH_SMOD# Input logic high 2 - -

SMOD# Logic Input Voltage

VIL_SMOD# Input logic low - - 0.8

PROTECTION

VCIN rising, on threshold - 3.7 4.1

Under Voltage Lockout VUVLO V

VCIN falling, off threshold 2.7 3.1 -

Under Voltage Lockout Hysteresis VUVLO_HYST - 575 - mV

THWn Flag Set (2) TTHWn_SET - 160 -

THWn Flag Clear (2) TTHWn_CLEAR - 135 - C

THWn Flag Hysteresis (2) TTHWn_HYST - 25 -

THWn Output Low VOL_THWn ITHWn = 2 mA - 0.02 - V

Notes

(1) Typical limits are established by characterization and are not production tested.

(2) Guaranteed by design.

DETAILED OPERATIONAL DESCRIPTION

PWM Input with Tri-state Function Pre-Charger Function

The PWM input receives the PWM control signal from the VR When DSBL# is driven from below VIL_DSBL# to above

controller IC. The PWM input is designed to be compatible VIH_DSBL# the low-side is turned ON for a short duration

with standard controllers using two state logic (H and L) and (60 ns typical) to refresh the BOOT capacitor in case it has

advanced controllers that incorporate tri-state logic (H, L been discharged due to the driver being in standby for a

and tri-state) on the PWM output. For two state logic, the long period of time.

PWM input operates as follows. When PWM is driven above

Diode Emulation Mode (SMOD#)

VPWM_TH_R the low-side is turned OFF and the high-side is

turned ON. When PWM input is driven below VPWM_TH_F the When SMOD# is logic low diode emulation mode is enabled

high-side is turned OFF and the low-side is turned ON. For and the low-side is turned OFF. This is a non-synchronous

tri-state logic, the PWM input operates as previously stated conversion mode that improves light load efficiency by

for driving the MOSFETs when PWM is logic high and logic reducing switching losses. Conducted losses that occur in

low. However, there is a third state that is entered as the synchronous buck regulators when inductor current is

PWM output of tri-state compatible controller enters its high negative can also be reduced. Circuitry in the external

impedance state during shut-down. The high impedance controller IC detects when inductor current crosses zero

state of the controllers PWM output allows the SiC789 and and drives SMOD# below VIL_SMOD# turning the low-side

SiC789A to pull the PWM input into the tri-state region (see MOSFET OFF. The function can be also be used for a

definition of PWM logic and Tri-State, fig. 4). If the PWM pre-biased output voltage. If SMOD# is left unconnected, an

input stays in this region for the Tri-state Hold-Off Period, internal pull up resistor will pull the pin to VCIN (logic high) to

tTSHO, both high-side and low-side MOSFETs are turned disable the SMOD# function.

OFF. The function allows the VR phase to be disabled Thermal Shutdown Warning (THWn)

without negative output voltage swing caused by inductor

The THWn pin is an open drain signal that flags the presence

ringing and saves a Schottky diode clamp. The PWM and

of excessive junction temperature. Connect, with a

tri-state regions are separated by hysteresis to prevent

maximum of 20 k, to VCIN. An internal temperature sensor

false triggering. The SiC789A incorporates PWM voltage

detects the junction temperature. The temperature

thresholds that are compatible with 3.3 V logic and the

threshold is 160 C. When this junction temperature is

SiC789 thresholds are compatible with 5 V logic.

exceeded the THWn flag is set. When the junction

Disable (DSBL#) temperature drops below 135 C the device will clear the

In the low state, the DSBL# pin shuts down the driver IC and THWn signal. The SiC789 and SiC789A do not stop

disables both high-side and low-side MOSFETs. In this operation when the flag is set. The decision to shutdown

state, standby current is minimized. If DSBL# is left must be made by an external thermal control function.

unconnected, an internal pull-down resistor will pull the pin

to CGND and shut down the IC.

S14-2287-Rev. B, 08-Dec-14 5 Document Number: 62972

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

SiC789, SiC789A

www.vishay.com

Vishay Siliconix

Voltage Input (VIN) Bootstrap Circuit (BOOT)

This is the power input to the drain of the high-side power The internal bootstrap diode and an external bootstrap

MOSFET. This pin is connected to the high power capacitor form a charge pump that supplies voltage to the

intermediate BUS rail. BOOT pin. An integrated bootstrap diode is incorporated so

that only an external capacitor is necessary to complete the

Switch Node (VSWH and PHASE)

bootstrap circuit. Connect a boot strap capacitor with one

The switch node, VSWH, is the circuit power stage output. leg tied to BOOT pin and the other tied to PHASE pin.

This is the output applied to the power inductor and output

filter to deliver the output for the buck converter. The PHASE Shoot-Through Protection and Adaptive Dead Time

pin is internally connected to the switch node, VSWH. This pin The SiC789 and SiC789A have an internal adaptive logic to

is to be used exclusively as the return pin for the BOOT avoid shoot through and optimize dead time. The shoot

capacitor. A 20 k resistor is connected between GH and through protection ensures that both high-side and low-side

PHASE to provide a discharge path for the HS MOSFET in MOSFETs are not turned ON at the same time. The adaptive

the event that VCIN goes to zero while VIN is still applied. dead time control operates as follows. The high-side and

low-side gate voltages are monitored to prevent the

Ground Connections (CGND and PGND)

MOSFET turning ON from tuning ON until the other

PGND (power ground) should be externally connected to MOSFET's gate voltage is sufficiently low (< 1 V). Built in

CGND (control signal ground). The layout of the printed circuit delays also ensure that one power MOSFET is completely

board should be such that the inductance separating CGND OFF, before the other can be turned ON. This feature helps

and PGND is minimized. Transient differences due to to adjust dead time as gate transitions change with respect

inductance effects between these two pins should not to output current and temperature.

exceed 0.5 V

Under Voltage Lockout (UVLO)

Control and Drive Supply Voltage Input (VDRV, VCIN)

During the start up cycle, the UVLO disables the gate

VCIN is the bias supply for the gate drive control IC. VDRV is drive, holding high-side and low-side MOSFET gates low,

the bias supply for the gate drivers. It is recommended to until the supply voltage rail has reached a point at which

separate these pins through a resistor. This creates a low the logic circuitry can be safely activated. The SiC789 and

pass filtering effect to avoid coupling of high frequency gate SiC789A also incorporate logic to clamp the gate drive

drive noise into the IC. signals to zero when the UVLO falling edge triggers the

shutdown of the device. As an added precaution, a 20 k

resistor is connected between GH and PHASE to provide a

discharge path for the HS MOSFET.

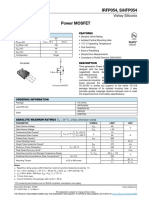

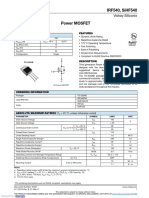

FUNCTIONAL BLOCK DIAGRAM

THWn BOOT GH V IN

VDRV

Thermal monitor

& warning

V CIN UVLO

DSBL#

VCIN

- 20K

+ PHASE

PWM logic Anti-cross

GL Vref = 1 V

control & conduction

PWM state control VSWH

-

machine logic

+

Vref = 1 V

VDRV

C GND

SMOD# GL PGND

Fig. 3 - SiC789 and SiC789A Functional Block Diagram

S14-2287-Rev. B, 08-Dec-14 6 Document Number: 62972

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

SiC789, SiC789A

www.vishay.com

Vishay Siliconix

DEVICE TRUTH TABLE

DSBL# SMOD# PWM GH GL

Open X X L L

L X X L L

H L L L L

H L H H L

H L Tri-state L L

H H L L H

H H H H L

H H Tri-state L L

PWM TIMING DIAGRAM

VTH_PWM_R

VTH_TRI_F

VTH_TRI_R

VTH_PWM_F

PWM

t PD_OFF_GL

t TSHO

GL

t PD_ON_GL

t PD_TRI_R

t TSHO

t PD_ON_GH t PD_OFF_GH

t PD_TRI_R

GH

Fig. 4 - Definition of PWM Logic and Tri-State

S14-2287-Rev. B, 08-Dec-14 7 Document Number: 62972

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

SiC789, SiC789A

www.vishay.com

Vishay Siliconix

OPERATION TIMING DIAGRAM: DSBL#

PWM PWM

DSBL # Enable DSBL #

GH GH

GL GL

t t

DSBL# High to GH Rising Propagation Delay DSBL# High to GL Rising Propagation Delay

PWM PWM

DSBL # Disable DSBL #

GH GH

GL GL

t t

DSBL# Low to GH Falling Propagation Delay DSBL# Low to GL Falling Propagation Delay

Fig. 5 - DSBL# Propagation Delay

S14-2287-Rev. B, 08-Dec-14 8 Document Number: 62972

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

SiC789, SiC789A

www.vishay.com

Vishay Siliconix

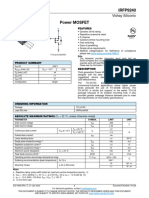

ELECTRICAL CHARACTERISTICS

Test condition: VIN = 12 V, VDRV = VCIN = 5 V, DSBL# = SMOD# = 5 V, VOUT = 1 V, LOUT = 270 nH (DCR = 0.32 m), TA = 25 C

(All power loss and normalized power loss curves show SiC789 and SiC789A losses only unless otherwise stated)

94 12.0

90 300 kHz 10.5

500 kHz

86 9.0 1 MHz

1 MHz

Power Loss, PL (W)

82 7.5

Efficiency (%)

800 kHz

78 6.0

800 kHz

74 4.5

300 kHz

70 Complete converter efficiency 3.0

PIN = [(VIN x IIN) + 5 V x (IVDRV + IVCIN)]

POUT = VOUT x IOUT, measured at output capacitor

66 1.5

500 kHz

62 0.0

0 5 10 15 20 25 30 35 40 45 50 55 0 5 10 15 20 25 30 35 40 45 50 55

Output Current, IOUT (A) Output Current, IOUT (A)

Fig. 6 - Efficiency vs. Output Current Fig. 9 - Power Loss vs. Output Current

94 12.0

VOUT = 1.0V

90 10.5

VOUT = 0.9V

fS = 500 kHz

86 9.0

VOUT = 0.7V

Power Loss, PL (W)

VOUT = 0.7 V

7.5 VOUT = 0.8 V

Efficiency (%)

82

VOUT = 0.9 V

VOUT = 0.8V

VOUT = 1.0 V

78 6.0

74 4.5

70 3.0

fS = 500kHz

66 1.5

62 0.0

0 5 10 15 20 25 30 35 40 45 50 55 0 5 10 15 20 25 30 35 40 45 50 55

Output Current, IOUT (A) Output Current, IOUT (A)

Fig. 7 - Efficiency vs. Output Current Fig. 10 - Power Loss vs. Output Current

8.0 64

7.0 56

fS = 300 kHz

300 kHz

6.0 48

Output Current, IOUT (A)

Power Loss, PL (W)

1 MHz

5.0 40

VOUT = 0.7 V

4.0 VOUT = 0.8 V 32

VOUT = 0.9 V

3.0 VOUT = 1.0 V 24

2.0 16

1.0 8

0.0 0

0 5 10 15 20 25 30 35 40 45 50 55 0 15 30 45 60 75 90 105 120 135 150

Output Current, IOUT (A) PCB Temperature, TPCB (C)

Fig. 8 - Power Loss vs. Output Current Fig. 11 - Safe Operating Area

S14-2287-Rev. B, 08-Dec-14 9 Document Number: 62972

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

SiC789, SiC789A

www.vishay.com

Vishay Siliconix

1.80 1.20

1.65 1.16

Normalized Driver Supply Current

1.50

Normalized Power Loss

1.12

300 kHz

1.35 1.08

1.20 1.04

1.05 1.00

0.90 0.96 1 MHz

0.75 0.92

0.60 0.88

200 300 400 500 600 700 800 900 1000 1100 1200 0 5 10 15 20 25 30 35 40 45 50 55

Switching Frequency, fS (kHz) Output Current, IOUT (A)

Fig. 12 - Power Loss vs. Switching Frequency Fig. 15 - Driver Supply Current vs. Output Current

4.2 0.40

4.0 0.35

IF = 2 mA

BOOT Diode Forward Voltage, VF (V)

Control Logic Supply Voltage, VCIN (V)

3.8 VUVLO_RISING 0.30

3.6 0.25

3.4 0.20

3.2 0.15

3.0 VUVLO_FALLING 0.10

2.8 0.05

2.6 0.00

-60 -40 -20 0 20 40 60 80 100 120 140 -60 -40 -20 0 20 40 60 80 100 120 140

Temperature (C) Temperature (C)

Fig. 13 - UVLO Threshold vs. Temperature Fig. 16 - BOOT Diode Forward Voltage vs. Temperature

3.4 3.2

3.0 2.8 VTH_PWM_R

PWM Threshold Voltage, VPWM (V)

PWM Threshold Voltage, VPWM (V)

VTH_PWM_R

2.6 2.4

VTRI_TH_F

2.2 2.0

VTRI_TH_F

VTRI

1.8 1.6

VTRI

VTRI_TH_R

1.4 1.2

VTRI_TH_R

1.0 0.8

VTH_PWM_F

0.6 VTH_PWM_F 0.4

0.2 0.0

-60 -40 -20 0 20 40 60 80 100 120 140 4.5 4.6 4.7 4.8 4.9 5.0 5.1 5.2 5.3 5.4 5.5

Temperature (C) Driver Supply Voltage, VCIN (V)

Fig. 14 - PWM Threshold vs. Temperature (SiC789A) Fig. 17 - PWM Threshold vs. Driver Supply Voltage (SiC789A)

S14-2287-Rev. B, 08-Dec-14 10 Document Number: 62972

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

SiC789, SiC789A

www.vishay.com

Vishay Siliconix

4.8 4.8

4.2 4.2 VTH_PWM_R

PWM Threshold Voltage, VPWM (V)

VTH_PWM_R

PWM Threshold Voltage, VPWM (V)

3.6 3.6

VTRI_TH_F

3.0 VTRI_TH_F 3.0

2.4 2.4

VTRI VTRI

1.8 1.8

VTRI_TH_R VTRI_TH_R

1.2 1.2

0.6 0.6 VTH_PWM_F

VTH_PWM_F

0.0 0.0

-60 -40 -20 0 20 40 60 80 100 120 140 4.5 4.6 4.7 4.8 4.9 5.0 5.1 5.2 5.3 5.4 5.5

Temperature (C) Driver Supply Voltage, VCIN (V)

Fig. 18 - PWM Threshold vs. Temperature (SiC789) Fig. 21 - PWM Threshold vs. Driver Supply Voltage (SiC789)

2.2 2.2

2.0 DSBL# Threshold Voltage, VDSBL# (V) 2.0

DSBL# Threshold Voltage, VDSBL# (V)

1.8 1.8

VIH_DSBL# VIH_DSBL#

1.6 1.6

1.4 1.4

VIL_DSBL#

1.2 1.2

1.0 VIL_DSBL# 1.0

0.8 0.8

0.6 0.6

-60 -40 -20 0 20 40 60 80 100 120 140 4.5 4.6 4.7 4.8 4.9 5.0 5.1 5.2 5.3 5.4 5.5

Temperature (C) Driver Supply Voltage, VCIN (V)

Fig. 19 - DSBL# Threshold vs. Temperature Fig. 22 - DSBL# Threshold vs. Driver Supply Voltage

2.2 2.2

2.0 2.0

SMOD# Threshold Voltage, VSMOD# (V)

SMOD# Threshold Voltage, VSMOD# (V)

1.8 1.8

VIH_SMOD# VIH_SMOD#

1.6 1.6

1.4 1.4

VIL_SMOD#

1.2 1.2

1.0 VIL_SMOD# 1.0

0.8 0.8

0.6 0.6

-60 -40 -20 0 20 40 60 80 100 120 140 4.5 4.6 4.7 4.8 4.9 5.0 5.1 5.2 5.3 5.4 5.5

Temperature (C) Driver Supply Voltage, VCIN (V)

Fig. 20 - SMOD# Threshold vs. Temperature Fig. 23 - SMOD# Threshold vs. Driver Supply Voltage

S14-2287-Rev. B, 08-Dec-14 11 Document Number: 62972

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

SiC789, SiC789A

www.vishay.com

Vishay Siliconix

12.0 -8.0

11.5 -8.5

SMOD# Pull-Up Current, ISMOD# (uA)

DSBL# Pull-Down Current, IDSBL# (uA)

VSMOD# = 0 V

11.0 -9.0

10.5 -9.5

10.0 -10.0

9.5 -10.5

9.0 -11.0

8.5 -11.5

8.0 -12.0

-60 -40 -20 0 20 40 60 80 100 120 140 -60 -40 -20 0 20 40 60 80 100 120 140

Temperature (C) Temperature (C)

Fig. 24 - DSBL# Pull-down Current vs. Temperature Fig. 26 - SMOD# Pull-up Current vs. Temperature

200 430

180 410

VPWM = FLOAT

VDSBL# = 0 V

Driver Supply Current, IVDVR & IVCIN (V)

Driver Supply Current, IVDVR & IVCIN (V)

160 390

140 370

120 350

100 330

80 310

60 290

40 270

-60 -40 -20 0 20 40 60 80 100 120 140 -60 -40 -20 0 20 40 60 80 100 120 140

Temperature (C) Temperature (C)

Fig. 25 - Driver Shutdown Current vs. Temperature Fig. 27 - Driver Quiescent Current vs. Temperature

S14-2287-Rev. B, 08-Dec-14 12 Document Number: 62972

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

SiC789, SiC789A

www.vishay.com

Vishay Siliconix

PCB LAYOUT RECOMMENDATIONS

Step 1: VIN / PGND Planes and Decoupling Step 3: VCIN / VDRV Input Filter

V IN Plane

Vias for ground connection

CGND

PGND

Cvdrv

V IN CGND

V SWH Cvcin

PGND Plane

1. Layout VIN and PGND planes as shown above 1. VCIN / VDRV input filter ceramic capacitors should be

2. Ceramic capacitors should be placed directly between placed as close as possible to IC. It is recommended to

VIN and PGND, and as close as possible to IC for best connect two capacitors separately

decoupling effect 2. VCIN capacitor should be placed between pin 2 and

3. Different ceramic capacitor values and packages should pin 37 (CGND of driver IC) to achieve best noise filtering

be used to cover entire decoupling spectrum, e.g. 1210, 3. VDRV capacitor should be placed between pin 3 and

0805, 0603, and 0402 PGND to provide maximum instantaneous driver current

4. Smaller capacitance values, placed closer to the ICs VIN for low-side MOSFET during switching cycle. PGND can

pin(s), result in better high frequency noise absorbing be connected to inner ground plane through vias, as

shown above

Step 2: VSWH Plane 4. Pin 5 and pin 37 should be connected with CGND pad, as

shown above

5. For connecting VCIN to CGND, it is recommended to use

a large plane to reduce parasitic inductance

Step 4: BOOT Resistor and Capacitor Placement

CGND

Snubber

V SWH

PGND Plane

1. Connect output inductor to IC with large plane to lower

resistance

2. VSWH plane also serves as a heat-sink for low-side

MOSFET. Please make the plane wide and short to

achieve best thermal path

3. If a snubber network is required, place components as 1. The components need to be placed as close as possible

shown above to IC, directly between PHASE (pin 7) and BOOT (pin 4)

2. To reduce parasitic inductance, 0402 package size can

be used

S14-2287-Rev. B, 08-Dec-14 13 Document Number: 62972

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

SiC789, SiC789A

www.vishay.com

Vishay Siliconix

Step 5: Signal Routing Step 7: Ground Connection

CGND

CGND

CGND

GND Plane

PGND

1. Route the PWM, SMOD#, DSBL#, and THWn signal 1. It is recommended to make the entire first inner layer

traces out of the top right corner, next to pin 1 (below top layer) the ground plane

2. The PWM signal is a very important signal, both signal 2. The ground plane provides analog ground and power

and return traces should not cross any power nodes on ground connections

any layer 3. The ground plane provides shielding between noise

3. It is best to shield these traces from power switching source on top layer and signal traces on bottom layer

nodes, e.g. VSWH, with a GND island to improve signal

integrity

Step 6: Adding Thermal Relief Vias

V IN Plane

V IN CGND

V SWH

PGND Plane

1. Thermal relief vias can be added to the VIN and CGND

pads to utilize inner layers for high-current and thermal

dissipation

2. To achieve better thermal performance, additional vias

can be added to VIN and PGND planes

3. The VSWH pad is a noise source and it is not

recommended to place vias on this pad

4. 8 mil drill for pads and 10 mils drill for planes are the

optional via sizes. Vias on pad may drain solder during

assembly and cause assembly issues. Please consult

with the assembly house for guidelines

S14-2287-Rev. B, 08-Dec-14 14 Document Number: 62972

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

SiC789, SiC789A

www.vishay.com

Vishay Siliconix

RECOMMENDED LAND PATTERN PowerPAK MLP66-40L in millimeters

2.200 2.200 0.100 0.100 0.100 0.100

0.276 0.200 0.276 0.025 0.025

1 1

0.600

0.100

40 40

1.700

0.100

0.320

0.100

0.310

2.600

0.100

4.600 0.100 0.100

S14-2287-Rev. B, 08-Dec-14 15 Document Number: 62972

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

SiC789, SiC789A

www.vishay.com

Vishay Siliconix

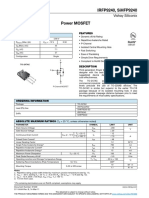

PACKAGE OUTLINE DRAWING MLP66-40L

2x

A 0.08 C K1

5 6 D 0.10 C A

A A1 K2 Pin #1 dent

Pin 1 dot 0.41 D2-1

by marking A2

31 40

2x

30 1

0.10 C B

E2-2

MLP66-40L

0.10 M C A B

(Nd-1)X e

(6 mm x 6 mm)

E2-1

ref.

E

E2-3

4

B 21 10

20 D2-3 D2-2 11

C

(Nd-1)X e

ref.

Top view Side view

Bottom view

MILLIMETERS INCHES

DIM.

MIN. NOM. MAX. MIN. NOM. MAX.

A 0.70 0.75 0.80 0.027 0.029 0.031

A1 0.00 - 0.05 0.000 - 0.002

A2 0.20 ref. 0.008 ref.

b 0.20 0.25 0.30 0.078 0.098 0.011

D 6.00 BSC 0.236 BSC

e 0.50 BSC 0.019 BSC

E 6.00 BSC 0.236 BSC

L 0.35 0.40 0.45 0.013 0.015 0.017

N 40 40

Nd 10 10

Ne 10 10

D2-1 1.45 1.50 1.55 0.057 0.059 0.061

D2-2 1.45 1.50 1.55 0.057 0.059 0.061

D2-3 2.35 2.40 2.45 0.095 0.094 0.096

E2-1 4.35 4.40 4.45 0.171 0.173 0.175

E2-2 1.95 2.00 2.05 0.076 0.078 0.080

E2-3 1.95 2.00 2.05 0.076 0.078 0.080

K1 0.73 BSC 0.028 BSC

K2 0.21 BSC 0.008 BSC

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon

Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and

reliability data, see www.vishay.com/ppg?62972.

S14-2287-Rev. B, 08-Dec-14 16 Document Number: 62972

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

Package Information

www.vishay.com

Vishay Siliconix

PowerPAK MLP66-40 Case Outline

2x K1

5 6 A 0.08 C

D 0.10 C A K2

Pin 1 dot A A1

0.41 D2-1

by marking A2

31 40

2x

30 1

0.10 C B

E2-2

MLP66-40

0.10 M C A B

(Nd-1)X e

(6 mm x 6 mm)

E2-1

ref.

E

E2-3

4

B 21 10

20 D2-3 D2-2 11

C

(Nd-1)X e

ref.

Top View Side View Bottom View

MILLIMETERS INCHES

DIM.

MIN. NOM. MAX. MIN. NOM. MAX.

A (8) 0.70 0.75 0.80 0.027 0.029 0.031

A1 0.00 - 0.05 0.000 - 0.002

A2 0.20 ref. 0.008 ref.

b (4) 0.20 0.25 0.30 0.078 0.098 0.011

D 6.00 BSC 0.236 BSC

e 0.50 BSC 0.019 BSC

E 6.00 BSC 0.236 BSC

L 0.35 0.40 0.45 0.013 0.015 0.017

N (3) 40 40

Nd (3) 10 10

Ne (3) 10 10

D2-1 1.45 1.50 1.55 0.057 0.059 0.061

D2-2 1.45 1.50 1.55 0.057 0.059 0.061

D2-3 2.35 2.40 2.45 0.095 0.094 0.096

E2-1 4.35 4.40 4.45 0.171 0.173 0.175

E2-2 1.95 2.00 2.05 0.076 0.078 0.080

E2-3 1.95 2.00 2.05 0.076 0.078 0.080

K1 0.73 BSC 0.028 BSC

K2 0.21 BSC 0.008 BSC

ECN: T14-0826-Rev. B, 12-Jan-15

DWG: 5986

Notes

1. Use millimeters as the primary measurement

2. Dimensioning and tolerances conform to ASME Y14.5M. - 1994

3. N is the number of terminals. Nd is the number of terminals in X-direction and Ne is the number of terminals in Y-direction

4. Dimension b applies to plated terminal and is measured between 0.20 mm and 0.25 mm from terminal tip

5. The pin #1 identifier must be existed on the top surface of the package by using indentation mark or other feature of package body

6. Exact shape and size of this feature is optional

7. Package warpage max. 0.08 mm

8. Applied only for terminals

Revision: 12-Jan-15 1 Document Number: 64846

For technical questions, contact: powerictechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

PAD Pattern

www.vishay.com

Vishay Siliconix

Recommended Land Pattern PowerPAK MLP66-40L

2.200 2.200 0.100 0.100 0.100 0.100

0.276 0.200 0.276 0.025 0.025

1 1

0.600

0.100

40 40

1.700

0.100

0.320

0.100

0.310

2.600

0.100

4.600 0.100 0.100

All Dimensions are in milimeters

Revision: 28-Feb-14 1 Document Number: 67964

For technical questions, contact: analogswitchtechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

Legal Disclaimer Notice

www.vishay.com

Vishay

Disclaimer

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE

RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively,

Vishay), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other

disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or

the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all

liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special,

consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular

purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishays knowledge of

typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding

statements about the suitability of products for a particular application. It is the customers responsibility to validate that a

particular product with the properties described in the product specification is suitable for use in a particular application.

Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over

time. All operating parameters, including typical parameters, must be validated for each customer application by the customers

technical experts. Product specifications do not expand or otherwise modify Vishays terms and conditions of purchase,

including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining

applications or for any other application in which the failure of the Vishay product could result in personal injury or death.

Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk.

Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for

such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document

or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

Revision: 13-Jun-16 1 Document Number: 91000

You might also like

- HUMSS - Q3 - Trends - Mod5 - Global Networks Part 1Document24 pagesHUMSS - Q3 - Trends - Mod5 - Global Networks Part 1Chernie Deroma Obsenares67% (6)

- Surge Arrester Function and Working PrinciplesDocument25 pagesSurge Arrester Function and Working PrinciplesMidhun Varghese100% (1)

- Schwing KVM 34X BrochureDocument4 pagesSchwing KVM 34X BrochureFlorinMacoveiNo ratings yet

- (2014) Colour and Technology in Historic Decorated Glazes and Glasses PDFDocument117 pages(2014) Colour and Technology in Historic Decorated Glazes and Glasses PDFtariq.toffa4760No ratings yet

- Sic 639Document17 pagesSic 639allradNo ratings yet

- Sic632, Sic632A: Vishay SiliconixDocument18 pagesSic632, Sic632A: Vishay SiliconixŁukasz SrogaNo ratings yet

- Sic 632Document19 pagesSic 632techgamebr85No ratings yet

- Sic 634Document17 pagesSic 634Tri Nguyen Real EstateNo ratings yet

- Sic 533Document16 pagesSic 533Tri Nguyen Real EstateNo ratings yet

- Sic 631Document19 pagesSic 631djavus123 djNo ratings yet

- Sic780, Sic780A: Vishay SiliconixDocument14 pagesSic780, Sic780A: Vishay SiliconixBoris ȚepeșNo ratings yet

- G22N60S Mosfet PDFDocument2 pagesG22N60S Mosfet PDFLucasNo ratings yet

- High-Voltage Power Mosfets: New 600-V Mosfets With Super Junction TechnologyDocument2 pagesHigh-Voltage Power Mosfets: New 600-V Mosfets With Super Junction TechnologyLucas YeniddinNo ratings yet

- Aoz5311nqi PDFDocument17 pagesAoz5311nqi PDFJohn InfinityNo ratings yet

- Irf 9640Document8 pagesIrf 9640Saeid AbraziNo ratings yet

- Irfp 360Document10 pagesIrfp 360movick.25No ratings yet

- Irfz 44Document9 pagesIrfz 44Harlan 123No ratings yet

- IRFR9024Document13 pagesIRFR9024RuslanNo ratings yet

- Spice Device Model Sis890Dn: Vishay SiliconixDocument4 pagesSpice Device Model Sis890Dn: Vishay Siliconixzinouu113113No ratings yet

- Irfz 48Document9 pagesIrfz 48Alexis GueraNo ratings yet

- NCP 81174Document18 pagesNCP 81174techgamebr85No ratings yet

- IRFPG50Document11 pagesIRFPG50RuslanNo ratings yet

- Datasheet NCP81109Document28 pagesDatasheet NCP81109zigmund zigmundNo ratings yet

- AOZ5312NQIDocument17 pagesAOZ5312NQISamuel tuñonNo ratings yet

- Irfp 250Document10 pagesIrfp 250bando janson purbaNo ratings yet

- SPICE Device Model SQD100N04-3m6 N-Channel 40 V (D-S) 175 °C MOSFETDocument4 pagesSPICE Device Model SQD100N04-3m6 N-Channel 40 V (D-S) 175 °C MOSFETAli KeyvanNo ratings yet

- Irfz24, Sihfz24: Vishay SiliconixDocument8 pagesIrfz24, Sihfz24: Vishay SiliconixAhmed Sherif CupoNo ratings yet

- Huf75344G3, Huf75344P3: N-Channel Ultrafet Power Mosfet FeaturesDocument10 pagesHuf75344G3, Huf75344P3: N-Channel Ultrafet Power Mosfet FeaturesChristina MullinsNo ratings yet

- Max6921-Max6931 VFD DriverDocument13 pagesMax6921-Max6931 VFD DriverVukica IvicNo ratings yet

- Irfp054, Sihfp054: Vishay SiliconixDocument10 pagesIrfp054, Sihfp054: Vishay SiliconixEmanuelLanNo ratings yet

- Vishay Siliconix: FeaturesDocument7 pagesVishay Siliconix: Featuresمركز القدسNo ratings yet

- IRFP460Document11 pagesIRFP460RuslanNo ratings yet

- Irfp9240, Sihfp9240: Vishay SiliconixDocument9 pagesIrfp9240, Sihfp9240: Vishay SiliconixALINUX SOUNDNo ratings yet

- Irfp9240, Sihfp9240: Vishay SiliconixDocument11 pagesIrfp9240, Sihfp9240: Vishay SiliconixLuverci GrosselNo ratings yet

- Irfp264, Sihfp264: Vishay SiliconixDocument9 pagesIrfp264, Sihfp264: Vishay SiliconixJunior Francisco QuijanoNo ratings yet

- IRFR9310 VishaySiliconixDocument11 pagesIRFR9310 VishaySiliconixDimas AprlioNo ratings yet

- DSASFU60008070Document21 pagesDSASFU60008070Orlando MendiolarNo ratings yet

- NCP81251 Single-Phase Voltage Regulator With SVID Interface For Computing ApplicationsDocument18 pagesNCP81251 Single-Phase Voltage Regulator With SVID Interface For Computing Applicationsankur rathiNo ratings yet

- AOZ5507QI Support DocumentsDocument17 pagesAOZ5507QI Support DocumentsNorberto CruzNo ratings yet

- IRFPE50Document11 pagesIRFPE50RuslanNo ratings yet

- MP24943Document13 pagesMP24943Agus OksNo ratings yet

- SPICE Device Model SQD50P06-15L: Vishay SiliconixDocument4 pagesSPICE Device Model SQD50P06-15L: Vishay SiliconixManikanta Sai KumarNo ratings yet

- Half-Bridge MOSFET Driver DocDocument7 pagesHalf-Bridge MOSFET Driver DocEric Lenin Marin MoncadaNo ratings yet

- SQ7414EN Product Bundle PDFDocument31 pagesSQ7414EN Product Bundle PDFHarris RaoNo ratings yet

- Irfpc60Lc, Sihfpc60Lc: Vishay SiliconixDocument9 pagesIrfpc60Lc, Sihfpc60Lc: Vishay Siliconixابو حميد ابو حميدNo ratings yet

- Irfpc60Lc, Sihfpc60Lc: Vishay SiliconixDocument11 pagesIrfpc60Lc, Sihfpc60Lc: Vishay Siliconixkotak kardusNo ratings yet

- TLV 7211 ADocument24 pagesTLV 7211 ADragan M.No ratings yet

- Irfp 9140Document11 pagesIrfp 9140loc nguyen dacNo ratings yet

- Synchronous Buck Nexfet Power Block: Features DescriptionDocument22 pagesSynchronous Buck Nexfet Power Block: Features DescriptionRawi MontillaNo ratings yet

- Irfp260, Sihfp260: Vishay SiliconixDocument11 pagesIrfp260, Sihfp260: Vishay Siliconixeki miftakhul firdausNo ratings yet

- Irfp260, Sihfp260: Vishay SiliconixDocument9 pagesIrfp260, Sihfp260: Vishay SiliconixSofyanNo ratings yet

- Green Mode Power Switch For Valley Switching Converter - Low EMI and High Efficiency FSQ0365, FSQ0265, FSQ0165, FSQ321Document22 pagesGreen Mode Power Switch For Valley Switching Converter - Low EMI and High Efficiency FSQ0365, FSQ0265, FSQ0165, FSQ321Mekkati MekkatiNo ratings yet

- Sllsec 4Document29 pagesSllsec 4solihinNo ratings yet

- LMR 23625Document43 pagesLMR 23625GaneshNo ratings yet

- Power MOSFET datasheet summaryDocument9 pagesPower MOSFET datasheet summaryAkhilesh Kumar MishraNo ratings yet

- Irfz44, Sihfz44: Vishay SiliconixDocument9 pagesIrfz44, Sihfz44: Vishay SiliconixherrysugarNo ratings yet

- FAN7314 LCD Backlight Inverter Drive IC: Features DescriptionDocument3 pagesFAN7314 LCD Backlight Inverter Drive IC: Features DescriptionJúnior Da Silva SantanaNo ratings yet

- Irf9540, Sihf9540: Vishay SiliconixDocument9 pagesIrf9540, Sihf9540: Vishay SiliconixPhamVanGiangNo ratings yet

- NCP 5392Document32 pagesNCP 5392techgamebr85No ratings yet

- Irf540, Sihf540: Vishay SiliconixDocument9 pagesIrf540, Sihf540: Vishay SiliconixJose Carlos Gonzales BecerraNo ratings yet

- Acti9 IK60N Katalog Indonesia PDFDocument3 pagesActi9 IK60N Katalog Indonesia PDFGeorge CalinNo ratings yet

- Irfp 9240Document11 pagesIrfp 9240NaderNo ratings yet

- Correlation Duality Relations For The (N,, ND) ModelDocument6 pagesCorrelation Duality Relations For The (N,, ND) ModelFlorinMacoveiNo ratings yet

- Lake George Health Regulations SummaryDocument34 pagesLake George Health Regulations SummaryFlorinMacoveiNo ratings yet

- Statistical Potential of Atomic Ions: Department of Physics, National Tsing Hua University, Hsinchu, Taiwan 300, R.O.CDocument9 pagesStatistical Potential of Atomic Ions: Department of Physics, National Tsing Hua University, Hsinchu, Taiwan 300, R.O.CFlorinMacoveiNo ratings yet

- Quantum Mechanics in Operator SpaceDocument7 pagesQuantum Mechanics in Operator SpaceFlorinMacoveiNo ratings yet

- Dr. Ta-You Wu's Contributions to Academia SinicaDocument2 pagesDr. Ta-You Wu's Contributions to Academia SinicaFlorinMacoveiNo ratings yet

- Elel Norcal MDFDocument6 pagesElel Norcal MDFFlorinMacoveiNo ratings yet

- Professor T. Y. Wu and Physics: Chinese Journal of Physics VOL. 35, NO. 6-11 December 1997Document5 pagesProfessor T. Y. Wu and Physics: Chinese Journal of Physics VOL. 35, NO. 6-11 December 1997FlorinMacoveiNo ratings yet

- 2014 15 Youth CalendarDocument2 pages2014 15 Youth CalendarFlorinMacoveiNo ratings yet

- Data SheetDocument11 pagesData SheetFlorinMacoveiNo ratings yet

- Po 4567Document7 pagesPo 4567FlorinMacoveiNo ratings yet

- HankookTire FY2013 Consolidated FinalDocument69 pagesHankookTire FY2013 Consolidated FinalFlorinMacoveiNo ratings yet

- Disclosure To Promote The Right To Information: IS 6987 (1973) : Steel Precision Polygons (PGD 25: Engineering Metrology)Document8 pagesDisclosure To Promote The Right To Information: IS 6987 (1973) : Steel Precision Polygons (PGD 25: Engineering Metrology)FlorinMacoveiNo ratings yet

- Naval Aircrewmen - Operator Career RoadmapDocument96 pagesNaval Aircrewmen - Operator Career RoadmapFlorinMacoveiNo ratings yet

- 908Document32 pages908FlorinMacoveiNo ratings yet

- 1998 - 37 - EC Machinery Safety enDocument46 pages1998 - 37 - EC Machinery Safety enharakosanNo ratings yet

- An Introduction To R: W. N. Venables, D. M. Smith and The R Core TeamDocument105 pagesAn Introduction To R: W. N. Venables, D. M. Smith and The R Core TeamMahadiNo ratings yet

- U.S. Robotics Modems: User's Guide: Published September 2000Document100 pagesU.S. Robotics Modems: User's Guide: Published September 2000FlorinMacoveiNo ratings yet

- Ceng3181-Transport Engineering: Haramaya Institute of Technology Department of Civil EngineeringDocument31 pagesCeng3181-Transport Engineering: Haramaya Institute of Technology Department of Civil EngineeringMuaz HararNo ratings yet

- ALL-Q (Coenzyme Q10) Plus - PDSDocument3 pagesALL-Q (Coenzyme Q10) Plus - PDSMarlon2370No ratings yet

- BackIntelligence Herniated Disc ExercisesDocument9 pagesBackIntelligence Herniated Disc Exercisesswaminathan1No ratings yet

- CEEAMA-TECHNICAL-PAPER-2018 by Sunil VoraDocument6 pagesCEEAMA-TECHNICAL-PAPER-2018 by Sunil VorasunilgvoraNo ratings yet

- Chapte4 ZamznDocument24 pagesChapte4 ZamznAHMED DARAJNo ratings yet

- Workshop Practices Lab Course DescriptorDocument8 pagesWorkshop Practices Lab Course DescriptorWossenu MekonnenNo ratings yet

- trs5 Key Cho Cac BanDocument35 pagestrs5 Key Cho Cac BanNguyệt NgôNo ratings yet

- Business Operations Group AssignmentDocument7 pagesBusiness Operations Group Assignmentankit gangeleNo ratings yet

- Cinnamon Streusel Muffin Recipe (Coffee Cake) - DDocument3 pagesCinnamon Streusel Muffin Recipe (Coffee Cake) - DBryce MitchellNo ratings yet

- Meter Moving CoilDocument4 pagesMeter Moving Coilabecdf100% (1)

- Manual Tud300Document70 pagesManual Tud300DionicioCasanovaNo ratings yet

- BIOpolitics PDFDocument3 pagesBIOpolitics PDFalpar7377No ratings yet

- Kisii University course explores environmental biotech, bioprocessingDocument4 pagesKisii University course explores environmental biotech, bioprocessingRyan ReighnsNo ratings yet

- C70Document3 pagesC70Jorge Luis Arevalo LopezNo ratings yet

- 842e In001 - en PDocument4 pages842e In001 - en PNilson Eduardo TorresNo ratings yet

- LC Passive Wireless Sensors Toward A Wireless Sensing Platform: Status, Prospects, and ChallengesDocument20 pagesLC Passive Wireless Sensors Toward A Wireless Sensing Platform: Status, Prospects, and ChallengesCristian David Merchan VegaNo ratings yet

- 06072G Chapter Sample PDFDocument11 pages06072G Chapter Sample PDFAnonymous 1hOgJqwZuzNo ratings yet

- Small ScienceDocument368 pagesSmall Sciencereach27No ratings yet

- Cash Valve Product OverviewDocument16 pagesCash Valve Product OverviewestebanNo ratings yet

- ForumIAS CSAT Test 10Document18 pagesForumIAS CSAT Test 10anilNo ratings yet

- Artists Budget TemplateDocument9 pagesArtists Budget TemplateMaia CelloNo ratings yet

- Micro Gear WheelDocument4 pagesMicro Gear WheelMuhammad Alep JamianNo ratings yet

- Solving Motion ProblemsDocument5 pagesSolving Motion ProblemsAkshat Kumar AgarwalNo ratings yet

- Noon Fees StructureDocument8 pagesNoon Fees StructureNithin SreekumarNo ratings yet

- Modeling Relationships in Scatter PlotsDocument45 pagesModeling Relationships in Scatter PlotsSiddarth Kalyan100% (1)

- Chapter 4Document9 pagesChapter 4Aung KhantNo ratings yet