Professional Documents

Culture Documents

Diseño Digital Con VHDL

Uploaded by

jose morenoCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Diseño Digital Con VHDL

Uploaded by

jose morenoCopyright:

Available Formats

TECNOLGICO NACIONAL DE MXICO

Secretara Acadmica, de Investigacin e Innovacin

Direccin de Docencia e Innovacin Educativa

1. Datos Generales de la asignatura

Nombre de la asignatura: Diseo Digital con VHDL

Clave de la asignatura: ETF-1015

SATCA1: 3-2-5

Carrera: Ingeniera Electrnica

2. Presentacin

Caracterizacin de la asignatura

Aportacin de la asignatura al perfil de egreso:

Simular e implementar modelos de sistemas electrnicos lgicos secuenciales que permitan

comprobar su comportamiento empleando lenguajes de descripcin de hardware.

Aplicar los conocimientos de dispositivos lgicos programables, para el anlisis, adaptacin,

operacin, mantenimiento y diseo de los sistemas digitales que conforman la base de los

microntroladores.

Analizar, adaptar, operar y disear los diferentes dispositivos de interfaz relacionados con sistemas

digitales.

Comunicarse con efectividad en forma oral y escrita en el mbito profesional tanto en su idioma

como en un idioma extranjero.

Importancia de la asignatura:

Esta asignatura es la base para la comprensin de la operacin de microprocesadores y

microcontroladores. Permite que el alumno pueda disear mediante el lenguaje de descripcin de

hardware cualquier circuito digital dentro de un circuito con alta escala de integracin.

Establece el vnculo entre los circuitos electrnicos digitales y los diferentes dispositivos de interfaz.

Descripcin general del contenido de la materia:

La materia presenta los fundamentos de diseo de los sistemas digitales, secuenciales empleando el

lenguaje de descripcin de hardware, permitiendo la implementacin de mquinas de estados.

Establece las bases de los componentes bsicos de un microprocesador (memoria y ALU), as como

los diversos dispositivos de interfaz con los que se relacionan.

Relacin con otras asignaturas:

Esta materia es la base de materias como Microntroladores, Controladores Lgicos Programables,

Control Digital y materias de especialidad, en los temas de diseo e implementacin de circuitos

digitales empleando lenguajes de descripcin de hardware y dispositivos lgicos programables,

desarrollando las competencias especficas de anlisis, diseo e implementacin de circuitos digitales

con VHDL.

Intencin didctica

El contenido de la materia de Diseo Digital con VHDL se organiza en cuatro temas.

En el primer tema se comienza con la programacin de circuitos digitales en VHDL. Considerando

que el alumno ya tiene las nociones del uso del mismo, en este tema se debe lograr el diseo de circuitos

1

Sistema de Asignacin y Transferencia de Crditos Acadmicos

TecNM mayo 2016 Pgina | 1

TECNOLGICO NACIONAL DE MXICO

Secretara Acadmica, de Investigacin e Innovacin

Direccin de Docencia e Innovacin Educativa

secuenciales sncronos utilizando PLDs y FPGAs, finalizando con una aplicacin para poner en

prctica los recursos aprendidos basados en VHDL.

En el tema dos, se realizan los procesos para el diseo y simulacin de mquinas de estados finitos

sncronas. Se desarrollan e implementan sistemas secuenciales en VHDL para que el estudiante

compruebe la ventaja del desarrollo de sistemas con VHDL.

El tema tres aborda el estudio de memorias semiconductoras e inicia la unidad retomando los

fundamentos de los sistemas numricos en el sistema hexadecimal para una mejor comprensin del

direccionamiento de la memoria; posteriormente se estudian los conceptos generales, funcionamiento,

programacin y aplicacin de memorias semiconductoras como una preparacin para el estudio de la

arquitectura de un procesador.

En el tema cuatro, se estudian un procesador con arquitectura Harvard y Arquitectura Von Neumann.

Se desarrollan por separado los componentes de un Microcontrolador bsico implementando prcticas

independientes para finalmente integrarlos en un sistema Microcontrolador.

Se sugiere una actividad integradora, en cada tema, que permita aplicar los conceptos estudiados. Esto

permite dar un cierre a la materia mostrndola como til por s misma en el desempeo profesional,

independientemente de la utilidad que representa en el tratamiento de temas en materias posteriores.

El enfoque sugerido para la materia propicia que las actividades en el aula y en el laboratorio,

desarrollen en el alumno las habilidades para la investigacin y experimentacin, adems del trabajo

en equipo y las capacidades de anlisis y sntesis en el diseo e implementacin de circuitos digitales.

Se sugieren sobre todo que las actividades que se realicen en el curso de esta materia tengan un

aprendizaje significativo y efectivo en el alumno. Algunas de las actividades sugeridas pueden hacerse

como actividad extra clase y comenzar el tratamiento en clase a partir de la discusin de los resultados

de las observaciones derivadas de las prcticas de laboratorio. Se busca que partir de experiencias de

la vida diaria el estudiante se acostumbre a reconocer los fenmenos fsicos y electrnicos.

Es necesario que el profesor ponga atencin y cuidado en los siguientes aspectos para el desarrollo de

las actividades de aprendizaje de esta asignatura. Las competencias genricas que son fortalecidas en

esta asignatura comprenden algunas interpersonales, instrumentales y sistmicas a travs de

investigacin, aplicacin de los conocimientos en la prctica, capacidad de aprender y actualizarse de

forma permanente, su compromiso con la calidad, trabajo en equipo, elaboracin de prcticas y

redaccin de reportes respectivos, ensayos, exposiciones, anlisis de casos, organizacin y

planificacin del tiempo, entre otros.

El profesor debe:

Conocer la disciplina que est bajo su responsabilidad, su origen y desarrollo histrico para

considerar este conocimiento al abordar los temas.

Desarrollar la capacidad para coordinar y trabajar en equipo; orientar el trabajo del estudiante

y potenciar en l la autonoma, el trabajo cooperativo y la toma de decisiones.

Mostrar flexibilidad en el seguimiento del proceso formativo y propiciar la interaccin entre

los estudiantes.

Tomar en cuenta el conocimiento de los estudiantes como punto de partida y como obstculo

para la construccin de nuevos conocimientos.

Enfatizar en trabajo en el laboratorio para descubrir las habilidades de los alumnos.

Detectar debilidades y fortalezas de los alumnos al inicio del curso.

TecNM mayo 2016 Pgina | 2

TECNOLGICO NACIONAL DE MXICO

Secretara Acadmica, de Investigacin e Innovacin

Direccin de Docencia e Innovacin Educativa

3. Participantes en el diseo y seguimiento curricular del programa

Lugar y fecha de elaboracin

Participantes Evento

o revisin

Representantes de los Institutos

Tecnolgicos de:

Aguascalientes, Apizaco,

Cajeme, Celaya, Chapala,

Chihuahua, Ciudad Guzmn, Reunin Nacional de Diseo e

Ciudad Jurez, Cosamaloapan, Innovacin Curricular para el

Cuautla, Culiacn, Durango, Desarrollo y Formacin de

Instituto Tecnolgico Superior Ecatepec, Ensenada, Hermosillo, Competencias Profesionales de

de Irapuato, del 24 al 28 de Irapuato, La Laguna, Lzaro las Carreras de Ingeniera

agosto de 2009. Crdenas, Lerdo, Lerma, Los Elctrica, Ingeniera

Mochis, Matamoros, Mrida, Electromecnica, Ingeniera

Mexicali, Minatitln, Nuevo Electrnica e Ingeniera

Laredo, Orizaba, Piedras Negras, Mecatrnica.

Reynosa, Salina Cruz, Saltillo,

Sur De Guanajuato, Tantoyuca,

Tijuana, Toluca, Tuxtepec,

Veracruz y Xalapa.

Representantes de los Institutos

Tecnolgicos de:

Aguascalientes, Apizaco,

Cajeme, Celaya, Chapala,

Chihuahua, Ciudad Guzmn,

Reunin Nacional de

Ciudad Jurez, Cosamaloapan,

Consolidacin de los

Cuautla, Durango, Ecatepec,

Programas en Competencias

Instituto Tecnolgico de Ensenada, Hermosillo, Irapuato,

Profesionales de las Carreras de

Mexicali, del 25 al 29 de enero La Laguna, Lzaro Crdenas,

Ingeniera Elctrica, Ingeniera

del 2010. Lerdo, Lerma, Los Mochis,

Electromecnica, Ingeniera

Matamoros, Mrida, Mexicali,

Electrnica e Ingeniera

Minatitln, Nuevo Laredo,

Mecatrnica.

Orizaba, Piedras Negras,

Reynosa, Salina Cruz, Saltillo,

Sur De Guanajuato, Tantoyuca,

Toluca, Tuxtepec, Veracruz y

Xalapa.

Reunin Nacional de

Seguimiento Curricular de los

Representantes de los Institutos

Programas en Competencias

Tecnolgicos de:

Instituto Tecnolgico de la Profesionales de las Carreras de

Orizaba, Quertaro, Celaya,

Laguna, del 26 al 29 de Ingeniera Elctrica, Ingeniera

Aguascalientes, Alvarado,

noviembre de 2012. Electromecnica, Ingeniera

Cuautitln Izcalli, La Laguna y

Electrnica, Ingeniera

Lerdo.

Mecnica e Ingeniera

Mecatrnica.

TecNM mayo 2016 Pgina | 3

TECNOLGICO NACIONAL DE MXICO

Secretara Acadmica, de Investigacin e Innovacin

Direccin de Docencia e Innovacin Educativa

Representantes de los Institutos Reunin de Seguimiento

Instituto Tecnolgico de Tecnolgicos de: Curricular de los Programas

Toluca, del 10 al 13 de febrero Aguascalientes, Boca del Ro, Educativos de Ingenieras,

de 2014. Celaya, Mrida, Orizaba, Puerto Licenciaturas y Asignaturas

Vallarta y Veracruz. Comunes del SNIT.

Representantes de los Institutos

Tecnolgicos de:

Aguascalientes, Apizaco, Boca

del Ro, Celaya, Cerro Azul, Cd.

Jurez, Cd. Madero, Chihuahua,

Coacalco, Coatzacoalcos,

Durango, Ecatepec, La Laguna, Reunin de trabajo para la

Tecnolgico Nacional de Lerdo, Matamoros, Mrida, actualizacin de los planes de

Mxico, del 25 al 26 de agosto Mexicali, Motl, Nuevo Laredo, estudio del sector energtico,

de 2014. Orizaba, Pachuca, Poza Rica, con la participacin de

Progreso, Reynosa, Saltillo, PEMEX.

Santiago Papasquiaro,

Tantoyuca, Tlalnepantla, Toluca,

Veracruz, Villahermosa,

Zacatecas y Zacatepec.

Representantes de Petrleos

Mexicanos (PEMEX).

4. Competencia(s) a desarrollar

Competencia(s) especfica(s) de la asignatura

Desarrolla y simula estructuras avanzadas de un programa en VHDL de circuitos lgicos secuenciales

sncronos para la programacin e implementacin de FPGAs o CPLDs en aplicaciones reales.

Conoce y desarrolla los componentes que conforman las arquitecturas bsicas de un microprocesador.

5. Competencias previas

Realiza demostraciones de teoremas y postulados del algebra de Boole.

Realiza reducciones de funciones lgicas.

Identifica y compara las familias de las compuertas lgicas.

Busca y selecciona informacin acerca de FPGAs o CPLDs.

Disea y construye circuitos combinacionales usando dispositivos SSI, MSI y FPGAs o CPLDs.

Analiza y disea circuitos secuenciales utilizando Flip- Flops.

Analiza y disea circuitos secuenciales sncronos utilizando Flip- Flops.

Analiza y disea circuitos secuenciales sncronos con FPGAs o CPLDs.

TecNM mayo 2016 Pgina | 4

TECNOLGICO NACIONAL DE MXICO

Secretara Acadmica, de Investigacin e Innovacin

Direccin de Docencia e Innovacin Educativa

6. Temario

No. Temas Subtemas

1 Programacin VHDL 1.1. Elementos del lenguaje VHDL.

1.1.1. Elementos sintcticos del VHDL.

1.1.2. Operadores y expresiones en VHDL.

1.2. Declaraciones de objetos.

1.2.1. Declaracin de seales

1.2.2. Declaracin de ficheros.

1.3. Declaraciones concurrentes.

1.3.1. Declaracin de arquitectura de flujo

de datos.

1.3.2. Ejemplos de descripcin flujo de

datos.

1.4. Ejemplos de declaraciones secuenciales.

1.4.1. Ejemplos de diagramas de mquinas

de estado.

1.5. Funciones y subprogramas.

1.5.1. Declaracin de procedimientos y

funciones.

1.5.2. Subprogramas.

1.5.3. Paquetes.

1.5.4. Bibliotecas

1.6. Programacin de FPGAs CPLDS en

diferentes aplicaciones.

2 Mquinas de Estados Finitos 2.1. Modelo de Mealy y Modelo de Moore.

2.2. Representacin de los modelos Mealy y

Moore en diagramas de estado y diagrama

ASM.

2.3. Diseo de mquinas de estados finitos tipo

Mealy y tipo Moore utilizando VHDL.

2.3.1. Obtencin de las tablas de estado.

2.3.2. Obtencin de las ecuaciones de

estado.

2.3.3. Programacin de archivo .VHD.

2.3.4. Simulacin del archivo .VHD.

2.3.5. Obtencin del archivo de

programacin.

2.3.6. Programacin de FPGAs CPLDs

3 Memorias 3.1. Conceptos de memorias.

3.1.1. Terminologa de memorias.

3.1.2. Operacin general de memorias.

3.1.3. Tipos de memorias.

3.1.4. Aplicaciones de memorias en la

lgica combinacional y secuencial.

TecNM mayo 2016 Pgina | 5

TECNOLGICO NACIONAL DE MXICO

Secretara Acadmica, de Investigacin e Innovacin

Direccin de Docencia e Innovacin Educativa

4 Arquitectura de Procesadores 4.1. Arquitectura Von Neumann.

4.1.1. Arquitectura de los

Microprocesadores.

4.2. Arquitectura Harvard.

4.2.1. Arquitectura de los Micro-

controladores.

4.3. Estructura y funcionamiento de una ALU.

4.3.1. Registro de estado.

4.3.2. Operaciones con datos de memoria y

registros.

4.3.3. Operaciones con punto flotante y fijo.

4.4. Descripcin de una ALU con VHDL.

5 Mdulos de Interfaz en VHDL. 5.1. Comunicacin serial con UART.

5.1.1. Introduccin.

5.1.2. Diseo de un UART en VHDL.

5.2. Comunicacin serial por I2C.

5.2.1. Introduccin a I2C.

5.2.2. Diseo de un mdulo para

comunicacin I2C.

5.2.3. Comunicacin de un FPGA con otro

dispositivo por medio de I2C.

5.3. Comunicacin por Ethernet utilizando IP

cores.

5.3.1. Introduccin a Ethernet.

5.3.2. Utilizacin de IP cores para

comunicar dos FPGAs por Ethernet.

5.4. Comunicacin por CAN utilizando IP cores.

5.4.1. Introduccin al Bus CAN.

5.4.2. Utilizacin de IP cores para

comunicar dos FPGAs por bus CAN.

7. Actividades de aprendizaje de los temas

1. Programacin VHDL

Competencias Actividades de aprendizaje

Especifica(s): Investigar, reflexionar y entender el uso de

Desarrolla y simula estructuras avanzadas de un software para el desarrollo de programas de

programa en VHDL de circuitos secuenciales descripcin de circuitos secuenciales digitales

sncronos para la programacin de CPLDs o en VHDL.

FPGAs. Realizar prcticas en computadora para

Genricas: edicin, compilacin de los programas

Capacidad de abstraccin, anlisis y sntesis. desarrollados en VHDL.

Capacidad de aplicar los conocimientos en Discutir los fundamentos del lenguaje de

la prctica. VHDL, para el desarrollo circuitos digitales

Capacidad para organizar y planificar el secuenciales.

tiempo.

TecNM mayo 2016 Pgina | 6

TECNOLGICO NACIONAL DE MXICO

Secretara Acadmica, de Investigacin e Innovacin

Direccin de Docencia e Innovacin Educativa

Capacidad de comunicacin oral y escrita. Utilizar un software de aplicacin en VHDL

Capacidad de aprender y actualizarse para la simulacin y programacin de circuitos

permanentemente. secuenciales sncronos.

Habilidad para trabajar en forma autnoma.

Capacidad de trabajo en equipo.

Compromiso con la calidad.

2. Mquinas de Estados Finitos

Competencias Actividades de aprendizaje

Especifica(s): Reflexionar y discutir las caractersticas y el

Desarrolla, simula e implementa estructuras funcionamiento de las mquinas de estados

avanzadas de un programa en VHDL para finitos.

comprender el funcionamiento de las mquinas Utilizar un software de aplicacin en VHDL

de estado finito programando CPLDs o para la simulacin y programacin de mquinas

FPGAs. de estados finitos.

Genricas: Realizar prcticas en computadora para edicin

Capacidad de abstraccin, anlisis y sntesis. y compilacin de los programas desarrollados

Capacidad de aplicar los conocimientos en en VHDL.

la prctica.

Capacidad para organizar y planificar el

tiempo.

Capacidad de comunicacin oral y escrita.

Capacidad de aprender y actualizarse

permanentemente.

Habilidad para trabajar en forma autnoma.

Capacidad de trabajo en equipo.

Compromiso con la calidad.

3. Memorias

Competencias Actividades de aprendizaje

Especifica(s): Investigar la clasificacin de memorias

Conoce los conceptos bsicos del semiconductoras.

funcionamiento de memorias para relacionarlos Realizar una investigacin documental para la

con los diferentes sistemas electrnicos. operacin de cada una de las diferentes

Genricas: memorias semiconductoras.

Capacidad de abstraccin, anlisis y sntesis. Realizar prcticas de implementacin de

Capacidad de aplicar los conocimientos en registros empleando VHDL para ejemplificar el

la prctica. funcionamiento de memorias.

Habilidades en el uso de las tecnologas de Realizar una bsqueda de las diferentes

la informacin y de la comunicacin. aplicaciones de las memorias en sistemas

Capacidad de investigacin. electrnicos.

Capacidad para organizar y planificar el

tiempo.

Capacidad de comunicacin oral y escrita.

Capacidad de aprender y actualizarse

permanentemente.

Habilidad para trabajar en forma autnoma.

TecNM mayo 2016 Pgina | 7

TECNOLGICO NACIONAL DE MXICO

Secretara Acadmica, de Investigacin e Innovacin

Direccin de Docencia e Innovacin Educativa

Capacidad de trabajo en equipo.

Compromiso con la calidad.

5. Arquitectura de Procesadores

Competencias Actividades de aprendizaje

Especifica(s): Explicar la estructura, funcionamiento y tipos

Comprende el funcionamiento de la ALU y de operaciones que una ALU puede realizar.

resuelve operaciones con punto fijo y punto Realizar una prctica en VHDL para

flotante mediante la implementacin en CPLDs ejemplificar el funcionamiento de la ALU.

FPGAs para comprender los elementos que Discutir la diferencia entre memoria de

componen un procesador utilizando VHDL. programa y memoria de datos.

Genricas: Investigar la diferencia entre las arquitecturas

Capacidad de abstraccin, anlisis y sntesis. Von Neumann y Harvard

Capacidad de aplicar los conocimientos en Realizar una presentacin en computadora de

la prctica. los elementos que conforman un procesador.

Capacidad para organizar y planificar el Utilizar un software de aplicacin en VHDL

tiempo. para la simulacin y programacin de una

Capacidad de comunicacin oral y escrita. unidad de control.

Capacidad de aprender y actualizarse Desarrollar un proyecto que ejemplifique el

permanentemente. funcionamiento de un procesador.

Habilidad para trabajar en forma autnoma.

Capacidad de trabajo en equipo.

Compromiso con la calidad.

6. Mdulos de Interfaz en VHDL.

Competencias Actividades de aprendizaje

Especifica(s): Explicar el principio de operacin de las

Analiza, simula, disea e implementa interfaces interfaces UART, I2C, CAN y Ethernet .

de comunicacin (UART, I2C, CAN, Ethernet) Discutir la diferencia entre cada una de las

mediante estructuras avanzadas de interfaces.

programacin en VHDL programando CPLDs Utilizar un software de aplicacin en VHDL

o FPGAs para realizar aplicaciones de para la simulacin de interfaz UART, I2C, CAN

adquisicin de datos. y Ethernet.

Genricas: Realizar prcticas en VHDL programando

Capacidad de abstraccin, anlisis y sntesis. CPLDs FPGA sobre interfaz UART, I2C,

Capacidad de aplicar los conocimientos en CAN y Ethernet.

la prctica.

Capacidad para organizar y planificar el

tiempo.

Capacidad de comunicacin oral y escrita.

Capacidad de aprender y actualizarse

permanentemente.

Habilidad para trabajar en forma autnoma.

Capacidad de trabajo en equipo.

Compromiso con la calidad.

TecNM mayo 2016 Pgina | 8

TECNOLGICO NACIONAL DE MXICO

Secretara Acadmica, de Investigacin e Innovacin

Direccin de Docencia e Innovacin Educativa

8. Prctica(s)

Diseo y simulacin de circuitos secuenciales sncronos con CPLDs FPGAs.

Diseo y simulacin de circuitos secuenciales sncronos mediante mquinas de estados con

CPLDs FPGAs.

Operaciones con datos de memoria y registros diseados en VHDL e implementados con CPLDs

o FPGAs.

Diseo y desarrollo de un circuito secuencial de aplicacin real basado en VHDL.

Desarrollo de una ALU con funciones bsicas mediante VHDL e implementarla en un FPGA o

CPLD.

Desarrollo un sistema de comunicacin entre dos FPGAs, mediante alguno de los protocolos de

comunicacin estudiados.

9. Proyecto de asignatura

El objetivo del proyecto que plante el docente que imparta esta asignatura, es demostrar el desarrollo

y alcance de la(s) competencia(s) de la asignatura, considerando las siguientes fases:

Fundamentacin: marco referencial (terico, conceptual, contextual, legal) en el cual se

fundamenta el proyecto de acuerdo con un diagnstico realizado, mismo que permite a los

estudiantes lograr la comprensin de la realidad o situacin objeto de estudio para definir un

proceso de intervencin o hacer el diseo de un modelo.

Planeacin: con base en el diagnstico en esta fase se realiza el diseo del proyecto por parte de

los estudiantes con asesora del docente; implica planificar un proceso: de intervencin

empresarial, social o comunitario, el diseo de un modelo, entre otros, segn el tipo de proyecto,

las actividades a realizar los recursos requeridos y el cronograma de trabajo.

Ejecucin: consiste en el desarrollo de la planeacin del proyecto realizada por parte de los

estudiantes con asesora del docente, es decir en la intervencin (social, empresarial), o

construccin del modelo propuesto segn el tipo de proyecto, es la fase de mayor duracin que

implica el desempeo de las competencias genricas y especificas a desarrollar.

Evaluacin: es la fase final que aplica un juicio de valor en el contexto laboral-profesin, social e

investigativo, sta se debe realizar a travs del reconocimiento de logros y aspectos a mejorar se

estar promoviendo el concepto de evaluacin para la mejora continua, la metacognicin, el

desarrollo del pensamiento crtico y reflexivo en los estudiantes.

10. Evaluacin por competencias

Instrumentos y herramientas sugeridas para evaluar las actividades de aprendizaje:

Exmenes escritos u orales para comprobar el manejo de aspectos tericos y de programacin.

Examen prctico (En el laboratorio y/o frente a la computadora).

Desarrollo de mapas conceptuales de actividades realizadas en clase.

Desarrollo de prcticas que incluyan simulacin e implementacin de circuitos digitales.

Desarrollo de actividades extra clase.

Participacin y exposicin en clase.

Desarrollo de un proyecto final del curso.

Cumplimiento de las actividades asignadas.

Realizacin de actividades de investigacin documental.

Participacin en eventos como: Innovacin tecnolgica, otros.

TecNM mayo 2016 Pgina | 9

TECNOLGICO NACIONAL DE MXICO

Secretara Acadmica, de Investigacin e Innovacin

Direccin de Docencia e Innovacin Educativa

11. Fuentes de informacin

1. Morris Mano M. (2005) Fundamentos de Diseo Lgico y de Computadoras, Tercera edicin,

Pearson, Mxico.

2. Tocci R. J. (2007), Sistemas digitales Principios y Aplicaciones, 10 edicin, Pearson, Mxico.

3. Marcovitz, A. B. (2005). Diseo Digital, Segunda Edicin. Mc Graw Hill.

4. Wakerly, J. F. (2002), Diseo Digital Principios y Aplicaciones, segunda edicin, Pearson,

Mxico.

5. Maxinez, D. G. (2002), VHDL: El Arte de Programar Sistemas Digitales, CECSA.

6. Pardo. F. Boluda, J. A. (2003), VHDL Lenguaje para Sntesis y modelado de Circuitos. Segunda

Edicin. RA-MA, Mxico.

7. Brown S. y Vranesic Z.G. (2006), Fundamentos de lgica digital con diseo VHDL, Segunda

Edicin, Mc Graw Hill, Mxico.

8. Ciletti, M. D. Advanced Digital Design with the Verilog HDL, Segunda edicin, Ed. Prentice Hall.

9. Ashenden, P. J. (2008), The Designer's Guide to VHDL, Volume 3, Third Edition, Morgan

Kaufmann Publishers, Australia.

10. Chu P. P. (2008), FPGA Prototyping by VHDL Examples: Xilinx Spartan-3, Primera Edicin,

Wiley & Sons.

11. Douglas P. L, (2002), VHDL Programming by example, Cuarta Edicin, McGraw Hill, USA.

TecNM mayo 2016 Pgina | 10

You might also like

- Cuentos de La Calle Broca Pierre GripariDocument141 pagesCuentos de La Calle Broca Pierre Griparikaren93% (14)

- Mapa Conceptual MercadotecniaDocument1 pageMapa Conceptual MercadotecniaAide Arvizu Meza79% (52)

- Curso de programación orientada a objetos en C# .NET: Ejemplos con aplicacines visualez y de consolaFrom EverandCurso de programación orientada a objetos en C# .NET: Ejemplos con aplicacines visualez y de consolaNo ratings yet

- Fundamentos de Programación: Diagramas de flujo, Diagramas N-S, Pseudocódigo y JavaFrom EverandFundamentos de Programación: Diagramas de flujo, Diagramas N-S, Pseudocódigo y JavaNo ratings yet

- Evaluación del aprendizaje en espacios virtuales-TICFrom EverandEvaluación del aprendizaje en espacios virtuales-TICRating: 5 out of 5 stars5/5 (2)

- Diseño DigitalDocument10 pagesDiseño DigitaladrianNo ratings yet

- Circuitos Electricos II PDFDocument12 pagesCircuitos Electricos II PDFJonas Isaac Méndez MendozaNo ratings yet

- Taller de Sistemas Operativos Temario PDFDocument11 pagesTaller de Sistemas Operativos Temario PDFKarlaRodriguezNo ratings yet

- Circuitos Electricos I PDFDocument9 pagesCircuitos Electricos I PDFMariana HernandezNo ratings yet

- Gestión de Proyectos de SoftwareDocument10 pagesGestión de Proyectos de SoftwareCESAR URIEL MOTA SALVADORNo ratings yet

- Carpeta de Evidencias PDFDocument68 pagesCarpeta de Evidencias PDFJuankiOrzuNo ratings yet

- Administración de Servidores.Document11 pagesAdministración de Servidores.ozdarkNo ratings yet

- Programacion VisualDocument9 pagesProgramacion Visualjesus manuelNo ratings yet

- Principios Eléctricos y Aplicaciones Digitales PDFDocument10 pagesPrincipios Eléctricos y Aplicaciones Digitales PDFGOOD TIMENo ratings yet

- MAD-2203 SimulacionDocument27 pagesMAD-2203 SimulacionAlfredo GracidaNo ratings yet

- LenguajesAutomatasI PDFDocument12 pagesLenguajesAutomatasI PDFFrancisco Javier Mayo JaimesNo ratings yet

- Tecnologías e Interfaces de Computadoras PDFDocument10 pagesTecnologías e Interfaces de Computadoras PDFServand Gunzand RosesNo ratings yet

- Diseño Mecanico IDocument10 pagesDiseño Mecanico IErickramirezNo ratings yet

- Bases de Datos DistribuidasDocument7 pagesBases de Datos DistribuidasElsa Irene Herrera SantiagoNo ratings yet

- Principios Eléctricos y Aplicaciones Digitales PDFDocument10 pagesPrincipios Eléctricos y Aplicaciones Digitales PDFAntonio CadenaNo ratings yet

- Sistemas Programables PDFDocument11 pagesSistemas Programables PDFAntonio CadenaNo ratings yet

- Temario de Opams PDFDocument9 pagesTemario de Opams PDFFlavio Cesar Martinez HernandezNo ratings yet

- Introducción A Las Telecomunicaciones PDFDocument12 pagesIntroducción A Las Telecomunicaciones PDFOscarNo ratings yet

- Ecuaciones Diferenciales PDFDocument12 pagesEcuaciones Diferenciales PDFTezoquitl PantliNo ratings yet

- Programación PDFDocument9 pagesProgramación PDFedgar yadhir perez hernandezNo ratings yet

- Taller de Ingeniería de Software PDFDocument7 pagesTaller de Ingeniería de Software PDFCarlos Omar Gris SuárezNo ratings yet

- Administración de Base de Datos PDFDocument11 pagesAdministración de Base de Datos PDFGenaro Lorenzo SantiagoNo ratings yet

- 0 - Taller de Emprendedores PDFDocument12 pages0 - Taller de Emprendedores PDFArista ArmandoNo ratings yet

- Simulación de ProcesosDocument10 pagesSimulación de Procesosedgar yadhir perez hernandezNo ratings yet

- Controladores Logicos ProgramablesDocument9 pagesControladores Logicos ProgramablesMicky CeceñaNo ratings yet

- Dina MicaDocument8 pagesDina MicaRayoOconerRodriguezNo ratings yet

- reDES EmergentesDocument7 pagesreDES EmergentesDario Perez PerezNo ratings yet

- Instrumentación y ControlDocument10 pagesInstrumentación y ControlaabbeeNo ratings yet

- Temario TECNM Invest OpersDocument20 pagesTemario TECNM Invest OpersLupita AmézquitaNo ratings yet

- Temario EDDocument8 pagesTemario EDLaboratorio BiomédicaNo ratings yet

- EjerciciosDocument14 pagesEjerciciosVictor Manuel Gonzalez HernandezNo ratings yet

- SAC1328Document9 pagesSAC1328Gonzalo Martinez QuiqueNo ratings yet

- Fundamentos de Ingeniería de SoftwareDocument12 pagesFundamentos de Ingeniería de SoftwareEDUARDO TOLENTINONo ratings yet

- Síntesis y Optimización de Procesos PDFDocument9 pagesSíntesis y Optimización de Procesos PDFr2rovbNo ratings yet

- Dibujo MecánicoDocument9 pagesDibujo MecánicoLebny MoralesNo ratings yet

- AE022 Electronica DigitalDocument12 pagesAE022 Electronica DigitalescamillaNo ratings yet

- Equipos MecanicosDocument10 pagesEquipos MecanicosJosé Rodolfo Manzano RosasNo ratings yet

- Fisica ModernaDocument7 pagesFisica ModernaMariana HernandezNo ratings yet

- Temario MecanismosDocument10 pagesTemario MecanismosGeovannied Zet de SantiagoNo ratings yet

- AC005 Ecuaciones DiferencialesDocument10 pagesAC005 Ecuaciones DiferencialesTotti CruzNo ratings yet

- Estrategias de Gestión de Servicios de Tecnologías de InformaciónDocument8 pagesEstrategias de Gestión de Servicios de Tecnologías de InformaciónTemo GálvezNo ratings yet

- Metodologia para El DiseñoDocument15 pagesMetodologia para El DiseñoEiner gallardp romeroNo ratings yet

- SAF1324-Mecanica de MaterialesDocument9 pagesSAF1324-Mecanica de Materialesjose angel carmona rodriguezNo ratings yet

- ISAU-2013-240 EstaticaDocument9 pagesISAU-2013-240 EstaticaFabiola MLNo ratings yet

- Diseño Practica y Reflexion de La Enseñanza Planificacion AnualDocument6 pagesDiseño Practica y Reflexion de La Enseñanza Planificacion AnualJULIETA ROMERONo ratings yet

- Tópicos Avanzados de Programación PDFDocument12 pagesTópicos Avanzados de Programación PDFidiavoloNo ratings yet

- Contabilidad Administrativa ADC 1012Document10 pagesContabilidad Administrativa ADC 1012Adolfo Alvarado MolinaNo ratings yet

- AE013 Dibujo Asistido Por ComputadoraDocument9 pagesAE013 Dibujo Asistido Por ComputadorancoNo ratings yet

- Tecnologías Inalámbricas PDFDocument7 pagesTecnologías Inalámbricas PDFUlises HernándezNo ratings yet

- Temario ETD1021Document8 pagesTemario ETD1021AbadNo ratings yet

- AE063 Taller de Base de Datos PDFDocument9 pagesAE063 Taller de Base de Datos PDFArlette VanesaNo ratings yet

- Temario Instalaciones Electricas InsdustrialesDocument12 pagesTemario Instalaciones Electricas InsdustrialesAnonymous pyi2cYg8No ratings yet

- Diseño e implementación de un currículo con enfoque por competencias: Experiencia en el Departamento de Matemáticas de la Escuela Colombiana de Ingeniería Julio GaravitoFrom EverandDiseño e implementación de un currículo con enfoque por competencias: Experiencia en el Departamento de Matemáticas de la Escuela Colombiana de Ingeniería Julio GaravitoNo ratings yet

- Innovación y sustentabilidad energética: Formación con MOOCs e investigación educativaFrom EverandInnovación y sustentabilidad energética: Formación con MOOCs e investigación educativaNo ratings yet

- Libro Científico: Investigaciones En Tecnologias De Información Informatica Y ComputaciónFrom EverandLibro Científico: Investigaciones En Tecnologias De Información Informatica Y ComputaciónNo ratings yet

- Integrando las TIC a la escuela de la sociedad del conocimiento: Formación y desarrollo profesional docenteFrom EverandIntegrando las TIC a la escuela de la sociedad del conocimiento: Formación y desarrollo profesional docenteNo ratings yet

- Métodos de modelación de procesos mediante respuesta al escalónDocument34 pagesMétodos de modelación de procesos mediante respuesta al escalónMikii GarcetteNo ratings yet

- Pie Diabetico PDFDocument17 pagesPie Diabetico PDFbachiche2012No ratings yet

- TFG - Jimenez Cortes, CarmenDocument146 pagesTFG - Jimenez Cortes, Carmenjose morenoNo ratings yet

- Ejemplos de Modelos AnalíticosDocument12 pagesEjemplos de Modelos AnalíticosMikii GarcetteNo ratings yet

- DM y Lesion Del PieDocument12 pagesDM y Lesion Del PieAnnie MVNo ratings yet

- ispLEVER CLASSIC 2.3Document13 pagesispLEVER CLASSIC 2.3jose morenoNo ratings yet

- LATAM-EP PDF-Alumno Clase1Document12 pagesLATAM-EP PDF-Alumno Clase1jose morenoNo ratings yet

- Rev 1 Articulo-PID-velocidadDocument6 pagesRev 1 Articulo-PID-velocidadjose morenoNo ratings yet

- Laboratorio de Señales y Sistemas Practica 1Document17 pagesLaboratorio de Señales y Sistemas Practica 1jose morenoNo ratings yet

- Mtodob 1 With Cover Page v2Document10 pagesMtodob 1 With Cover Page v2jose morenoNo ratings yet

- SC18Document8 pagesSC18jose morenoNo ratings yet

- Transmision de Audio Usando Redes Zigbee PDFDocument6 pagesTransmision de Audio Usando Redes Zigbee PDFThe Ghoul ZoneNo ratings yet

- File 1Document16 pagesFile 1jose morenoNo ratings yet

- Marco de Referencia 2018 (Ingenierias)Document127 pagesMarco de Referencia 2018 (Ingenierias)José Luis Sánchez AmadorNo ratings yet

- Muestreo y Reonstruccion de Señales-Funcion de TransferenciaDocument16 pagesMuestreo y Reonstruccion de Señales-Funcion de Transferenciajesuslopez_mecaNo ratings yet

- AvrDocument387 pagesAvrEddie Marin100% (4)

- Amplificacion PDFDocument546 pagesAmplificacion PDFJoshua SchultzNo ratings yet

- Tarjeta - Madre - B365M Gaming HDDocument7 pagesTarjeta - Madre - B365M Gaming HDjose morenoNo ratings yet

- 29 Analisis - de - Senales - Audio - Utilizando - Transformada - GaborDocument8 pages29 Analisis - de - Senales - Audio - Utilizando - Transformada - Gaborjose morenoNo ratings yet

- Aguirre - Desarrollo y Análisis de Clasificadores de Señales de Audio PDFDocument119 pagesAguirre - Desarrollo y Análisis de Clasificadores de Señales de Audio PDFjose morenoNo ratings yet

- Análisis resultados pruebas equipos audio MATLABDocument44 pagesAnálisis resultados pruebas equipos audio MATLABjose morenoNo ratings yet

- DialneDocument10 pagesDialneghinNo ratings yet

- Sonido DigitalDocument252 pagesSonido DigitalamgstiNo ratings yet

- Reduccion de Ruido en AudiosDocument118 pagesReduccion de Ruido en AudiosMarvin MoralesNo ratings yet

- Reconocimiento de Voz en MatlabDocument88 pagesReconocimiento de Voz en MatlabJennyfer Herrera AvilezNo ratings yet

- Memoria PFCDocument110 pagesMemoria PFCjose morenoNo ratings yet

- Transmision de Audio Usando Redes Zigbee PDFDocument6 pagesTransmision de Audio Usando Redes Zigbee PDFThe Ghoul ZoneNo ratings yet

- Páginas Extraídas Sin TítuloDocument6 pagesPáginas Extraídas Sin Títulojose morenoNo ratings yet

- FiltroDocument1 pageFiltrojose morenoNo ratings yet

- Articulo - 1 1Document1 pageArticulo - 1 1jose morenoNo ratings yet

- Reporte médico Bloque 58 CobrapetroDocument2 pagesReporte médico Bloque 58 CobrapetroJaneth MorochoNo ratings yet

- 27 de Marzo - Filosofia y CristianismoDocument23 pages27 de Marzo - Filosofia y CristianismoGabriela Rodriguez CaldasNo ratings yet

- FarmacosDocument2 pagesFarmacosMilagros AlvarezNo ratings yet

- Animación A La Lectura (Cuentos)Document7 pagesAnimación A La Lectura (Cuentos)torrecita81No ratings yet

- Cuestiones TipológicasDocument3 pagesCuestiones TipológicasNorma CamilaNo ratings yet

- Toxina RTXDocument5 pagesToxina RTXAuroraCortesNo ratings yet

- 00 U2000 R16C50 Funciones BásicasDocument82 pages00 U2000 R16C50 Funciones BásicasAlvaro CueNo ratings yet

- TrabajoDocument14 pagesTrabajoLovelyperson LoveNo ratings yet

- Embajadores Derribando Argumentos.Document2 pagesEmbajadores Derribando Argumentos.Joel AlvaradoNo ratings yet

- CuestionarioDocument493 pagesCuestionarioAndrea Azucena Moreira zambranoNo ratings yet

- Esquema de Analisis de ObraDocument2 pagesEsquema de Analisis de ObrakaritoNo ratings yet

- Espacios-Ana Kely Andrade Q.Document15 pagesEspacios-Ana Kely Andrade Q.Kely AndradeNo ratings yet

- Betsabe H. García PedagogíaDocument34 pagesBetsabe H. García PedagogíaRoman Alzate 619No ratings yet

- Metodología Investigación SocialDocument6 pagesMetodología Investigación SocialRUBEN100% (1)

- AnálisisSPSSDocument12 pagesAnálisisSPSSMaryuri Lisset MoncayoNo ratings yet

- Ensayo Core ArendtDocument5 pagesEnsayo Core ArendtJorge UaracNo ratings yet

- Diagnostico Psi 101Document5 pagesDiagnostico Psi 101Daniela CarrascoNo ratings yet

- Carbohidratos: clasificación, estructura y funcionesDocument132 pagesCarbohidratos: clasificación, estructura y funcionesFernando Garcia MendozaNo ratings yet

- Control de Lectura El Extraño CasoDocument3 pagesControl de Lectura El Extraño CasoGinna Carriel100% (1)

- 3 Lengua y Literatura Actividad Sumativa Modulo 4Document11 pages3 Lengua y Literatura Actividad Sumativa Modulo 4ILCI ALVAREZNo ratings yet

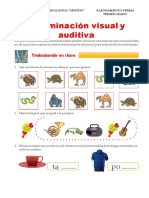

- Discriminación visual y auditivaDocument6 pagesDiscriminación visual y auditivaVia SajaNo ratings yet

- Dolor Psicógeno - WikipediaDocument9 pagesDolor Psicógeno - WikipediaMatty A.No ratings yet

- Introducción a la Enfermería UNIAPADocument7 pagesIntroducción a la Enfermería UNIAPAESMARLIS BELLO JOSENo ratings yet

- Validación de Instrumento - 2Document2 pagesValidación de Instrumento - 2MikeNo ratings yet

- Ley 24 417 Violencia FamiliarDocument2 pagesLey 24 417 Violencia FamiliarpepaNo ratings yet

- Guía de Lectura 2 - ZenobiDocument4 pagesGuía de Lectura 2 - ZenobimiriamNo ratings yet

- Ensayo Sobre La Ley PenalDocument6 pagesEnsayo Sobre La Ley PenalTransportes SalinasNo ratings yet

- Rúbrica de involucramiento estudiantilDocument5 pagesRúbrica de involucramiento estudiantilherbyn10No ratings yet