Professional Documents

Culture Documents

Fonte Chaveada

Uploaded by

Matheus RufinoOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Fonte Chaveada

Uploaded by

Matheus RufinoCopyright:

Available Formats

Projeto: Fonte chaveada

Matheus Rufino

160925 UNICAMP (IFGW)

Anlise e caracterizao do sistema de circuitos que compe uma fonte

chaveada

Anlise e caracterizao de cada um dos blocos que compe a fonte chaveada e tambm do seu

circuito completo, seu funcionamento e como os componentes, principalmente, amplificador

operacional e transstor, atuam como partes cruciais de um circuito controlador interno.

G_F 540B_2017S1 - Mtodos da Fsica Experimental I

Parte Experimental e aquisio dos dados: Matheus, Diego e Eduardo

FONTE CHAVEADA

Introduo e resumo.

Com a inteno de modelar uma fonte de alimentao eletrnica incorporada de um regulador chaveado, doravante Fonte

Chaveada, monta-se um circuito composto de 5 sub-blocos, sendo cada bloco um circuito com uma funo especfica.

Neste relatrio, os cinco circuitos que compe a fonte e a fonte sero criteriosamente analisados em respeito principalmente a sua

caracterizao e uma anlise eletrnica sobre o funcionamento de cada componente e como o todo se apresenta.

Dessa forma, visamos observar o comportamento componente-a-componente de uma fonte que possui um circuito controlador

interno que chaveia (comuta) a corrente, ligando e desligando rapidamente, de forma a manter uma tenso de sada estabilizada. O relatrio

tem a proposta de apresentar e explicar o funcionamento desse circuito e tambm testar os modelos fsicos que circundam esse universo.

As caractersticas gerais desejadas neste projeto para a fonte chaveada so:

1. Frequncia de 5 kHz.

2. Sada do circuito integrador 10 V

3. Tenso de entrada 15 V

4. Tenso de referncia 0~5 V

5. Tenso de sada 0~15 V

Os materiais utilizados so:

1. Fonte de alimentao 0 15

2. Amplificadores operacionais AO741

3. Diversos capacitores

4. Diversas resistncias

5. Protoboard

Printed by Wolfram Mathematica Student Edition

2 pjfontechaveada.nb

ndice

1. Anlise e discusso por bloco do circuito da fonte chaveada.

Anlise e caracterizao de todos os circuitos (blocos) que compe a fonte chaveada.

a. Oscilador de relaxao

b. Integrador

c. Gerador de pulsos

d. Transistor chave e filtro (capacitor)

e. Realimentao: Amplificador da diferena e Integrador acoplado.

2. Anlise e caracterizao do circuito completo

Anlise e caracterizao do circuito completo da fonte chaveada.

a. Funcionamento

b. Caracterizao

c. Anlise e discusso

3. Concluso

Concluso e discusso final.

Printed by Wolfram Mathematica Student Edition

pjfontechaveada.nb 3

1. Anlise por bloco do circuito da fonte chaveada: Anlise e caracterizao de todos os circuitos

(blocos) que compe a fonte chaveada.

Circuito 1. a. Oscilador de relaxao Teoria e Modelo

1.a. Oscilador de relaxao

Modelo simples de oscilador onde o controle do tempo est associado a ciclos de carga/descarga de um capacitor. O capacitor (C3

= 45 nF 1) carrega/descarrega por conta da resistncia (R5 = 2.2 0.1 k ) entre a entrada inversora e a sada do amplificador opera-

cional AO741 (OP1), quando o potencial da entrada inversora (Vc) atinge o valor do potencial da entrada no inversora (+) o sinal da sada

(Vosc) invertido, iniciando assim um novo ciclo de carga/descarga no capacitor.

O potencial da entrada no inversora ser a tenso de referncia desse circuito, dado por:

R1

= (1)

R1 + R2

A frequncia desse oscilador uma funo da capacitncia, a resistncia em srie e o que aponta a tenso de referncia:

+1 -1

f = 2 RC ln (2)

1-

No caso do circuito da Figura 1,

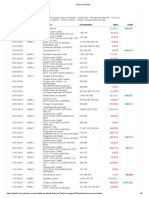

Tabela 1. Impedncias e medidas modelo experimental

Resistncias Medidas

R1 R7 = (1.0 0.1) k C C3 = (451) nF

R2 R6 = (1.0 0.1) k f = 4 kHz

R R5 = (2.2 0.1) k Vs = 15 V

Figura 1. Circuito a Oscilador de relaxao

As funes dos componentes da figura 1 so:

R6 e R7 Fornecer a tenso de referncia para a entrada no-inversora.

R5 Limitar a tenso na carga do capacitor proveniente da sada do circuito.

C Alterar a sada do amplificador operacional carregando a entrada inversora

Printed by Wolfram Mathematica Student Edition

4 pjfontechaveada.nb

Anlise e caracterizao do circuito 1.a.

Neste circuito temos um feedback por meio de um Schimidt trigger caracterizado pelas resistncias R7 (1 0.1 k) e R6 (1 0.1 k)

acopladas no pino 3 do OP1 (a entrada no inversora) que possui a funo de comparar dois sinais distintos, associando essa realimentao

a um capacitor (C3 = 451 nF) e uma resistncia (R5 = 2.2 0.1 k) podemos criar um oscilador a partir do decaimento do capacitor no

tempo, da forma que:

q(t)

Vc = Vc(t) = (3)

C

q0 -t/RC

Sendo Vc(t) = na descarga e (4)

C

q0 1 - -t/RC

Vc(t) = durante a carga. (5)

C

O decaimento do capacitor forma o oscilador que possui um ciclo que uma rotina, supondo Vout = Vs, da forma:

1. O capacitor carrega at que Vc (V+) = (1/2)Vs = VR, sendo Vs a tenso que polariza o OP1;

2. A partir deste ponto Vosc -Vs;

3. O capacitor vai descarregar e recarregar negativamente at que Vc (V+) = VR;

4. A partir deste ponto Vosc + Vs, recomeando o ciclo.

A tenso de sada, Vosc, que ser usada para alimentar o prximo bloco da fonte chaveada, pode ser caracterizada da forma:

R7 R7

I) Se Vosc = Vs V+ = R7+R6 Vs implicando que o comparador muda de sinal quando V+ Vc < 0 Vc = R7+R6

Vs.

R7 R7

II) Se Vosc = Vs V+ = R7+R6 Vs implicando que o comparador muda de sinal quando V+ Vc > 0 Vc = R7+R6 Vs.

Desta forma podemos definir as equaes para a frequncia desse oscilador,

sendo IC e IR as correntes que passam no capacitor C3 e na resistncia R5 :

v- v o - v-

IC = C = IR = (6)

t R

Para v- tenso AC na entrada inversora e vo tenso AC na sada, pino 6. (Lei dos ns de Kirchoff ) .

Resolvendo a equao diferencial:

v- v- v0 v- t

+ = = v- = v0 - A -t/(R C) (7)

t RC RC (v0 - v- ) RC

t = 0 : v- = - L = L - A 0 A = L ( + 1) (8)

T T

t = : v- = L = L - L( + 1) - 2 R C (9)

2

Assim,

T ( - 1)

- 2 R C = (10)

( + 1)

( - 1)

T = 2 R C ln (11)

( + 1)

(12)

Para gerar as curvas tericas para VC , V+ e VOSC utilizaremos as seguintes funes como modelo:

Vosc = vo (t) = 12.1105 SquareWave[0.00408 t] (13)

V+ = 6 ' SquareWave[0.00408 t] (14)

VC = Equaes (4) e (5) (15)

Printed by Wolfram Mathematica Student Edition

pjfontechaveada.nb 5

Caracterizao do circuito 1.a.

Figura a.1: Experimental Tenso (V) nos pinos 2,3,6 vs Tempo (s)

10

5

Tenso (V)

0

-5

-10

0 200 400 600 800 1000

Tempo (s)

Pino 2: VC carga/descarga Capacitor Pino 3: V+ tenso na entrada no inversora

Pino 6: Vosc tenso de sada do oscilador de relaxacao

Figura a.2 Tenso (V) vs Tempo (s): Modelo e Experimental para VOSC

10

5

Tenso (V)

-5

-10

-400 -200 0 200 400

Tempo (s)

Tenso de (V) para VOSC Experimental

FIT VOSC [t] := 12.1105` SquareWave[0.00408` t]

Uma onda quadrada de amplitude (12 1) V e frequncia de 4.08 kHz como sada do nosso oscilador de relaxao experimental.

Printed by Wolfram Mathematica Student Edition

6 pjfontechaveada.nb

Figura 1.3 Tenso (V) vs Tempo (s): Modelo e Experimental para VOSC

2

Tenso (V)

Out[181]= 0

-2

-4

-6

-400 -200 0 200 400

Tempo (s)

Tenso (V) para V+ Experimental FIT V+ [t] := 6` SquareWave[0.00408` t]

Uma onda quadrada de amplitude (6 1) V e frequncia de 4.08 kHz como a tenso na entrada no-inversora V+ H amplificao

do sinal de sada! ||Vosc|| = 2 || V+ ||

Carga (Figura A) e Descarga (Figura B) do Capacitor:

Figura 1.4.A. Tenso (V) vs Tempo (s): Carga do Capacitor

7

5

Tenso (V)

0

0 20 40 60 80 100

Tempo (s)

Tenso (V) para VC Experimental

Fit : 8.65374 1 - -0.016743 t

Printed by Wolfram Mathematica Student Edition

pjfontechaveada.nb 7

Figura 1.4.B. Tenso (V) vs Tempo (s): Descarga do Capacitor

4

Tenso (V)

0

105 110 115 120 125 130 135 140

Tempo (s)

Tenso (V) para VC Experimental

Fit : 271.65 -0.0369525 t

Printed by Wolfram Mathematica Student Edition

8 pjfontechaveada.nb

Circuito 1. b. Integrador

1.b. Integrador

O circuito integrador de modo geral, designado pelo nome de Integrador de Miller, caracteriza-se pela funo

1 t

vout (t) = - vin (t ') t ' (16)

RC 0

Experimentalmente, para o projeto da fonte chaveada, utilizamos o circuito da figura 3 composto com uma resistncia R3 (100 1)

k afim de limitar o ganho em d.c.

No caso do circuito da figura 3:

Tabela 2. Impedncias e medidas

Impedncias

R4 = (1.0 0.1) k

R3 = (100.0 0.1) k

C2 = (75 1) nF

f = 4 kHz

Figura 2. Circuito b Integrador

As funes dos componentes da figura 2 so:

R3 Controle do ganho de tenso no capacitor.

R4 Fornecer a queda de tenso entre Vint e V- de modo que C2 opere como integrador.

C Integrar a corrente at um certo limite de ganho, condicionado pela resistncia R3.

Anlise e caracterizao do circuito 1.a.

Anlise e caracterizao do circuito:

Para o circuito integrador temos a sada do bloco 1 na resistncia R4, sendo um sinal a.c caracterizado na seco 1.a. A entrada deste

circuito o sinal Vosc que dever ser integrado por conta do arranjo esquematizado na figura 2. Assim, para caracterizar esse circuito deve-

se investigar a entrada e a sada e observar se o modelo do circuito integrador est operando de forma correta.

O modelo para esse circuito ser:

-j 1 -1

Zeq = +

2 f C2 R3 (17)

Vosc = v0 (t) = R4 i(t) i(t) = -v0 (t) / R4

Printed by Wolfram Mathematica Student Edition

pjfontechaveada.nb 9

Vint = vout (t) = Zeq i(t) (18)

j 1 -1 v0 (t)

vout (t) = - + (19)

2 f C2 R3 R4

j 1 -1 Vosc(t)

Vint (t) = - + (20)

2 f C2 R3 R4

Podemos observar que para baixas frequncias a resistncia R4 controlar para que a tenso nos terminais do capacitor no sejam grandes

demais, ou seja, a medida que o capacitor esteja carregado o suficiente a corrente no mais passar por ele e ser ento dissipada em R4

que funciona como um limitador de ganhos para baixas frequncias.

Portanto, estamos garantindo que para a frequncia desejada no projeto o circuito integrador possa operar da forma que o sinal de entrada

saa em Vint integrado (equao 20). Com a finalidade de observar o funcionamento deste bloco e como ele se relaciona com a fonte

chaveada, adquirimos os sinais de entrada e sada versus o tempo mostrados nas figuras abaixo:

Figura b.1 Tenso (V) vs Tempo (s): Entrada e Sada do Circuito Integrador

10

5

Tenso (V)

0

Out[183]=

-5

-10

-15

0 200 400 600 800 1000

Tempo (s)

Entrada VOSC (V) no circuito integrador

12.4 TriangleWave[0.136 + 0.003755 t]

Sinal de sada VINT (V) do circuito integrador

Printed by Wolfram Mathematica Student Edition

10 pjfontechaveada.nb

Figura b.2 Tenso (V) vs Tempo (s): Sada do Circuito Integrador

15

10

5

Tenso (V)

0

Out[185]=

-5

-10

-15

200 300 400 500 600

Tempo (s)

Sinal de sada VINT (V) do circuito integrador 12.4 TriangleWave[0.136 + 0.003755 t]

Dessa forma estaremos fornecendo uma onda triangular para a entrada no inversora do Op.Amp 3 que ser o gerador de pulsos da fonte

chaveada.

Printed by Wolfram Mathematica Student Edition

pjfontechaveada.nb 11

Circuito 1. c. Gerador de pulsos

1.c. Gerador de pulsos

O circuito gerador de pulsos aqui ser caracterizado para uma tenso de referncia V Ref = (5.0 0.1) V proveniente de uma fonte

fixa, como representado no circuito da figura 4. Esse circuito responsvel por comparar um sinal de referncia com a tenso na entrada

no inversora V+ e pela regra de ouro do Op.Amp funcionar como um circuito comparador da forma que observamos nas figuras no

tpico de anlise e caracterizao do circuito.

Figura 3. Circuito c Gerador de Pulsos

As funes dos componentes do circuito c da figura 3 so:

Amplificador Operacional 3 sendo alimentado por Vint (AC) e Vref (DC) funcionando como um comparador de sinais, gerando

assim um pulso de acordo com essa comparao.

Printed by Wolfram Mathematica Student Edition

12 pjfontechaveada.nb

Anlise e caracterizao do circuito c da figura 3:

Figura c.1 Tenso (V) vs Tempo (s): Gerador de pulso com Vref = (5.0 0.1)

15

10

5

Tenso (V)

0

Out[187]=

-5

-10

-15

0 200 400 600 800 1000

Tempo (s)

Sinal de entrada VINT (V) no circuito gerador de pulso

Sinal de sada Vpulso (V) do gerador de pulso 14.255 SquareWave[0.174 + 0.00371 t]

Tenso VRef = (5.0 0.1)V

Conforme a tenso de referncia na entrada no inversora varie, a largura do pulso tambm ir variar. Este o aspecto primordial para o

funcionamento da fonte chaveada uma vez que parte do sistema de controle da tenso ser comandado por este comparador uma vez que a

tenso de referncia passa a ser dada pelo bloco de feedback.

Printed by Wolfram Mathematica Student Edition

pjfontechaveada.nb 13

Circuito 1. d. Transistor como chave e filtro (capacitor)

1.d. Transistor como chave e filtro (capacitor)

Este circuito caracteriza-se pela atuao de um transistor BD135 com funo de chave aberta/fechada de acordo com a corrente que

recebe em sua base atravs da tenso do pulso do bloco anterior. Usando uma referncia em sua polarizao DC em Vin, teremos ento um

controle para determinada largura do pulso em que o transistor ir funcionar como uma chave impedindo ou no a passagem de corrente.

Dessa forma ele ir regular o ganho para tenso de sada Vout que est em paralelo com o capacitor C1 que funciona como um filtro para a

realimentao.

Tabela 3. Impedncias e medidas

Impedncias

RB = (10.0 0.1) k

R8 = (10.0 0.1) k

C2 = (10 1) F

Vin = (15.03 0.15) V (DC)

Vpulso = 14.255 SquareWave[0.174 + 0.00371 t]

Figura 4. Circuito d Transistor como chave e filtro (capacitor)

As funes dos componentes do circuito d da figura 4 so:

Transistor (T1) BD135: Controlador de ganho de corrente no emissor de acordo com a corrente na base. A configurao de um

seguidor de emissor (coletor comum).

Capacitor (C1): Filtro para Vout, se C1 est carregado a tenso que chega do emissor enviada para o bloco de feedback, ou seja,

atenua o sinal de sada enquanto o capacitor carrega.

Anlise e caracterizao do circuito c da figura 3:

Utilizando uma tenso de referncia de (5.00 0.01)V podemos caracterizar esse circuito pelas equaes, usando I B como corrente

na Base, IE a corrente no emissor e IC a corrente no coletor.

Printed by Wolfram Mathematica Student Edition

14 pjfontechaveada.nb

IE = IC + IB (21)

Ic IE e IB << IC = IC / IB (22)

VCE = Vin - Vout (23)

No caso do circuito montado com base comum, VE ~ VB - 0.7V para Vin > 0.7. Portanto, como no h resistncia no coletor temos que a

impedncia da entrada muito maior do que a de sada havendo assim ganho de corrente sem ganho de tenso.

Av = vout / vin = Vout / Vpulso 1. , enquanto Vin > 0.7 V. (24)

As figuras abaixo caracterizam a sada deste circuito:

A figura d.1 apresenta uma curva caracterstica do transistor em que a tenso medida no eixo y pode ser interpretada como a corrente no

coletor. O ponto de operao desejado deste transistor o ponto de corte, onde ele ir funcionar como uma chave:

Figura d.1 Tenso (V) vs Tempo (s): VOUT

3.0

2.5

Tenso (V)

2.0

Out[303]= 1.5 Interpolao dos pontos

1.0

0.5

0.0

0 20 40 60 80 100 120

Tempo (s)

VOUT com (5.00.1) V para teste

Na figura d.2 temos caracterizadas a entrada e sada deste bloco do circuito, sendo a sada a prpria tenso de sada da fonte.

Printed by Wolfram Mathematica Student Edition

pjfontechaveada.nb 15

Figura d.2 Tenso (V) vs Tempo (s): VOUT e VPulso

15

10

5

Tenso (V)

0

Out[356]=

-5

-10

-15

0 200 400 600 800 1000

Tempo (s)

Tenso VOUT (V)

Sinal de sada Vpulso (V) do gerador de pulso

Printed by Wolfram Mathematica Student Edition

16 pjfontechaveada.nb

Circuito 1. e. Realimentao: Amplificador da diferena e Integrador acoplado.

Realimentao: Amplificador da diferena e Integrador acoplado.

Este bloco da fonte-chaveada possui a funo de ser a realimentao com memria para a sada da fonte, controlando a largura do pulso do

comparador a medida que o seu integrador local age para manter a sada da tenso do amplificador da diferena (Verro) prximo de zero

com um sinal anterior rejeitado pelo filtro do capacitor 1 do bloco da chave transistor. Assim, a tenso de referncia Vref controlada opera

na subtrao da tenso que chega nas resistncias R1 e R2 (1.00 0.01) k.

Aps a subtrao, a sada VErro integrada no Op.Amp 6. Para caracterizar a realimentao usaremos as equaes para o circuito amplifi-

cador da diferena e iremos enfim caracterizar a prpria fonte chaveada.

Tabela 4. Impedncias e medidas

Impedncias

R1 = R2 = R14 (1.0 0.1) k

R10 = R11 = R9 = R13 = R12 = (100.0 0.1) k

C4 = (100 1) nF

Vref = (0 ~ 15) V

Vpulso = 14.255 SquareWave[0.174 + 0.00371 t]

Figura 5. Circuito (e) Realimentao: Amplificador da diferena e Integrador acoplado.

As funes dos componentes do circuito e da figura 5 so:

Transistor (T1) BD135: Controlador de ganho de corrente no emissor de acordo com a corrente na base. A configurao de um

seguidor de emissor (coletor comum).

Capacitor (C1): Filtro para Vout, se C1 est carregado a tenso que chega do emissor enviada para o bloco de feedback, ou seja,

atenua o sinal de sada enquanto o capacitor carrega.

OP6: Circuito Integrador, analisado no tpico 1.b.

OP5: Circuito amplificador da diferena

Anlise e caracterizao do circuito amplificador da diferena:

As equaes que caracterizam esse circuito so:

Printed by Wolfram Mathematica Student Edition

pjfontechaveada.nb 17

Vsubtr = (R12 + R11 ) I1 + V1 (25)

Onde V1 Vout(R1*R2/R1+R2) = Vout/2.

Vsubtr = V- (1 + R12 / R11 ) - V1 R12 / R11 , V- = -R9 * I2 V- = (R9 / (R10 + R9 ). (26)

Desta forma chegamos a:

R12 R9

Vsubtr = V+ 1 + - V- R12 / R11 (27)

R11 R10 + R9

Vsubtr = a V+ - b V- (28)

R12 R9

a= 1+ (29)

R11 R10 + R9

R12

b= , como R9,12 = 100 k a = b (30)

R11

Portanto, para esse caso experimental temos que Vsubtr = V+ - V- sendo V+ a tenso de referncia controlada por um potencimetro e V-

a tenso rejeitada na malha de Vout . O valor da sada Verro ou Vsubtr ser integrada pelo circuito integrador e esse valor ser armazenado

para ser usado na prxima iterao da fonte.

2. Anlise e caracterizao do circuito completo da fonte chaveada.

2.a. Funcionamento da fonte chaveada

O funcionamento total da fonte chaveada ser a soma das iteraes realizadas por cada bloco que compe o circuito inteiro. Assim, a fonte

trabalha graas a operao de trs sistemas controladores:

1) Oscilador de relaxao e integrador: Criando uma onda triangular com frequncia definida para 4 kHz que servir para, em conjunto

com o comparador, criar um pulso de largura e frequncias definidas e conhecidas;

2) Gerador de Pulso, comparador e feedback: A onda triangular comparada com o sinal da integrao da diferena amplificada nos

Op.Amp 6 e 5 respectivamente. Enquanto o circuito integrador no saturar em seu limite fsico esse pulso ser da largura necessria para

que o prximo bloco rejeite ou no tenso com a atuao do transistor, dando um ganho de corrente se necessrio. Dessa forma estamos

garantindo que a tenso de sada da fonte ser constante e controlada por uma tenso de referncia definida.

3) Transistor como chave e filtro (capacitor): O terceiro e ltimo bloco um transistor polarizado com emissor comum numa tenso DC de

(15.00.1)V. A funo desse transistor manter um ganho de corrente Av 1 e funcionar como uma chave liga/desliga para a passagem

de corrente da base para o emissor. Esse sinal ser ento filtrado pela carga de um capacitor em paralelo e parte dele ir voltar ao bloco do

feedback e ento ser feita a diferena entre esse sinal e a referncia. Enquanto o integrador do bloco 2 for capaz de integrar esse sinal da

diferena, a fonte ir estabilizar a sada de tenso e estar funcionando normalmente.

2.b. Caracterizao

A caracterizao da fonte chaveada fica a critrio dos sinais de sada Vout, a sada do integrador feedback para o comparador, Verro e o

Vpulso.

Caracterizao do sinal de sada Vout em relao ao Verro

Printed by Wolfram Mathematica Student Edition

18 pjfontechaveada.nb

Resposta do circuito a variao da tenso de referncia

Printed by Wolfram Mathematica Student Edition

pjfontechaveada.nb 19

Figura 2.b.

Sinais VErro e VOut (V) em relao a VRef (V)

12

10

Tenso (V)

8

Variao de VErro

Out[386]=

6

Variao de VOut

4

0

0 2 4 6 8 10 12 14

Tenso de Referncia (V)

2.d. Discusso e Concluso

Em face de todos os dados presentes nesse relatrio, fomos capazes de verificar o funcionamento experimental dessa fonte equipada de um

circuito regulador de tenso na sada. A tenso de referncia variando de 0 at 6V apresenta o funcionamento da fonte at a sua saturao

em 13V, a partir deste ponto a fonte mantm estabilizada a tenso de sada ao preo da operao de diferena entre a tenso de referncia e

o resto que volta para o feedback para ser diferenciado e integrado, armazenando assim uma memria nesse integrador. O funcionamento

da fonte estvel para os valores de erro medidos entre 760.2 0.2 mV e 8.470.01 V, retornando um sinal estvel de 13.2 V nesta

sequncia.

Dessa forma pudemos verificar a atuao desses importantes componentes para o desenvolvimento de sistemas controladores.

Bibliografia:

Brophy, J. J. Basic electronics for scientists. McGraw-Hill, New York, 5th edition.

Printed by Wolfram Mathematica Student Edition

You might also like

- Apostila Fabricacao de Acucar 2012 2Document9 pagesApostila Fabricacao de Acucar 2012 2Roberto Corazza DolciNo ratings yet

- SISBB - Sistema de Informações Banco Do Brasil - 23/03/2020 - Autoatendimento BB - 20:18:23 Agência: 3069-4 Conta: 27060-1 ClienteDocument3 pagesSISBB - Sistema de Informações Banco Do Brasil - 23/03/2020 - Autoatendimento BB - 20:18:23 Agência: 3069-4 Conta: 27060-1 ClienteDomínio FrancaNo ratings yet

- Infocus In2x Userguide PTDocument8 pagesInfocus In2x Userguide PTGeorge TenorioNo ratings yet

- 3 - Aspectos Tecnológicos Da Usinagem A Seco e Com Mínima Quantidade de Fluido Na Furação Com Broca Helicoidal - MestradoDocument208 pages3 - Aspectos Tecnológicos Da Usinagem A Seco e Com Mínima Quantidade de Fluido Na Furação Com Broca Helicoidal - MestradoAmanda Dela JustinaNo ratings yet

- Contrato cessão direitos imóvelDocument3 pagesContrato cessão direitos imóvelPablo RuanNo ratings yet

- Estresse Ocupacional e A Sindrome de Burnout Na Vida Profissional Das MulheresDocument50 pagesEstresse Ocupacional e A Sindrome de Burnout Na Vida Profissional Das Mulheresgcarlos_24No ratings yet

- Cálculo estrutural linha de vida industrialDocument12 pagesCálculo estrutural linha de vida industrialPaulo VenutoNo ratings yet

- Ligas Ferrosas: Aços e seus Elementos de LigaDocument86 pagesLigas Ferrosas: Aços e seus Elementos de LigaEltonNo ratings yet

- ALVES, G. O Que É A Mundialização Do Capital. Trabalho e Mundialização Do Capital - A Nova Degradação Do Trabalho Na Era Da Globalização.Document11 pagesALVES, G. O Que É A Mundialização Do Capital. Trabalho e Mundialização Do Capital - A Nova Degradação Do Trabalho Na Era Da Globalização.Luiz LimaNo ratings yet

- Classificação das contas contábeisDocument3 pagesClassificação das contas contábeisWELLINGTON MARQUESNo ratings yet

- Prova de Matemática do 6o ano do CMBDocument24 pagesProva de Matemática do 6o ano do CMBOsmayr SousaNo ratings yet

- EC380D L Volvo valve specificationsDocument2 pagesEC380D L Volvo valve specificationspaulo100% (1)

- Arquivo de ImagensDocument1,496 pagesArquivo de ImagensMárcio LopesNo ratings yet

- Relatório de Medição de Espessura Por Ultra-SomDocument1 pageRelatório de Medição de Espessura Por Ultra-SomI9Educação Projeto100% (1)

- Clip 18042014Document61 pagesClip 18042014Ronnie TurriniNo ratings yet

- Rotinas GarçomDocument6 pagesRotinas GarçomJuan Souza100% (1)

- Edital N 36-21 Classificao Preliminar - Vestibular 2021Document34 pagesEdital N 36-21 Classificao Preliminar - Vestibular 2021KatiuskaNo ratings yet

- PPRA Supermercado GiganteDocument21 pagesPPRA Supermercado Giganteedson de sousa parente jrNo ratings yet

- Doubleway 3F 380 Dwtt10a2 - Dwtt80a2Document78 pagesDoubleway 3F 380 Dwtt10a2 - Dwtt80a2Janaína da Silva dos Santos100% (1)

- Componentes Fisicos Uma Rede Aula 3Document25 pagesComponentes Fisicos Uma Rede Aula 3Eurico RodriguesNo ratings yet

- Listado CCTV Febrero 2020 Hikvision - Precio MayorDocument11 pagesListado CCTV Febrero 2020 Hikvision - Precio MayorJosue ValdezNo ratings yet

- Simulado 3-CompletoDocument12 pagesSimulado 3-CompletoSAILAVELLOSONo ratings yet

- Laboratório Java OODocument155 pagesLaboratório Java OOJanerson DouglasNo ratings yet

- NAMITECDocument2 pagesNAMITECAlexandre KennedyNo ratings yet

- UltimoDocument1 pageUltimoJorge Rafael AbreuNo ratings yet

- Manual de Uso Do ER9x. Porque Você Pediu Por Isto!Document37 pagesManual de Uso Do ER9x. Porque Você Pediu Por Isto!Edson ReisNo ratings yet

- Modelo Capm e Teorias AlternativasDocument20 pagesModelo Capm e Teorias AlternativasAnderson SousaNo ratings yet

- Pasta 1Document14 pagesPasta 1Rosi DutraNo ratings yet

- Pedido 1064Document1 pagePedido 1064Diego CarlosNo ratings yet

- Camila Silva - Costa - 70000000108944Document4 pagesCamila Silva - Costa - 70000000108944CAMILANo ratings yet